#### **Features**

- 12V Power supply

- Drain Voltage Range 1.0V to 20V

- · Internal Gate Voltage Charge Pump

- · Controlled Turn on Delay

- · Controlled Load Discharge Rate

- · Controlled Turn on Slew Rate

- 2mm x 2mm TDFN-8 Package

- · Pb-Free / Halogen-Free / RoHS compliant

#### **Applications**

- · Power Rail Switches

- · Hot Plugging Applications

- · Soft Switching

- Personal computers and Servers

- · Data Communications Equipment

#### **Pin Configuration**

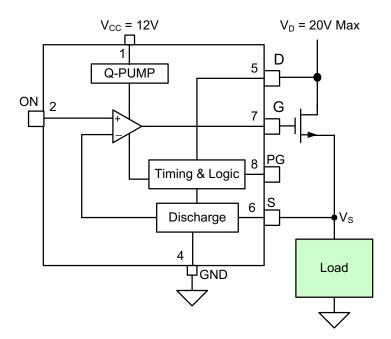

#### **Block Diagram**

#### **Pin Description**

| Pin# | Pin Name | Туре   | Pin Description                                                                                                                |

|------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------|

| VCC  | 1        | Power  | Supply Voltage                                                                                                                 |

| ON   | 2        | Input  | CMOS Logic Level. High True                                                                                                    |

| NC   | 3        |        | No Connect.                                                                                                                    |

| GND  | 4        | GND    | Ground.                                                                                                                        |

| D    | 5        | Input  | FET Drain Connection                                                                                                           |

| S    | 6        | Input  | Source Connection                                                                                                              |

| G    | 7        | Output | FET Gate Drive                                                                                                                 |

| PG   | 8        | Output | Output CMOS Open Drain - Power Good, indicates external FET fully on. Pull-up resistor greater than $300 k\Omega$ recommended. |

#### **Overview**

The SLG55022 N-Channel FET Gate Driver is used for controlling a delayed turn on and ramping slew rate of the source voltage on N-Channel FET switches from a CMOS logic level input. Intended as a supporting control element for switched voltage rails in energy efficient, advanced power management systems, the SLG55022 also integrates circuits to discharge opened switched voltage rails. The gate driver is available in a variety of configurations supporting a range of turn-on slew rates from 0.80V/ms up to 4V/ms which, depending on load supplying source voltages in the range of 1.0V to 20V results in ramp times from  $200\mu s$  to over 20ms(see Application Section). Delays until the ramp begins are source voltage independent and range from  $250\mu s$  to 5ms. A power good condition is output to indicate that the ramp-up slew of the source voltage is finished. Additionally, an internal discharge circuit provides a controlled path to remove charge from open power rails. The SLG55022 gate drive is packaged in an 8 pin DFN package.

When used with external N-Channel FETs, the SLG55022 supports low transient, energy efficient switching of high current loads at source voltages ranging from 1.0V to 20V.

#### **Ordering Information**

| Part Number        | Туре                              |

|--------------------|-----------------------------------|

| SLG55022-200030V   | TDFN-8                            |

| SLG55022-200030VTR | TDFN-8 - Tape and Reel (3k units) |

#### **Absolute Maximum Ratings**

| Parameter                               | Min. | Max. | Unit |

|-----------------------------------------|------|------|------|

| V <sub>D</sub> or V <sub>S</sub> to GND | -0.3 | 40.0 | V    |

| Voltage at Logic Input pins             | -0.3 | 6.5  | V    |

| Current at input pin                    | -1.0 | 1.0  | mA   |

| Storage temperature range               | -65  | 150  | °C   |

| Junction temperature                    |      | 150  | °C   |

| ESD Human Body Model                    |      | 2000 | V    |

| ESD Machine Model                       |      | 200  | V    |

| Moisture Sensitivity Level              |      | 1    |      |

#### **Electrical Characteristics**

$T_A$  = -10 °C to 75 °C

| Parameter              | Description                  | Conditions                                     | Min. | Тур. | Max. | Unit |

|------------------------|------------------------------|------------------------------------------------|------|------|------|------|

| V <sub>CC</sub>        | Supply Voltage               |                                                | 11.5 | 12.0 | 12.5 | V    |

| T <sub>VCC_RAMP</sub>  | V <sub>CC</sub> Ramp-up Rate | See Note 1                                     | 0.25 |      |      | V/ms |

| -                      | Quiescent Current            | V <sub>G</sub> not ramping<br>FET = ON         |      | 50   | 80   | μА   |

| Iq                     | Quiescent Guirent            | V <sub>G</sub> not ramping<br>FET = OFF        |      | 0.1  | 1    | μА   |

| $V_{D}$                | FET Drain Voltage            |                                                | 1.0  |      | 21   | V    |

| $V_{GS}$               | Gate-Source Voltage          |                                                | 8.0  | 11.5 | 16   | V    |

| $C_{G}$                | FET Gate Capacitance         |                                                | 500  |      | 8000 | pF   |

| T <sub>DELAY</sub>     | Ramp Delay Range             | 1.5ms Default, 500μs step                      | 0    | 500  | 750  | μS   |

| T <sub>SLEW</sub>      | FET Turn on Slew Rate        |                                                | 1.2  | 2.0  | 2.8  | V/ms |

| I <sub>DISCHARGE</sub> | Internal Discharge Resistor  | Nominal discharge time of ~100ms 10mA max rate | 180  | 300  | 420  | Ω    |

| V <sub>IH</sub>        | HIGH-level input voltage     | ON (200mV Hysteresis)                          | 2.4  |      | 5.5  | V    |

| $V_{IL}$               | LOW-level Input voltage      | ON (200mV Hysteresis)                          |      |      | 0.4  | V    |

| V <sub>OH</sub>        | HIGH-level output voltage    | PG Open Drain                                  |      |      | 5.5  | V    |

| I <sub>OL_LOGIC</sub>  | Logic LOW level output       | PG Sink Current                                | 1    | 2    | 3    | mA   |

| I <sub>IH</sub> *      | HIGH-level input current     | V <sub>IH</sub> = 3.3V                         |      |      | <1.0 | μА   |

Notes:

<sup>1.</sup> If  $T_{VCC\_RAMP} > 5V/ms$  and ON is asserted, Gate charging will begin after 1ms.

#### **Device Operation**

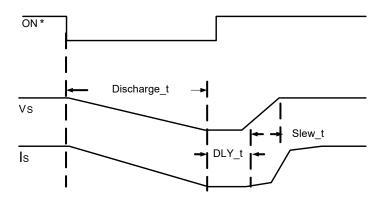

In a typical application, de-asserting ON (low) turns off the external power N-FET. When the FET is turned off, the voltage at the load is discharged through a resistor (300 Ohms) internal to the SLG55022. When ON is asserted (high), the device will not begin driving the gate of the external power FET unless the voltage at the drain of the device is at or above 0.8V (e.g.  $V_D \ge 0.8$ ) to prevent a 'shootthrough' situation to the FET's source load. Gate voltage is not applied to the gate of the external power N-FET after DLY\_t then the gate source (Vgs) voltage is ramped up to 11.5V above the source voltage  $V_S$  at a slew rate determined by the internal slew rate control element internal to the SLG55022. Monotonic rise of Vs is maintained even as ID increases dramatically after the load device turn on threshold voltage is reached. After the source voltage has ramped up to its maximum steady state value, the Open Drain PG (Power Good) signal is asserted. PG may be used as the ON control of a second SLG55022 thereby providing power on sequence control of a number of switched power rails, or used in a 'wired and' with other PG signals to indicate all switched power rails are in a power good condition.

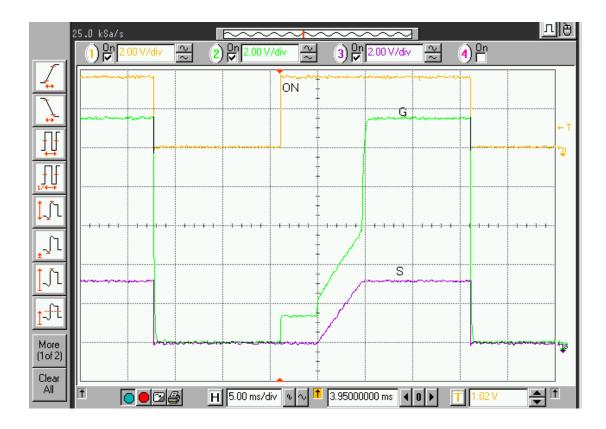

The waveforms shown illustrate the monotonic rise of the source voltage of a FET as gate voltage is controlled to accommodate for variations in load current as the voltage is applied.

#### **Delay Time and Slew Rates**

The two components of controlling the application of FET source voltage to the load are a fixed time delay before beginning turn on of the FET (DLY t below) and the Slew Time of the source voltage (Slew t below).

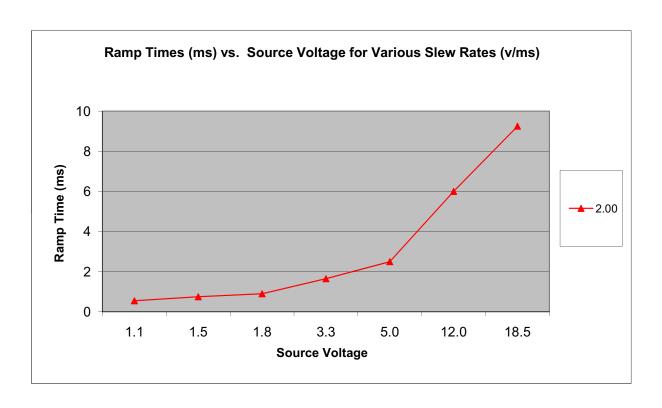

Having control over the Slew Rate of the FET's source voltage as the FET is turning on is important in controlling dv/dt caused transients. A power FET, for example, switching a 5V rail which has a total of  $500\mu\text{F}$  of decoupling, fully on in  $10\mu\text{s}$  will generate a 250A current surge which is very undesirable. If the FET turn on time can be stretched to 1ms, the current surge to charge the decoupling capacitors is reduced to 2.5A. The SLG55022 controls slew rate of a FET's source voltage as it is turned on. A range of slew rates are available as device order options. Obviously the time to fully slew the source voltage to fully on is a function of the drain supply voltage. The table and graph below shows source voltage ramp times for various slew rates supported by the SLG55022 for a range of specific source voltages.

| Slew Rates | Ramp Times (ms) vs. Source Voltages (V) |      |      |      |      |      |       |  |  |  |

|------------|-----------------------------------------|------|------|------|------|------|-------|--|--|--|

| (V/ms)     | 1.1V                                    | 1.5V | 1.8V | 3.3V | 5.0V | 12V  | 18.5V |  |  |  |

| 2.00       | 0.55                                    | 0.75 | 0.90 | 1.65 | 2.50 | 6.00 | 9.25  |  |  |  |

<sup>\*</sup> The minimum time that ON can be de-asserted between switching cycles is 100ms.

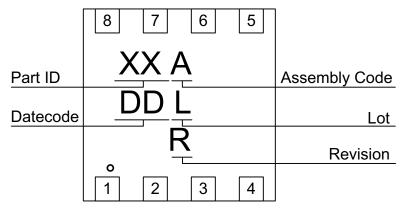

#### **Package Top Marking System Definition**

XX - Part ID Field: identifies the specific device configuration

A — Assembly Code Field: Assembly Location of the device.

DD - Date Code Field: Coded date of manufacture

L - Lot Code: Designates Lot #

R - Revision Code: Device Revision

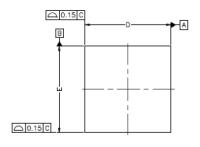

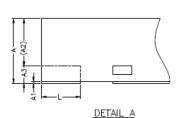

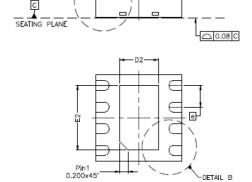

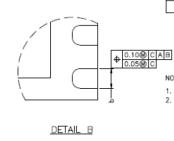

#### **Package Drawing and Dimensions**

#### 8 Lead TDFN Package

// 0.10 C

|        | Г    | DIMENSION | M    |       | DIMENSION | V    |  |

|--------|------|-----------|------|-------|-----------|------|--|

| SYMBOL |      | (MM)      |      | (MIL) |           |      |  |

|        | MIN. | NOM.      | MAX. | MIN.  | NOM.      | MAX. |  |

| Α      | 0.70 | 0.75      | 0.80 | 28    | 30        | 31   |  |

| A1     | 0.00 | 0.02      | 0.05 | 0     | 1         | 2    |  |

| A2     | 0    | 0.55      | 0.80 | 0     | 22        | 31   |  |

| A3     | _    | 0.20      | -    | _     | 8         | _    |  |

| b      | 0.18 | 0.25      | 0.30 | 7     | 10        | 12   |  |

| D      | 1.90 | 2.00      | 2.10 | 74    | 79        | 83   |  |

| D1     |      | _         |      | _     |           |      |  |

| D2     | 0.75 | 0.90      | 1.05 | 30    | 35        | 41   |  |

| Е      | 1.90 | 2.00      | 2.10 | 75    | 79        | 83   |  |

| E1     |      | _         |      |       | _         |      |  |

| E2     | 1.50 | 1.65      | 1.70 | 53    | 59        | 65   |  |

| е      | (    | 0.50 BSC  | ;    |       | 20 BSC    |      |  |

| L      | 0.25 | 0.30      | 0.35 | 10    | 12        | 14   |  |

- 1. REFER TO JEDEC STD: MO-229.

2. DIMENSION "b" APPLIES TO METALLIZED TERMINAL AND IS MEASURED BETWEEN 0.15MM AND 0.30MM FROM THE TERMINAL TIP. IF THE TERMINAL HAS OPTIONAL RADIUS ON THE OTHER END OF THE TERMINAL, THE DIMENSION B SHOULD NOT BE MEASURED IN THAT RADIUS AREA.

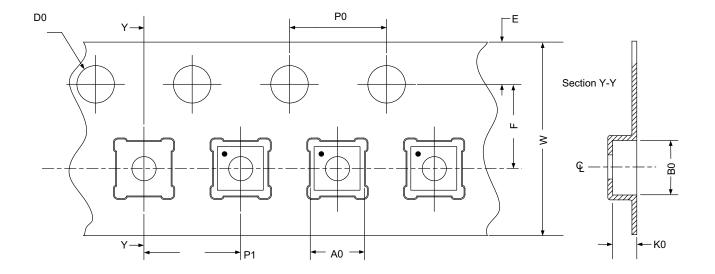

#### **Tape and Reel Specifications**

| Dookogo          | #            | Nominal           | Max Units |         | Reel &        | Leader (min) |                | Trailer (min) |                | Tape          | Part          |

|------------------|--------------|-------------------|-----------|---------|---------------|--------------|----------------|---------------|----------------|---------------|---------------|

| Package<br>Type  | # of<br>Pins | Package Size [mm] | per Reel  | per Box | Hub Size [mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| TDFN 8L<br>Green | 8            | 2 x 2 x 0.75      | 3,000     | 3,000   | 178 / 60      | 100          | 400            | 100           | 400            | 8             | 4             |

#### **Carrier Tape Drawing and Dimensions**

| Package<br>Type  | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge |     | Tape Width |

|------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----|------------|

|                  | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F   | W          |

| TDFN 8L<br>Green | 2.3                 | 2.3                | 1.05            | 4                   | 4               | 1.55                   | 1.75                          | 3.5 | 8          |

#### **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 3.00 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

#### **Revision History**

| Date      | Version | Change                                                  |

|-----------|---------|---------------------------------------------------------|

| 7/10/2018 | 1.03    | Updated style and formatting                            |

| 7/29/2017 | 1.02    | Added Pb-Free/Halogen Free/RoHS compliance<br>Added MSL |