# An Ultra-small, 4 m $\Omega$ , 2 A Integrated Power Switch with Multiple Protection Features

#### **General Description**

Operating from a 2.5 V to 5.5 V power supply and fully specified over the -40 °C to 85 °C temperature range, the SLG59M1710V is a high-performance 4 m $\Omega$ , 2 A single-channel nFET integrated power switch with adjustable inrush current control which is achieved by adjusting the V<sub>OUT</sub> slew rate with an external capacitor. Using a proprietary MOSFET design, the SLG59M1710V achieves a stable 4 m $\Omega$  RDSON across a wide input/supply voltage range. Incorporating two-stage current protection as well as thermal protection, the SLG59M1710V is designed for all 0.8 V to 5.5V power rail applications. Using Silego's proprietary CuFET<sup>TM</sup> technology for high-current operation, the SLG59M1710V is packaged in a space-efficient, low thermal resistance, RoHS-compliant 1.6 mm x 2.5 mm STQFN package

#### **Features**

- Low Typical RDS<sub>ON</sub> nFET: 4 mΩ

- · Maximum Continuous Switch Current: Up to 2 A

- Supply Voltage: 2.5 V ≤ V<sub>DD</sub> ≤ 5.5 V

- Wide Input Voltage Range: 0.8 V ≤ V<sub>IN</sub> ≤ V<sub>DD</sub>

- · Capacitor-adjustable Start-up and Inrush Current Control

- · Two-stage Overcurrent Protection:

- · Fixed threshold, 4 A Active Current Limit

- · Fixed 0.5 A Short-circuit Current Limit

- Operating Temperature: -40 °C to 85 °C

- Low  $\theta_{JA}$ , 16-pin 1.6 mm x 2.5 mm STQFN Packaging

- · Pb-Free / Halogen-Free / RoHS compliant

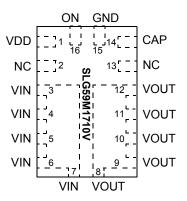

### **Pin Configuration**

**16-pin FC-STQFN** (Top View)

#### **Applications**

- · Notebook Power Rail Switching

- · Tablet Power Rail Switching

- · Smartphone Power Rail Switching

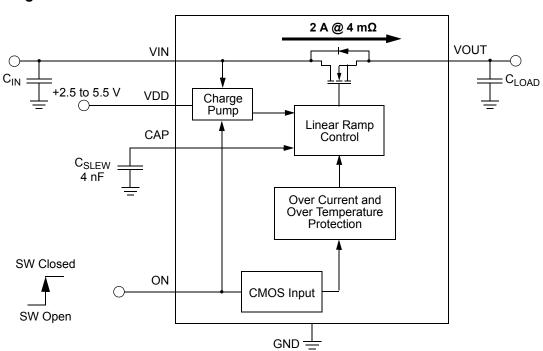

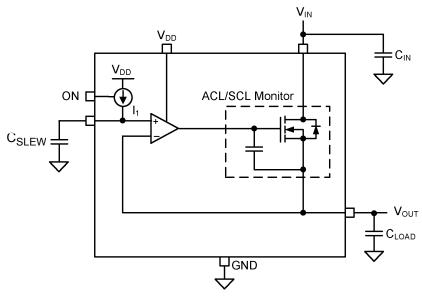

#### **Block Diagram**

## **Pin Description**

| Pin# | Pin Name | Туре   | Pin Description                                                                                                                                                                                                                                                                                                                                                                                              |

|------|----------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1    | VDD      | Power  | With an internal 1.9 V UVLO threshold, VDD supplies the power for the operation of the power switch and internal control circuitry where its range is 2.5 V $\leq$ V <sub>DD</sub> $\leq$ 5.5 V. Bypass the VDD pin to GND with a 0.1 $\mu$ F (or larger) capacitor                                                                                                                                          |

| 2    | NC       | NC     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                   |

| 3-7  | VIN      | MOSFET | Drain terminal of Power MOSFET (Pins 3-7 fused together). Connect a 10 $\mu$ F (or larger) low ESR capacitor from this pin to GND. Capacitors used at VIN should be rated at 10 V or higher.                                                                                                                                                                                                                 |

| 8-12 | VOUT     | MOSFET | Source terminal of Power MOSFET (Pins 8-12 fused together) Connect a low ESR capacitor (up to 500 $\mu$ F) from this pin to GND. Capacitors used at VOUT should be rated at 10 V or higher.                                                                                                                                                                                                                  |

| 13   | NC       | NC     | No Connect                                                                                                                                                                                                                                                                                                                                                                                                   |

| 14   | CAP      | Input  | A low-ESR, stable dielectric, ceramic surface-mount capacitor connected from CAP pin to GND sets the V <sub>OUT</sub> slew rate and overall turn-on time of the SLG59M1710V. For best performance, the range for C <sub>SLEW</sub> values are 2 nF $\leq$ C <sub>SLEW</sub> $\leq$ 22 nF. Capacitors used at the CAP pin should be rated at 10 V or higher.                                                  |

| 15   | GND      | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                       |

| 16   | ON       | Input  | A low-to-high transition on this pin closes the power switch. ON is an asserted-HIGH, level-sensitive CMOS input with V $_{IL}$ < 0.3 V and V $_{IH}$ > 0.85 V. Connect this pin to the output of a general-purpose output (GPO) from a microcontroller or other application processor. While there is an internal pull down circuit to ground (~4 M $\Omega$ ), do not allow this pin to be open-circuited. |

## **Ordering Information**

| Part Number   | Туре                      | Production Flow             |

|---------------|---------------------------|-----------------------------|

| SLG59M1710V   | STQFN 16L                 | Industrial, -40 °C to 85 °C |

| SLG59M1710VTR | STQFN 16L (Tape and Reel) | Industrial, -40 °C to 85 °C |

000-0059M1710-100 Page 2 of 18

## **Absolute Maximum Ratings**

| Parameter                | Description                                        | Conditions                                                                                                                   | Min. | Тур. | Max.            | Unit |

|--------------------------|----------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------|------|------|-----------------|------|

| $V_{DD}$                 | Power Supply Pin to GND                            |                                                                                                                              |      | -    | 6               | V    |

| V <sub>IN</sub> to GND   | Power Switch Input Voltage to GND                  |                                                                                                                              | -0.3 |      | 6               | V    |

| V <sub>OUT</sub> to GND  | Power Switch Output Voltage to GND                 |                                                                                                                              | -0.3 |      | V <sub>IN</sub> | V    |

| ON, CAP to<br>GND        | ON and CAP Pin Voltages to GND                     |                                                                                                                              | -0.3 |      | 6               | V    |

| T <sub>S</sub>           | Storage Temperature                                |                                                                                                                              | -65  |      | 150             | °C   |

| ESD <sub>HBM</sub>       | ESD Protection                                     | Human Body Model                                                                                                             | 2000 | -    |                 | V    |

| ESD <sub>CDM</sub>       | ESD Protection                                     | Charged Device Model                                                                                                         | 500  |      |                 | V    |

| MSL                      | Moisture Sensitivity Level                         |                                                                                                                              |      | •    | 1               |      |

| $\theta_{JA}$            | Package Thermal Resistance,<br>Junction-to-Ambient | 1.6 x 2.5 mm 16L STQFN; Determined using 1 in <sup>2</sup> , 1.2 oz. copper pads under each VIN and VOUT on FR4 pcb material |      | 35   |                 | °C/W |

| W <sub>DIS</sub>         | Package Power Dissipation                          |                                                                                                                              |      |      | 1.2             | W    |

| IDS <sub>MAX</sub>       | Max Continuous Switch Current                      |                                                                                                                              |      |      | 2               | Α    |

| MOSFET IDS <sub>PK</sub> | Peak Current from Drain to Source                  | Maximum pulsed switch current, pulse width < 1 ms, 1% duty cycle                                                             |      |      | 3               | Α    |

Note: Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions above those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect reliability.

#### **Electrical Characteristics**

$T_A = -40 \, ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  (unless otherwise stated)

| Parameter            | Description                                      | Conditions                                                                              | Min. | Тур. | Max.     | Unit |

|----------------------|--------------------------------------------------|-----------------------------------------------------------------------------------------|------|------|----------|------|

| $V_{DD}$             | Power Supply Voltage                             |                                                                                         | 2.5  |      | 5.5      | V    |

| V                    | V <sub>DD</sub> Undervoltage Lockout             | V <sub>DD</sub> ↑                                                                       | 1.6  | 1.9  | 2.2      | V    |

| $V_{DD(UVLO)}$       | Threshold                                        | $V_{DD} \downarrow$                                                                     | 1.5  | 1.8  | 2.2      | V    |

|                      | Power Supply Current when OFF                    | V <sub>DD</sub> = V <sub>IN</sub> = 5.5 V; ON = 0                                       |      | 1    | 2        | μA   |

| I <sub>DD</sub>      | Power Supply Current,<br>ON (Steady State)       | V <sub>DD</sub> = V <sub>IN</sub> = ON = 5.5 V; No Load                                 |      | 120  | 170      | μΑ   |

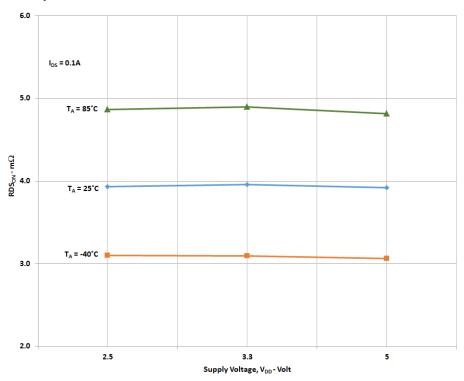

| DDO                  | ON Resistance                                    | V <sub>DD</sub> = V <sub>IN</sub> = 5 V;<br>T <sub>A</sub> 25°C MOSFET @100 mA          |      | 4    | 5.5      | mΩ   |

| RDS <sub>ON</sub>    | ON Resistance                                    | V <sub>DD</sub> = V <sub>IN</sub> = 5 V;<br>T <sub>A</sub> 85°C MOSFET @100 mA          |      | 5    | 6.8      | mΩ   |

| MOSFET<br>IDS        | Current from V <sub>IN</sub> to V <sub>OUT</sub> | Continuous                                                                              |      |      | 2        | Α    |

| I <sub>FET_OFF</sub> | MOSFET OFF Leakage Current                       | $V_{DD} = V_{IN} = 5.5 \text{ V};$<br>$V_{OUT} = 0 \text{ V}; \text{ ON} = 0 \text{ V}$ |      |      | 2        | μΑ   |

| V <sub>IN</sub>      | Drain Voltage                                    |                                                                                         | 0.8  |      | $V_{DD}$ | V    |

| 1                    | Active Current Limit, I <sub>ACL</sub>           | V <sub>OUT</sub> > 0.3 V                                                                | 3    | 4    | 5        | Α    |

| I <sub>LIMIT</sub>   | Short-circuit Current Limit, I <sub>SCL</sub>    | V <sub>OUT</sub> < 0.3 V                                                                |      | 0.5  |          | Α    |

000-0059M1710-100 Page 3 of 18

#### **Electrical Characteristics** (continued)

$T_A = -40 \, ^{\circ}\text{C}$  to 85  $^{\circ}\text{C}$  (unless otherwise stated)

| Parameter              | Description                          | Conditions                                                                                                                      | Min.   | Тур.       | Max.                | Unit |

|------------------------|--------------------------------------|---------------------------------------------------------------------------------------------------------------------------------|--------|------------|---------------------|------|

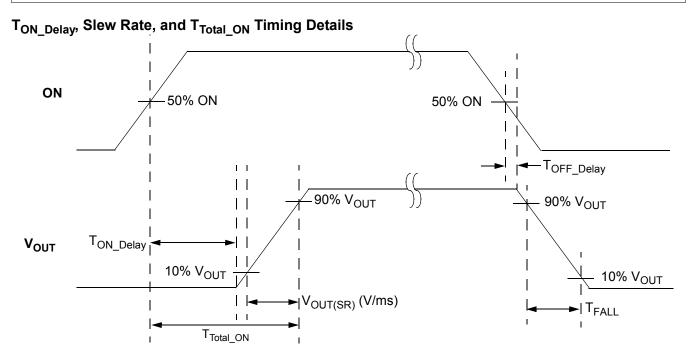

| T <sub>ON_Delay</sub>  | ON pin Delay Time                    | 50% ON to $V_{OUT}$ Ramp Start $V_{DD}$ = $V_{IN}$ = 5 V; $C_{SLEW}$ = 4 nF; $R_{LOAD}$ = 20 $\Omega$ , $C_{LOAD}$ = 10 $\mu$ F |        | 200        |                     | μs   |

|                        |                                      | 10% V <sub>OUT</sub> to 90% V <sub>OUT</sub> ↑                                                                                  | Set by | External ( | C <sub>SLEW</sub> 1 | V/ms |

| V <sub>OUT(SR)</sub>   | V <sub>OUT</sub> Slew Rate           | Example: $C_{SLEW}$ = 4 nF;<br>$V_{DD}$ = $V_{IN}$ = 5 V; $R_{LOAD}$ = 20 $\Omega$ ,<br>$C_{LOAD}$ = 10 $\mu$ F                 | 2.5    | 2.9        | 3.5                 | V/ms |

|                        |                                      | 50% ON to 90% V <sub>OUT</sub> ↑                                                                                                | Set by | External ( | SLEW <sup>1</sup>   | ms   |

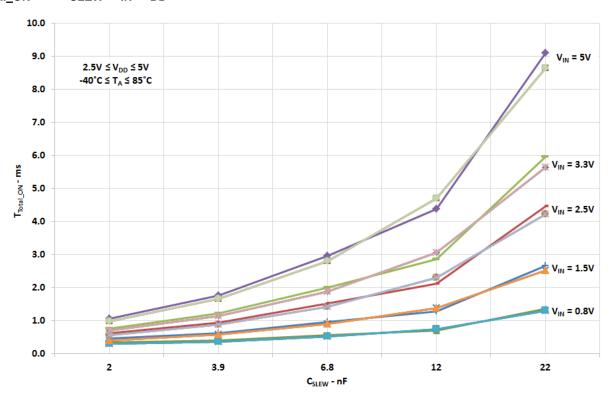

| T <sub>Total_ON</sub>  | Total Turn-on Time                   | Example: $C_{SLEW}$ = 4 nF;<br>$V_{DD}$ = $V_{IN}$ = 5 V; $R_{LOAD}$ = 20 $\Omega$ ,<br>$C_{LOAD}$ = 10 $\mu$ F                 | 1.4    | 1.7        | 2                   | ms   |

| T <sub>OFF_Delay</sub> | OFF Delay Time                       | 50% ON to $V_{OUT}$ Fall Start;<br>$V_{DD} = V_{IN} = 5 \text{ V}$ ;<br>$R_{LOAD} = 20 \Omega$ , no $C_{LOAD}$                  |        | 8          | 15                  | μs   |

| C <sub>LOAD</sub>      | Output Load Capacitance              | C <sub>LOAD</sub> connected from VOUT to GND                                                                                    |        |            | 500                 | μF   |

| ON_V <sub>IH</sub>     | High Input Voltage on ON pin         |                                                                                                                                 | 0.85   |            | V <sub>DD</sub>     | V    |

| ON_V <sub>IL</sub>     | Low Input Voltage on ON pin          |                                                                                                                                 | -0.3   | 0          | 0.3                 | V    |

| I <sub>ON(LKG)</sub>   | ON Pin Leakage Current               | ON = ON_V <sub>IH</sub> or ON = GND                                                                                             |        | 1.5        |                     | μΑ   |

| THERMON                | Thermal shutoff turn-on temperature  |                                                                                                                                 |        | 125        |                     | °C   |

| THERMOFF               | Thermal shutoff turn-off temperature |                                                                                                                                 |        | 100        |                     | °C   |

Notes:

1. Refer to typical Timing Parameter vs. C<sub>SLEW</sub> performance charts for additional information when available.

000-0059M1710-100 Page 4 of 18

### **Typical Performance Characteristics**

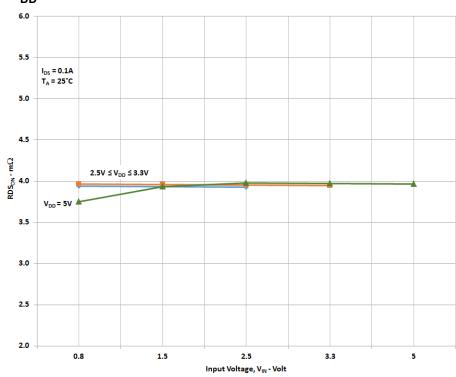

## $\ensuremath{\mathsf{RDS_{ON}}}\xspace$ vs. $\ensuremath{V_{DD}}\xspace$ and Temperature

## $\ensuremath{\mathsf{RDS}_\mathsf{ON}}$ vs. $\ensuremath{\mathsf{V_{IN}}}$ and $\ensuremath{\mathsf{V_{DD}}}$

000-0059M1710-100 Page 5 of 18

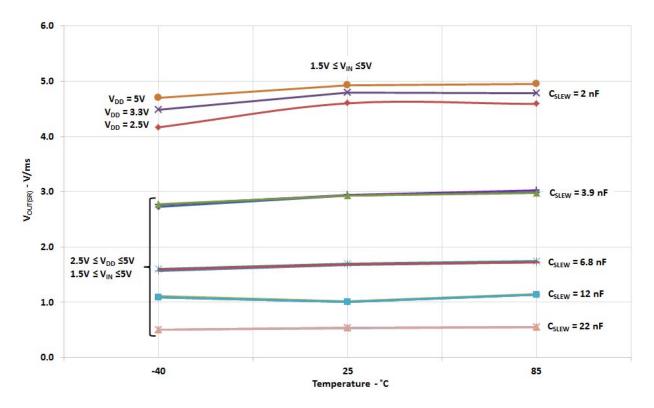

## $\rm V_{OUT}$ Slew Rate vs. Temperature, $\rm V_{DD}, \, \rm V_{IN}, \, and \, \rm C_{SLEW}$

$\rm T_{Total\_ON}$  vs.  $\rm C_{SLEW}, \, \rm V_{IN}, \, \rm V_{DD}, \, and \, \rm Temperature$

000-0059M1710-100 Page 6 of 18

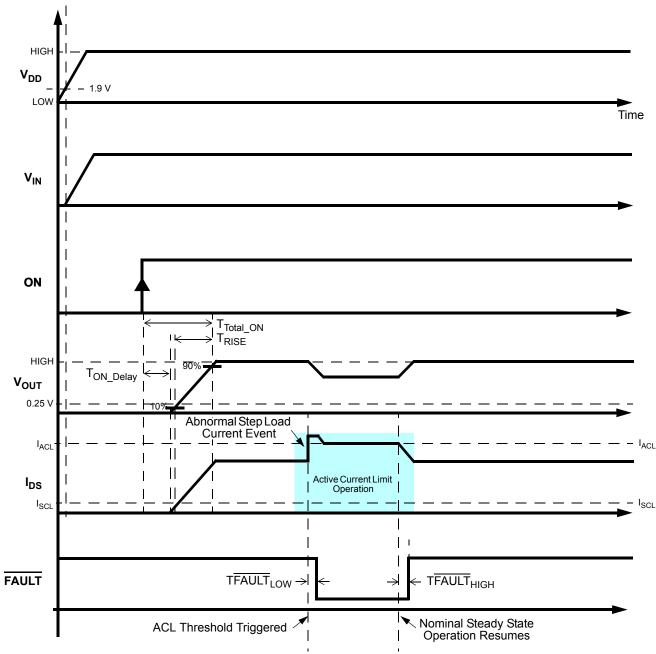

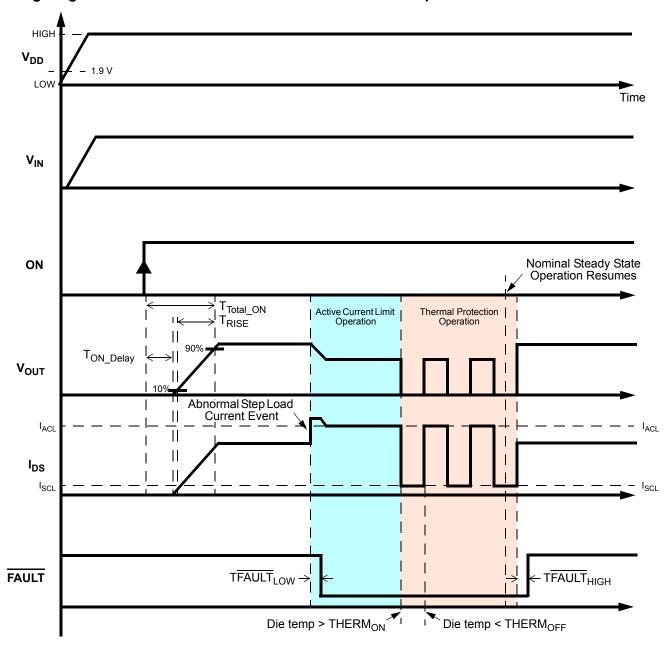

### **Timing Diagram - Basic Operation including Active Current Limit Protection**

000-0059M1710-100 Page 7 of 18

### **Timing Diagram - Active Current Limit & Thermal Protection Operation**

000-0059M1710-100 Page 8 of 18

#### SLG59M1710V Power-Up/Power-Down Sequence Considerations

To ensure glitch-free power-up under all conditions, apply  $V_{DD}$  first, followed by  $V_{IN}$  after  $V_{DD}$  exceeds 1.9 V. Then allow  $V_{IN}$  to reach 90% of its max value before toggling the ON pin from Low-to-High. Likewise, power-down in reverse order.

If  $V_{DD}$  and  $V_{IN}$  need to be powered up simultaneously, glitching can be minimized by having a suitable load capacitor. A 10  $\mu$ F  $C_{LOAD}$  will prevent glitches for rise times of  $V_{DD}$  and  $V_{IN}$  less than 2 ms.

If the ON pin is toggled HIGH before  $V_{DD}$  and  $V_{IN}$  have reached their steady-state values, the IPS timing parameters may differ from datasheet specifications.

The slew rate of output V<sub>OUT</sub> follows a linear ramp set by a capacitor connected to the CAP pin. A larger capacitor value at the CAP pin produces a slower ramp, reducing inrush current from capacitive loads.

#### SLG59M1710V Current Limiting Operation

The SLG59M1710V has two types of current limiting triggered by the output V<sub>OUT</sub> voltage.

#### 1. Standard Current Limiting Mode (with Thermal Shutdown Protection)

When the  $V_{OUT}$  voltage > 300 mV, the output current is initially limited to the Active Current Limit ( $I_{ACL}$ ) specification listed in the Electrical Characteristics table. The ACL monitor's response time is very fast and is triggered within a few microseconds to sudden (transient) changes in load current. When a load current overload is detected, the ACL monitor increases the FET resistance to keep the current from exceeding the power switch's  $I_{ACL}$  threshold. During active current-limit operation,  $V_{OUT}$  is also reduced by  $I_{ACL}$  x RDSON<sub>ACL</sub>. This observed behavior is illustrated in the timing diagrams on Pages 7 and 8.

However, if a load-current overload condition persists where the die temperature rises because of the increased FET resistance, the power switch's internal Thermal Shutdown Protection circuit can be activated. If the die temperature exceeds the listed THERM<sub>ON</sub> specification, the FET is shut OFF completely, thereby allowing the die to cool. When the die cools to the listed THERM<sub>OFF</sub> temperature threshold, the FET is allowed to turn back on. This process may repeat as long as the output current overload condition persists.

#### 2. Short Circuit Current Limiting Mode (with Thermal Shutdown Protection)

When the  $V_{OUT}$  voltage < 300 mV (which is the case with a hard short, such as a solder bridge on the power rail), the power switch's internal Short-circuit Current Limit (SCL) monitor limits the FET current to approximately 500 mA (the  $I_{SCL}$  threshold). While the internal Thermal Shutdown Protection circuit remains enabled and since the  $I_{SCL}$  threshold is much lower than the  $I_{ACL}$  threshold, thermal shutdown protection may become activated only at higher ambient temperatures.

#### SLG59M1710V Start-up Inrush Current Considerations with Capacitive Loads

In distributed power applications, the SLG59M1710V is generally implemented on the outboard or downstream side of switching regulator dc/dc converters with internal overcurrent protection. As an adjustable output voltage slew-rate, integrated power switch, it is important to understand the start-up operation of the SLG59M1710V with capacitive loads. An equivalent circuit of the SLG59M1710V's slew-rate control loop with capacitors at its VIN and VOUT pins is shown in Figure 1:

000-0059M1710-100 Page 9 of 18

#### SLG59M1710V Start-up Inrush Current Considerations with Capacitive Loads (continued)

Figure 1. SLG59M1710V's Equivalent Slew-rate Control Loop Circuit.

For a desired  $V_{OUT}$  slew-rate  $(V_{OUT(SR)})$ , a corresponding  $C_{SLEW}$  value is selected. At the VOUT pin and with ON = LOW, the internal FET is OFF,  $V_{OUT}$  is initially at 0V, and there is no stored charge on  $C_{LOAD}$ . When a low-to-high transition is applied to the IC's ON pin, an internal current source (I<sub>1</sub>) is enabled which, in turn, charges the external slew-rate capacitor,  $C_{SLEW}$ . The SLG59M1710V's internal micropower op amp sets the circuit's  $V_{OUT(SR)}$  based on the slew rate of the nodal voltage at its non-inverting pin (the voltage at the CAP pin).

As a function of  $V_{OUT(SR)}$  and  $C_{LOAD}$ , a 1st-order expression for the circuit's FET current (and inrush current) when a low-to-high transition on the ON pin is applied becomes:

From the expression above and for a given  $V_{OUT(SR)}$ ,  $C_{LOAD}$  determines the magnitude of the inrush current; that is, for large values of  $C_{LOAD}$ , large inrush currents can result. If the inrush currents are large enough to trigger the overcurrent protection of an upstream dc/dc converter, the system can be shut down.

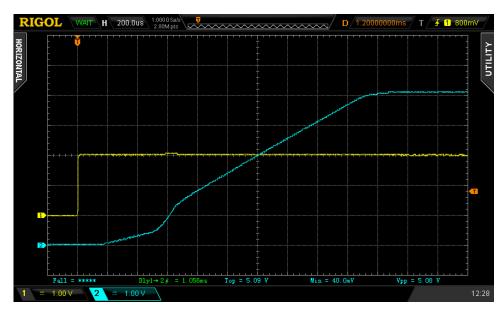

In applications where the desired  $V_{OUT(SR)}$  is fast and  $C_{LOAD}$  is very large (>200  $\mu$ F), there is a secondary effect on the observed  $V_{OUT(SR)}$  attributed to the SLG59M1710V's internal short-circuit current limit monitor (its SCL monitor). If the resultant inrush current is larger than the IC's  $I_{SCL}$  threshold, the SCL current monitor limits the inrush current and the current to charge  $C_{LOAD}$  until the  $I_{SCL}$  OFF threshold is crossed (~0.3V). During the time the SCL monitor's been activated, the inrush current profile may exhibit an observable reduction in  $V_{OUT(SR)}$  as shown in Figure 2 where  $C_{SLEW}$  was set to 4nF and 470  $\mu$ F was chosen for  $C_{LOAD}$ .

000-0059M1710-100 Page 10 of 18

#### SLG59M1710V Start-up Inrush Current Considerations with Capacitive Loads (continued)

Figure 2. A SLG59M1710V with  $C_{SLEW}$  set to 4nF and 470 $\mu$ F for  $C_{LOAD}$ .  $C_{LOAD}$ -to- $C_{SLEW}$  ratio is greater than 33,600. Note that the internal SCL monitor's been triggered and  $V_{OUT(SR)}$  is reduced until  $V_{OUT}$  reaches ~0.3V.

A closer analysis of the IC's internal slew-control large-scale yields the following:

$$\frac{I_{SCL}}{C_{LOAD}} = M_{SR} \times \frac{I_1}{C_{SLEW}}$$

where

I<sub>SCL</sub> = IC's short-circuit current limit threshold, typically 0.5A;

$M_{SR}$  = An internal slew-rate multiplier from the IC's CAP pin to the VOUT pin;

$I_1$  = An internal current source to charge the external capacitor ( $C_{SIFW}$ ).

Rearranging the equation to isolate both  $C_{LOAD}$  and  $C_{SLEW}$  yields the following:

$$\frac{C_{LOAD}}{C_{SLEW}} = \frac{I_{SCL}}{I_1 \times M_{SR}}$$

For the SLG59M1710V device, the right-hand side of the expression is approximately 33,600 after taking into account part-to-part variations because of process, voltage, and temperature.

Referring to the configuration of Figure 2's scope capture, the  $C_{LOAD}$ -to- $C_{SLEW}$  ratio is 117,500 (470 $\mu$ F/4nF) where it is evident that the SCL monitor circuit is charging  $C_{LOAD}$  shortly after a low-to-high ON transition. If it is desired to avoid a reduction in  $V_{OUT(SR)}$ , the choices are decreasing  $C_{LOAD}$  and/or increasing  $C_{SLEW}$  so that the ratio is always less than 33,600 including taking into account external capacitor tolerances for initial accuracy and temperature.

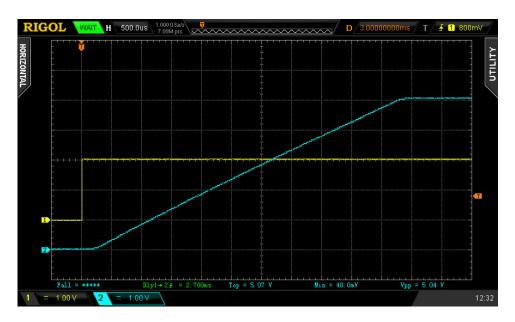

As shown in Figure 3, it was chosen to reduce  $V_{OUT(SR)}$  by increasing  $C_{SLEW}$  to 15nF while keeping  $C_{LOAD}$  at 470 $\mu$ F. With this configuration, the ratio of  $C_{LOAD}$  to  $C_{SLEW}$  is about 31,333 (smaller than 33,600). Upon a low-to-high transition on the ON pin, the  $V_{OUT}$  increases smoothly with no evidence of SCL monitor's interaction.

000-0059M1710-100 Page 11 of 18

#### SLG59M1710V Start-up Inrush Current Considerations with Capacitive Loads (continued)

Figure 3. A SLG59M1710V with  $C_{SLEW}$  set to 15nF and 470 $\mu$ F retained for  $C_{LOAD}$ .  $C_{LOAD}$ -to- $C_{SLEW}$  ratio is smaller than 33,600. Note smooth  $V_{OUT}$  transition.

#### **Power Dissipation**

The junction temperature of the SLG59M1710V depends on different factors such as board layout, ambient temperature, and other environmental factors. The primary contributor to the increase in the junction temperature of the SLG59M1710V is the power dissipation of its power MOSFET. Its power dissipation and the junction temperature in nominal operating mode can be calculated using the following equations:

$$PD = RDS_{ON} \times I_{DS}^{2}$$

where:

PD = Power dissipation, in Watts (W) RDS<sub>ON</sub> = Power MOSFET ON resistance, in Ohms ( $\Omega$ ) I<sub>DS</sub> = Output current, in Amps (A)

and

$$T_J = PD \times \theta_{JA} + T_A$$

where:

T<sub>J</sub> = Junction temperature, in Celsius degrees (°C)

θ<sub>JA</sub> = Package thermal resistance, in Celsius degrees per Watt (°C/W)

T<sub>A</sub> = Ambient temperature, in Celsius degrees (°C)

000-0059M1710-100 Page 12 of 18

#### **Power Dissipation (continued)**

During active current-limit operation, the SLG59M1710V's power dissipation can be calculated by taking into account the voltage drop across the power switch  $(V_{IN}-V_{OUT})$  and the magnitude of the output current in active current-limit operation  $(I_{ACL})$ :

$$PD = (V_{IN} - V_{OUT}) \times I_{ACL} \text{ or}$$

$$PD = (V_{IN} - (R_{LOAD} \times I_{ACL})) \times I_{ACL}$$

#### where:

PD = Power dissipation, in Watts (W)  $V_{IN}$  = Input Voltage, in Volts (V)  $R_{LOAD}$  = Load Resistance, in Ohms ( $\Omega$ )  $I_{ACL}$  = Output limited current, in Amps (A)  $V_{OUT}$  =  $R_{LOAD}$  x  $I_{ACL}$

For more information on Silego GreenFET3 integrated power switch features, please visit our <u>Application Notes</u> page at our website and see <u>App Note "AN-1068 GreenFET3 Integrated Power Switch Basics"</u>.

000-0059M1710-100 Page 13 of 18

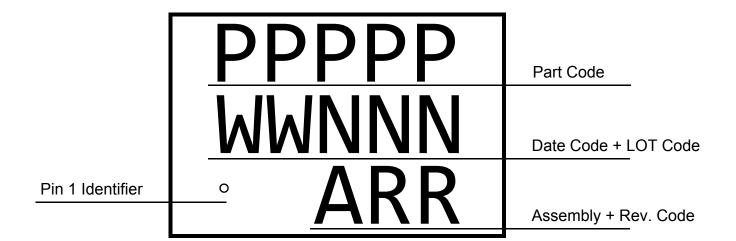

### **Package Top Marking System Definition**

PPPPP - Part ID Field WW - Date Code Field<sup>1</sup> NNN - Lot Traceability Code Field<sup>1</sup> A - Assembly Site Code Field<sup>2</sup> RR - Part Revision Code Field<sup>2</sup>

Note 1: Each character in code field can be alphanumeric A-Z and 0-9

Note 2: Character in code field can be alphabetic A-Z

000-0059M1710-100 Page 14 of 18

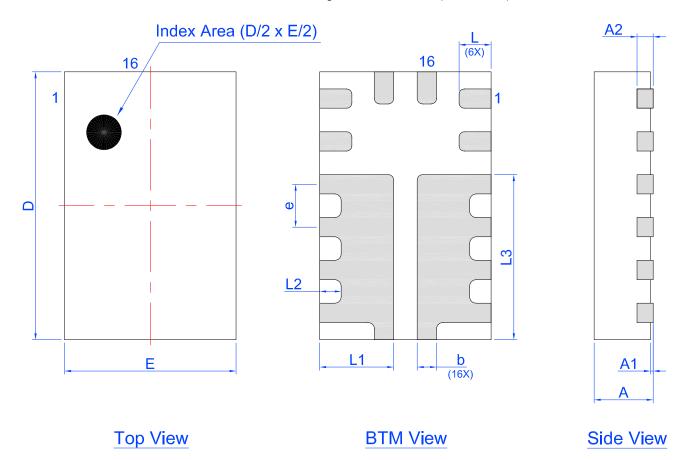

## **Package Drawing and Dimensions**

16 Lead STQFN Package 1.6 mm x 2.5 mm (Fused Lead)

## Unit: mm

| Symbol | Min   | Nom.     | Max  | Symbol | Min  | Nom. | Max  |

|--------|-------|----------|------|--------|------|------|------|

| Α      | 0.50  | 0.55     | 0.60 | D      | 2.45 | 2.50 | 2.55 |

| A1     | 0.005 | -        | 0.05 | Е      | 1.55 | 1.60 | 1.65 |

| A2     | 0.10  | 0.15     | 0.20 | L      | 0.25 | 0.30 | 0.35 |

| b      | 0.13  | 0.18     | 0.23 | L1     | 0.64 | 0.69 | 0.74 |

| е      | (     | 0.40 BSC | ,    | L2     | 0.15 | 0.20 | 0.25 |

|        |       |          |      | L3     | 1.49 | 1.54 | 1.59 |

000-0059M1710-100 Page 15 of 18

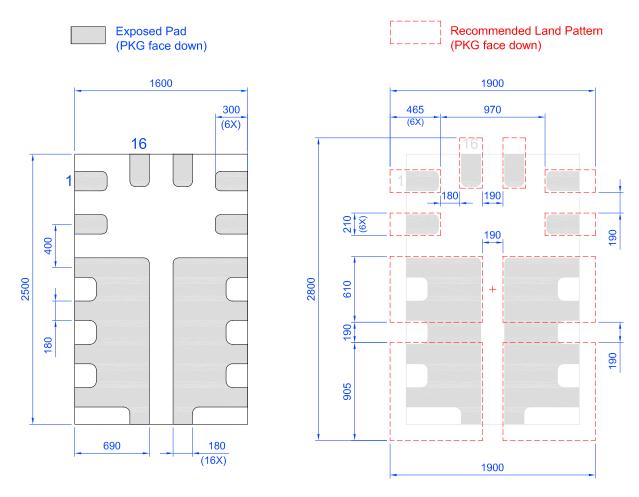

## SLG59M1710V 16-pin STQFN PCB Landing Pattern

Unit: um

000-0059M1710-100 Page 16 of 18

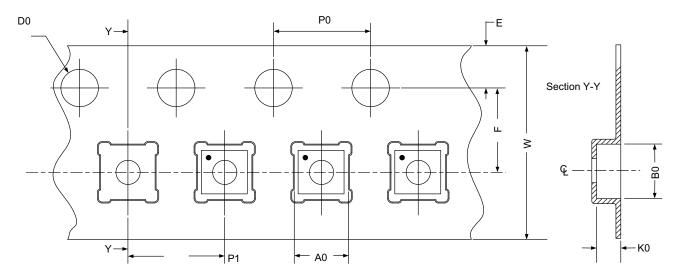

### **Tape and Reel Specifications**

| Dookogo                                        | # of         | Nominal              | Nominal Max Units |         | Reel &           | Leader (min) |                | Trailer (min) |                | Таре          | Part          |

|------------------------------------------------|--------------|----------------------|-------------------|---------|------------------|--------------|----------------|---------------|----------------|---------------|---------------|

| Package<br>Type                                | # OI<br>Pins | Package Size<br>[mm] | per Reel          | per Box | Hub Size<br>[mm] | Pockets      | Length<br>[mm] | Pockets       | Length<br>[mm] | Width<br>[mm] | Pitch<br>[mm] |

| STQFN<br>16L<br>1.6x2.5mm<br>0.4P FCA<br>Green | 16           | 1.6x2.5x<br>0.55mm   | 3000              | 3000    | 178/60           | 100          | 400            | 100           | 400            | 8             | 4             |

## **Carrier Tape Drawing and Dimensions**

| Package<br>Type                             | PocketBTM<br>Length | PocketBTM<br>Width | Pocket<br>Depth | Index Hole<br>Pitch | Pocket<br>Pitch | Index Hole<br>Diameter | Index Hole<br>to Tape<br>Edge |     | Tape Width |

|---------------------------------------------|---------------------|--------------------|-----------------|---------------------|-----------------|------------------------|-------------------------------|-----|------------|

|                                             | A0                  | В0                 | K0              | P0                  | P1              | D0                     | E                             | F   | W          |

| STQFN 16L<br>1.6x2.5mm<br>0.4P FCA<br>Green |                     | 2.8                | 0.7             | 4                   | 4               | 1.55                   | 1.75                          | 3.5 | 8          |

Refer to EIA-481 specification

## **Recommended Reflow Soldering Profile**

Please see IPC/JEDEC J-STD-020: latest revision for reflow profile based on package volume of 2.2 mm<sup>3</sup> (nominal). More information can be found at www.jedec.org.

000-0059M1710-100 Page 17 of 18

## **Revision History**

| Date      | Version | Change             |

|-----------|---------|--------------------|

| 2/23/2017 | 1.00    | Production Release |

000-0059M1710-100 Page 18 of 18