# SHANGHAI SEMITECH SEMICONDUCTOR CO., LTD

#### **SLVU2.8-8**

## **Utralow Capacitance Transient Voltage Suppressors Array**

#### **General Description**

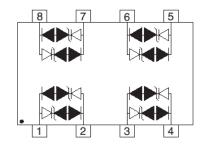

The SLVU2.8-8 is in an SOP-8 package and may be used to protect four high-speed line pairs. The "flow-thru" design minimizes trace inductance and reduces voltage overshoot associated with ESD events. The low clamping voltage of the SLVU2.8-8 minimizes the stress on the protected IC.

### **Applications**

- Ethernet 10/100/1000 Base T

- WAN/LAN Equipment

- Desktops,Servers,Notebooks & Handhelds,base stations Laser Diode Protection

#### **Features**

- 400 W Peak Pulse Power per Line (tp=8/20μs)

- Protects four line pairs

- Low capacitance

- Low Leakage Current.

- Low Operating and Clamping Voltages.

- Transient Protection for High Speed Data Lines to IEC61000-4-2(ESD)±15kV(air),±8kV(Contact) IEC61000-4-4(EFT) 40A(5/50ns)

IEC61000-4-5(lightning) 24A(8/20us)

#### **Absolute Maximum Ratings**

| Parameter                                              | Symbol           | Value      | Units |

|--------------------------------------------------------|------------------|------------|-------|

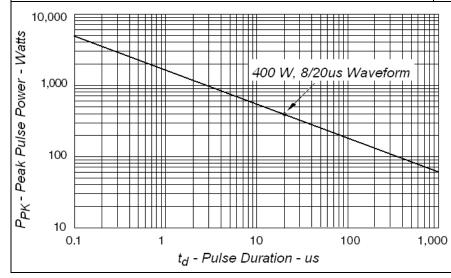

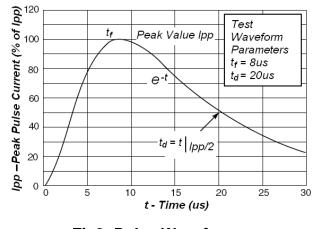

| Peak Pulse Power (t <sub>p</sub> = 8/20μs) - See Fig1. | P <sub>PK</sub>  | 400        | W     |

| Peak Pulse Current (t <sub>P</sub> = 8/20μs)           | I <sub>PP</sub>  | 24         | Α     |

| Storage Temperature Range                              | T <sub>STG</sub> | -55 to 150 | °C    |

| Operating Junction Temperature Range                   | TJ               | -55 to 150 | °C    |

Fig1. Peak Pulse Power VS Pulse Time

## **Electrical Parameter**

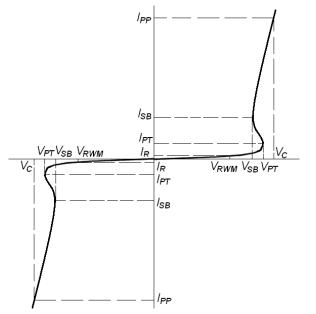

| Symbol          | Parameter                                  |  |  |  |

|-----------------|--------------------------------------------|--|--|--|

| I <sub>PP</sub> | Peak Pulse Current                         |  |  |  |

| V <sub>C</sub>  | Clamping Voltage @ I <sub>PP</sub>         |  |  |  |

| $V_{RWM}$       | Reverse Stand-Off Voltage                  |  |  |  |

| I <sub>R</sub>  | Reverse Leakage Current @ V <sub>RWM</sub> |  |  |  |

| $V_{SB}$        | Snap-Back Voltage @ I <sub>SB</sub>        |  |  |  |

| I <sub>SB</sub> | Snap-Back Current                          |  |  |  |

| $V_{PT}$        | Punch-Through Voltage                      |  |  |  |

| I <sub>PT</sub> | Punch-Through Current                      |  |  |  |

Fig2. SLVU2.8-8 IV Characteristic Curve

## **Electrical Characteristics**

| Parameter                 | Symbol          | Conditions                     | Minimum | Typical | Maximum | Units |

|---------------------------|-----------------|--------------------------------|---------|---------|---------|-------|

| Reverse Stand-Off Voltage | $V_{RWM}$       |                                |         | 2.8     | V       |       |

| Punch-Through Voltage     | V <sub>PT</sub> | I <sub>PT</sub> = 2uA 3.0      |         |         |         | V     |

| Snap-Back Voltage         | $V_{SB}$        | I <sub>SB</sub> = 50mA 2.8     |         |         | V       |       |

| Reverse Leakage Current   | 1               | V <sub>RWM</sub> =2.8V, T=25℃  |         |         | 1       | uA    |

|                           | I <sub>R</sub>  | (Each Line)                    |         |         |         |       |

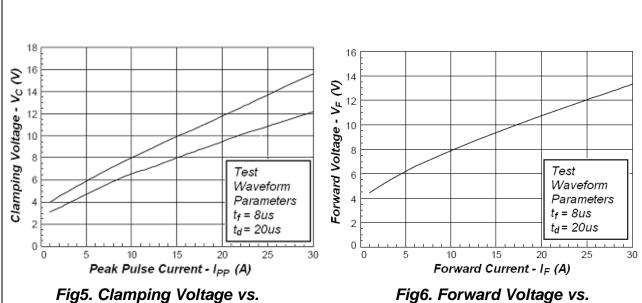

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP} = 2A, t_P = 8/20us$    |         |         | 5.5     | V     |

|                           |                 | (Each Line)                    |         |         | 5.5     |       |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP} = 5A, t_{P} = 8/20us$  |         |         | 8.5     | V     |

|                           |                 | (Each Line)                    |         |         | 0.5     |       |

| Clamping Voltage          | V <sub>C</sub>  | $I_{PP} = 24A, t_{P} = 8/20us$ |         | 15      |         | V     |

|                           |                 | (Each Line)                    |         |         | 10      | v     |

| Junction Capacitance      | C <sub>j</sub>  | VR =0V, f =1MHz                |         | 7       | 10      | pF    |

|                           |                 | (Each Line)                    |         | '       |         |       |

## **Typical Characteristics**

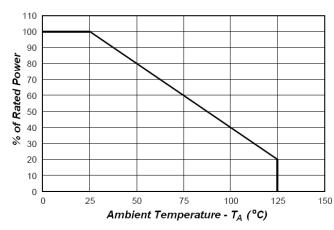

Fig3. Pulse Waveform Fig4. Power Derating Curve

Fig6. Forward Voltage vs. Forward Current

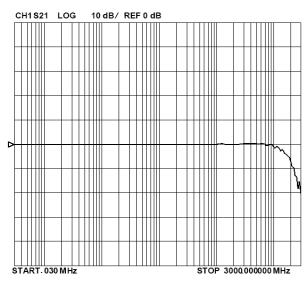

Fig7. Insertion Loss S21

## **Application Note**

Electronic equipment is susceptible to damage caused by Electrostatic Discharge (ESD), Electrical Fast Transients (EFT), and tertiary lightningeffects. Knowing that equipment can be damaged, the SLVU2.8-4 was designed to provide the level of protection required to safe guard sensitive equipment. This product can be used in different configurations to provide a level of protection to meet unidirectional line requirements as well as bidirectional requirements either in a common-mode or differential-mode configuration.

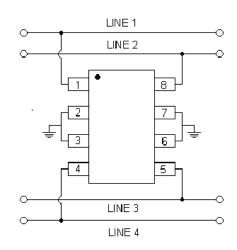

#### Bidirectional Common-Mode Protection (Figure 9)

The SLVU2.8-8 provides up to four lines of protection in a common-mode configuration as depicted in figure 9. Circuit connectivity is as follows:

- Line 1 is connected to Pin 1

- Line 2 is connected to Pin 7

- Line 3 is connected to Pin 3

- Line 4 is connected to Pin 5

- Pins 2, 4, 7 and 8 are connected to ground

Fig 9.

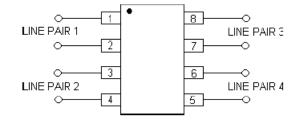

#### Bidirectional different--Mode Protection (Figure 10)

The SLVU2.8-8 provides up to two-line pairs of protection in a differential-mode configuration as depicted in figure 11.

Circuit connectivity is as follows:

- Line Pair 1 is connected to Pins 1 & 2

- Line Pair 2 is connected to Pins 3 & 4

- Line Pair 3 is connected to Pins 7 & 8

- Line Pair 4 is connected to Pins 5 & 6

#### Circuit Board Layout Protection

Circuit board layout is critical for Electromagnetic Compatibility (EMC) protection. The following guidelines are recommended:

- Fig10.

- The protection device should be placed near the input terminals or connectors, the device will divert the transient current immediately before it can be coupled into the nearby traces.

- The path length between the TVS device and the protected line should be minimized.

- All conductive loops including power and ground loops should be minimized.

- The transient current return path to ground should be kept as short as possible to reduce parasitic inductance.

- Ground planes should be used whenever possible. For multilayer PCBs, use ground vias.

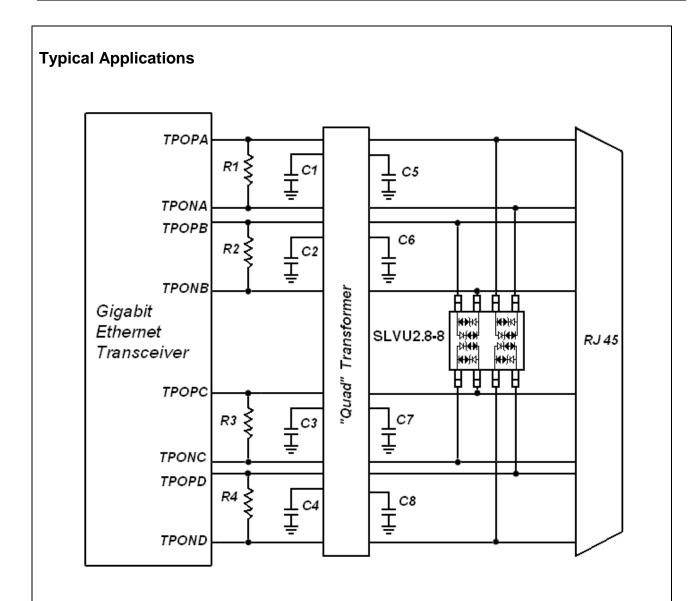

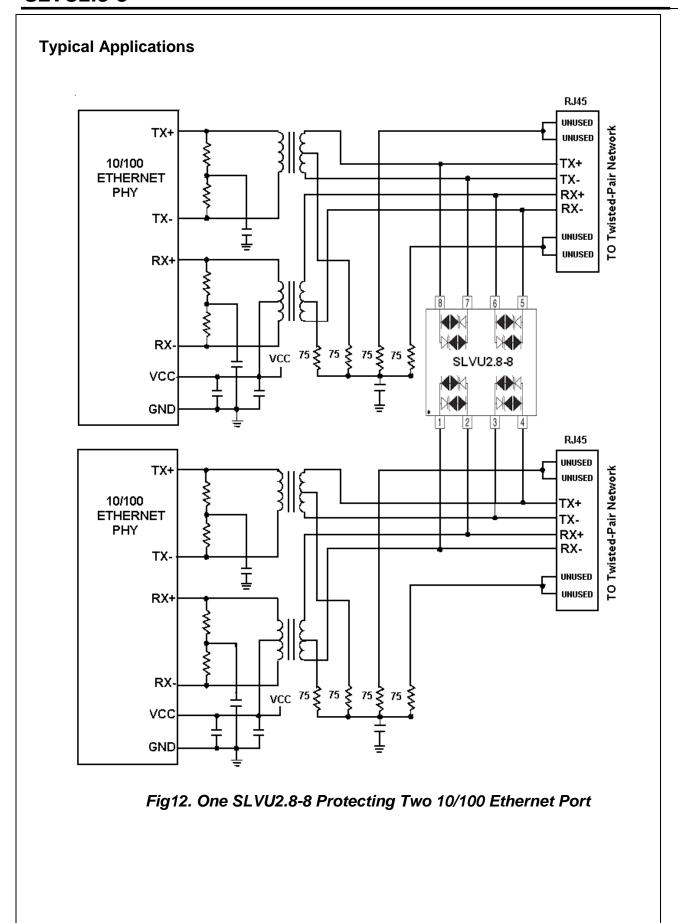

Fig11. Gigabit Ethernet Protection Circuit

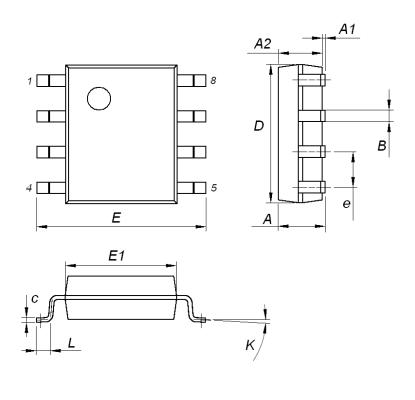

# **SOP-8 MECHANICAL DATA**

| DIM | Millimeters |      |      |  |

|-----|-------------|------|------|--|

|     | MIN         | TYP  | MAX  |  |

| Α   |             |      | 1.75 |  |

| A1  | 0.10        |      | 0.25 |  |

| A2  | 1.35        | 1.55 | 1.75 |  |

| В   | 0.35        | 0.42 | 0.49 |  |

| С   | 0.19        |      | 0.25 |  |

| D   | 4.80        | 4.90 | 5.00 |  |

| Е   | 5.80        | 6.00 | 6.20 |  |

| E1  | 3.80        | 3.95 | 4.00 |  |

| е   |             | 1.27 |      |  |

| L   | 0.40        |      | 0.90 |  |

| K   | 0°          |      | 8°   |  |