### **OVERVIEW**

The SM6105 and SM6106 are multi-channel, 8-bit A/D converters fabricated in Molybdenum-gate CMOS. They feature fast conversion times for four or eight channels, respectively, using a half-flash conversion method. They do not require an external sample-and-hold circuit, and can operate with or without an external microprocessor.

The SM6105 is available in 24-pin plastic skinny DIPs and 24-pin SOPs, and the SM6106, in 28-pin plastic DIPs and 28-pin SOPs.

#### **FEATURES**

- 8-bit resolution

- Four (SM6105) or eight (SM6106) multiplexed input channels

- 1.3 μs (max) conversion time in RD mode and 0.7 μs (max) in WR-RD mode

- External sample-and-hold circuit not required for input signals with less than 200 mV/s slew rate

- 7 mA (typ) current consumption (excluding VREF current)

- ±0.7 LSB (max) non-linearity

- ±0.7 LSB (max) differential non-linearity

- · No external clock required

- · Direct microprocessor interface

- TTL- and CMOS-compatible input/outputs

- Single 5 V supply

- 24-pin plastic skinny DIP and 24-pin SOP (SM6105)

- 28-pin plastic DIP and 28-pin SOP (SM6106)

- Molybdenum-gate CMOS process

## **APPLICATIONS**

- · Data acquisition systems

- · Measuring instruments

- · Process control

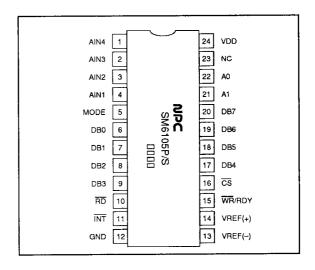

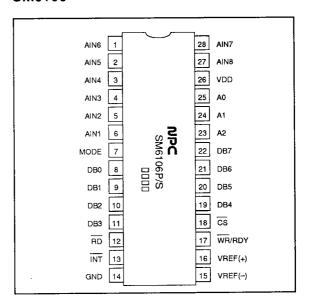

#### **PINOUT**

#### SM6105

#### SM6106

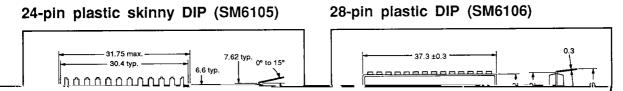

# PACKAGE DIMENSIONS

Unit: mm

# PIN DESCRIPTION

| Number |        | T .,   | D                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

|--------|--------|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SM6105 | SM6106 | - Name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |  |

| _      | 1      | AIN6   | Analog input channel 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| -      | 2      | AIN5   | Analog input channel 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 1      | 3      | AIN4   | Analog input channel 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 2      | 4      | AIN3   | Analog input channel 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 3      | 5      | AIN2   | Analog input channel 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 4      | 6      | AIN1   | Analog input channel 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 5      | 7      | MODE   | Mode select input with internal pull-down resistance. RD mode when LOW or open, and WR-RD mode when HIGH                                                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |

| 6      | 8      | DB0    | Tristate data output bit 0 (LSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 7      | 9      | DB1    | Tristate data output bit 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 8      | 10     | DB2    | Tristate data output bit 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 9      | 11     | DB3    | Tristate data output bit 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 10     | 12     | ŘD     | WR-RD mode: The results of the last conversion are output on DB0 to DB7 who CS and NT are LOW and RD is pulled LOW. If RD is pulled LOW before the internal conversion time has elapsed (approx. 400 ns), the conversion results are latched and output. For stand-alone operation, RD should be held LOW. RD mode: Conversion begins when CS is LOW and RD is pulled LOW. Mode AB is selected depending on whether RD is held LOW until conversion is complet or RD is returned HIGH before conversion is completed.                                 |  |  |  |

| 11     | 13     | INT    | INT goes LOW when conversion is completed and the data is latched. INT returns HIGH on the rising edge of RD or CS.                                                                                                                                                                                                                                                                                                                                                                                                                                   |  |  |  |

| 12     | 14     | GND    | Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |

| 13     | 15     | VREF-  | Reference voltage input (low end)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |  |  |  |

| 14     | 16     | VREF+  | Reference voltage input (high end)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |  |  |  |

| 15     | 17     | WR/RDY | WR-RD mode ( $\overline{WR}$ input): Conversion is started on the falling edge of $\overline{WR}$ . If $\overline{RD}$ is HIGH, the conversion is completed approx. 400 ns after the rising edge of $\overline{WR}$ . INT then goes LOW and the data is latched. RD mode (RDY output): This is an N-channel open-drain output. RDY goes LOW on the falling edge of $\overline{CS}$ or $\overline{RD}$ . It enters a high-impedance state when conversion is completed (mode A) or on the falling edge of $\overline{CS}$ or $\overline{RD}$ (mode B). |  |  |  |

| 16     | 18     | CS     | Chip select input. $\overline{\text{RD}}$ and $\overline{\text{WR}}$ propagate through the internal circuits only when $\overline{\text{CS}}$ is LOW.                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |

| 17     | 19     | DB4    | Tristate data output bit 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 18     | 20     | DB5    | Tristate data output bit 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 19     | 21     | DB6    | Tristate data output bit 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |  |  |  |

| 20     | 22     | DB7    | Tristate data output bit 7 (MSB)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| -      | 23     | A2     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 21     | 24     | A1     | Analog channel select inputs with internal pull-down resistances                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |

| 22     | 25     | A0     |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |  |  |  |

| 23     | -      | NC     | No connection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |  |  |  |

| 24     | 26     | VDD    | Supply voltage                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |

| Nun    | nber   | Name | Description            |  |  |  |

|--------|--------|------|------------------------|--|--|--|

| SM6105 | SM6106 | Name | Description            |  |  |  |

| -      | 27     | AIN8 | Analog input channel 8 |  |  |  |

| -      | 28     | AIN7 | Analog input channel 7 |  |  |  |

## **SPECIFICATIONS**

## **Absolute Maximum Ratings**

$V_{ss}\,=\,0\ V$

| Parameter                   | Symbol           | Rating                   | Unit   |  |

|-----------------------------|------------------|--------------------------|--------|--|

| Supply voltage range        | V <sub>DD</sub>  | -0.3 to 7.0              |        |  |

| Input voltage range         | V <sub>IN</sub>  | $-0.3$ to $V_{DD}$ + 0.3 | ٧      |  |

| Output voltage range        | V <sub>OUT</sub> | $-0.3$ to $V_{DD}$ + 0.3 | V      |  |

| Power dissipation           | P <sub>D</sub>   | 250                      | mW     |  |

| Operating temperature range | T <sub>opr</sub> | -20 to 80                | deg. C |  |

| Storage tempeature range    | T <sub>stg</sub> | -40 to 125               | deg. C |  |

| Soldering temperature       | T <sub>sld</sub> | 260                      | deg. C |  |

| Soldering time              | <sup>‡</sup> sid | 10                       | S      |  |

# **Recommended Operating Conditions**

| Parameter             | Symbol          | Rating |     |      | Unit   |

|-----------------------|-----------------|--------|-----|------|--------|

| Parameter             | Symbol          | min    | typ | max  |        |

| Supply voltage        | V <sub>DD</sub> | 4.75   | 5.0 | 5.25 | ٧      |

| Operating temperature | Торх            | -20    | _   | 70   | deg. C |

## **DC Electrical Characteristics**

$V_{DD}$  = 5 V ±5%,  $T_a$  = -20 to 70 deg. C, unless otherwise noted

|                                                     | Symbol           | O a malinia m                                         | Rating |      |                       | 11   |

|-----------------------------------------------------|------------------|-------------------------------------------------------|--------|------|-----------------------|------|

| Parameter                                           |                  | Condition                                             | min    | typ  | max                   | Unit |

| VREF+ to VREF reference resistance                  | R <sub>REF</sub> |                                                       | 0.5    | 0.85 | 1.3                   | kΩ   |

| Analog input voltage                                | V <sub>IN</sub>  |                                                       | -0.1   |      | V <sub>DD</sub> + 0.1 | ٧    |

| Analog input leakage current                        | lleak1           | $ \begin{array}{llllllllllllllllllllllllllllllllllll$ | _      | ±0.1 | ±3                    | μΑ   |

| CS, WR, RD and A0 to A2<br>HIGH-level input voltage | V <sub>IH1</sub> |                                                       | 2.4    | _    | _                     | ٧    |

| MODE HIGH-level input voltage                       | V <sub>IH2</sub> |                                                       | 3.5    | _    | -                     | ٧    |

| CS, WR, RD and A0 to A2<br>LOW-level input voltage  | V <sub>IL1</sub> |                                                       | -      | _    | 0.8                   | ٧    |

| MODE LOW-level input voltage                        | V <sub>IL2</sub> |                                                       |        | -    | 1.5                   | ٧    |

| Parameter                                                | Cumhal           | Condition                                                                                                                                      |     | Rating      |     | Unit |  |

|----------------------------------------------------------|------------------|------------------------------------------------------------------------------------------------------------------------------------------------|-----|-------------|-----|------|--|

| Parameter                                                | Symbol           | Condition                                                                                                                                      | min | min typ max |     |      |  |

| CS and RD HIGH-level input current                       | hн <sub>1</sub>  | V <sub>IH</sub> = V <sub>DD</sub>                                                                                                              | -   | _           | 1   | μА   |  |

| WR HIGH-level input current                              | I <sub>IH2</sub> | V <sub>IH</sub> = V <sub>DD</sub>                                                                                                              | _   |             | 3   | μА   |  |

| MODE and A0 to A2 HIGH-level input current               | l <sub>IH3</sub> | V <sub>IH</sub> = V <sub>DD</sub>                                                                                                              | -   | 60          | _   | μА   |  |

| CS, WR, RD, MODE and A0 to<br>A2 LOW-level input current | lıL              | V <sub>1L</sub> = 0 V                                                                                                                          | -1  | -           | -   | μА   |  |

| DB0 to DB7 and INT HIGH-level output voltage             | V <sub>ОН</sub>  | I <sub>source</sub> = 360 μA                                                                                                                   | 4   | -           | -   | v    |  |

| DB0 to DB7, INT and RDY<br>LOW-level output voltage      | V <sub>OL</sub>  | l <sub>sink</sub> = 1.6 mA                                                                                                                     | -   | -           | 0.4 | v    |  |

| DB0 to DB7 high-impedance                                | ILEAK2           | V <sub>OUT</sub> = V <sub>DD</sub>                                                                                                             | _   | -           | 3   | μА   |  |

| leakage current                                          |                  | V <sub>OUT</sub> = 0 V                                                                                                                         | -3  | _           | -   |      |  |

|                                                          |                  | Not operating,<br>Vos = VRD =<br>VMODE = 0 V                                                                                                   | -   | 5           | -   |      |  |

| Current consumption                                      | I <sub>DD</sub>  | Operating twn = 250 ns, $t_{RD}$ = 300 ns, $RD_{PW}$ = 150 ns, $t_{P}$ = 100 ns, $t_{P}$ = 100 ns, $t_{P}$ = 100 ns, $t_{P}$ = 100 ns, $t_{P}$ | ÷   | 7           | _   | mA   |  |

| AIN1 to AIN8 analog input pin capacitance                | C <sub>VIN</sub> |                                                                                                                                                |     | 30          | _   | pF   |  |

| Logic output pin capacitance                             | C <sub>OUT</sub> |                                                                                                                                                | -   | 5           | _   | pF   |  |

| Logic input pin capacitance                              | CiN              |                                                                                                                                                | -   | 5           | _   | pF   |  |

# **AC Electrical Characteristics**

$V_{\text{DD}}$  = 5 V ±5%,  $t_{r}$  =  $t_{f}$  = 20 ns,  $T_{a}$  = -20 to 70 deg. C

| Downwater                    | Cymahal           | Condition                                         | Rating |                       |                       | Unit |

|------------------------------|-------------------|---------------------------------------------------|--------|-----------------------|-----------------------|------|

| Parameter                    | Symbol            | Condition                                         | min    | typ                   | max                   | Onit |

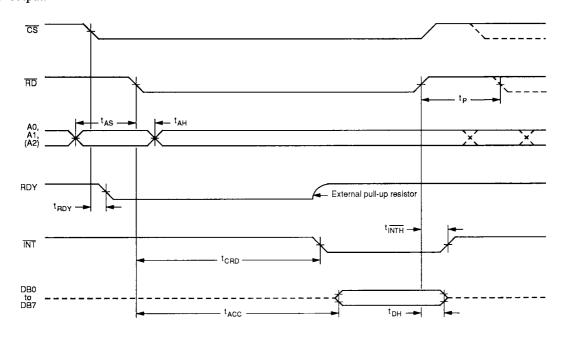

| RD mode conversion time      | tcrd              |                                                   | _      | 0.8                   | 1.3                   | μs   |

| WR-RD mode B conversion time | twr + trd +       | twn = 250 ns,<br>tnD = 300 ns                     | _      | -                     | 0.7                   | μs   |

| Input signal slew rate       | SR                |                                                   | -      | -                     | 0.2                   | V/µs |

| A0 to A2 setup time          | las               |                                                   | 0      | <u> </u>              | -                     | ns   |

| A0 to A2 hold time           | t <sub>AH</sub>   |                                                   | 35     | -                     | -                     | ns   |

| CS to RDY delay time         | trdy              | RD mode                                           | -      | 30                    | 60                    | ns   |

| RD to INT delay time         | ₹ <del>INTH</del> |                                                   | _      | 50                    | 100                   | ns   |

| Data access time             | †ACC              | RD mode A. See note 2.                            | -      | t <sub>CRD</sub> + 20 | t <sub>CRD</sub> + 40 | ns   |

| Data hold time               | tон               | See note 3.                                       | -      | 50                    | 100                   | ns   |

| RD pulsewidth                | RD <sub>PW1</sub> | RD mode B                                         | 70     | -                     | 300                   | ns   |

| Data access time             | tacc2             | RD mode B, WR-RD<br>modes A and B.<br>See note 2. | -      | 50                    | 100                   | ns   |

| Parameter                       | Symbol            | Condition                    | Rating |                      |                       | 11-14 |

|---------------------------------|-------------------|------------------------------|--------|----------------------|-----------------------|-------|

| rarameter                       | Symbol            | Condition                    | min    | typ                  | max                   | Unit  |

| WR pulsewidth                   | twr               | WR-RD mode                   | 0.25   |                      | 50                    | μs    |

| WR to RD setup time             | t <sub>RD</sub>   | WR-RD modes A and B          | 300    | -                    | -                     | ns    |

| WR to RD setup time             | tintl             | WR-RD mode A                 | -      | -                    | t <sub>i</sub>        |       |

| Wh to his setup time            |                   | WR-RD mode B                 | -      | t <sub>RD</sub> + 50 | t <sub>RD</sub> + 100 | ns    |

| Data access time                | tacc1             | WR-RD mode B.<br>See note 2. | -      | 80                   | 150                   | ns    |

| RD pulsewidth                   | RD <sub>PW2</sub> | WR-RD modes A and B          | 150    | -                    | _                     | ns .  |

| Internal comparison time        | ti                | WR-RD mode                   | -      | 400                  | 650                   | ns    |

| INT to data delay time          | t <sub>ID</sub>   | WR-RD mode C.<br>See note 2. | -      | 20                   | 40                    | ns    |

| Succeeding conversion wait time | tp                |                              | 100    | -                    | _                     | ns    |

#### **Notes**

- 1. All timing is measured at a signal control level of 1.6 V.

- 2. Measured using the data access test circuits at output levels of 1.6 V.

- 3. Measured using the data hold test circuits at output levels of 1.6 V.

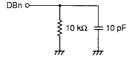

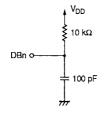

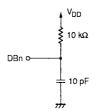

## Data access test circuits

#### Data hold test circuits

V<sub>OH</sub> from high impedance

High impedance from VoH

Vol. from high impedance

High impedance from Vol

## **Converter Characteristics**

$V_{DD}$  = 5 V ±5%,  $V_{REF+}$  = 5 ±0.5 V,  $V_{REF-}$  = 0 V,  $T_a$  = -20 to 70 deg. C

| Deventer                   |     | Rating |      |      |  |

|----------------------------|-----|--------|------|------|--|

| Parameter                  | min | typ    | max  | Unit |  |

| Resolution                 | 8   | _      | -    | bit  |  |

| Non-linearity              | -   | -      | ±0.7 | LSB  |  |

| Differential non-linearity | -   | _      | ±0.7 | LSB  |  |

| Offset error               | -   | -      | ±0.7 | LSB  |  |

| Gain error                 | -   | _      | ±0.7 | LSB  |  |

## **FUNCTIONAL DESCRIPTION**

The SM6105 and SM6106 comprise two parallel A/D converters, one each for the upper and lower four bits of the 8-bit output.

When both  $\overline{RD}$  and  $\overline{CS}$  go LOW (RD mode) or both  $\overline{WR}$  and  $\overline{CS}$  go LOW (WR-RD mode), analog data on the selected input channel is latched and conversion begins. The fifteen comparators in the upper converter (upper four bits) set the threshold levels for the fifteen comparators in the lower converter (lower four bits). The data is then latched and buffered for output.

The SM6105 and SM6106 have two basic modes of operation, set by the level on MODE. If MODE is LOW or open, RD mode is selected, and if MODE is HIGH, WR-RD mode is selected. These two basic modes also have sub-modes of operation, according to the timing of  $\overline{\text{CS}}$ ,  $\overline{\text{RD}}$  and  $\overline{\text{WR}}$ .

## RD Mode (MODE = LOW or open)

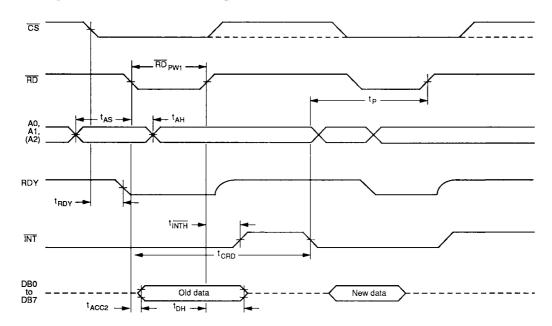

#### Mode A

This mode is provided for microprocessors that support wait cycles. When  $\overline{CS}$  is LOW, the CPU can strobe  $\overline{RD}$  LOW. The data on the selected input channel is latched on the falling edge of  $\overline{CS}$ , then RDY goes LOW and conversion begins.  $\overline{INT}$  goes LOW to signal the CPU that the conversion has completed approximately 800 ns later, and the data is output.

#### Input Channel Selection

| A2 | A1 | AO | Channel |

|----|----|----|---------|

| 0  | 0  | 0  | AIN1    |

| 0  | 0  | 1  | AIN2    |

| 0  | 1  | 0  | AIN3    |

| 0  | 1  | 1  | AIN4    |

| 1  | 0  | 0  | AIN5    |

| 1  | 0  | 1  | AIN6    |

| 1  | 1  | 0  | AIN7    |

| 1  | 1  | 1  | AIN8    |

The thick line indicates the data that applies to the SM6105.

If RDY is connected to a pull-up resistor, RDY goes HIGH on the falling edge of  $\overline{INT}$ , thus acting as the bus wait signal for the CPU.  $\overline{INT}$  returns HIGH and the outputs go high impedance on the rising edge of  $\overline{RD}$  or  $\overline{CS}$ .

Figure 1. RD mode A

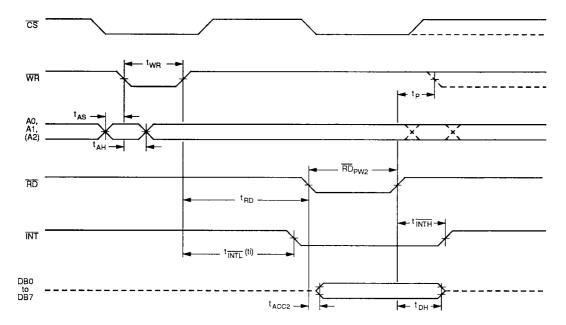

#### Mode B

This mode is provided for microprocessors that do not support wait cycles. When  $\overline{CS}$  is LOW, the CPU can strobe  $\overline{RD}$  LOW. The data on the selected input channel is latched on the falling edge of  $\overline{CS}$ , then RDY goes LOW and conversion begins.  $\overline{INT}$

goes HIGH on the rising edge of  $\overline{RD}$  or  $\overline{CS}$ , and then LOW again when conversion completes. The output data is read by strobing  $\overline{RD}$  LOW again; this also starts the succeeding conversion cycle.

Figure 2. RD mode B

## WR-RD Mode (MODE = HIGH)

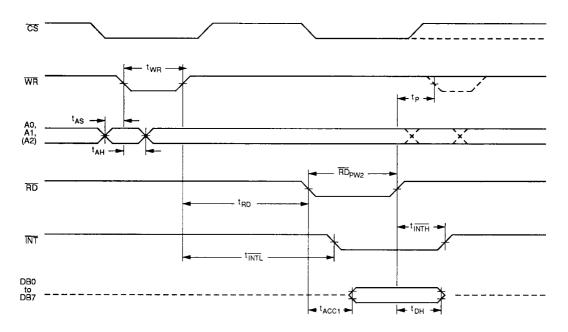

#### Mode A

When  $\overline{CS}$  is LOW, either  $\overline{RD}$  or  $\overline{WR}$  can be pulled LOW. The data on the selected input channel is latched on the falling edge of  $\overline{WR}$ , and conversion begins. If  $\overline{RD}$  is held HIGH,  $\overline{INT}$  goes LOW approximately 400 ns after the rising edge of  $\overline{WR}$ ,

to inform the CPU that conversion is complete, and the output data is latched. When  $\overline{RD}$  goes LOW, the output data is output on DB0 to DB7 to be read by the CPU. In this mode, the CPU is effectively performing interrupt processing.

Figure 3. WR-RD mode A  $(t_{RD} > t_i)$

#### Mode B

In mode A,  $\overline{RD}$  is not pulled LOW until after  $\overline{INT}$  goes LOW, indicating conversion completion. In mode B, however,  $\overline{RD}$  is pulled LOW earlier to shorten the conversion cycle. Provided that the WR-RD setup time ( $t_{RD}$ ) is satisfied, approximately

300 ns,  $\overline{RD}$  can be pulled LOW to complete the conversion without error.  $\overline{INT}$  then goes LOW and the output data is latched and output on DB0 to DB7. In this mode, the CPU is effectively polling the A/D converter.

Figure 4. WR-RD mode B  $(t_{RD} < t_i)$

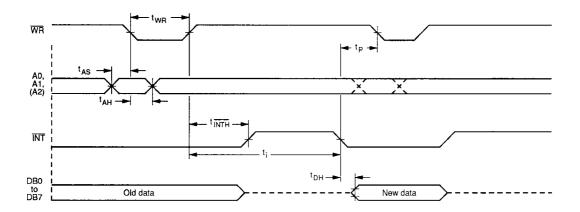

## Mode C

In mode C,  $\overline{\text{CS}}$  and  $\overline{\text{RD}}$  are both tied LOW to allow stand-alone operation (without an external microprocessor). The data on the selected input channel is latched on the falling edge of  $\overline{\text{WR}}$ , and conversion begins.  $\overline{\text{INT}}$  then goes HIGH on the

rising edge of  $\overline{WR}$ , and the DB0 to DB7 outputs go high impedance.  $\overline{INT}$  then goes LOW again approximately 400 ns after the rising edge of  $\overline{WR}$ , and the output data is output on DB0 to DB7.

Figure 5. WR-RD mode C ( $\overline{CS} = \overline{RD} = LOW$ )

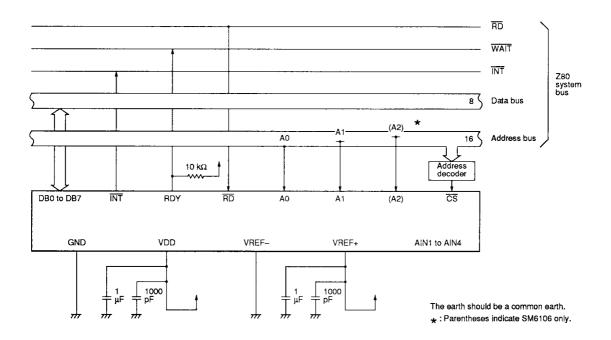

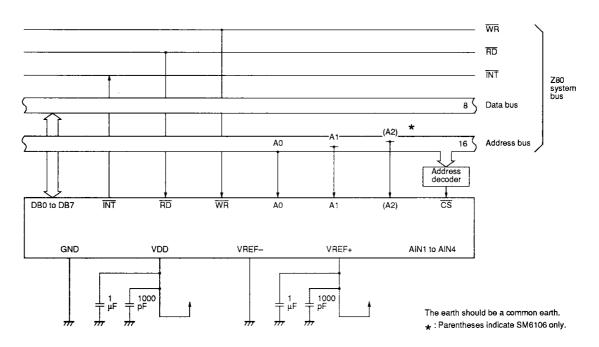

# **Standard Configuration**

## RD mode

## WR-RD mode

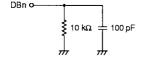

## **DESIGN NOTE**

The SM6105 and SM6106 use CMOS chopper comparators where the analog input is alternately connected and disconnected from the input circuits.

The analog inputs should, therefore, have a low impedance. Also, input buffering is recommended.

NIPPON PRECISION CIRCUITS LTD. reserves the right to make changes to the products contained in this data sheet in order to improve the design or performance and to supply the best possible products. Nippon Precision Circuits Ltd. assumes no responsibility for the use of any circuits shown in this data sheet, conveys no license under any patent or other rights, and makes no claim that the circuits are free from patent infringement. Applications for any devices shown in this data sheet are for illustration only and Nippon Precision Circuits Ltd. makes no claim or warranty that such applications will be suitable for the use specified without further testing or modification.

## NIPPON PRECISION CIRCUITS LTD.

Shuwa Sakurabashi Building 5-4, Hachobori 4-chome Chuo-ku, Tokyo 104 Japan Telephone: 03-3555-7521 Facsimile: 03-3555-7528

NC8930AE 1993.07