#### OVERVIEW

The SM7831 is a CMOS-LSI arithmetic processor developed for decimal long-word arithmetic. This LSI functions as the arithmetic co-processor and dramatically improves the cost performance of a microcomputer. The SM7831 fabricated in the CMOS process requires only an extremely low power to execute various arithmetic operations..

#### ■ FEATURES

- High-speed execution of decimal arithmetic operations, such as addition, subtraction, multiplication, division and square root extraction

- Easy connection with the CPU

Data transfer ... program transfer

End of operation ... interrupt and status read

- The number of arithmetic digits can be selected by the program from 16 digits, 14 digits and 12 digits.

- Convenient register control commands

Clear, Move, Exchange, Zero Sense, Normalize, Shift Right, Shift Left

- Low power consumption 10 mA Typ.

- CMOS single 5 V power supply

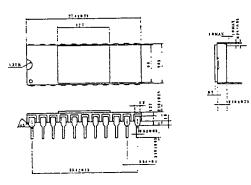

- 22-pin ceramic DIP

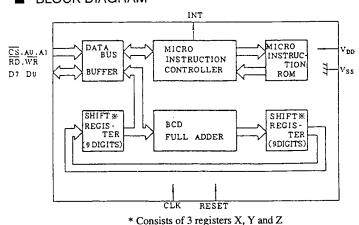

#### ■ BLOCK DIAGRAM

## ■ OVERVIEW (Unit: mm)

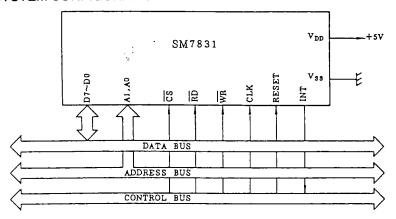

### ■ PINOUT TOP VIEW

# ■ PIN DESCRIPTION

| No. | Name   | Description                                         | No.      | Name            | Description                                         |

|-----|--------|-----------------------------------------------------|----------|-----------------|-----------------------------------------------------|

| 1   | SFTx   | Test pin                                            | 8        | WR              | Write input.                                        |

| 2   | CLK    | External clock input                                | İ        |                 | When the SM7831 is enabled by CS, the data bus      |

| 3   | INT    | Operation end output signal                         |          |                 | data is written into each register via D0 - D7 upon |

| ļ   |        | This signal has positive logic and is output after  |          |                 | input of a negative logic signal to this pin.       |

|     |        | the command input to the SM7831 has executed        |          |                 |                                                     |

|     |        | completely. This signal may be used as a CPU        | 9        | CS              | Chip select input                                   |

|     |        | interrupt request signal. After input, the signal   |          |                 | This input enables the D0 to D7 pins of the         |

|     |        | resets either when digit specification, command     |          |                 | SM7831 for communication between the data bus       |

|     | 1      | input, register input or reset is performed in the  | 1        |                 | and the SM7831.                                     |

|     | •      | SM7831.                                             | 1        |                 |                                                     |

| 4   | RESET  | System reset input.                                 | 10-17    | D7-D0           | Data bus bi-directional input/output                |

|     |        | The reset signal has positive logic and initializes |          |                 | Data and commands are transferred between the       |

|     |        | the SM7831. The status register in the SM7831       |          |                 | CPU and the SM7831 via these 8 input/output         |

|     | İ      | is cleared upon reset.                              |          |                 | pins.                                               |

| 5,6 | A1, A0 | Address bus inputs.                                 | 1        |                 |                                                     |

|     | }      | Various SM7831 operations are selected using        | 18       | Vss             | Ground                                              |

|     |        | these two address control lines.                    | <u> </u> |                 |                                                     |

| 7   | RD     | Read input.                                         | 19 to    | T9 to T7        | Test pins                                           |

|     |        | When the SM7831 is enabled by CS, each              | 21       |                 |                                                     |

| 1   |        | register data is output to D0 - D7 upon input of a  | 22       | V <sub>DD</sub> | Power supply                                        |

|     |        | negative logic signal to this pin.                  |          |                 |                                                     |

# **■** COMMAND ALLOCATION TABLE

|    | Addre | ess |            | Data                |     |                              |               |       |       |      |  |  |  |  |  |

|----|-------|-----|------------|---------------------|-----|------------------------------|---------------|-------|-------|------|--|--|--|--|--|

|    | A1    | Α0  | D7         | D6                  | D5  | D4                           | D3            | D2    | D1    | D0   |  |  |  |  |  |

|    | 0     | 0   | Note)      | The numb<br>DSO and |     | netic digit                  | s is specifie | ed by | DS1   | DS0  |  |  |  |  |  |

| wr | 0     | 1   | SL         | SR                  | Y/X | Arithmetic control command — |               |       |       |      |  |  |  |  |  |

| WA | 1     | 0   | MEM<br>MEM | DAP<br>MEM          | Y/X |                              |               |       |       |      |  |  |  |  |  |

|    | 1     | 1   | -          | WRITE DATA          |     |                              |               |       |       |      |  |  |  |  |  |

|    | 0     | 0   | BUSY       |                     |     |                              | ERROR         | SIGN  | CARRY | ZERO |  |  |  |  |  |

| RD | 0     | 1   |            |                     |     |                              |               |       |       |      |  |  |  |  |  |

|    | 1     | 0   |            |                     |     | DN4                          | DN3           | DN2   | DN1   | DN0  |  |  |  |  |  |

|    | 1     | 1   | -          |                     | — р | EAD DA                       | TA —          |       |       | -    |  |  |  |  |  |

# ■ SYSTEM CONFIGURATION

## OPERATION TIME

The operation time is indicated by the unit time as shown in the table below. The actual time is obtained by multiplying the operation clock frequency to the unit time. In this table, n stands for the number of arithmetic digits, and m for the number of shift digits.

| Item        | Opera            | tion unit time     |

|-------------|------------------|--------------------|

|             | MIN              | MAX                |

| Clear       |                  | n + 7              |

| Move        |                  | n + 7              |

| Exchange    |                  | n + 7              |

| Zero Sense  |                  | n + 7              |

| Normalize   |                  | mn + 5m + 9        |

| Shift Right |                  | 8m + 9             |

| Shift Left  |                  | mn + 5m + 9        |

| Add         | n + 10           | n + 14             |

| Sub         | n + 10           | 2n + 11            |

| MLT         | 23n + 24         | $5n^2 + 43n + 27$  |

| DIV         | $n^2 + 14n + 34$ | $8n^2 + 47n + 24$  |

| SQT         | $n^2 + 14N + 26$ | $12n^2 + 68n + 21$ |

## ■ OPERATION TIME EXAMPLE

14 digits, 2 MHz

| Operation      | MAX (µsec) | MIN (μsec) |

|----------------|------------|------------|

| Addition       | 14         | 12         |

| Subtraction    | 20         | 12         |

| Multiplication | 805        | 173        |

| Division       | 1125       | 213        |

| Square root    | 1663       | 209        |

# COMMAND LIST

|     | Addr  | ess        | Command                           |                       | D                                  |           |          |            | Da         | ta       |          |                                       |                                                                                   | Description                                                                              |  |

|-----|-------|------------|-----------------------------------|-----------------------|------------------------------------|-----------|----------|------------|------------|----------|----------|---------------------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--|

| R/W | A1    | A0         | Command                           | Mnemonic              | Processing                         | D7        | D6       | D5         | D4         | D3       | D2       | DI                                    | D0                                                                                |                                                                                          |  |

|     | 0     | 0          | Specification of<br>the number of | Mode<br>Set           | 12 digits<br>14 digits             | 0         | 00       | 0          | 00         | 0 0      | 0        | 0                                     | 0                                                                                 | Specify the number of arithmetic digits.                                                 |  |

| ļ   |       |            | arithmetic digits                 | SEL                   | 16 digits                          | 0         | 0        | 0          | 0          | 0        | 0        | 1                                     | 0                                                                                 |                                                                                          |  |

|     | 0     | i          | Control                           | Clear                 | X register clear                   | 0         | 0        | 0          | ō          | 0        | 0        | Ô                                     | 0                                                                                 | Clear all digits of the specified register (X,Y) to zero.                                |  |

|     |       | _          | command                           | ****                  | Y register clear                   | 0         | 0        | l          | 0          | 0        | 0        | 0                                     | 0                                                                                 | -                                                                                        |  |

|     |       |            |                                   | Move                  | $X \to Y$ (X is unchanged)         | 0         | 0        | 0          | 0          | 0        | 0        | 0                                     | 1                                                                                 | Transfer the contents of the specified                                                   |  |

| į . |       |            |                                   |                       |                                    |           |          |            | _          | L        | L        | ļ.,                                   | Ļ                                                                                 | register (X,Y) to another register (X,Y).                                                |  |

|     |       |            |                                   |                       | $Y \rightarrow X$ (Y is unchanged) | 0         | 0        | 1          | 0          | 0        | 0        | 0                                     | 1                                                                                 | The contents of the first register remain unchanged.                                     |  |

|     |       |            |                                   | Exchange              | X  Y                               | 0         | 0        | 0          | 0          | ō        | 0        | 1                                     | 0                                                                                 | Exchange the contents of the specified register (Y,Z) with those of the X register.      |  |

|     |       |            |                                   |                       | $X \rightleftharpoons Z$           | 0         | 0        | i          | 0          | 0        | 0        | 1                                     | 0                                                                                 | The contents of unspecified registers remain unchanged.                                  |  |

|     |       |            |                                   | Zero Sence            | X register 0 detection             | 0         | 0        | 0          | 0          | 0        | 0        | 1                                     | 1                                                                                 | Check if the specified register (X,Y) contains all zeros.                                |  |

| 1   |       |            |                                   |                       | Y register 0 detection             | 0         | 0        | 1          | 0          | 0        | 0        | 1                                     | 1                                                                                 | Zero Flag is set if the contents are zero.                                               |  |

|     |       |            |                                   | Normalize             | X register                         | 0         | 0        | 0          | 0          | 0        | 1        | 0                                     | 0                                                                                 | When unnecessary zeros are in high-order                                                 |  |

|     |       |            |                                   |                       | normalization                      |           |          |            |            |          |          |                                       |                                                                                   | digits of the specified register (X,Y), data is                                          |  |

| 1   |       |            |                                   |                       |                                    | L         | _        | _          | _          | _        | _        |                                       | ļ.,                                                                               | shifted leftward by the number of zero                                                   |  |

| 1   |       |            |                                   |                       | Y register                         | 0         | 0        | 1          | 0          | 0        | 1        | 0                                     | 0                                                                                 | digits for normalization. After the shift, the number of shifted digits can be read from |  |

| 1   |       |            |                                   |                       | normalization                      |           |          |            |            |          |          |                                       |                                                                                   | DN4 - DN0.                                                                               |  |

|     |       |            |                                   | SL                    | X register shift left              | 1         | 0        | 0          | <b>S</b> 4 | S3       | S2       | SI                                    | so                                                                                | The shift operation can be performed by                                                  |  |

|     |       |            |                                   |                       | Y register shift left              | 1         | 0        | 1          |            | S3       |          |                                       | SO                                                                                | setting one of these bits to "1" and specifying the number of shift digits with 5        |  |

| WR  |       |            |                                   | SR                    |                                    | 0         | 0        | 0          | <b>↓</b>   | S3       | <b>!</b> | _                                     | SO                                                                                | bits of D4 to D0 (binary). The arithmetic/                                               |  |

| 1   |       |            |                                   | J.K                   | X register shift right             | <u> </u>  |          |            |            | ↓        | ┡        | -                                     | SO                                                                                | control command is executed when both SL                                                 |  |

| ŀ   |       |            | Y register shift right            | 0                     | i                                  | 1         | ₩        | <b>S</b> 3 | 1          | $\vdash$ |          | (D7) and SR (D6) are "0".             |                                                                                   |                                                                                          |  |

|     | 1 1 1 | Arithmetic | Add                               | $X + Y \rightarrow X$ | 0                                  | 0         | 0        | 0          | 1          | 0        | 0        | 0                                     | Adds the values of the X and Y registers and stores the result in the X register. |                                                                                          |  |

|     |       | command    |                                   |                       |                                    |           |          |            | 1          |          |          |                                       |                                                                                   | When a carry is generated, 1-digit                                                       |  |

|     |       | l          |                                   |                       |                                    |           | ì        |            |            |          |          |                                       |                                                                                   | rightward shift is performed automatically,                                              |  |

|     | ŀ     | i          |                                   |                       |                                    |           |          |            | ŀ          |          |          |                                       |                                                                                   | and Carry Flag is set. The contents of the Y                                             |  |

|     | ĺ     |            |                                   |                       |                                    |           |          |            |            | 1        |          |                                       |                                                                                   | register remain unchanged. Both the X and Y registers need not be normalized.            |  |

|     |       | 1          | 1                                 | Sub                   | $X - Y \rightarrow X$              | 0         | 0        | 0          | 0          | ١.       | 0        | 0                                     | 1                                                                                 | Subtract the Y register value from the X                                                 |  |

|     |       |            |                                   | 500                   | A-1 /A                             | "         | 0        | ١ '        | ١٧         | 1        | ١        | 0                                     | '                                                                                 | register value and store the result in the X                                             |  |

|     |       |            |                                   | İ                     |                                    |           | ĺ        |            |            | Ì        |          | ł                                     |                                                                                   | register. Zero Flag is set when X = Y. Sign                                              |  |

| 1   |       |            |                                   |                       |                                    |           |          |            | ļ          |          |          |                                       |                                                                                   | Flag is set when X < Y. The contents of the                                              |  |

|     |       | ļ          |                                   |                       | !                                  |           |          |            |            |          |          | ļ                                     |                                                                                   | Y register remain unchanged. Both the X and Y registers need not be normalized.          |  |

|     |       | İ          |                                   | Mlt                   | $X*Y \rightarrow X$                | 0         | 0        | 0          | 0          | 1        | 0        | 1                                     | 0                                                                                 | Multiply the X register value by the Y                                                   |  |

| 1   | 1     |            |                                   |                       |                                    | -         |          |            |            | -        |          |                                       |                                                                                   | register value and store the result in the X                                             |  |

|     |       |            |                                   |                       |                                    | 1         |          |            | 1          | ĺ        |          | 1                                     |                                                                                   | register. If a carry is generated, the 1-digit                                           |  |

|     |       |            |                                   | •                     |                                    |           |          |            |            |          |          |                                       |                                                                                   | right shift is carried out automatically, and                                            |  |

| 1   | 1     | ŀ          |                                   |                       |                                    |           |          |            |            |          |          |                                       |                                                                                   | Carry Flag is set. The contents of the Y register remain unchanged, and the contents     |  |

|     |       |            |                                   |                       |                                    |           |          |            |            | 1        |          | 1                                     |                                                                                   | of the X register remain unchanged in the Z                                              |  |

|     |       |            |                                   |                       |                                    |           |          |            |            |          |          |                                       | 1                                                                                 | register. Although the Y register need not                                               |  |

|     |       |            |                                   |                       |                                    |           |          |            |            |          |          |                                       |                                                                                   | be normalized, the X register must be                                                    |  |

|     |       |            |                                   | Div                   | V/V A. V                           | -         | Ļ        | _          | -          | +        | +        | <del> -</del>                         | -                                                                                 | normalized.  Divide the X register value by the Y                                        |  |

|     |       |            |                                   | Div                   | X/Y to X                           | 0         | 0        | 0          | 0          | 1        | 1        | 0                                     | 0                                                                                 | register value and store the result in the X                                             |  |

|     |       |            |                                   |                       |                                    | 1         |          |            |            |          |          |                                       |                                                                                   | register. The residual is stored in the Z                                                |  |

|     |       |            |                                   |                       |                                    |           |          |            |            |          |          |                                       |                                                                                   | register. Error Flag is set if this command                                              |  |

|     |       |            |                                   |                       |                                    |           | 1        |            |            |          |          |                                       |                                                                                   | is executed with the Y register set to zero.                                             |  |

|     |       |            |                                   |                       |                                    |           |          |            |            |          |          | The contents of the Y register remain |                                                                                   |                                                                                          |  |

|     |       |            |                                   |                       |                                    |           |          |            |            | 1        |          |                                       |                                                                                   | unchanged. Both the X and Y registers must be normalized.                                |  |

| L.  | 1     | Ш.         | .1                                | l                     | <u> </u>                           | <u>t_</u> | <u> </u> | Щ.         | L          | 1_       |          | <u> </u>                              | <u>L</u>                                                                          |                                                                                          |  |

| /W A1 A | A0 Comman   | ic SQRTode        |                                       | D7 | D6<br>0 | D5<br>0 | D4<br>0 |   | D2 | DΙ | D0 | Description                                                                                                                                                                                                                                                          |

|---------|-------------|-------------------|---------------------------------------|----|---------|---------|---------|---|----|----|----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0       |             | d                 | $\sqrt{X_{\text{odd}}} \to X$         | 0  | 0       | 0       | -       |   |    |    |    |                                                                                                                                                                                                                                                                      |

|         |             | CODT              |                                       |    |         |         |         | 1 | 1  | 1  | 0  | Calculate the square root of the X register and store the result in the X register. The x register value must be normalized. Note                                                                                                                                    |

|         |             | SQRTeve           | $^{n}  \sqrt{X_{even}} \rightarrow X$ | 0  | 0       | 0       | 1       | 1 | 1  | 1  | 0  | that the SQRT command differs depending<br>on whether the number of digits before the<br>decimal point is odd or even.                                                                                                                                               |

| 1 0     | 0 Data tran | sfer MEM →<br>DAP | MEMORY →<br>X register                | 1  | 0       | 0       | 0       | 0 | 0  | 0  | 0  | Set this bit to "1" and specify the X and Y registers to enable MEM → DAP operation Next, sequentially transfer the write data to store it in the specified register. Eight-bit data is transferred from the least significant digit (LSD) in units of 2 digits. For |

| VR      | R           | •                 | MEMORY→ Y register                    | 1  | 0       | 1       | 0       | 0 | 0  | 0  | 0  | example, when the number of arithmetic digits is 16, D3 to D0 are transferred first a LDD and DT to DA to the transferred first a                                                                                                                                    |

| R/W   | Add | ress | Community                 |           |                   | Τ                    |    | _  | D     | ata                 |      |     |      |                                                                                                                                                                                                           |

|-------|-----|------|---------------------------|-----------|-------------------|----------------------|----|----|-------|---------------------|------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| IN ** | Al  | A0   | Command                   | Mnemonic  | Processing        | D7                   | D6 | D5 | D4    | D3                  | D2   | 2 D | Do   | Description                                                                                                                                                                                               |

|       | 0   | 0    | Status flag               | Status    |                   | Busy                 | 1  | ,  | ,     |                     | Sign | T   | Zero | Busy     This bit goes "1" during operation.     Error     This bit goes "1" when division is performed and the Y register is zero.                                                                       |

| RD    | 1   | 0    | Number of shift<br>digits | Shift     |                   | 1                    | -  | 1  | 5 DN4 | DN3                 | DN2  | DN1 | DN0  | <ul> <li>Sign This bit goes "1" when the result of the SUB command is X &lt; Y (negative).</li> <li>Carry This bit goes "1" when a carry is generated in the Add or Mlt command.</li> <li>Zero</li> </ul> |

|       | 1   | 1    | Read data                 | Read Data | Decimal, 2 digits | High-order<br>digits |    |    | - 1   | Low-order<br>digits |      |     |      | This bit goes "1" when the X register is zero and Zero Sensor or another operation command is executed.                                                                                                   |

#### Notes

- \*1  $S_0$  to  $S_4$  set the number of shift digits in binary.

- \*2  $\sqrt{X_{odd}}$ : when the number of digits before the decimal point is odd in the X register.

- √X<sub>even</sub>: when the number of digits before the decimal point is even in the X register.

\*3 DN0 to DN4 indicate the number of shift digits after the normalization command in binary.

# ■ ABSOLUTE MAXIMUM RATINGS

| Item                  | Symbol                            | Rating               | Unit | Remarks   |

|-----------------------|-----------------------------------|----------------------|------|-----------|

| Supply voltage        | V <sub>DD</sub> - V <sub>SS</sub> | -0.3 to +6.5         | v    |           |

| Input voltage         | Vin                               | Vss -0.3 to Vpd +0.3 | v    |           |

| Output voltage        | Vout                              | Vss -0.3 to VDD +0.3 | V    |           |

| Allowable dissipation | PD                                | 250                  | mW   | Ta = 70°C |

| Storage temperature   | Тѕтс                              | -40 to +125          | °C   |           |

| Operating temperature | Topr                              | -20 to +70           | °C   |           |

| Soldering temperature | Tsld                              | 260±5                | °C   |           |

| Soldering time        | tsld                              | 10                   | Sec  |           |

# ■ ELECTRICAL CHARACTERISTICS

## <DC Characteristics>

$V_{DD} = 5 \text{ V} \pm 5\%$ , Ta = 0 to 70 °C unless otherwise noted.

|                           | T .             |                                  |      | LIMITS |      |      |  |  |  |

|---------------------------|-----------------|----------------------------------|------|--------|------|------|--|--|--|

| ITEM                      | SYMBOL          | CONDITIONS                       | MIN  | TYP    | MAX  | UNIT |  |  |  |

| Current consumption       | Idd             |                                  |      | 10     | 25   | mA   |  |  |  |

| Operating voltage         | V <sub>DD</sub> |                                  | 4.75 | 5.00   | 5.25 | V    |  |  |  |

| High-level output voltage | Von             | IOH = 400 μA other than test pin | 3.5  |        | 5.25 | v    |  |  |  |

| Low-level output voltage  | Vol             | IOL = 2 mA other than test pin   | 0    | L      | 0.4  | v    |  |  |  |

| High-level output voltage | Vон             | Ioн = 400 µA test pin            | 3.5  |        | 5.25 | V    |  |  |  |

| Low-level output voltage  | Vol             | IoL = 400 μA test pin            | 0    |        | 0.4  |      |  |  |  |

| High-level input voltage  | ViH             |                                  | 2.4  |        | 5.25 | v    |  |  |  |

| Low-level input voltage   | VıL             |                                  | 0    |        | 0.8  | V    |  |  |  |

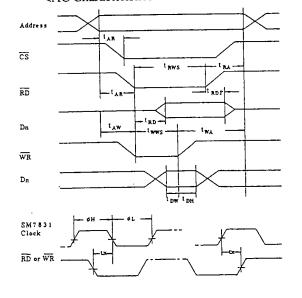

# <AC Characteristics>

<sup>\*</sup> The "High" period of the SM7831 clock and the "Low" period of the  $\overline{RD}$  or  $\overline{WR}$  pulse must overlap by at least tx.

|                             | ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ ~~ | LIN | 1ITS | UNIT |

|-----------------------------|----------------------------------------|-----|------|------|

| ITEM                        | SYMBOL                                 | MIN | MAX  | UNII |

| Address RD or CS delay      | tar                                    | 20  |      | ns   |

| RD-Address delay            | tra                                    | 20  |      | ns   |

| RD pulse width              | trws                                   | 400 |      | ns   |

| RD-Data Bus Enable delay    | trd                                    |     | 300  | ns   |

| RD-Data Bus Disable delay   | trdf                                   |     | 100  | ns   |

| Address-RD delay            | taw                                    | 20  |      | ns   |

| WR-Address delay            | twa                                    | 20  |      | ns   |

| WR pulse width              | twws                                   | 400 |      | ns   |

| WR-Data Bus Enable overlap  | tow                                    | 50  |      | ns   |

| WR-Data Bus Disable overlap | <b>t</b> DH                            | 50  |      | ns   |

| Operating frequency         | forg                                   | DC  | 2.0  | MHz  |

| SM7831 clock pulse width    | øH                                     | 200 |      | ns   |

| (tr, tr≤20ns)               | øL                                     | 300 |      | ns   |

| Clock-RD,WR overlap         | tx                                     | 100 |      | ns   |

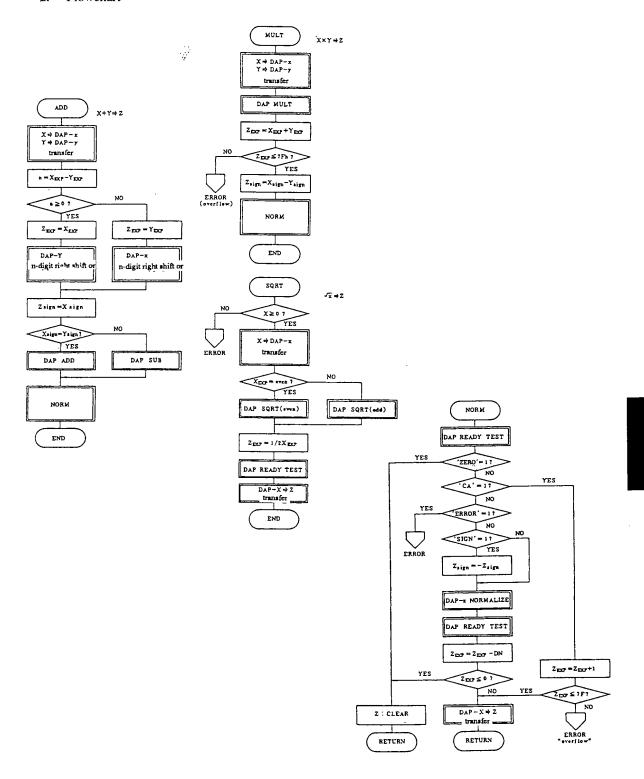

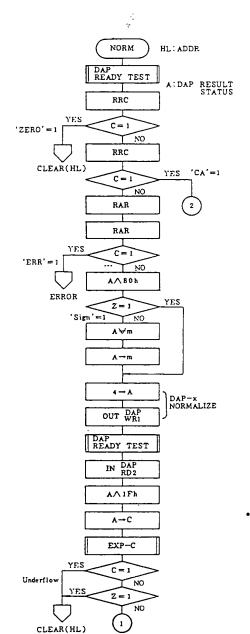

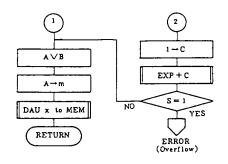

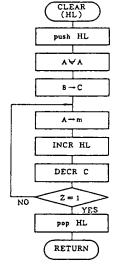

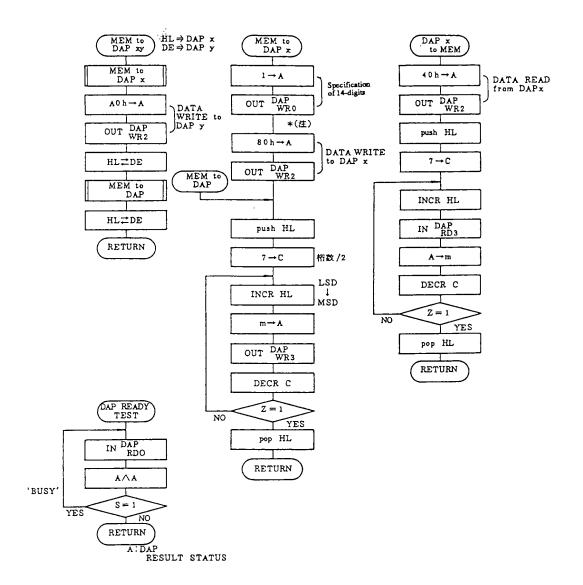

## ■ EXPLANATION OF APPLICATION

The following describes an example of executing various arithmetic operations with 14-digit decimal floating-point data. In this example, the 8085A is used for CP. In the flowchart, parts enclosed in parenthesis ( ) are executed by the SM7831, and the rest by the CPU.

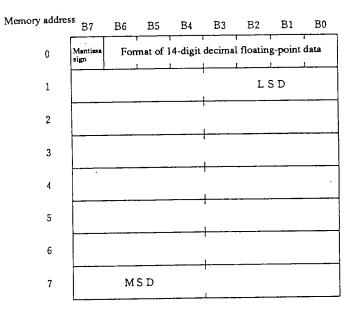

Data format

Format of 14-digit decimal floating-point data

| Note 1. | The mantissa part is always normalized. |

|---------|-----------------------------------------|

|         | Decimal number only.                    |

| Note 2  | Sign of the mantissa                    |

|        | "0" Positive          |

|--------|-----------------------|

|        | "1" Negative          |

| Note 3 | Exponent data example |

| Exponent data | Contents                               |

|---------------|----------------------------------------|

| 00            | When data is "0"                       |

| 01            | 10 <sup>-63</sup><br>10 <sup>-62</sup> |

| 02            | 10 <sup>-62</sup>                      |

| · ·           |                                        |

| 3FH           | 10-1                                   |

| 40h           | 100                                    |

| 41h           | 10 <sup>1</sup>                        |

| -             |                                        |

| 7Fh           | 10 <sup>63</sup>                       |

[Example] How to represent 123.45

Memory address

|    | 4 | $\perp$ | 2           |                                       |

|----|---|---------|-------------|---------------------------------------|

|    | 0 | $\perp$ | 0           |                                       |

| Γ  | 0 | I       | 0           |                                       |

|    | 0 | T       | 0           |                                       |

|    | 0 | T       | 0           | _                                     |

| Γ  | 5 | I       | 0           |                                       |

| Ţ. | 3 | Ι       | 4           |                                       |

| Γ  | 1 | T       | 2           |                                       |

|    |   | 0 0 5   | 0 0 0 0 0 5 | 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 0 |

#### 2. Flowchart

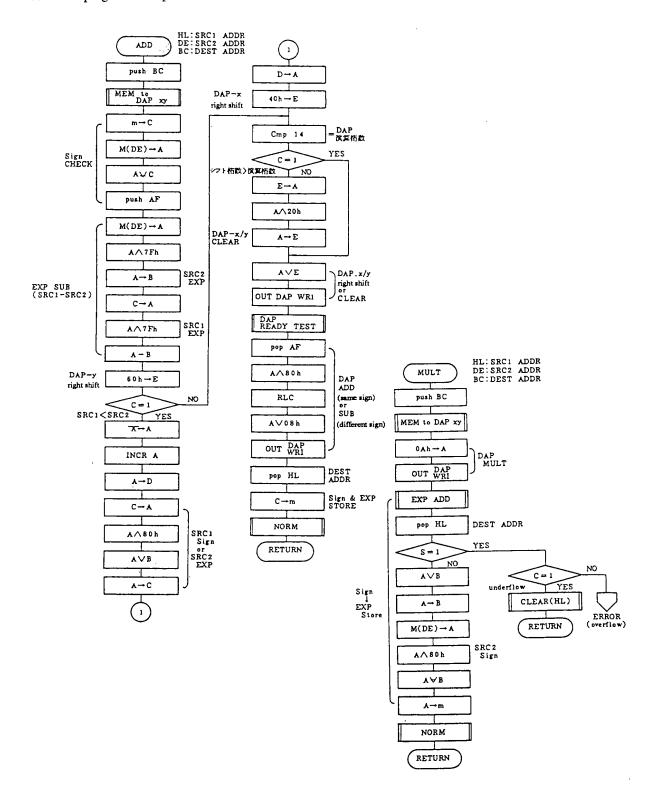

## 3. 8085 program example

NORM routine common to ADD, SUB, MULT and DIV.

The dedicated NORM routine must consider only the following STATUS.

'ZERO' ---- common 'CA' ----- ADD, MULT

'ERR' ----- DIV

'SIGN' ----- SUB

The routine below DAP-x, NORMALIZE is needed for SUB and DIV. It can be omitted for ADD and MULT.

(Note) Though the specification of the number of digits is included in this routine, it must be performed only once in a routine of system initialization etc.

## ■ TYPICAL APPLICATIONS

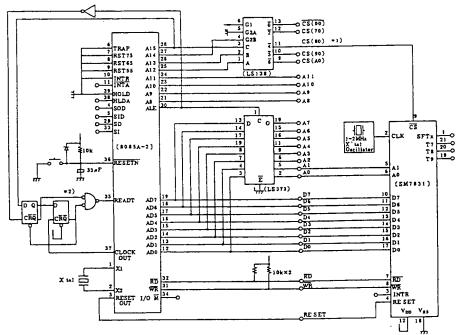

1. Connection with the 8085A (reference circuit)

- \*1 I/O port address is in the order of 8000.

- \*2 Wait Control example

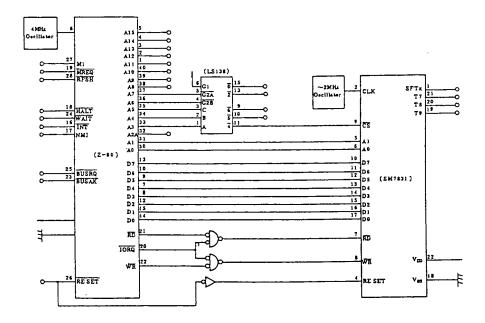

- 2. Connection with the Z-80 (reference circuit)

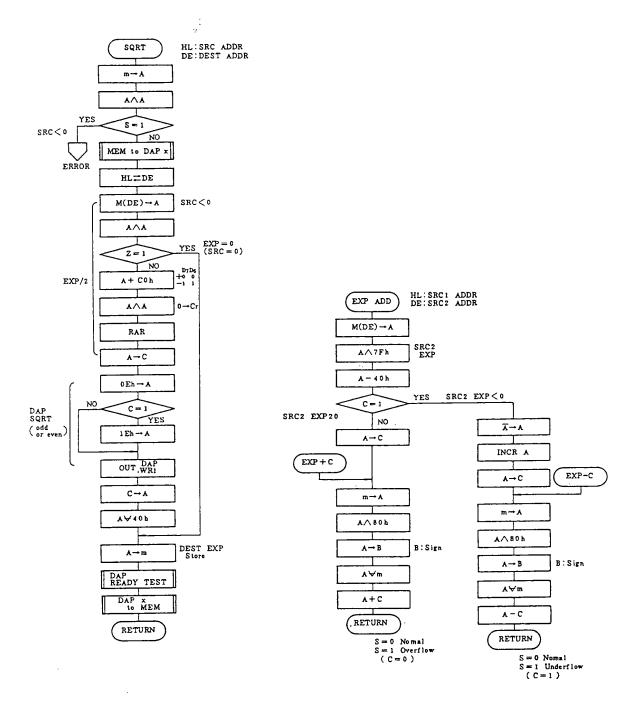

# ■ SUPPLEMENTARY EXPLANATION

Source list of arithmetic operations (addition, subtraction, multiplication, division, square root) performed by the 8088

In this example, the data format is set as shown below.

| Memory address |     | <15 | -digit  | floati     | ng po    | int da | ata> |   |

|----------------|-----|-----|---------|------------|----------|--------|------|---|

| 0              |     |     | Expanen | L data (be | exadecin | ul)    |      |   |

| 1              |     | M   | SD      |            |          | MSI    | )-1  |   |

| 2              |     | MSI | D-2     |            |          |        |      |   |

| 3              |     |     |         |            |          |        |      |   |

| 4              | - , |     |         |            |          |        |      |   |

| 5              |     |     |         |            |          |        |      | L |

| 6              |     |     |         |            |          |        |      |   |

|                |     |     |         |            |          |        |      |   |

LSD+1

LSD+2

LSD

| 01h<br>02h | - 127<br>- 126 |

|------------|----------------|

| :          | :              |

| 7Fh        | -1             |

| 80h        | 0              |

| 81h        | +1             |

| :          | ; i            |

| FFh        | + 127          |

Note 1: Exponent data is shown below.

When mantissa data is "0", the exponent is set to "0".

Note 2: Signs are as follows.

When mantissa data is positive ... "Ch"

When mantissa data is negative ... "Dh"

```

SOURCE

LOC

овј

LINE

Function_Module (2)

NAME

*83.09.13

09.22

10

1 1

1 2

1 3

1 4

1 5

1 6

1 7

Addition, Additon...W.

PUBLIC

Subtraction, Subtraction_W.

Multiply, Multiply_W.

Division, Division_W.

Square_Root, Square_Root_W.

1 9

2 0

2 1

2 2

2 3

Integer. Integer_W.

Round_UP. Round_UP_W.

Round, Round_W.

Round_Down, Round_Down_W.

Clear_W

2 4 2 5

SECMENT PUBLIC 'CODE'

Function_Module

ÁSSUME

CS: Punction_Module

3 0

3 1

3 2

3 3

3 4

3 5

3 6

3 7

WORK_0: byte, WORK_1: byte, WORK_2: byte, WORK_3: byte, WORK_4: byte, WORK_5: byte, WORK_6: byte, WORK_7: byte

EXTRN

Func_error:near

EXTRN

3839

Function_Sub!

PROC

0000

4 0

41

42

43

44

45

46

Function_Sub (1)

DAU_DIGIT

DAU_COMMAND

FOU

0030

EQU

47

DAU_DIRECTION

FOU

3 4 11

3 6 11

49

DAU_WRITE_DATA

EQU

:

3 6 10

DAU_STATUS EQU

DAU_NORM_STATUS EQU

```

```

LOC OBJ

LINE

SOURCE

5 3

0036

DAU_READ_DATA

54

EQU

3 6 !!

*****

Addition (W)

5 7

0000

(DS:SI) + (ES:DI) => (DS:SI)

58

Addition_w:

0000 8BDE

Mov

6 0

6 1

6 2

****

Addition

0002

(DS:SI) + (ES:DI) => (DS:BX)

.

Addition:

0002 32D2

6 4

6 5

0004 EB04

XOR

DL. DL

JMP

short ADD_or_SUB

67

;**** Subtraction (W)

0006

(DS:SI) - (ES:DI) -> (DS:SI)

7071

Subtraction_W:

0006 8BDE

MOV

BX. SI

7 3

Subtraction

0008

(DS:SI) - (ES:DI) -> (DS:BX)

Subtraction:

0008 B201

7.6

MOV

7 ?

7 8

JMP

short ADD_or_SUB

***** ADD_or_SUB ****

8 0

0 0 0 A

000A 325408

000D 26325508

0011 80E201

ADD_or_SUB:

8 2

8 3

XOR

DL. DS: [SI+8]

DL. ES: [DI+8]

DL. 1

XOR

AND

8 5

0014

0014 8A04

0016 268A25

0019 B620

001B 3AC4

001D 7304

ADD_or_SUB_2:

MOV

MOV

AL, DS: [SI]

AH, ES: [DI]

DH, 20H

88

MOV

CMP

AL. AH

9 J

9 2

001F 86E0

0021 32F6

JNC

J_00]

XCHG

0023

XOR

94

0023 8807

J_001:

[BX], AL

0025 2AC4

0027 3C0F

0029 7304

002B 0C40

MOV

; AL - GRATE EXP

SUB

AL. AH

9 7

9 8

CMP

AL. OFH

J_002

AL. 40H

DH. AL

J_002:

JNC

OR

DO2D DAPO

100

002F

OR

101

: X/Y R_SHIFT

102

002F E8DA00

;

103

CALL

MEM_to_DAU_XY

104

0032 8AC6

0034 E632

;

105

MOV

AL, DH

DAU_COMMAND, AL

106

OUT

0036 E82501

0039 8A4408

003C 884708

107

108

CALL

DAU_READY_TEST

AL, DS: [S!+8]

[BX+8], AL

0 0

MOV

110

MOV

003F 8AC2

0041 0403

0043 E632

0045 7A13

моч

AL, DL

113

ADD

AL, 8

AL, 8

DAU_COMMAND, AL

NORM_W_2

ENOTE NORM_W_1

: (DL) 0/1

: 8/9

ADD/SUB

115

:. . .

JMP

118

NORM W (1) ****

119

0047

0047 E81401

NORM_W_1 :

121

CALL .

DAU_READY_TEST

004A D0E8

004C 7229

1 2 2

: DAU 'ZERO'?

AL, 1

Clear_W

SHR

124

JC

004E D0E8

0050 7304

: DAU 'CA'?

SHR

AL. 1

J_101

127

JNC

0052 FE07

0054 7448

0056

128

: DAU 'CA--1

INC

byte ptr [BX]

ENZAN_ERROR .

130

0056 E8E300

0059 C3

JΖ

131

J-101:

CALL

DAU_X_ LO_MEM

```

```

LOC OBJ

LINE

SOURCE

134

: **** NORM W (2) ****

1 3 5

136

NORM_W_2:

005A

005A E80101

CALL

DAU_READY_TEST

138

; DAU 'ZERO'?

139

i 4 0

005D D0E8

005F 7216

Clear_W

JC

142

:

0 0 6 1 D 0 E 8

0 0 6 3 2 4 0 1

0 0 6 5 3 0 4 7 0 8

SHR

AL. 1

AND

AL, ]

[BX+8], AL

: 'SIGN'=1 CHG_SIGN

: DAU X_NORMALIZE

MOV

0068 B004

006A E632

147

AL, 4

DAU_COMMAND, AL

OUT

CALL

DAU_READY_TEST

005C E8EP00

150

AL, DAU_NORM_STATUS

AL, 1FH

(BX), AL

J_101

short Clear_W

D 0 6 F E 4 3 4

0 0 7 1 2 4 1 F

0 0 7 3 2 8 0 7

0 0 7 5 7 7 D F

IN

AND

SUB

153

155

JA

JMP

1. . .

158

**** Clear W

(DS:BX)

1 6 0

161

0077

0077 1E

0078 07

Clear_W:

PUSH

DS

163

POP

E S

0079 57

007A 8BFB

007C B90400

007F 33C0

PUSH

DI

DI. BX

CX. 4

AX, AX

166

MOV

MOV

XOR

CLD

169

0082 F3

0083 AB

0084 C6050C

REP

170

byta ptr [DI], OCH

i 7 1

MOV

POP

0087 5F

0088 C3

172

173

RET

174

175 :

176 +1 $EJECT

177

Multiply (W) ***** (DS:S1) + (ES:D1) -> (DS:S1)

180

Multiply_W:

MoV

0089

0089 8BDE

BX. 51

182

183

.....

Multiply

(DS:S1) * (ES:D1) -> (DS:BX)

1 8 5

1 8 6

.

Multiply:

008B

MEM_to_DAU_XY

CALL

008B E87E00

187

; DAU X+Y

188

моч

AL, OAH

DAU_COMMAND, AL

008E B00A

0090 E632

189

190

OUT

191

SIGN_EXP_STORES NORM_W_1

CALL

0092 E82300

0095 71B0

JNO

193

194

OVERPLOW_CHECK:

PUSHF

CALL

POPF

0097

0097 9C

0098 E8C300

009B 9D

009C 72D9

196

DAU_READY_TEST

Clear_W

J C

199

200

009E

009E E90000

201

ENZAN_ERROR:

Func_Error

JMP

E

202

```

```

LOC OBJ

LINE

SOURCE

203

204

205

; * * * * *

Division (W)

(DS:S1) / (ES:D1) => (DS:S1)

206

:

Divlsion_W:

MOV

0 0 A 1

BX. SI

OOAL BBDE

208

Division

210

, *****

(DS:S1) / (ES:D1) => (DS:BX)

2 1 1

Division:

0 0 A 3

byle pir ES: [D1+1]. OFFII

ENZAN_ERROR ; (ES: D

TEST

00A3 26F64501FF

213

; (ES:D1) =0

00A8 74F4

214

JZ

00AA E85F00

216

CALL

MEM_ L . _ DAU_XY

; DAU X/Y

217

AL. OCH

DAU_COMMAND, AL

00AD B00C

00AF E632

MOV

OUT

220

00B1 E80C00

00B4 71A4

00B6 EBDF

CALL

SIGN_EXP_STORE2

NORM_W_2

OVERFLOW_CHECK

JNO

JMP

\begin{smallmatrix}2&2&3\\2&2&4\end{smallmatrix}

EY**

2 2 5

SIGN , EXP STORE (I) ****

SIGN (XOR) , EXP (ADD)

226

2 2 8

2 2 9

2 3 0

SIGN_EXP_STORE1:

0 0 B 8

MOV

AH, ES [DI]

DOB8 268A25

00BB 80EC80

00BE EB05

SUB

AH, 80H

short J_121

231

JMP

SIGN . EXP STORE (2) ****

SIGN (XOR) . EXP (SUB)

233

234

SIGN_EXP_STORE2:

0.000

00C0 B480

00C2 262A25

AH. 80H

236

AH, ES: [D1]

237

SUB

J_121:

0.005

AL, [$1+8]

AL, ES: [DI+8]

AL, 00001100B

[BX+8], AL

00C5 8A4408

239

MOV

00C8 26324503

00CC 0C0C

00CE 884708

240

XOR

OR

MOV

243

244

00D1 8A04

00D3 2C80

00D5 02C4

00D7 7004

00D9 3480

моч

AL, [S1]

AL, 80H

SUB

AL, AH

J_122

AL, 80H

[BX], AL

ADD

2 4 6

247

10

XOR

2 4 9

2 5 0

00DB 8807

MOV

J_122:

0 0 D D

00DD C3

RET

2 5 2

2 5 3

; * * * * * Square_Root (W)

Square_Root (DS:S1) => (DS:S1)

255

256

Square_Root_W:

OODE

OODE SBDE

моч

BX. SI

258

: **** Square_Root

Square_Root (DS:S1) => (DS:BX)

260

00E0

00E0 F6440801

00E4 75B8

Square_Root;

2 6 1

byte ptr [51+8]. 1

ENZAN_ERROR ;

TEST

; (DS:SI) <0

263

JNZ

264

00E6 E83600

CALL

MEM_to_DAU_X

266

00E9 8A24

00EB 22E4

00ED 7414

00EF 80F480

00F2 32C0

00F4 D1F8

00F6 80F480

267

моч

AH, [S1]

AND

AH. AH

269

270

J_123

AH, 80H

1 Z

XOR

XOR

AL. AL

272

SAR

AX, I

XOR

AIL BOH

: DAU X SORT

00F9 D0E8

00FB D0E8

275

SHR

AL. 1

SHR

AL. 1

00FD DOE8

00FF 0C0E

0101 E632

SHR

AL. I

AL. DEH

DAU_COMMAND. AL

: AL - DE/1E

278

OR

OUT

; EXP STORE

J_123:

0103 8827

2 8 1

[BX]. AH

2 8 2

0105 E85600

0108 E83100

010B C3

DAU_READY_TEST

DAU_X_ 1 o _ MEM

CALL

CALL

2 8 5

```

```

LOC OBJ

LINE

SOURCE

287

288 +1 SEJECT

290

291

292

MEM to DAU (X, Y) ====

(DS:S1) =>DAUX, (ES:D1) =>DAUY

0 1 0 C

MEM_to_DAU_XY:

010C E81000

294

CALL

MEM_to_DAU_X

010F

296

MEM_ to_DAU_Y;

DS

CX. ES

DS, CX

SI, DI

010F 1E

0110 8CC1

297

298

PUSH

0112 8ED9

0114 87F7

299

300

MOV

XCHG

: ES -> DS

0116 B0A0

0118 E80C00

302

303

MOV

AL, OAOH

MEM_Lo_DAU

DAU WRITE Y

CALL

304

011B 87F7

011D 1F

011E C3

3 0 5

3 0 6

XCHG

SI. DI

DS

POP

3 0 7

3 0 8

309

3 1 0

MEN to DAU (X)

311

(DS:SI) =>DAUX

0 1 1 F

0 1 1 F B 0 0 2

0 1 2 1 E 6 3 0

MEM_ to_DAU_X:

313

MOV

: DAU ISDIGIT

OUT

DAU_DIGIT, AL

0 1 2 3 9 0

0 1 2 4 9 0

316

NOP

DELAY FOR DAU_7031

317

NOP

319

0125 B080

MOV

3 2 0

; DAU WRITE X

AL. 80H

MEM_ to_DAU:

3 2 1

0127 E634

OUT

DAU_DIRECTION, AL

323

0 1 2 9 8 3 C 6 0 8

0 1 2 C F D

0 1 2 D A C

0 1 2 E 2 4 F 0

0 1 3 0 E 6 3 6

ÁDD

51. 8

STD

LODSB

3 2 6

3 2 7

AND

AL. OFOR

3 2 8

OUT

DAU_WRITE_DATA, AL

329

0132 B90700

йои

CX. 7

331

332

333

334

335

;

J_131:

LODSB

OUT

LOOP

0135

0135 AC

0136 E636

0138 E2FB

DAU_WRITE_DATA, AL

J_131

3 3 6

3 3 7

3 3 8

013A FC

013B C3

ĊLD

RET

3 3 9

3 4 0

DAU (X)

to MEM

342

DAU (X) -> (DS: BX)

DAU_X_to_MEM:

013C

013C 1E

013D 07

013E 87FB

DS

3 4 5 3 4 6

POP

ΕS

XCHG

DI, BX

0140 B040

0142 E634

ώοv

AL, 40H

DAU_DIRECTION, AL

3 4 8

3 4 9

OUT

; DAU READ X

0144 83C708

0147 80250F

014A E436

014C 24F0

014E 0805

0150 4F

ÀDD

byte ptr [DI], DFH

AL, DAU_READ_DATA

AL, OFOH

[DI], AL

352

AND

1 א

3 5 4

AND

355

OR

3 5 6

REC

DI

3 5 7

3 5 8

3 5 9

0151 B90700

0154 FD

MOV

CX. 7

STD

3 6 0

0 1 5 5

0 1 5 5 E 4 3 6

0 1 5 7 AA

0 1 5 8 E 2 F B

j_133:

361

ALL. DAU_READ_DATA

3.6.3

STOSB

3 6 4

LOOP

J_133

3 6 5

015A FC

3 5 6

ĊLD

015B 87FB

015D C3

367

XCIIC

DI, BX

RET

```

```

LOC OBJ LINE SOURCE

369 :

370 :

371 : **** DAU READY TEST ****

015E 373 DAU_READY_TEST:

015E 2430 374 IN AL. DAU_STATUS

0160 22C0 375 AND AL. AL

0162 78FA 376 JS DAU_READY_TEST

0164 C3 377 RET

378 :

379 :

380 :

381 +1 $EJECT

```