### **OVERVIEW**

The SM8760CA is a compact clock generator IC with 4-times multiplication clock signal output that has a spread spectrum (SS) function to reduce undesirable EMI radiation. The SM8760CA has built-in crystal oscildator circuit, PLL, and loop filter. It accepts an input clock signal, generated using an external crystal or direct external clock input, and outputs 1 SS-modulated 4-times multiplication clock signal and 1 unmodulated reference signal. In addition, the SM8760CA features control pins to select SS modulation function ON/OFF and power-down modes.

### **FEATURES**

- Spread spectrum clock output to reduce EMI

- Modulation rate: Center spread: ± 1.0%

- Input frequency

- Using crystal element connection: 12.75MHz (fundamental frequency)

- Using external input clock: 12.75MHz

- Multiplication: 4-time multiplication

- Operating supply voltage:  $3.3 \pm 0.3$ V

- Low jitter: 350ps typ (Cycle-to-Cycle)

- Functions: Power-down function, SS modulation ON/OFF

- Mode control pins: Pull-up resistors built-in

- Package: 8-pin VSOP

### **APPLICATIONS**

- Printer (laser/inkjet)

- Photocopiers, scanners

- LCD/PDP displays

- Projectors

- Miscellaneous electronic equipment

### ORDERING INFORMATION

| Device    | Package    |

|-----------|------------|

| SM8760CAV | 8-pin VSOP |

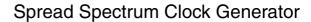

### **PINOUT**

(Top view)

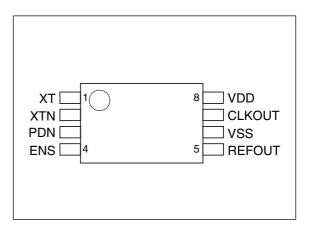

### PACKAGE DIMENSIONS

(Unit: mm)

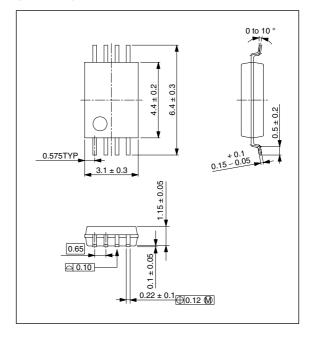

# **BLOCK DIAGRAM**

## **PIN DESCRIPTION**

| Number | Name   | I/O | Function                                                       |  |  |

|--------|--------|-----|----------------------------------------------------------------|--|--|

| 1      | XT     | I   | Crystal oscillator element connection or external clock input  |  |  |

| 2      | XTN    | 0   | Crystal oscillator element connection                          |  |  |

| 3      | PDN    | I   | Power-down control (with built-in pull-up resistor)            |  |  |

| 4      | ENS    | I   | SS modulation function ON/OFF (with built-in pull-up resistor) |  |  |

| 5      | REFOUT | 0   | Reference clock output                                         |  |  |

| 6      | VSS    | GND | Ground                                                         |  |  |

| 7      | CLKOUT | 0   | SS clock output                                                |  |  |

| 8      | VDD    | PWR | Supply voltage                                                 |  |  |

## **SPECIFICATIONS**

# **Absolute Maximum Ratings**

| Parameter                 | Symbol           | Rating                        | Unit |

|---------------------------|------------------|-------------------------------|------|

| Supply voltage range      | V <sub>DD</sub>  | -0.3 to +6.5                  | V    |

| Input voltage range       | V <sub>IN</sub>  | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Output voltage range      | V <sub>OUT</sub> | -0.3 to V <sub>DD</sub> + 0.3 | V    |

| Power dissipation         | P <sub>D</sub>   | 150                           | mW   |

| Storage temperature range | T <sub>STG</sub> | -55 to +125                   | °C   |

# **Recommended Operating Conditions**

$V_{SS} = 0V$  unless otherwise noted.

| Devenueter                  | Comple at         | O am distant                          | Rating |       |      | l lada |

|-----------------------------|-------------------|---------------------------------------|--------|-------|------|--------|

| Parameter                   | Symbol            | Condition                             | min    | typ   | max  | Unit   |

| Supply voltage range        | V <sub>DD</sub>   |                                       | +3.0   | -     | +3.6 | V      |

| Output load capacitance     | CL                | CLKOUT, REFOUT output pins            | -      | -     | 15   | pF     |

| Master clock frequency      | f <sub>XTAL</sub> | Crystal oscillator element connection | -      | 12.75 | _    | MHz    |

|                             |                   | External clock input                  | -      | 12.75 | -    |        |

| Operating temperature range | T <sub>OPR</sub>  |                                       | -20    | -     | +80  | °C     |

## **ELECTRICAL CHARACTERISTICS**

# **DC Characteristics**

$V_{DD}$  = 3.3 ± 0.3V,  $V_{SS}$  = 0V, Ta = -20 to +80°C,  $f_{XTAL}$  = 12.75MHz unless otherwise noted.

| Parameter           | Symbol           | Pins                | Condition                                                                                      | Rating                |     |                     | Unit  |  |

|---------------------|------------------|---------------------|------------------------------------------------------------------------------------------------|-----------------------|-----|---------------------|-------|--|

| raiailletei         | Symbol           | Joi Filis Condition |                                                                                                | min                   | typ | max                 | Jille |  |

| Current consumption | I <sub>DD</sub>  | VDD                 | V <sub>DD</sub> = 3.3V, Ta = 25°C, crystal oscillator element connection, all outputs unloaded | -                     | 9   | 14                  | mA    |  |

|                     | V <sub>IH1</sub> | PDN, ENS            | V <b>-</b> 2 2V                                                                                | 0.85V <sub>DD</sub>   | -   | -                   | V     |  |

| Input voltage       | V <sub>IL1</sub> | FDIN, LING          | $V_{DD} = 3.3V$                                                                                | -                     | -   | 0.15V <sub>DD</sub> |       |  |

| input voltage       | V <sub>IH2</sub> | XT                  | V <sub>DD</sub> = 3.3V                                                                         | 0.80V <sub>DD</sub>   | -   | _                   |       |  |

|                     | V <sub>IL2</sub> |                     |                                                                                                | -                     | -   | 0.20V <sub>DD</sub> |       |  |

|                     | I <sub>IH1</sub> | PDN, ENS            | V <sub>IN</sub> = V <sub>DD</sub> , built-in pull-up resistor                                  | -                     | -   | 1                   |       |  |

| Innut augrent       | I <sub>IL1</sub> | FDIN, EINS          | V <sub>IN</sub> = 0V, built-in pull-up resistor                                                | -100                  | -   | -                   |       |  |

| Input current       | I <sub>IH2</sub> | XT -                | $V_{IN} = V_{DD}$                                                                              | -                     | -   | 40                  | μΑ    |  |

|                     | I <sub>IL2</sub> |                     | V <sub>IN</sub> = 0V                                                                           | -40                   | -   | -                   |       |  |

| Output valtage      | V <sub>OH</sub>  | All outputs         | I <sub>OH</sub> = -2mA                                                                         | V <sub>DD</sub> - 0.4 | -   | -                   | V     |  |

| Output voltage      | V <sub>OL</sub>  | excluding XTN pin   | I <sub>OL</sub> = 2mA                                                                          | _                     | -   | 0.4                 | V     |  |

### **AC Characteristics**

$V_{DD} = 3.3 \pm 0.3 \text{V}$ ,  $V_{SS} = 0 \text{V}$ ,  $\text{Ta} = -20 \text{ to } +80 ^{\circ}\text{C}$  unless otherwise noted.

| Parameter                                 | Symbol          | Pins                                                                                                     | Condition                                                                                                       | Rating |       |     | Unit  |

|-------------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------|--------|-------|-----|-------|

| raiailletei                               | Syllibol        | Filis                                                                                                    | Condition                                                                                                       | min    | typ   | max | O'III |

| Cleak fraguency                           |                 | , ),-                                                                                                    | Crystal connection                                                                                              | -      | 12.75 | -   |       |

| Clock frequency                           | f <sub>in</sub> | XT                                                                                                       | External clock input*1                                                                                          | -      | 12.75 | -   | MHz   |

| Output clock rise time*2                  | t <sub>r</sub>  | CLKOUT,<br>REFOUT                                                                                        | $C_L$ = 15pF, $V_{OL}$ = 0.2 $V_{DD}$ to $V_{OH}$ = 0.8 $V_{DD}$ transition time                                | -      | 2.0   | -   | ns    |

| Output clock fall time*2                  | t <sub>f</sub>  | CLKOUT,<br>REFOUT                                                                                        | $C_L$ = 15pF, $V_{OH}$ = 0.8 $V_{DD}$ to $V_{OL}$ = 0.2 $V_{DD}$ transition time                                | -      | 2.0   | -   | ns    |

| Output clock jitter*2 t <sub>jitter</sub> |                 | REFOUT                                                                                                   | 1-sigma jitter, Ta = 25°C, $C_L$ = 15pF, $V_O$ = 0.5 $V_{DD}$                                                   | -      | 25    | _   |       |

|                                           | NEI OOT         | Peak-to-peak jitter, Ta = 25 $^{\circ}$ C,<br>C <sub>L</sub> = 15pF, V <sub>O</sub> = 0.5V <sub>DD</sub> | -                                                                                                               | 180    | -     | ps  |       |

|                                           |                 | CLKOUT                                                                                                   | Cycle-to-cycle jitter, Ta = $25^{\circ}$ C,<br>C <sub>L</sub> = $15$ pF, V <sub>O</sub> = $0.5$ V <sub>DD</sub> | -      | 350   | -   |       |

| Output clock duty cycle*2                 | Dt              | CLKOUT,<br>REFOUT                                                                                        | Ta = 25°C, $C_L$ = 15pF, $V_O$ = 0.5 $V_{DD}$                                                                   | 45     | 50    | 55  | %     |

| Power-up time*2,*3                        | t <sub>p</sub>  | CLKOUT,<br>REFOUT                                                                                        |                                                                                                                 | -      | 1     | 5   | ms    |

<sup>\*1.</sup> When using an external clock input, it is recommended that the clock on XT have 50% duty and V<sub>DD</sub> level signal amplitude. Note that the input signal voltage must not exceed the absolute maximum rating, otherwise it may cause the device to breakdown.

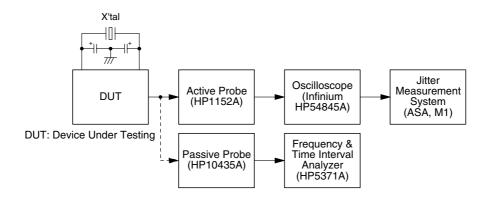

Figure 1. Measurement circuit

<sup>\*2.</sup> Measured using the circuit in Figure 1 on the NPC standard evaluation board.

<sup>\*3.</sup> The power-up time is the time from when the supply reaches 3.0V after the supply is turned ON until each output clock reaches its designated frequency to within ± 0.1%.

#### **FUNCTIONAL DESCRIPTION**

#### **Master Clock**

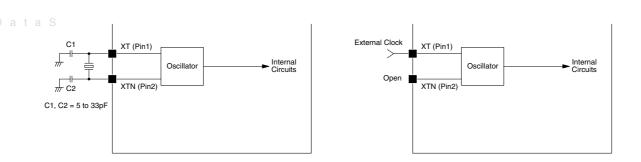

The SM8760CA master clock can be generated by the crystal oscillator formed by connecting a crystal (fundamental mode) between XT (pin 1) and XTN (pin 2) as shown in Figure 2. Alternatively, an external master clock can be input directly on XT (pin 1) as shown in Figure 3. If an external clock is input on XT, it is recommended that the clock have 50% duty and  $V_{DD}$  level voltage amplitude. Note that the input clock amplitude voltage must not exceed the absolute maximum rating, otherwise it may cause the SM8760CA to breakdown.

Figure 2. Crystal element connection

Figure 3. External clock input

### **Function Controls**

The SM8760CA power-down and SS modulation ON/OFF functions are controlled using the PDN and ENS input pins as shown in Table 1.

The power-down function is controlled using the PDN input pin. When PDN (pin 3) is "H", normal operating mode is selected. When PDN is "L", power-down mode is selected. In power-down mode, the CLKOUT and REFOUT output pins are in a high impedance state.

The SS modulation function is controlled using the ENS input pin. When ENS (pin 4) is "H", the SS modulation function is ON, and an SS-modulated clock is output on the CLKOUT pin. When ON, the modulation mode and amplitude is a fixed center spread modulation  $\pm$  1.0%. When ENS is "L", the SS modulation function is OFF.

Table 1. Function summary

| PDN (Pin 3) | ENS (Pin 4) | Power Down | Output (Pin 5, Pin 7) | SS ON/OFF | SS Mode       | SS Modulation [%] |

|-------------|-------------|------------|-----------------------|-----------|---------------|-------------------|

| Н           | Н           | OFF        | Clock out             | ON        | Center spread | ± 1.0             |

| Н           | L           | OFF        | Clock out             | OFF       | -             | 0.0               |

| L           | Н           | ON         | ON Hi-Z               |           |               |                   |

| L           | L           | ON         | 111-2                 | _         | _             | _                 |

Note. "H" signal represents  $V_{DD}$  level, and "L" represents  $V_{SS}$  level.

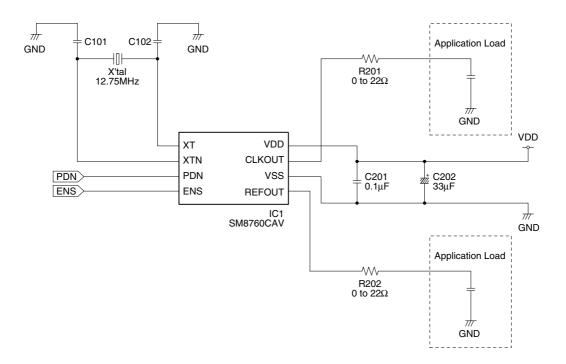

## **Typical Connection Circuit**

A typical connection circuit diagram is shown in Figure 4.

- 1) The SM8760CA oscillator circuit between XT and XTN has a built-in feedback resistor (approximately  $250k\Omega$ ).

- 2) The oscillator circuit capacitances C101 and C102 connected to XTN and XT, to match the crystal load capacitor.

- 3) R201 and R202 are impedance matching resistor for board pattern.

- 4) C201 and C202 are bypass capacitors inserted between the supply voltage lines. C201 is a 0.1μF (approximately) multi-layer ceramic capacitor connected directly alongside the www.DataSheet4U.conSM8760CA.

C202 is a 33µF (approximately) electrolytic capacitor.

Figure 4. Typical connection circuit

Note. This is a sample connection diagram only, and its use is not a guarantee of SM8760CA device characteristics.

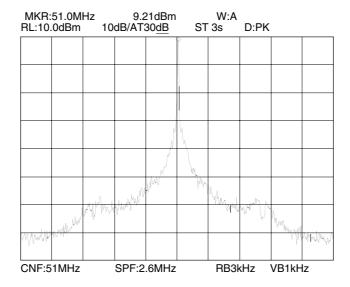

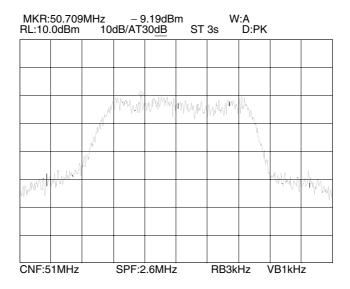

## **CLKOUT Output Spectrum Sample**

A sample SM8760CA CLKOUT output spectrum is shown in Figure 5.

(a) ENS = "L", SS OFF

(b) ENS = "H", SS  $\pm$  1.0%

Figure 5. Output spectrum sample

Note. These spectrum diagrams were obtained using the NPC evaluation board. These spectrum diagrams are not guaranteed SM8760CA device characteristics.

www.DataSheet4U.co

www.DataSheet4LL.com

Please pay your attention to the following points at time of using the products shown in this document.

The products shown in this document (hereinafter "Products") are not intended to be used for the apparatus that exerts harmful influence on human lives due to the defects, failure or malfunction of the Products. Customers are requested to obtain prior written agreement for such use from SEIKO NPC CORPORATION (hereinafter "NPC"). Customers shall be solely responsible for, and indemnify and hold NPC free and harmless from, any and all claims, damages, losses, expenses or lawsuits, due to such use without such agreement. NPC reserves the right to change the specifications of the Products in order to improve the characteristic or reliability thereof. NPC makes no claim or warranty that the contents described in this document dose not infringe any intellectual property right or other similar right owned by third parties. Therefore, NPC shall not be responsible for such problems, even if the use is in accordance with the descriptions provided in this document. Any descriptions including applications, circuits, and the parameters of the Products in this document are for reference to use the Products, and shall not be guaranteed free from defect, inapplicability to the design for the mass-production products without further testing or modification. Customers are requested not to export or re-export, directly or indirectly, the Products to any country or any entity not in compliance with or in violation of the national export administration laws, treaties, orders and regulations. Customers are requested appropriately take steps to obtain required permissions or approvals from appropriate government agencies.

#### SEIKO NPC CORPORATION

15-6, Nihombashi-kabutocho, Chuo-ku, Tokyo 103-0026, Japan Telephone: +81-3-6667-6601 Facsimile: +81-3-6667-6611 http://www.npc.co.jp/ Email: sales@npc.co.jp

NC0401BE 2006.04