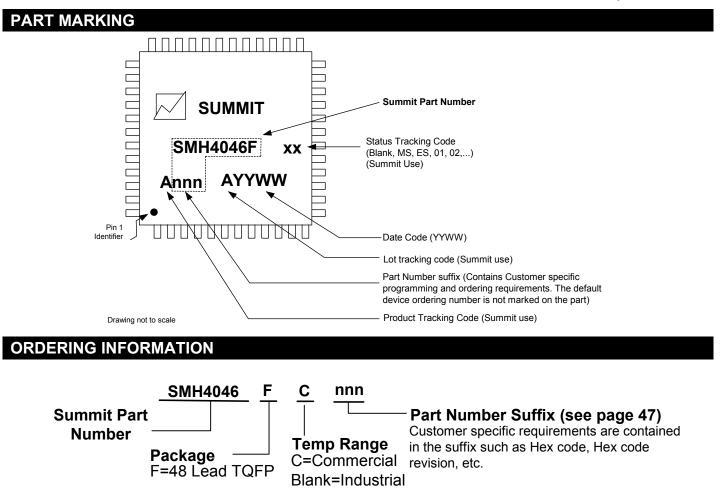

Preliminary Information <sup>1</sup> (See Last Page)

## Hot-Swap, Active DC Output Control (ADOC<sup>™</sup>) Power Manager with I<sup>2</sup>C Interface

## **FEATURES & APPLICATIONS**

- Full voltage Control for hot-swap applications

- Add-in Card insertion detection

- Platform voltage detection

- Universal FPGA configuration I/O pins

- High Voltage and logic level enable outputs

- Active control (ADOC<sup>™</sup>) for three downstream DC/DC converters with ±0.5% accuracy

- Margining of three DC/DC converters

- Power-up sequencing of all supply voltages

- Power-down sequencing in Forward or Reverse

- UV and OV sensors per channel with programmable reset and interrupt

- Programmable glitch filter for all channels

- Configuration may be locked

- Auto monitoring of all channels and Ext Temp

- I<sup>2</sup>C<sup>™</sup> serial bus interface

- Programmable slew rate control

- Integrated 2K EEPROM

- Applications

- Monitor/Control Distributed and POL Supplies

- Multi-voltage Processors, DSPs, ASICs used in Telecom or server systems

## INTRODUCTION

The SMH4046 is an all-inclusive power management controller that integrates hot swap protection of three positive-voltage supplies (+12V or less). In addition to hot swapping three bus voltages, it provides sequencing and Active DC Output Control (ADOC<sup>™</sup>) of three on-card DC-DC converters as used in blade servers and Telecom systems. It can also upload configuration code from the host to on-card FPGAs.

All six channels can cascade-sequence during powerup in any order as set by either hardware or firmware; and sequence down in forward or reverse order. ADOC<sup>TM</sup> control of the three DC/DC converters maintains their accuracy to within  $\pm 0.5\%$  of the set point using an internal voltage reference. ADOC<sup>TM</sup> is also included during "margining" to allow card-by-card performance evaluation during production with arbitrary setting within  $\pm 10\%$  in any combination.

A full set of monitoring and control features are included, with user programmability that can be locked. The SMH4046 uses the  $I^2C$  bus interface for programming and FPGA configuration.

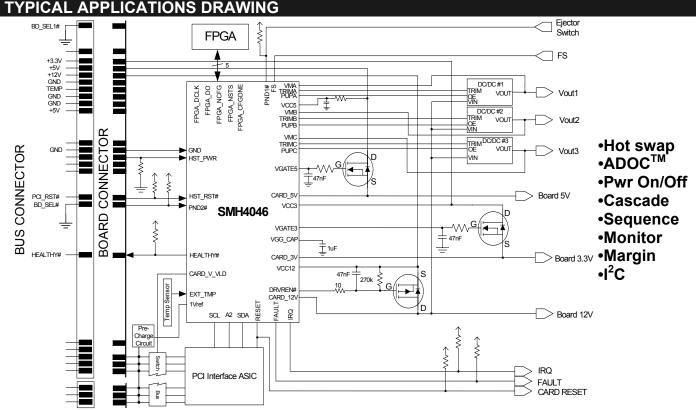

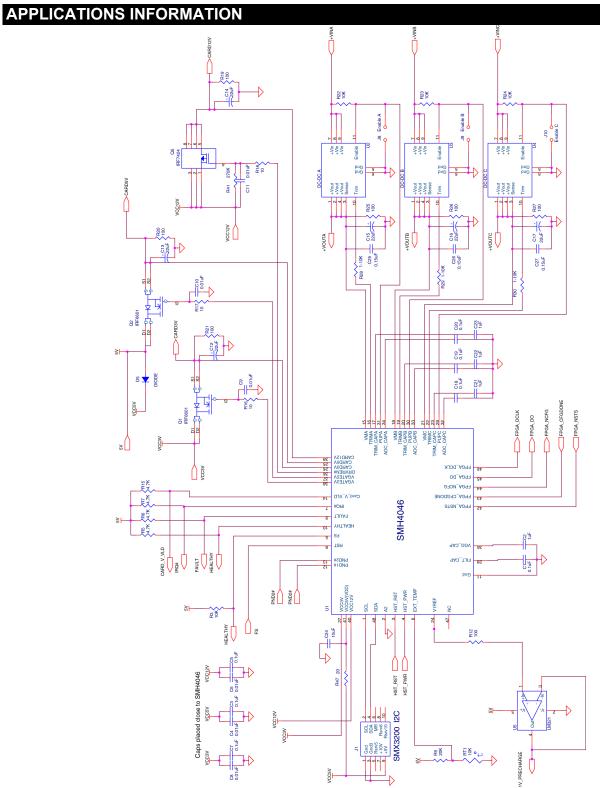

Figure 1 – Applications Schematic using the SMH4046 Controller to hot swap and actively control the output levels of three DC/DC Converters while providing power on/off, cascade sequencing and output margining. Note: This is an applications example only. Some pins, components and values are not shown.

© SUMMIT Microelectronics, Inc. 2004 • 1717 Fox Drive • San Jose CA 95131 • Phone 408 436-9890 • FAX 408 436-9897 The Summit Web Site can be accessed by "right" or "left" mouse clicking on the link: http://www.swww.DataSheet4U.com 2082 1.7 08/23/04

### GENERAL DESCRIPTION

The SMH4046 is a fully integrated hot swap controller intended for use on add-in cards that are hot swapped from powered-on host platforms. The SMH4046 performs a variety of tasks starting with the validation of proper card insertion and the presence of "in-spec" voltages at the host platform interface.

Once the SMH4046 switches power on, it continues to monitor the back-end power to the add-in card and the host power supply. When programmed to do so, the SMH4046 immediately asserts the RESET outputs and powers-down the add-in card when the 12V, 5V or 3.3V supplies drop below a programmable UV or above an OV threshold.

In addition to the power control for the add-in card, the SMH4046 provides status signals that can be employed by the host for the control of bus interface components.

On-chip EEPROM memory can be used to store serial ID numbers or other pertinent information for the individual card or as general-purpose memory. The FPGA configuration-interface provides a direct interface for simplified access to the add-in card's FPGAs using the  $I^2C$  interface.

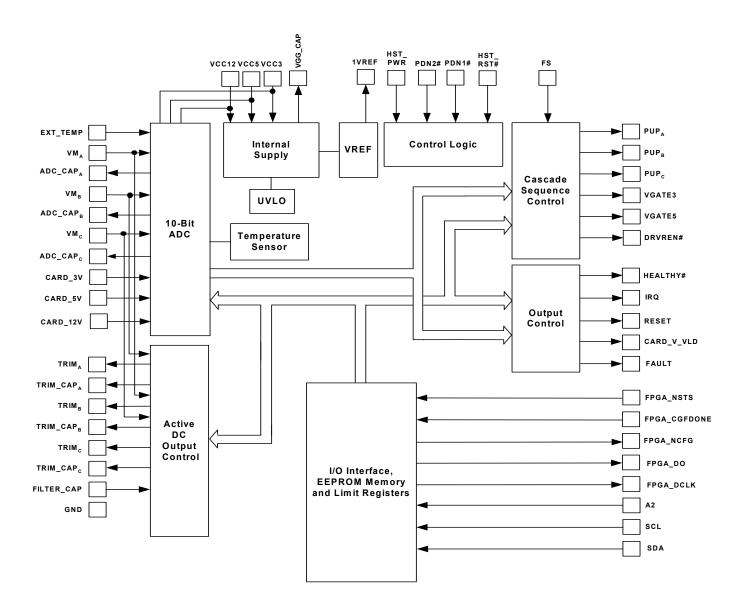

The SMH4046 has the ability to monitor and sequence up to six power supplies (Figure 1). The SMH4046 can monitor the 12V input and the internal and external temperature sensors. The SMH4046 has four operating modes: Power-on sequencing mode, monitor and control mode using Active DC Output Control (ADOC), supply margining mode using ADOC, and Power-off sequencing mode.

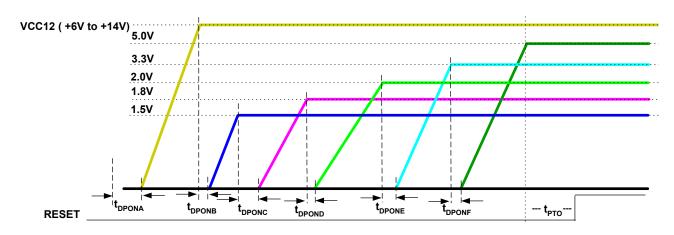

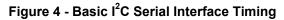

Power-on sequencing can be initiated via the HST PWR pin or through the serial interface. In this mode, the SMH4046 sequences the power supply channels on in any order by activating the PUPx, VGATE and DRVREN# outputs while monitoring the respective converter and host voltages to ensure correct cascading of the supplies. Cascadesequencing is the ability to hold off the next sequenced supply until the previous supply reaches a programmed threshold voltage (See Figure 2). A programmable sequence termination timer can be set to disable all channels if the power-on sequence stalls. During this mode, the HEALTHY# output remains inactive and the RESET output remains active. When the HEALTHY# output is true and RESET is false, that signals the end of power-on sequencing mode.

Once the Power-on sequencing mode is complete, the SMH4046 enters monitor control mode. Once all supplies have sequenced on and the voltages are above the UV settings, the Active DC Output Control (ADOC), if enabled, brings the three DC-DC converter supply output voltages to their programmed nominal settings and adjusts the output voltage under all load conditions. This feature is especially useful for supplies without sense lines as the monitor VMx pins can be routed and sense variations at the load. Typical converters have  $\pm 2$  to  $\pm 5\%$  accuracy output voltage ratings. The Active DC Output Control feature of the SMH4046 increases the accuracy to  $\pm 0.5\%$ .

## **GENERAL DESCRIPTION (CONTINUED)**

The device also triggers outputs by monitoring fault conditions. The 10-bit ADC cycles through all channels every 2 ms and checks the conversions against the programmed threshold limits. The results can be used to trigger the RESET, HEALTHY# and FAULT outputs as well as to trigger a power-off or a force- shutdown operation.

While the SMH4046 is in monitoring mode, a serial interface command to margin the supply voltages can bring the part into margining mode. In margining mode the SMH4046 can margin the three supply voltages in any combination of nominal, high or low voltage settings using the ADOC feature, all to within  $\pm 0.5\%$ . The margin high and margin low voltage settings can range from 0.9V to the overvoltage limit of the DC-DC converters and depends on the margin range of the converters. During this mode the HEALTHY# output is always active and the RESET output is always inactive regardless of the voltage threshold limit settings and triggers. Furthermore, the triggers for power-off and force-shutdown are temporarily disabled.

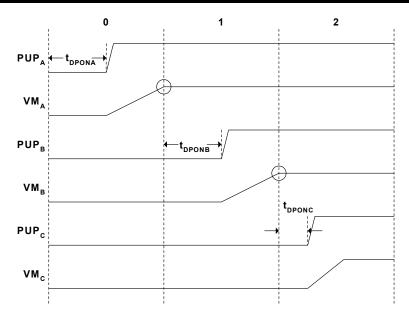

The power-off sequencing mode can only be entered while the SMH4046 is in the monitoring mode. It can be initiated by either bringing the HST\_PWR pin inactive, through the serial interface control, or triggered by a channel exceeding its programmed thresholds. Once power-off is initiated, active DC control is disabled, and the PUP outputs are sequenced off in either the same or reverse order as power-on sequencing. Monitoring of the supply voltages continues to ensure cascading of the supplies as they turn off. The sequence termination timer can be programmed to immediately disable all channels if the power-off sequencing stalls. The RESET output remains active throughout this mode while the HEALTHY# output remains inactive.

The CARD\_3V and CARD\_5V monitor pins are also used to detect overcurrents on the card side 3V and 5V supply. The FAULT pin is a programmable active high/low open drain fault output that is asserted by the SMH4046 when a programmed fault condition occurs on the internal/external temperature sensor. If programmed to do so, FAULT is asserted whenever an over-current condition is detected. Fault will be released at the same time that the VGATE outputs are turned back on after a reset from the host on the HST\_PWR pin. Programming is accomplished by using the I<sup>2</sup>C serial bus interface.

## INTERNAL FUNCTIONAL BLOCK DIAGRAM

Figure 3 – Internal Functional Block Diagram

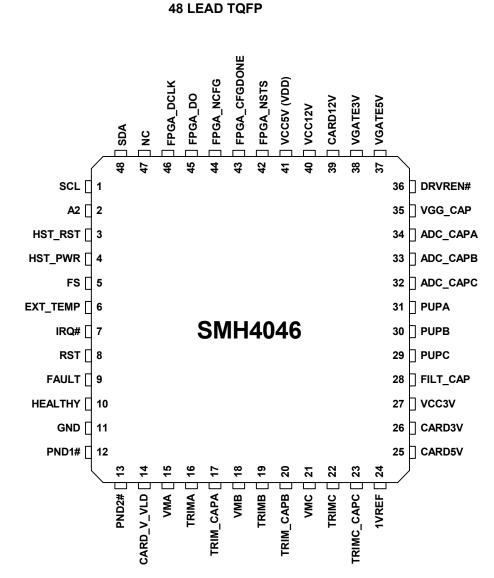

# PIN DESCRIPTIONS

| Symbol      | Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                           |  |  |

|-------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| SCL         | 1   | I    | The I <sup>2</sup> C serial bus clock.                                                                                                                                                                                                                                                                                                                                                                                |  |  |

| A2          | 2   | I    | An external address bit for I <sup>2</sup> C.                                                                                                                                                                                                                                                                                                                                                                         |  |  |

| HST_RST     | 3   | I    | Host reset. This input is the reset signal from the host interface. Asserting this pin causes a reset sequence to be performed on the card. Programmable polarity.                                                                                                                                                                                                                                                    |  |  |

| HST_PWR     | 4   | I    | Host power-up enable. This input provides the host system with active control over the sequencing of the power up operation. When de-asserted, the SMH4046 holds the add-in card in reset and blocks all power to the back-end logic. When HST_PWR is asserted, the power sequencing begins immediately and the reset output is driven active after the time tPURST. Programmable polarity.                           |  |  |

| FS          | 5   | I    | Force Shutdown. This programmable active high/low input is used to immediately turn off all converter enable signals and external FETs.                                                                                                                                                                                                                                                                               |  |  |

| EXT_TEMP    | 6   | I    | This input can be used to sense a voltage generated from an external temperature monitoring device.                                                                                                                                                                                                                                                                                                                   |  |  |

| IRQ#        | 7   | 0    | Active low Interrupt output. Generated by the SMH4046 on an error condition.<br>This signal can be used by external logic to interrupt the host.                                                                                                                                                                                                                                                                      |  |  |

| RESET (RST) | 8   | 0    | ESET is a programmable active high/low open drain output that is asserted y the SMH4046 when a programmed reset condition occurs.                                                                                                                                                                                                                                                                                     |  |  |

| FAULT       | 9   | 0    | AULT is a programmable active high/low open drain fault output that is asserted by the SMH4046 when a programmed fault condition occurs.                                                                                                                                                                                                                                                                              |  |  |

| HEALTHY     | 10  | 0    | Healthy is a programmable active high/low open drain output that is asserted by the SMH4046 when all programmed healthy conditions are met.                                                                                                                                                                                                                                                                           |  |  |

| GND         | 11  | PWR  | Ground.                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |

| PND1#       | 12  | I    | Pin detect 1 is an active low CMOS level input. In conjunction with PND2#, this signal indicates proper card insertion when taken low. This pin must be connected to ground on the host side of the connector. PND1# and PND2# should be placed on opposite corners of the connector and will preferably be staggered shorter than the power connector pins. Board insertion is assumed when PND1# and PND2# are low. |  |  |

| PND2#       | 13  | I    | Pin detect 2 is an active low CMOS level input. In conjunction with PND1#, this signal indicates proper card insertion when taken low. This pin must be connected to ground on the host side of the connector. PND1# and PND2# should be placed on opposite corners of the connector and will preferably be staggered shorter than the power connector pins. Board insertion is assumed when PND1# and PND2# are low. |  |  |

| CARD_V_VLD  | 14  | 0    | Card voltage valid. This open drain output indicates that the card side voltages are at or above their respective trip levels. Active high.                                                                                                                                                                                                                                                                           |  |  |

| VMA         | 15  | I    | Positive converter sense line for DC/DC converter A                                                                                                                                                                                                                                                                                                                                                                   |  |  |

| TRIMA       | 16  | 0    | Output voltage used to control the output of DC/DC converter A.                                                                                                                                                                                                                                                                                                                                                       |  |  |

| TRIM_CAPA   | 17  | I    | External sample and hold capacitor input used to set the voltage on the TRIMA pin.                                                                                                                                                                                                                                                                                                                                    |  |  |

# PIN DESCRIPTIONS (CONTINUED)

| Symbol    | Pin | Туре | Description                                                                                                                                                                                                                                                                                                                                                                                                                          |  |

|-----------|-----|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| VMB       | 18  | I    | Positive converter sense line for DC/DC converter B                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TRIMB     | 19  | 0    | Output voltage used to control the output of DC/DC converter B.                                                                                                                                                                                                                                                                                                                                                                      |  |

| TRIM_CAPB | 20  | I    | External sample and hold capacitor input used to set the voltage on the TRIMB pin.                                                                                                                                                                                                                                                                                                                                                   |  |

| VMC       | 21  | I    | Positive converter sense line for DC/DC converter C                                                                                                                                                                                                                                                                                                                                                                                  |  |

| TRIMC     | 22  | 0    | Output voltage used to control the output of DC/DC converter C.                                                                                                                                                                                                                                                                                                                                                                      |  |

| TRIM_CAPC | 23  | I    | External sample and hold capacitor input used to set the voltage on the TRIMC pin.                                                                                                                                                                                                                                                                                                                                                   |  |

| 1VREF     | 24  | 0    | This output provides a 1V reference for pre-charging the CompactPCI bus signal pins.                                                                                                                                                                                                                                                                                                                                                 |  |

| CARD_5V   | 25  | I    | 5V card side supply input. This input is monitored for power integrity. If it falls below the 5V sense threshold, the CARD_V_VLD signal is de-asserted.                                                                                                                                                                                                                                                                              |  |

| CARD_3V   | 26  | I    | 3.3V monitor input from the line card. This input is monitored for power integrity. If it falls below the 3.3V sense threshold, the CARD_V_VLD signal is de-asserted.                                                                                                                                                                                                                                                                |  |

| VCC3V     | 27  | I    | 3V host side supply input. This input is monitored for power integrity.                                                                                                                                                                                                                                                                                                                                                              |  |

| FILT_CAP  | 28  | I    | External capacitor input used to filter VMX inputs                                                                                                                                                                                                                                                                                                                                                                                   |  |

| PUPC      | 29  | 0    | Programmable active high/low open drain converter enable output for DC/DC converter C.                                                                                                                                                                                                                                                                                                                                               |  |

| PUPB      | 30  | 0    | Programmable active high/low open drain converter enable output for DC/DC converter B.                                                                                                                                                                                                                                                                                                                                               |  |

| PUPA      | 31  | 0    | Programmable active high/low open drain converter enable output for DC/DC converter A.                                                                                                                                                                                                                                                                                                                                               |  |

| ADC_CAPC  | 32  | I    | External capacitor input used to filter the VMC input to the 10-bit ADC.                                                                                                                                                                                                                                                                                                                                                             |  |

| ADC_CAPB  | 33  | I    | External capacitor input used to filter the VMB input to the 10-bit ADC.                                                                                                                                                                                                                                                                                                                                                             |  |

| ADC_CAPA  | 34  | I    | External capacitor input used to filter the VMA input to the 10-bit ADC.                                                                                                                                                                                                                                                                                                                                                             |  |

| VGG_CAP   | 35  | 0    | This pin supplies power for the high-side drivers. An external 1uF ceramic charge pump capacitor should be connected to VGG_CAP. VGG_CAP is a charge storage connection for the internal charge pump of the SMH4046. This capacitor should be of sufficient size to provide current to the VGATE outputs high side drivers under varying load conditions. For most applications this can be tied to a 1.0 $\mu$ F ceramic capacitor. |  |

| DRVREN#   | 36  | 0    | High-side driver enable used to switch on the 12V supply. Pulldown current of 100µA when on.                                                                                                                                                                                                                                                                                                                                         |  |

| VGATE5V   | 37  | 0    | 5V gate output. Slew rate limited high side driver output for the 5V external Power FET gate. Alternatively this can be used as a PUP output.                                                                                                                                                                                                                                                                                        |  |

| VGATE3V   | 38  | 0    | 3.3V gate output. Slew rate limited high side driver output for the 3.3V external Power FET gate. Alternatively, this can be used as a PUP output.                                                                                                                                                                                                                                                                                   |  |

# PIN DESCRIPTIONS (CONTINUED)

| Symbol           | Pin | Туре | Description                                                                                                                                               |  |

|------------------|-----|------|-----------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| CARD_12V         | 39  | I    | 12V card side supply input. This input is monitored for power integrity. If it falls below the 12V sense threshold, the CARD_V_VLD signal is de-asserted. |  |

| VCC12            | 40  | I    | s-side 12V input                                                                                                                                          |  |

| VCC5V (VDD)      | 41  | PWR  | This pin supplies power to the SMH4046 and is monitored for power integrity.                                                                              |  |

| FPGA_NSTS        | 42  | I    | FPGA configuration status input pin                                                                                                                       |  |

| FPGA_CFGD<br>ONE | 43  | I    | FPGA_CFGDONE indicates completion of the configuration process.                                                                                           |  |

| FPGA_NCFG        | 44  | 0    | FPGA_NCFG is a configuration control output. A low transition resets the target device; a low-to-high transition begins configuration.                    |  |

| FPGA_DO          | 45  | 0    | FPGA_DO provides preamble and configuration data to downstream devices in a daisy-chain.                                                                  |  |

| FPGA_DCLK        | 46  | 0    | FPGA Configuration clock output. Clock output used to clock configuration data using pin FPGA_DO.                                                         |  |

| NC               | 47  | NC   | No Connect                                                                                                                                                |  |

| SDA              | 48  | I/O  | The bidirectional I <sup>2</sup> C serial data line.                                                                                                      |  |

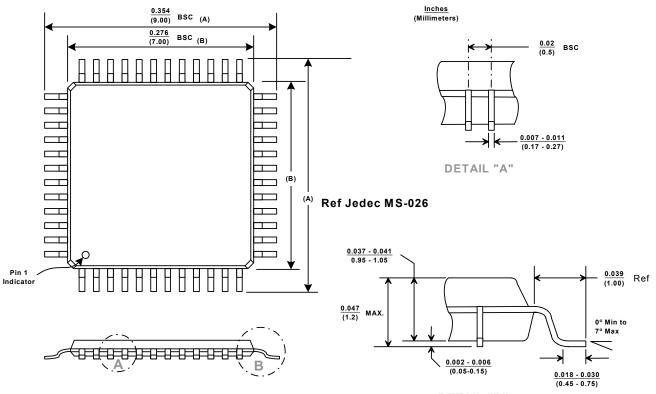

## PACKAGE AND PIN CONFIGURATION

Preliminary Information

### ABSOLUTE MAXIMUM RATINGS

| Temperature Under Bias                | °C |

|---------------------------------------|----|

| Storage Temperature65°C to 150°C      | °C |

| Terminal Voltage with Respect to GND: |    |

| VCC3/5 Supply Voltage0.3V to 6.0V     | 0V |

| VCC12 Supply Voltage0.3V to 15.0V     | 0V |

| Open Drain Outputs GND to 15.0V       |    |

| All OthersVDD + 0.7V                  | 7V |

| Output Short Circuit Current 100mA    | nΑ |

| Reflow Solder Temperature (30 secs)   | °C |

| Lead Solder Temperature (10 secs)     |    |

| Junction Temperature150°C             |    |

| ESD Rating per JEDEC2000V             | V  |

| Latch-Up testing per JEDEC±100mA      | ιA |

Note - The device is not guaranteed to function outside its operating rating. Stresses listed under Absolute Maximum Ratings may cause permanent damage to the device. These are stress ratings only and functional operation of the device at these or any other conditions outside those listed in the operational sections of the specification is not implied. Exposure to any absolute maximum rating for extended periods may affect device performance and reliability. Devices are ESD sensitive. Handling precautions are recommended.

### **RECOMMENDED OPERATING CONDITIONS**

| (Commercial)0°C to +70°C<br>VCC3V Supply Voltage2.7V to 5V |

|------------------------------------------------------------|

| VCC3V Supply Voltage 2 7V to 5V                            |

|                                                            |

| VCC5V Supply Voltage2.7V to 6V                             |

| VCC12V Supply Voltage                                      |

| VIN GND to VCC5                                            |

| VOUT GND to 15.0V                                          |

| Package Thermal Resistance ( $\theta_{JA}$ )               |

| 48 Lead TQFP80°C/W                                         |

Moisture Classification Level 1 (MSL 1) per J-STD- 020

#### **RELIABILITY CHARACTERISTICS**

| Data Retention | 100 Years      |

|----------------|----------------|

| Endurance      | 100,000 Cycles |

## DC OPERATING CHARACTERISTICS

| (Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND) |

|---------------------------------------------------------------------------------------------------|

|---------------------------------------------------------------------------------------------------|

| Symbol            | Parameter                                      | Notes                                                                    | Min       | Тур | Max       | Unit |

|-------------------|------------------------------------------------|--------------------------------------------------------------------------|-----------|-----|-----------|------|

| VCC3              | Supply Voltage Monitor                         | Not a supply input                                                       | 2.7       | 3.3 | 5.0       | V    |

| VCC5              | Supply Voltage                                 | VCC5 must be higher then<br>any other input except<br>VCC12 and CARD12V  | 2.7       | 5.0 | 6.0       | V    |

| VCC12             | Supply Voltage Monitor                         | Not a supply input                                                       | 6         | 12  | 14        | V    |

| VMx               | Positive sense voltage for VMA,<br>VMB and VMC |                                                                          | -0.3      |     | VCC5V     |      |

| I <sub>DD</sub>   | Power Supply Current                           | All TRIM pins floating                                                   |           | 3   | 5         | mA   |

| 1                 | TRIMA, TRIMB, TRIMC current                    | TRIMx pin sourcing current                                               | 1.5       |     |           | mA   |

| I <sub>TRIM</sub> |                                                | TRIMx pin sinking current                                                | 1.5       |     |           | mA   |

| V <sub>TRIM</sub> | Margin Control and ADOC Range                  | I <sub>TRIM</sub> ±1.5mA, Depends on<br>Trim range of DC-DC<br>Converter | GND       |     | VCC5V     | V    |

| V                 | Input High Voltage                             | VCC5V = 2.7V                                                             | 0.9xVCC5V |     | VCC5V     | V    |

| V <sub>IH</sub>   |                                                | VCC5V = 5.0V                                                             | 0.7xVCC5V |     | VCC5V     | V    |

| V                 |                                                | VCC5V = 2.7V                                                             |           |     | 0.1xVCC5V | V    |

| V <sub>IL</sub>   | Input Low Voltage                              | VCC5V = 5.0V                                                             |           |     | 0.3xVCC5V | V    |

| V <sub>OL</sub>   | Programmable Open Drain Outputs                | I <sub>SINK</sub> = 1mA                                                  |           | 0.2 |           | V    |

Preliminary Information

| DC OPER              | RATING CHARACTERISTICS                | (CONTINUED)                                                  |      | 1 1011 |       | Ionnation |

|----------------------|---------------------------------------|--------------------------------------------------------------|------|--------|-------|-----------|

| (Over reco           | mmended operating conditions, u       | nless otherwise noted. All volt                              |      |        |       |           |

| Symbol               | Parameter                             | Notes                                                        | Min  | Тур    | Max   | Unit      |

| VGATE                | VGATE3/5 Outputs                      |                                                              |      | 12     |       | V         |

| V <sub>SENSE</sub>   | Positive Sense Voltage                | VM pin                                                       | +0.3 |        | VCC5V | V         |

| V <sub>Monitor</sub> | Monitor Threshold Step Size           | VM pins                                                      |      | 5      |       | mV        |

| T <sub>Monitor</sub> | Temperature Threshold Step Size       | Internal Temp Sensor                                         |      | 1      |       | °C        |

| т                    | Internal Temperature Sensor           | Commercial Temp Range                                        | -3   |        | +3    | °C        |

| T <sub>SA</sub>      | Accuracy                              | Industrial Temp Range                                        | -5   |        | +5    | °C        |

| 1V <sub>ref</sub>    | 1V <sub>REF</sub> Output Voltage      | Optional data bus pre-charge output                          | 0.95 | 1.00   | 1.05  | V         |

| V <sub>REF</sub> ACC | Internal V <sub>REF</sub> Accuracy    |                                                              | -0.4 |        | +0.4  | %         |

| ADOC <sub>ACC</sub>  | ADOC/Margin Accuracy                  | $V_{SENSE} \leq 3.5V$                                        | -0.5 | ±0.3   | +0.5  | %         |

|                      |                                       | $V_{SENSE} \geq 3.5V$                                        | -1   | ±0.8   | +1    | %         |

|                      | Under Voltage Lockout                 | VDD_CAP Rising                                               |      | 2.6    |       | V         |

| UVLO                 | Threshold <sup>1</sup>                | VDD_CAP Falling                                              |      | 2.5    |       | V         |

| Note 1 - (100r       | nV typ Hysteresis)                    |                                                              |      |        |       |           |

| ADC chara            | octeristics                           |                                                              |      |        |       |           |

| N                    | Resolution                            |                                                              | 10   |        |       | Bits      |

| MC                   | Missing Codes                         | Minimum resolution for which no missing codes are guaranteed | 10   |        |       | Bits      |

| S/N                  | Signal-to-Noise Ratio                 | Conversion rate = 500Hz                                      |      | 72     |       | db        |

| DNL                  | Differential Non-Linearity            |                                                              | -1/2 |        | +1/2  | LSB       |

| INL                  | Integral Non-Linearity                |                                                              | -1   |        | +1    | LSB       |

| GAIN                 | Positive full scale gain error        |                                                              | -0.5 |        | +0.5  | %         |

| Offset               | Offset Error                          |                                                              | -1   |        | +1    | LSB       |

| ADC_TC               | Full Scale Temperature<br>Coefficient |                                                              |      | ±15    |       | PPM/°C    |

| IM <sub>ADC</sub>    | Analog ADC Input Impedance            | EXT_TEMP                                                     |      | 10     |       | MΩ        |

The formula for the total ADC inaccuracy is: [((ADC read voltage) +/- INL)\*(range of gain error)]+range of offset error

Preliminary Information

## AC OPERATING CHARACTERISTICS

Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND. See Figure 5A and 5B Timing diagrams.

| Symbol                  | Description                                                                       | Conditions                                           | Min | Тур                | Max | Unit |

|-------------------------|-----------------------------------------------------------------------------------|------------------------------------------------------|-----|--------------------|-----|------|

|                         |                                                                                   | t <sub>DOCT</sub> = 5.5 μs                           |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 8.5 μs                           |     |                    |     | %    |

|                         |                                                                                   | t <sub>DOCT</sub> = 11.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 14.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 17.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 20.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 23.5 μs                          |     |                    |     |      |

|                         | Programmable Over Current Trip                                                    | t <sub>DOCT</sub> = 26.5 μs                          | 45  |                    |     |      |

| t <sub>DOCT</sub>       | Delay Time                                                                        | t <sub>DOCT</sub> = 29.5 μs                          | -15 | t <sub>DOCT</sub>  | +15 |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 32.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 35.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 38.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 41.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 44.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 47.5 μs                          |     |                    |     |      |

|                         |                                                                                   | t <sub>DOCT</sub> = 50.5 μs                          | -   |                    |     |      |

|                         |                                                                                   | $t_{\text{DPON}} = 1 \text{ ms}$                     |     |                    |     |      |

|                         | Programmable Power-on delay from VM_X out-of-fault to $\mbox{PUP}_{\rm Y}$ active | t <sub>DPON</sub> = 20 ms                            | -15 | t <sub>DPON</sub>  | +15 | %    |

| t <sub>DPON</sub>       |                                                                                   | t <sub>DPON</sub> = 40 ms                            |     |                    |     |      |

|                         |                                                                                   | t <sub>DPON</sub> = 75 ms                            |     |                    |     |      |

| 4                       | Programmable Power-off delay from $VM_X$ off to $PUP_Y$ inactive                  | t <sub>DPOFF</sub> = 1 ms                            | -15 | t <sub>DPOFF</sub> | +15 |      |

|                         |                                                                                   | t <sub>DPOFF</sub> = 20 ms                           |     |                    |     | %    |

| t <sub>DPOFF</sub>      |                                                                                   | t <sub>DPOFF</sub> = 40 ms                           |     |                    |     |      |

|                         |                                                                                   | t <sub>DPOFF</sub> = 75 ms                           |     |                    |     |      |

|                         | Programmable Reset Time-Out<br>Period                                             | t <sub>PRTO</sub> = 1 ms                             | -15 | t <sub>PRTO</sub>  | +15 | %    |

| t <sub>PRTO</sub>       |                                                                                   | t <sub>PRTO</sub> = 40 ms                            |     |                    |     |      |

| PRIO                    |                                                                                   | t <sub>PRTO</sub> = 150 ms                           |     |                    |     |      |

|                         |                                                                                   | t <sub>PRTO</sub> = 300 ms                           |     |                    |     |      |

|                         | Programmable Sequence<br>Termination Timer                                        | $t_{STT}$ = 40 ms                                    |     | t <sub>stt</sub>   | +15 | %    |

| t <sub>s⊤⊤</sub>        |                                                                                   | $t_{STT} = 75 \text{ ms}$                            | -15 |                    |     |      |

| -511                    |                                                                                   | $t_{STT} = 150 \text{ ms}$                           |     |                    |     |      |

|                         |                                                                                   | t <sub>STT</sub> = 300 ms<br>Time for ADC conversion |     |                    |     |      |

| t <sub>ADC</sub>        | 10-bit ADC sampling period                                                        | of all 11 channels                                   |     | 2                  |     | ms   |

|                         |                                                                                   | Update period for Active                             |     |                    |     |      |

| t                       | Active DC Control sampling period                                                 | DC Control of channels                               |     | 1.7                |     | ms   |

| t <sub>DC_CONTROL</sub> | , leave be control camping period                                                 | A - C                                                |     | 1.7                |     | 1113 |

|                         |                                                                                   | Slow Margin, + 10%                                   |     |                    |     |      |

|                         |                                                                                   | change in voltage with                               |     | 050                |     |      |

|                         |                                                                                   | 0.1% ripple                                          |     | 850                |     | ms   |

| т                       | Margin Timo from Nominal                                                          | TRIM_CAP=1µF                                         |     |                    |     |      |

| Tmargin                 | Margin Time from Nominal                                                          | Fast Margin, <u>+</u> 10%                            |     |                    |     |      |

|                         |                                                                                   | change in voltage with                               |     | 85                 |     | me   |

|                         |                                                                                   | 0.1% ripple                                          |     |                    |     | ms   |

|                         |                                                                                   | TRIM_CAΡ=1μF                                         |     |                    |     |      |

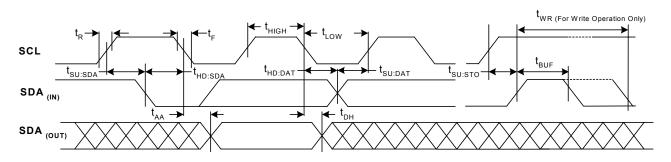

## I<sup>2</sup>C 2-WIRE SERIAL INTERFACE AC OPERATING CHARACTERISTICS – 100kHz

Over recommended operating conditions, unless otherwise noted. All voltages are relative to GND. See Figure 4 Timing Diagram.

| Symbol                       | Description                | Conditions                        |     |     |      |       |

|------------------------------|----------------------------|-----------------------------------|-----|-----|------|-------|

| Symbol                       | Description                |                                   |     | Тур | Max  | Units |

| f <sub>SCL</sub>             | SCL Clock Frequency        |                                   | 0   |     | 100  | KHz   |

| t <sub>LOW</sub>             | Clock Low Period           |                                   | 4.7 |     |      | μS    |

| t <sub>HIGH</sub>            | Clock High Period          |                                   | 4.0 |     |      | μS    |

| t <sub>BUF</sub>             | Bus Free Time              | Before New Transmission - Note 1/ | 4.7 |     |      | μS    |

| $t_{\text{SU:STA}}$          | Start Condition Setup Time |                                   | 4.7 |     |      | μS    |

| t <sub>HD:STA</sub>          | Start Condition Hold Time  |                                   | 4.0 |     |      | μS    |

| t <sub>SU:STO</sub>          | Stop Condition Setup Time  |                                   | 4.7 |     |      | μS    |

| t <sub>AA</sub>              | Clock Edge to Data Valid   | SCL low to valid SDA (cycle n)    | 0.2 |     | 3.5  | μS    |

| t <sub>DH</sub>              | Data Output Hold Time      | SCL low (cycle n+1) to SDA change | 0.2 |     |      | μS    |

| t <sub>R</sub>               | SCL and SDA Rise Time      | Note <u>1</u> /                   |     |     | 1000 | ns    |

| t <sub>F</sub>               | SCL and SDA Fall Time      | Note <u>1</u> /                   |     |     | 300  | ns    |

| t <sub>su:dat</sub>          | Data In Setup Time         |                                   | 250 |     |      | ns    |

| $\mathbf{t}_{\text{HD:DAT}}$ | Data In Hold Time          |                                   | 0   |     |      | ns    |

| TI                           | Noise Filter SCL and SDA   | Noise suppression                 |     | 100 |      | ns    |

| t <sub>wr_confi</sub><br>g   | Write Cycle Time Config    | Configuration Registers           |     |     | 10   | ms    |

| $t_{WR\_EE}$                 | Write Cycle Time EE        | Memory Array                      |     |     | 5    | ms    |

Note: <u>1</u>/ - Guaranteed by Design.

## TIMING DIAGRAMS

Preliminary Information

## TIMING DIAGRAMS (CONTINUED)

### Figure 5A - Cascade Sequencing the Supplies On and then Monitoring for Fault Conditions

Figure 5B - Cascade Sequencing the Supplies Off

Preliminary Information

Figure 6 - Typical Applications Schematic

Preliminary Information

### **APPLICATIONS INFORMATION (CONTINUED)**

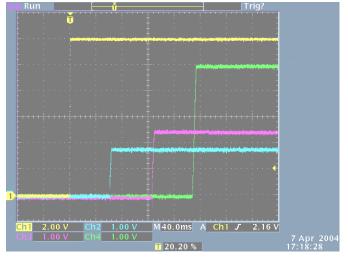

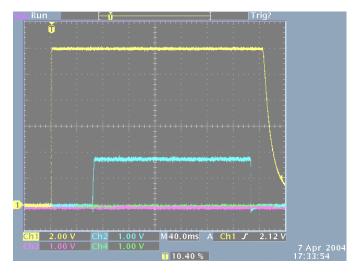

Using the schematic in Figure 6 and assuming all input voltages are within the programmed limits, application of power to the SMH4046 will enable all DC-DC converters according to the sequence programmed for each channel in the SMH4046. An I<sup>2</sup>C software Power-On command can also be used to enable the DC-DC converters. The waveforms in Figure 7 were generated using Channel 1 (12V output) for the time-base trigger. Note the outputs are asserted once the pre-programmed time limit is passed.

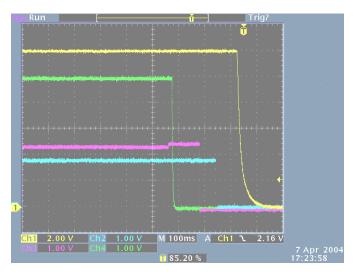

Conversely, the SMH4046 can issue an  $I^2C$  Power-Off command (Figure 8). The SMH4046 reverses the Power-Off sequence; that is, the first supply to shut off is the last to have turned on (Channel 4 in this case). As displayed in Figure 8, the supplies are turned off in reverse order of the turn-on sequence.

Figure 7: SMH4046EV Sequence-On Waveforms Tektronix TDS3054: Time/Horizontal division = 40mS Ch 1(2V/Div) = 12V output (Yellow trace) Ch 2 (1V/Div) = 1.8V DC-DC converter output (Blue trace) Ch 3 (1V/Div) = 2.5V DC-DC converter output (Purple trace) Ch 4 (1V/Div) = 5.0V output (Green trace)

## Figure 8: SMH4046EV Sequence-Off Waveforms Tektronix TDS3054: Time/Horizontal division = 100mS

Ch 1(2V/Div) = 12V output (Yellow trace) Ch 2 (1V/Div) = 1.8V DC-DC converter output (Blue trace) Ch 3 (1V/Div) = 2.5V DC-DC converter output (Purple trace) Ch 4 (1V/Div) = 5.0V output (Green trace)

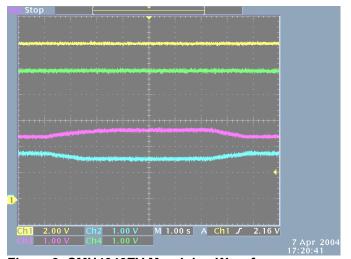

The SMH4046's has many features including the ability to change the channel sequence positions and slew-rates for system flexibility and software programmability to simplify changes. Figure 9 displays the SMH4046 margining the 2.5V converter high and the 1.8V converter low.

## **APPLICATIONS INFORMATION (CONTINUED)**

Figure 9: SMH4046EV Margining Waveforms Tektronix TDS3054: Time/Horizontal division = 1S Ch 1(2V/Div) = 12V output (Yellow trace) Ch 2 (1V/Div) = 1.8V DC-DC converter output (Blue trace) Ch 3 (1V/Div) = 2.5V DC-DC converter output (Purple trace) Ch 4 (1V/Div) = 5.0V output (Green trace)

Figure 10 displays the SMH4046 shutting the power supplies (Force Shutdown) during the Sequence-On interval due to the time-out of the Sequence Termination Timer.

#### Figure 10: SMH4046EV Forced Sequence-Off Tektronix TDS3054: Time/Horizontal division = 40mS Ch 1(2V/Div) = 12V output (Yellow trace)

Ch 2 (1V/Div) = 1.8V DC-DC converter output (Blue trace)

Ch 3 (1V/Div) = 2.5V DC-DC converter output (Purple trace) Ch 4 (1V/Div) = 5.0V output (Green trace)

#### **COMMENTS & PRECAUTIONS**

The SMH4046 is a precision integrated circuit requiring certain attention is spent with regards to component selection and printed circuit board layout to ensure the greatest possible performance. Bypass all DC-DC converter outputs with a suitable low value capacitor to decrease the high frequency noise and thereby improve the SMH4046's accuracy.

Locate the VCC bypass capacitors nearby the SMH4046 returning the low side directly to a ground pin on the device. Do the same for the bulk capacitor for the DC-DC converter inputs, the 3.3V and 12V inputs; if used. Add an additional low value bypass capacitor if the supplies are noisy.

#### VCC5 Noise

Noise introduced onto the supply (VCC5 pin) of the SMH4046 by the DC/DC converters or other sources may affect the ADC and ADOC<sup>tm</sup> (margining) accuracy. The result is that the ADC reading and final ADOC<sup>tm</sup> (margined) voltage may exhibit an error or the actual ADOC voltage may differ noticeably from the target value. To obtain more accurate results, an external series  $20\Omega$  (R47 in Figure 6) resistor should be added in series between the VCC5 pin 41 and the supply voltage and a  $10\mu$ F ceramic bypass capacitor (C24 in Figure 6) added from VCC5 to GND to form a low pass filter.

#### **ADC Function – VOUT Noise**

The ADC can appear to return erroneous readings when connected to a power supply DC/DC converter output exhibiting a low frequency noise component. Adding additional filter capacitance to the VMX pins 15, 18 and 21 can reduce this effect by lowering the corner frequency of the low pass filter (C25, C26 and C27 in Figure 6). The maximum recommended value is 150nF.

Preliminary Information

#### I<sup>2</sup>C 2-WIRE SERIAL INTERFACE

### Programming Information

### I<sup>2</sup>C Bus Interface

The I<sup>2</sup>C bus interface is a standard two-wire serial protocol that allows communication between integrated circuits. The data line (SDA) is a bi-directional I/O; the clock line (SCL) runs at speeds of up to 400kHz. The SMH4046 supports a 100 kHz clock rate. The SDA line must be connected to a positive logic supply through a pull-up resistor located on the bus.

#### Start and Stop Conditions

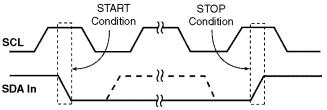

Both the SDA and SCL pins remain high when the bus is not busy. Data transfers between devices may be initiated with a Start condition. A high-to-low transition of the SDA input while the SCL pin is high is defined as a Start condition. A low-to-high transition SDA while SCL is high is defined as a Stop condition. Figure 11 shows a timing diagram of the start and stop conditions.

Figure 11 - Start and Stop Conditions

#### Master/Slave Protocol

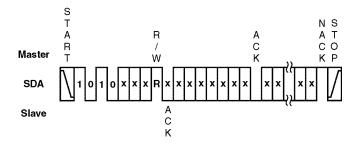

The master/slave protocol defines any device that sends data onto the bus as a transmitter, and any device that receives data as a receiver. The device controlling data transmission is called the Master, and the controlled device is called the Slave. In all cases the SMH4046 is referred to as a Slave device since it never initiates any data transfers. One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during clock high time, because a change on the data line while SCL is high is interpreted as either a Start or a Stop condition.

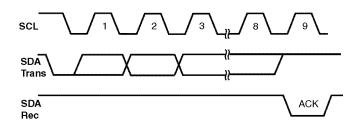

#### Acknowledge

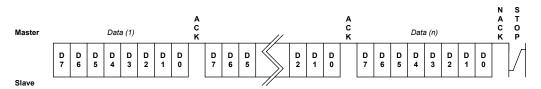

Data is always transferred in bytes. Acknowledge (ACK) is used to indicate a successful data transfer. The transmitting device releases the bus after transmitting eight bits. During the ninth clock cycle the Receiver pulls the SDA line low to acknowledge that it received the eight bits of data. This is shown by the ACK callout in Figure 12.

When the last byte has been transferred to the Master during a read of the SMH4046, the Master leaves SDA high for a Not Acknowledge (NACK) cycle. This causes the SMH4046 part to stop sending data, and the Master issues a Stop on the clock pulse following the NACK.

#### **Read and Write**

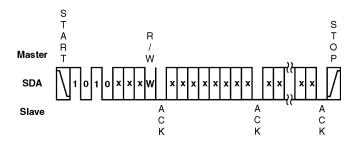

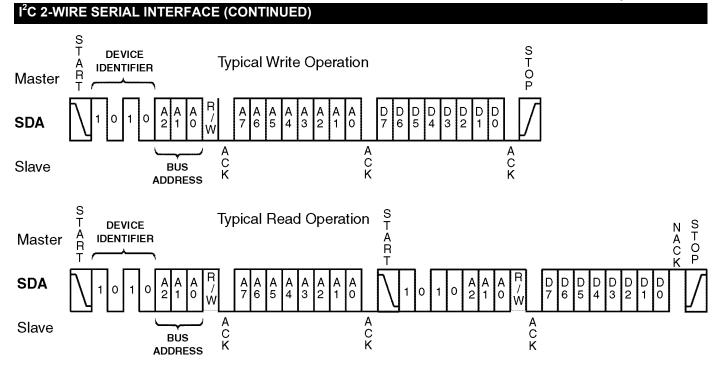

The first byte from a Master is always made up of a 7bit Slave address and the Read/Write (R/W) bit. The R/W bit tells the Slave whether the Master is reading data from the bus or writing data to the bus (1 = Read, 0 = Write). The first four of the seven address bits are called the Device Type Identifier (DTI). In the case of the SMH4046, the next two bits are Bus Address values, used to distinguish multiple devices on a common bus. The seventh bit of the slave address represents the ninth bit of the word address. The SMH4046 issues an Acknowledge after recognizing a Start condition and its DTI. Figure 13 shows an example of a typical master address byte transmission.

SCL SDA 0 ACK х ХхХ

Figure 13 - Typical Master Address Byte Transmission

#### I<sup>2</sup>C 2-WIRE SERIAL INTERFACE (CONTINUED)

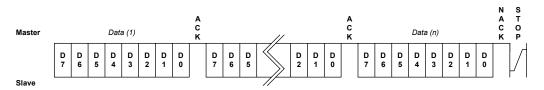

During a read by the Master device, the SMH4046 transmits eight bits of data, then releases the SDA line, and monitors the line for an Acknowledge signal. If an Acknowledge is detected, and no Stop condition is generated by the Master, the SMH4046 continues to transmit data. If an Acknowledge is not detected (NACK), the SMH4046 terminates any subsequent data transmission. The read transfer protocol on SDA is shown in Figure 14.

#### Figure 14 - Read Protocol

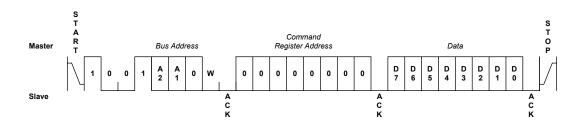

During a Master write, the SMH4046 receives eight bits of data, then generates an Acknowledge signal. The device continues to generate the ACK condition on SDA until a Stop condition is generated by the Master. The write transfer protocol on SDA is shown in Figure 15.

Figure 15 - Write Protocol

## SMH4046

Preliminary Information

#### **Random Access Read**

Random address read operations (Figure 16) allow the Master to access any memory location in a random fashion. This operation involves a two-step process. First, the Master issues a Write command which includes the Start condition and the Slave address field (with the R/W bit set to Write) followed by the address of the word it is to read. This procedure sets the internal address counter of the SMH4046 to the desired address.

After the word address Acknowledge is received by the Master, it immediately reissues a Start condition followed by another Slave address field with the R/W bit set to Read. The SMH4046 responds with an Acknowledge and then transmits the 8 data bits stored at the addressed location. At this point, the Master sets the SDA line to NACK and generates a Stop condition. The SMH4046 discontinues data transmission and reverts to its standby power mode.

#### Sequential Reads

Sequential reads (Figure 16) can be initiated as either a current address read or a random access read. The first word is transmitted as with the other byte Read modes (current address byte Read or random address byte Read). However, the Master now responds with an Acknowledge, indicating that it requires additional data from the SMH4046.

The SMH4046 continues to output data for each Acknowledge received. The Master sets the SDA line to NACK and generates a Stop condition. During a sequential Read operation the internal address counter is automatically incremented with each Acknowledge signal.

For Read operations all address bits are incremented, allowing the entire array to be read using a single Read command. After a count of the last memory address the address counter rolls over and the memory continues to output data.

Preliminary Information

Figure 16 - Typical EE Memory Write and Random Read Operations

#### FPGA Configuration Interface

The FPGA interface is used to perform configuration of industry standard FPGAs by loading application specific data into the FPGA configuration memory via the SMH4046 FPGA interface. To enable the FPGA interface option, Bit 7 of configuration register hex0C must be set to a 1. Bits [2:0] of register hex84, slave address 1001are write/read bits that are mapped to output pins FPGA\_DCLK, FPGA\_DO, and FPGA\_NCFG, respectively. A write to these bits will result in the same corresponding state on the output pins. Bits [7:6] are mapped to input pins FPGA\_NSTS and FPGA\_CFGDONE, respectively. The state of these pins is reflected in the corresponding bits and can be read. The function of each pin is described in Table 1. For more information, see the FPGA data sheet for configuration options.

| Symbol                                                                                                                                     | Туре                                      | Description                                                                                                                            |  |

|--------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------|--|

| FPGA_NSTS                                                                                                                                  | STS I FPGA configuration status input pin |                                                                                                                                        |  |

| FPGA_CFGD<br>ONE                                                                                                                           | ļ                                         | I FPGA_CFGDONE indicates completion of the configuration process.                                                                      |  |

| FPGA_NCFG O FPGA_NCFG is a configuration control output. A low transition resets th device; a low-to-high transition begins configuration. |                                           | FPGA_NCFG is a configuration control output. A low transition resets the target device; a low-to-high transition begins configuration. |  |

| FPGA_DO O FPGA_DO provides preamble and configuration data to down daisy-chain.                                                            |                                           | FPGA_DO provides preamble and configuration data to downstream devices in a daisy-chain.                                               |  |

|                                                                                                                                            |                                           | FPGA Configuration clock output. Clock output used to clock configuration data using pin FPGA_DO.                                      |  |

#### TABLE 1 – FPGA Configuration interface

Preliminary Information

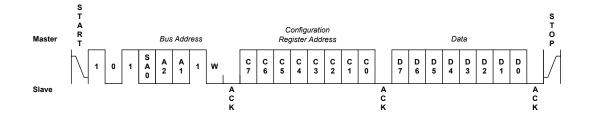

### I<sup>2</sup>C 2-WIRE SERIAL INTERFACE (CONTINUED)

#### **Register Access**

The SMH4046 contains a 2-wire bus interface for register access as explained in the previous section. This bus is highly configurable, while maintaining the industry standard protocol. The SMH4046 responds to one of two selectable Device Type Addresses:  $1010_{BIN}$ , generally assigned to NV-memories and the default address for the SMH4046, or  $1011_{BIN}$ . The Device Type Address is assigned by programming bit 3 of Register 0x0E.

The configuration registers may be locked out by setting bit 7 of register 0x0D high. This is a one-time, non-reversible operation.

The SMH4046 has two virtual address pins, A[1:0] (set with R0E[1:0]), associated with the 2-wire bus.

| Slave Address             | Bus Address | Register Type                                           |

|---------------------------|-------------|---------------------------------------------------------|

| 1001 <sub>BIN</sub>       | A2 A1 A0    | Command and Status Registers,<br>ADC Conversion Readout |

| 1010 <sub>BIN</sub>       | A2 A1 0     | 2-k Bits of General-Purpose Memory                      |

| or<br>1011 <sub>BIN</sub> | A2 A1 1     | Configuration Registers                                 |

Table 2 - Address bytes used by the SMH4046.

Preliminary Information

## I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

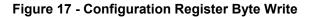

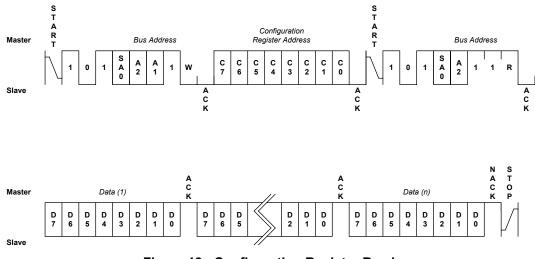

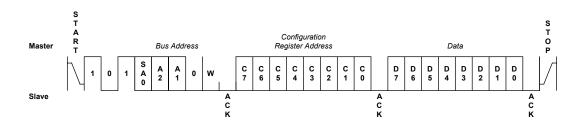

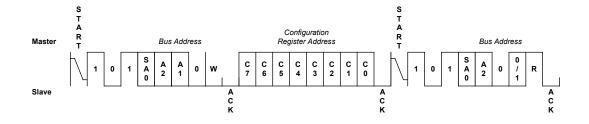

Figure 18 - Configuration Register Read

Preliminary Information

### I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

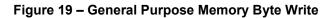

Figure 20 - General Purpose Memory Read

Preliminary Information

### I<sup>2</sup>C PROGRAMMING INFORMATION (CONTINUED)

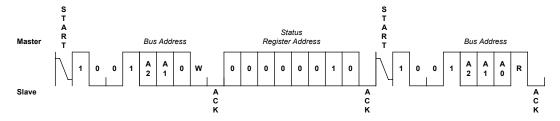

Figure 22 - Status Register Read

## I<sup>2</sup>C DEVELOPMENT HARDWARE & SOFTWARE

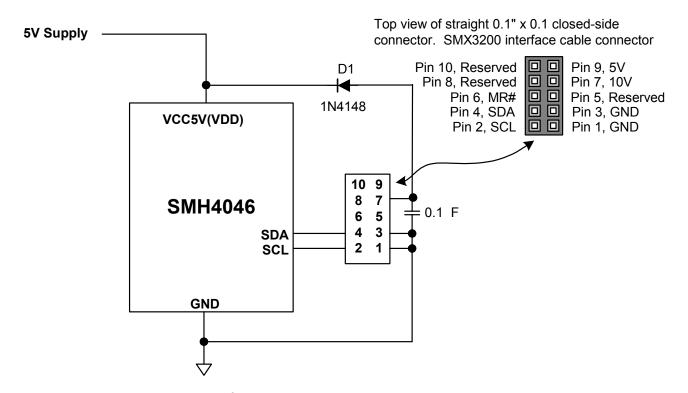

The end user can obtain the Summit SMX3200 programming system for device prototype development. The SMX3200 system consists of a programming Dongle, cable and Windows<sup>™</sup> GUI software. It can be ordered on the website or from a local representative.

The SMX3200 programming Dongle/cable interfaces directly between a PC's parallel port and the target application. The device is then configured on-screen via an intuitive graphical user interface employing drop-down menus.

The Windows GUI software will generate the data and send it in  $I^2C$  serial bus format so that it can be directly downloaded to the SMH4046 via the programming Dongle and cable. An example of the connection interface is shown in Figure 23.

When design prototyping is complete, the software can generate a HEX data file that should be transmitted to Summit for approval. Summit will then assign a unique customer ID to the HEX code and program production devices before the final electrical test operations. This will ensure proper device operation in the end application.

### Figure 23 – SMX3200 Programmer I<sup>2</sup>C serial bus connections to program the SMH4046.

The latest revisions of all software and an application brief describing the SMX3200 is available from the website at:

http://www.summitmicro.com/tech\_support/tech.htm#GUI

### **CONFIGURATION REGISTERS**

#### Configuration Registers:

The configuration registers are accessible via the  $I^2C$  interface at slave address 1010 or 1011 and 1001. These registers determine which features of the device are active, set voltage sensing threshold levels, and define the programmable output logic.

#### Register R00 – VREF nominal settings.

bits in detail. The following registers are accessed using slave address 101 SA0 A2 A1 1 (SA0 =  $C_0E[3]$ ).

The following tables describe the configuration register

Bits D[7:6] are unused and should be set to 00. Bits D[5:4] control the Ch C VREF value. Bits D[3:2] control Ch B VREF and Bits D[1:0] control Ch A VREF.

| R  | egister | R00 |    |    |    |    |    |                             |

|----|---------|-----|----|----|----|----|----|-----------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                      |

| 0  | 0       | -   | -  | -  | -  | -  | -  | Unused.                     |

| -  | -       | 0   | 0  | -  | -  | -  | -  | Ch C VREF=0.75 V            |

| -  | -       | 0   | 1  | -  | -  | -  | -  | Ch C VREF=1.0 V             |

| -  | -       | 1   | 0  | -  | -  | -  | -  | Ch C VREF=1.25 V            |

| -  | -       | 1   | 1  | -  | -  | -  | -  | Ch C VREF=2.0 V             |

| -  | -       | -   | -  | 1  | 1  | -  | -  | Ch B VREF selection Nominal |

| -  | -       | -   | -  | -  | -  | 1  | 1  | Ch A VREF selection Nominal |

#### Register R01 – Channel A Nominal Setting.

Bits D[7:0] control the Channel A Margin Nominal setting. The DC Control Voltage setting bits (C[7:0]) are set using C[7:0] = 256 \* VREF\_CNTL / DC Control Voltage. VREF\_CNTL is from register R00.

| R  | egister | R01 |    |    |    |    |    |                                     |

|----|---------|-----|----|----|----|----|----|-------------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                              |

| C7 | C6      | C5  | C4 | C3 | C2 | C1 | C0 | Channel A Margin Nominal Bits [7:0] |

#### Register R02 – Channel C Nominal Setting.

Bits D[7:0] control the Channel C Margin Nominal setting

| l  | Register | R02 |    |    |    |    |    |                                     |

|----|----------|-----|----|----|----|----|----|-------------------------------------|

| D7 | D6       | D5  | D4 | D3 | D2 | D1 | D0 | Action                              |

| C7 | C6       | C5  | C4 | C3 | C2 | C1 | C0 | Channel C Margin Nominal Bits [7:0] |

#### Register R03 – Channel B Nominal Setting.

Bits D[7:0] control the Channel B Margin Nominal setting

| R  | egister | R03 |    |    |    |    |    |                                     |

|----|---------|-----|----|----|----|----|----|-------------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                              |

| C7 | C6      | C5  | C4 | C3 | C2 | C1 | C0 | Channel B Margin Nominal Bits [7:0] |

## **CONFIGURATION REGISTERS (CONTINUED)**

#### Register R04 – Over-Current Configuration.

Bit D[7] and D[5] are unused. Bit D[6] controls if OC causes an IRQ and D[4] controls if OC causes a FAULT. Bits D[3:0] control the overcurrent Delay.

| R  | egister | R04 |    |    |    |    |    |                                             |

|----|---------|-----|----|----|----|----|----|---------------------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                                      |

| 0  | -       | -   | -  | -  | -  | -  | -  | Unused                                      |

| -  | 0       | -   | -  | -  | -  | -  | -  | OC does not cause an IRQ                    |

| -  | 1       | -   | -  | -  | -  | -  | -  | OC causes an IRQ                            |

| -  | -       | 0   | -  | -  | -  | -  | -  | Unused                                      |

| -  | -       | -   | 0  | -  | -  | -  | -  | OC does not cause a FAULT                   |

| -  | -       | -   | 1  | -  | -  | -  | -  | OC causes a FAULT                           |

| -  | -       | -   | -  | 0  | 0  | 0  | 0  | Minimum Overcurrent Delay = 5.5µs, 1LSB=3µs |

| -  | -       | -   | -  | 1  | 1  | 1  | 1  | Maximum Overcurrent Delay = 50.5µs          |

#### Register R05 – Overcurrent configuration and fault latch.

Bits D[7:6] control the VDD differential level that causes an OC. Bits D[5:4] control the VCC3 differential level that causes an OC. Bit D[3] controls the 5V OC detection. Bit D[2] controls the 3V OC detection. Bit D[1] controls the FAULT output latch and D[0] is unused.

| R  | egister | R05 |    |    |    |    |    |                                                         |

|----|---------|-----|----|----|----|----|----|---------------------------------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                                                  |

| 0  | 0       | -   | -  | -  | -  | -  | -  | 50mV differential between VDD and CARD5V causes OC      |

| 0  | 1       | -   | -  | -  | -  | -  | -  | 100mV differential between VDD and CARD5V<br>causes OC  |

| 1  | 0       | -   | -  | -  | -  | -  | -  | 150mV differential between VDD and CARD5V<br>causes OC  |

| 1  | 1       | -   | -  | -  | -  | -  | -  | 250mV differential between VDD and CARD5V causes OC     |

| -  | -       | 0   | 0  | -  | -  | -  | -  | 50mV differential between VCC3 and CARD3V<br>causes OC  |

| -  | -       | 0   | 1  | -  | -  | -  | -  | 100mV differential between VCC3 and CARD3V<br>causes OC |

| -  | -       | 1   | 0  | -  | -  | -  | -  | 150mV differential between VCC3 and CARD3V causes OC    |

| -  | -       | 1   | 1  | -  | -  | -  | -  | 250mV differential between VCC3 and CARD3V<br>causes OC |

| -  | -       | -   | -  | 0  | -  | -  | -  | OC detection on 5V channel OFF                          |

| -  | -       | -   | -  | 1  | -  | -  | -  | OC detection on 5V channel ON                           |

| -  | -       | -   | -  | -  | 0  | -  | -  | OC detection on 3V channel OFF                          |

| -  | -       | -   | -  | -  | 1  | -  | -  | OC detection on 3V channel ON                           |

| -  | -       | -   | -  | -  | -  | 0  | -  | Fault output is unlatched                               |

| -  | -       | -   | -  | -  | -  | 1  | -  | Fault output is latched                                 |

| -  | -       | -   | -  | -  | -  | -  | 0  | Unused                                                  |

# **CONFIGURATION REGISTERS (CONTINUED)**

Register R06 – Healthy Triggers.

| R  | egister | R06 |    |    |    |    |    |                                               |

|----|---------|-----|----|----|----|----|----|-----------------------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                                        |

| 0  | -       | -   | -  | -  | -  | -  | -  | Ext Temp fault does not cause a HEALTHY.      |

| 1  | -       | -   | -  | -  | -  | -  | -  | Ext Temp fault causes a HEALTHY.              |

| -  | 0       | -   | -  | -  | -  | -  | -  | Internal Temp fault does not cause a HEALTHY. |

| -  | 1       | -   | -  | -  | -  | -  | -  | Internal Temp fault causes a HEALTHY.         |

| -  | -       | 0   | -  | -  | -  | -  | -  | CARD12V fault does not cause a HEALTHY.       |

| -  | -       | 1   | -  | -  | -  | -  | -  | CARD12V fault causes a HEALTHY.               |

| -  | -       | -   | 0  | -  | -  | -  | -  | CARD5V fault does not cause a HEALTHY.        |

| -  | -       | -   | 1  | -  | -  | -  | -  | CARD5V fault causes a HEALTHY.                |

| -  | -       | -   | -  | 0  | -  | -  | -  | CARD3V fault does not cause a HEALTHY.        |

| -  | -       | -   | -  | 1  | -  | -  | -  | CARD3V fault causes a HEALTHY.                |

| -  | -       | -   | -  | -  | 0  | -  | -  | VMC fault does not cause a HEALTHY.           |

| -  | -       | -   | -  | -  | 1  | -  | -  | VMC fault causes a HEALTHY.                   |

| -  | -       | -   | -  | -  | -  | 0  | -  | VMB fault does not cause a HEALTHY.           |

| -  | -       | -   | -  | -  | -  | 1  | -  | VMB fault causes a HEALTHY.                   |

| -  | -       | -   | -  | -  | -  | -  | 0  | VMA fault does not cause a HEALTHY.           |

| -  | -       | -   | -  | -  | -  | -  | 1  | VMA fault causes a HEALTHY.                   |

## Register R0C – Misc Config

| R  | egister | R0C |    |    |    |    |    |                                  |

|----|---------|-----|----|----|----|----|----|----------------------------------|

| D7 | D6      | D5  | D4 | D3 | D2 | D1 | D0 | Action                           |

| 0  | -       | -   | -  | -  | -  | -  | -  | FPGA feature disabled.           |

| 1  | -       | -   | -  | -  | -  | -  | -  | FPGA selected from register.     |

| -  | 0       | -   | -  | -  | -  | -  | -  | ADOC fast convergence disabled.  |

| -  | 1       | -   | -  | -  | -  | -  | -  | ADOC fast convergence enabled.   |

| -  |         | 0   | -  | -  | -  | -  | -  | Unused                           |

| -  |         | 0   | -  | -  | -  | -  | -  | Unused                           |

| -  | -       | -   | 0  | -  | -  | -  | -  | Unused                           |

| -  | -       | -   | 0  | -  | -  | -  | -  | Unused                           |

| -  | -       | -   | -  | 0  | -  | -  | -  | VGATE charge pump not always on. |