SGKS001D - JULY 1997 - REVISED OCTOBER 2001

**Performance:**

- 80 Million Floating-Point Operations Per Second (MFLOPS) With 496-MBps-Burst I/O Rate for 40-MHz Modules

- Zero-Wait-State Local Memory for Each Processor

- **Organization:**

- 128K-Word × 32-Bit Static **Random-Access Memory (SRAM)** (SMJ320MCM42D)

- 256K-Word × 32-Bit SRAM (SMJ320MCM42C)

- Compliant With MIL-PRF-38535 QML

- **Dual C40 Performance With Local Memory** Requiring Only 8.7 Square Inches of Board Space

- **Enhanced Performance Offered By Multichip-Module Solution**

- SMJ320MCM42C

- 67% Reduction in Number of Interconnects

- 54% Reduction (Minimum) in Board Area

- Estimated 38% Reduction in Power **Dissipation Due to Reduced Parasitic** Capacitance and Interconnect Lengths

- SMJ320MCM42D

- 56% Reduction in Number of Interconnects

- 30% Reduction (Minimum) in Board Area

- Estimated 20% Reduction in Power **Dissipation Due to Reduced Parasitic** Capacitance and Interconnect Lengths

- Four Memory Ports for High Data **Bandwidth**

- Two Full 2G-Word External Buses

- Two Internal Buses Mapped to Memory

- 128K-Word × 32-Bit SRAM for Each C40 Local Bus (SMJ320MCM42D)

- 256K-Word × 32-Bit SRAM for Each C40 Local Bus (SMJ320MCM42C)

- **Ten External Communication Ports for** Direct Processor-to-Processor Communication

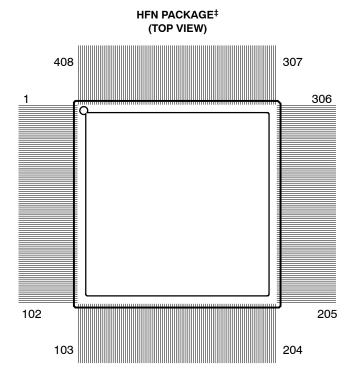

<sup>‡</sup> Terminal assignment information is provided by the terminal assignments table. Package is shown for pinout reference only.

- IEEE-1149.1<sup>†</sup> (JTAG) Boundary-Scan Compatible

- 408-Lead Ceramic Quad Flatpack Package (HFN Suffix)

- **Operating Free-Air Temperature Ranges:** -55°C to 125°C . . . (Military) 0°C to 70°C . . . (Commercial)

- **Communication-Port Connection Provided Between C40s for Interprocessor** Communication

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

<sup>†</sup> IEEE Standard 1149.1-1990 Standard Test-Access Port and Boundary-Scan Architecture

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2001, Texas Instruments Incorporated On products compliant to MIL-STD-PRF-38535, all parameters are tested unless otherwise noted. On all other products, production processing does not necessarily include testing of all parameters.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

#### description

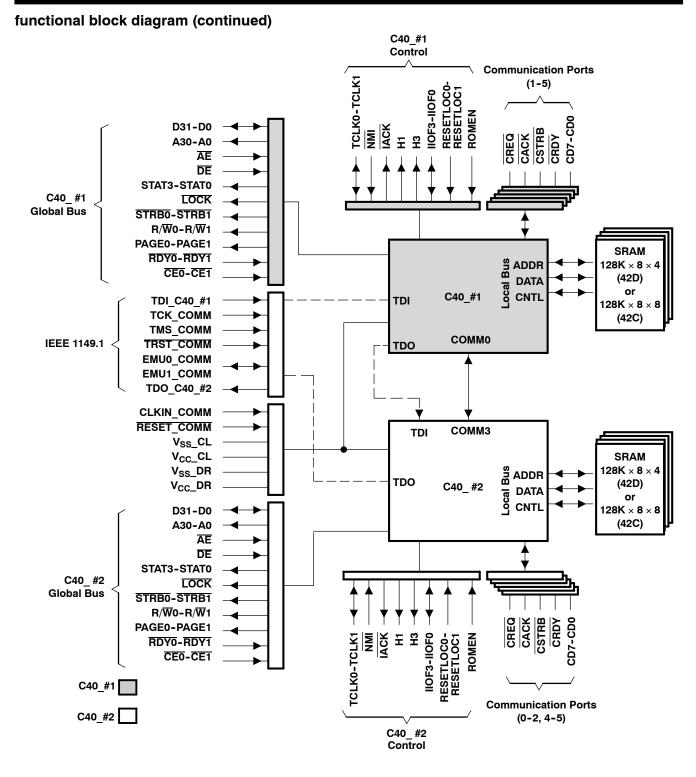

The 42 dual C40 multichip module (MCM) contains two SMJ320C40 digital signal processors (DSPs) with 128K words  $\times$  32 bits (42D) or 256K words  $\times$  32 bits (42C) of zero-wait-state SRAMs mapped to each local bus. Global address and data buses with two sets of control signals are routed externally for each processor, allowing external memory to be accessed. The external global bus provides a continuous address reach of 2G words.

The dual C40 configuration allows standard microprocessor initialization using the bootstrap loader. Both reset-vector-control terminals are brought out to external terminals for each processor. A single CLKIN line and a RESET line feed both processors in parallel, minimizing clock skew and allowing easy synchronization for interlocked operations.

Communication port 0 of CPU #1 connects to communication port 3 of CPU #2 for direct processor-to-processor communication.

The IEEE-1149.1 (JTAG) test ports of the C40s are connected serially to allow scan operations and emulation of the module as a whole. Testability of the 42 adds value and reduces development and support costs. Texas Instruments offers a wide variety of ANSI/IEEE-1149.1 products and support.

The 42 dual C40 MCM is packaged in a 408-pin ceramic quad flat pack. The 42 dual C40 MCM is available in both a commercial temperature range (0°C to 70°C) and a military temperature range (-55°C to 125°C) option.

For additional information when designing for cold temperature operation, please see Texas Instruments application report *320C3x*, *320C4x and 320MCM42x Power-up Sensitivity at Cold Temperature*, literature number SGUA001.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

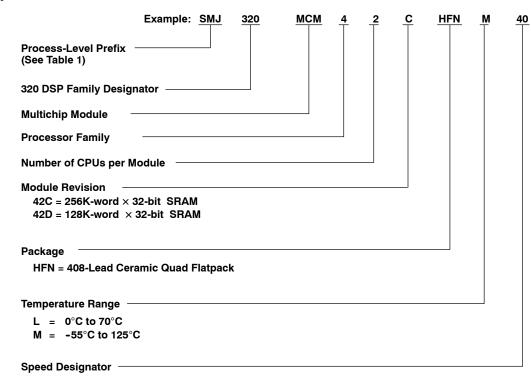

## device symbol nomenclature

40 = 40 MHz

| PROCESS<br>LEVEL | TEMPERAT  | TEMPERATURE RANGE |                  | ERATURE RANGE |     | 100%<br>PROCESSED | SPEED<br>TEST | TEST<br>TEMPERATURE<br>RANGE | QUALIFICATION<br>TESTING |  |

|------------------|-----------|-------------------|------------------|---------------|-----|-------------------|---------------|------------------------------|--------------------------|--|

|                  | L version | 0°C to 70°C       | Probed           | No            | No  | 25°C to 70°C      | Package       |                              |                          |  |

| SM               | M version | -55°C to 125°C    | Probed           | No            | Yes | -55°C to 125°C    | Package       |                              |                          |  |

| SMJ <sup>†</sup> | M version | -55°C to 125°C    | KGD <sup>‡</sup> | Yes           | Yes | -55°C to 125°C    | MIL-H-38534   |                              |                          |  |

<sup>†</sup> SMJ-level product is full MIL-PRF-38535 QML compliant.

<sup>‡</sup> KGD stands for the known-good-die strategy as defined in the reference documentation section.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

TERMINAL TERMINAL TERMINAL TERMINAL NO. NO. NO. NO. NAME NAME NAME NAME ROMEN C40 #1 52 A10 C40 #1 103 RDY1 C40 #2 154 C4D5 C40 #2 1 2 IIOF0 C40 #1 53 A9\_C40\_#1 104  $V_{SS}DR$ C4D4 C40 #2 155 3 IIOF1\_C40\_#1 54 A8\_C40\_#1 105 V<sub>SS</sub>\_CL 156 C4D3\_C40\_#2 4 IIOF2\_C40\_#1 55 A7\_C40\_#1 106 LOCK\_C40\_#2 157 C4D2\_C40\_#2 5 IIOF3\_C40\_#1 56 A6\_C40\_#1 107 V<sub>CC</sub>\_CL 158 C4D1\_C40\_#2 6 NMI C40 #1 57 A5 C40 #1 108 V<sub>SS</sub>\_CL 159 C4D0\_C40\_#2 CE0 C40 #2 7 V<sub>CC</sub>\_DR 58 A4 C40 #1 109 160 V<sub>CC</sub> DR 8 V<sub>SS</sub>\_CL 59 V<sub>CC</sub> DR RDY0 C40 #2 V<sub>CC</sub>\_DR 110 161 A3 C40 #1 DE C40 #2 9 TCLK0 C40 #1 60 111 162 V<sub>SS</sub>\_CL 10 TCLK1\_C40\_#1 61 A2 C40 #1 112 TCK COMM 163 C2D7\_C40\_#2 A1\_C40\_#1 11 H3\_C40\_#1 62 113 TDO\_C40\_#2 164 C2D6\_C40\_#2 TMS COMM C2D5 C40 #2 H1\_C40\_#1 63 A0 C40 #1 165 12 114 D31\_C40\_#2 TRST COMM C2D4 C40 #2 13 V<sub>SS</sub>\_CL 64 115 166 14 IACK C40 #1 65 D30 C40 #2 116 EMU0 COMM 167 C2D3 C40 #2 15 CLKIN COMM 66 D29 C40 #2 117 EMU1 COMM 168 C2D2 C40 #2 16 V<sub>CC</sub>\_DR 67 D28 C40 #2 118 PAGE1 C40 #2 169 C2D1\_C40\_#2 17 V<sub>CC</sub>\_CL 68 D27\_C40\_#2 119 R/W1 C40 #2 170 C2D0 C40 #2 18 V<sub>CC</sub>\_DR 69 D26\_C40\_#2 120 STRB1\_C40\_#2 171 CRDY2 C40 #2 70 STAT0 C40 #2 19 V<sub>SS</sub>\_CL V<sub>CC</sub>\_DR 121 172 CSTRB2 C40 #2 V<sub>SS</sub>\_DR D25\_C40\_#2 STAT1\_C40\_#2 20 71 122 173 CACK2\_C40\_#2 21 V<sub>CC</sub>\_DR 72 D24 C40 #2 123 CREQ2 C40 #2 V<sub>SS</sub>\_CL 174 V<sub>CC</sub>\_DR D23 C40 #2 STAT2 C40 #2 22 73 124 175 V<sub>CC</sub>\_DR 23 V<sub>CC</sub>\_CL 74 D22 C40 #2 125 STAT3 C40 #2 176 CRDY1 C40 #2 24 V<sub>SS</sub>\_CL 75 D21 C40 #2 126 PAGE0 C40 #2 177 CSTRB1 C40 #2 V<sub>SS</sub>\_DR 25 76 D20\_C40\_#2 127 R/W0\_C40\_#2 178 CACK1 C40 #2 V<sub>SS</sub>\_CL 77 D19 C40 #2 128 STRB0 C40 #2 CREQ1 C40 #2 26 179 27 V<sub>CC</sub>\_DR 78 D18 C40 #2 129 AE C40 #2 180 CRDY0 C40 #2 28 A30 C40 #1 79 D17 C40 #2 130 RESETLOC1 C40 #2 181 CSTRB0 C40 #2 29 A29 C40 #1 80 D16 C40 #2 131 V<sub>CC</sub>\_DR 182 CACK0 C40 #2 30 A28\_C40\_#1 81 V<sub>SS</sub>\_CL 132 RESETLOC0\_C40\_#2 183 CREQ0 C40 #2 V<sub>CC</sub>\_DR 31 82 V<sub>SS</sub>\_CL 133 RESET\_COMM 184 V<sub>SS\_</sub>DR 32 A27 C40 #1 83 V<sub>CC</sub>\_DR 134 CRDY5 C40 #2 185 V<sub>SS</sub>\_CL 33 A26 C40 #1 84 V<sub>SS</sub>\_DR 135 CSTRB5 C40 #2 186 V<sub>SS</sub>\_DR 34 A25 C40 #1 85 D15 C40 #2 136 CACK5 C40 #2 187 V<sub>CC</sub>\_DR 35 A24 C40 #1 86 D14 C40 #2 137 CREQ5 C40 #2 188 C1D7 C40 #2 CRDY4 C40 #2 36 A23 C40 #1 87 D13 C40 #2 138 189 C1D6 C40 #2 37 A22 C40 #1 88 D12 C40 #2 139 CSTRB4 C40 #2 190 C1D5 C40 #2 CACK4\_C40\_#2 38 A21\_C40\_#1 89 D11\_C40\_#2 140 191 C1D4\_C40\_#2 39 A20 C40 #1 90 D10 C40 #2 141 CREQ4 C40 #2 192 C1D3\_C40\_#2 40 A19 C40 #1 91 D9 C40 #2 142 V<sub>CC</sub> DR 193 C1D2 C40 #2 41 A18 C40 #1 92 D8 C40 #2 143 C5D7 C40 #2 194 C1D1 C40 #2 A17\_C40\_#1 93 D7 C40 #2 C5D6 C40 #2 C1D0 C40 #2 42 144 195 43 V<sub>CC</sub>\_DR 94 D6 C40 #2 145 C5D5 C40 #2 196 V<sub>CC</sub>\_DR 44 V<sub>SS</sub>\_CL 95 D5\_C40\_#2 146 C5D4\_C40\_#2 197 C0D7\_C40\_#2 45 V<sub>SS</sub>\_DR 96 V<sub>CC</sub>\_DR 147 C5D3 C40 #2 198 C0D6 C40 #2 46 A16 C40 #1 97 D4 C40 #2 148 C5D2 C40 #2 199 C0D5 C40 #2 47 A15 C40 #1 98 D3 C40 #2 149 C5D1 C40 #2 200 C0D4 C40 #2 A14 C40 #1 D2 C40 #2 C5D0 C40 #2 C0D3 C40 #2 48 99 150 201 D1 C40 #2 49 A13 C40 #1 100 151 V<sub>CC</sub>\_DR 202 C0D2 C40 #2 50 A12 C40 #1 101 D0 C40 #2 152 C4D7 C40 #2 203 C0D1 C40 #2 CE1\_C40\_#2 A11\_C40\_#1 C4D6\_C40\_#2 204 C0D0\_C40\_#2 51 102 153

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

| Terminal Assignments (Continued) |                     |     |                     |     |                     |     |                     |  |  |  |

|----------------------------------|---------------------|-----|---------------------|-----|---------------------|-----|---------------------|--|--|--|

|                                  | TERMINAL            | т   | ERMINAL             |     | TERMINAL            |     | TERMINAL            |  |  |  |

| NO.                              | NAME                | NO. | NAME                | NO. | NAME                | NO. | NAME                |  |  |  |

| 205                              | ROMEN_C40_#2        | 256 | A9_C40_#2           | 307 | V <sub>SS</sub> _DR | 358 | V <sub>SS</sub> _DR |  |  |  |

| 206                              | IIOF0_C40_#2        | 257 | A8_C40_#2           | 308 | V <sub>SS</sub> _CL | 359 | V <sub>CC</sub> _DR |  |  |  |

| 207                              | IIOF1_C40_#2        | 258 | A7_C40_#2           | 309 | LOCK_C40_#1         | 360 | C3D7_C40_#1         |  |  |  |

| 208                              | IIOF2_C40_#2        | 259 | A6_C40_#2           | 310 | V <sub>CC</sub> _CL | 361 | C3D6_C40_#1         |  |  |  |

| 209                              | IIOF3_C40_#2        | 260 | A5_C40_#2           | 311 | V <sub>SS</sub> _CL | 362 | C3D5_C40_#1         |  |  |  |

| 210                              | NMI_C40_#2          | 261 | A4_C40_#2           | 312 | CE0_C40_#1          | 363 | C3D4_C40_#1         |  |  |  |

| 211                              | V <sub>CC</sub> _DR | 262 | V <sub>CC</sub> _DR | 313 | RDY0_C40_#1         | 364 | C3D3_C40_#1         |  |  |  |

| 212                              | V <sub>SS</sub> _CL | 263 | A3_C40_#2           | 314 | DE_C40_#1           | 365 | C3D2_C40_#1         |  |  |  |

| 213                              | TCLK0_C40_#2        | 264 | A2_C40_#2           | 315 | TDI_C40_#1          | 366 | C3D1_C40_#1         |  |  |  |

| 214                              | TCLK1_C40_#2        | 265 | A1_C40_#2           | 316 | PAGE1_C40_#1        | 367 | C3D0_C40_#1         |  |  |  |

| 215                              | H3_C40_#2           | 266 | A0_C40_#2           | 317 | R/W1_C40_#1         | 368 | V <sub>CC</sub> _DR |  |  |  |

| 216                              | H1_C40_#2           | 267 | D31_C40_#1          | 318 | STRB1_C40_#1        | 369 | V <sub>SS</sub> _CL |  |  |  |

| 217                              | V <sub>SS</sub> _CL | 268 | D30_C40_#1          | 319 | STAT0_C40_#1        | 370 | C2D7_C40_#1         |  |  |  |

| 218                              | IACK_C40_#2         | 269 | D29_C40_#1          | 320 | STAT1_C40_#1        | 371 | C2D6_C40_#1         |  |  |  |

| 219                              | V <sub>CC</sub> _DR | 270 | D28_C40_#1          | 321 | V <sub>SS</sub> _CL | 372 | C2D5_C40_#1         |  |  |  |

| 220                              | V <sub>CC</sub> _DR | 271 | D27_C40_#1          | 322 | STAT2_C40_#1        | 373 | C2D4_C40_#1         |  |  |  |

| 221                              | V <sub>CC</sub> _DR | 272 | D26_C40_#1          | 323 | STAT3_C40_#1        | 374 | C2D3_C40_#1         |  |  |  |

| 222                              | V <sub>SS</sub> _CL | 273 | V <sub>CC</sub> _DR | 324 | PAGE0_C40_#1        | 375 | C2D2_C40_#1         |  |  |  |

| 223                              | V <sub>SS</sub> _DR | 274 | D25_C40_#1          | 325 | R/W0_C40_#1         | 376 | C2D1_C40_#1         |  |  |  |

| 224                              | V <sub>CC</sub> _DR | 275 | D24_C40_#1          | 326 | STRB0_C40_#1        | 377 | C2D0_C40_#1         |  |  |  |

| 225                              | V <sub>CC</sub> _DR | 276 | D23_C40_#1          | 327 | AE_C40_#1           | 378 | V <sub>SS</sub> _DR |  |  |  |

| 226                              | V <sub>CC</sub> _CL | 277 | D22 C40 #1          | 328 | RESETLOC1 C40 #1    | 379 | V <sub>CC</sub> _DR |  |  |  |

| 227                              | V <sub>SS</sub> _CL | 278 | D21 C40 #1          | 329 | V <sub>CC</sub> _DR | 380 | CRDY3 C40 #1        |  |  |  |

| 228                              | V <sub>SS</sub> _DR | 279 | D20 C40 #1          | 330 | RESETLOC0 C40 #1    | 381 | CSTRB3_C40_#1       |  |  |  |

| 229                              | V <sub>SS</sub> _CL | 280 | D19_C40_#1          | 331 | CRDY5_C40_#1        | 382 | CACK3_C40_#1        |  |  |  |

| 230                              | V <sub>CC</sub> _DR | 281 | D18_C40_#1          | 332 | CSTRB5_C40_#1       | 383 | CREQ3_C40_#1        |  |  |  |

| 231                              | A30_C40_#2          | 282 | D17_C40_#1          | 333 | CACK5_C40_#1        | 384 | V <sub>CC</sub> _CL |  |  |  |

| 232                              | A29_C40_#2          | 283 | D16_C40_#1          | 334 | CREQ5_C40_#1        | 385 | V <sub>SS</sub> _CL |  |  |  |

| 233                              | A28_C40_#2          | 284 | V <sub>SS</sub> _CL | 335 | CRDY4_C40_#1        | 386 | CRDY2_C40_#1        |  |  |  |

| 234                              | V <sub>CC</sub> _DR | 285 | V <sub>SS</sub> _CL | 336 | CSTRB4_C40_#1       | 387 | CSTRB2_C40_#1       |  |  |  |

| 235                              | A27_C40_#2          | 286 | V <sub>CC</sub> _DR | 337 | CACK4_C40_#1        | 388 | CACK2_C40_#1        |  |  |  |

| 236                              | A26_C40_#2          | 287 | V <sub>SS</sub> _DR | 338 | CREQ4_C40_#1        | 389 | CREQ2_C40_#1        |  |  |  |

| 237                              | A25_C40_#2          | 288 | D15_C40_#1          | 339 | V <sub>SS</sub> _DR | 390 | V <sub>CC</sub> _DR |  |  |  |

| 238                              | A24_C40_#2          | 289 | D14_C40_#1          | 340 | V <sub>CC</sub> _DR | 391 | CRDY1_C40_#1        |  |  |  |

| 239                              | A23_C40_#2          | 290 | D13_C40_#1          | 341 | C5D7_C40_#1         | 392 | CSTRB1_C40_#1       |  |  |  |

| 240                              | A22_C40_#2          | 291 | D12_C40_#1          | 342 | C5D6_C40_#1         | 393 | CACK1_C40_#1        |  |  |  |

| 241                              | A21_C40_#2          | 292 | D11_C40_#1          | 343 | C5D5_C40_#1         | 394 | CREQ1_C40_#1        |  |  |  |

| 242                              | A20_C40_#2          | 293 | D10_C40_#1          | 344 | C5D4_C40_#1         | 395 | V <sub>SS</sub> _DR |  |  |  |

| 243                              | A19_C40_#2          | 294 | <br>D9_C40_#1       | 345 | C5D3_C40_#1         | 396 | V <sub>SS</sub> _CL |  |  |  |

| 244                              | A18_C40_#2          | 295 | <br>D8_C40_#1       | 346 | C5D2_C40_#1         | 397 | V <sub>SS</sub> _DR |  |  |  |

| 245                              | A17_C40_#2          | 296 | D7_C40_#1           | 347 | C5D1_C40_#1         | 398 | V <sub>CC</sub> _DR |  |  |  |

| 246                              | V <sub>CC</sub> _DR | 297 | D6_C40_#1           | 348 | C5D0_C40_#1         | 399 | C1D7_C40_#1         |  |  |  |

| 247                              | V <sub>SS</sub> _CL | 298 | D5_C40_#1           | 349 | V <sub>CC</sub> _DR | 400 | C1D6_C40_#1         |  |  |  |

| 248                              | V <sub>SS</sub> _DR | 299 | V <sub>CC</sub> _DR | 350 | C4D7_C40_#1         | 401 | C1D5_C40_#1         |  |  |  |

| 249                              | A16_C40_#2          | 300 | D4_C40_#1           | 351 | C4D6_C40_#1         | 402 | C1D4_C40_#1         |  |  |  |

| 250                              | A15_C40_#2          | 301 | D3_C40_#1           | 352 | C4D5_C40_#1         | 403 | C1D3_C40_#1         |  |  |  |

| 251                              | A14_C40_#2          | 302 | D2_C40_#1           | 353 | C4D4_C40_#1         | 404 | C1D2_C40_#1         |  |  |  |

| 252                              | A13_C40_#2          | 303 | D1_C40_#1           | 354 | C4D3_C40_#1         | 405 | C1D1_C40_#1         |  |  |  |

| 253                              | A12_C40_#2          | 304 | D0_C40_#1           | 355 | C4D2_C40_#1         | 406 | C1D0_C40_#1         |  |  |  |

| 254                              | A11_C40_#2          | 305 | CE1_C40_#1          | 356 | C4D1_C40_#1         | 407 | V <sub>CC</sub> _DR |  |  |  |

| 255                              | A10_C40_#2          | 306 | RDY1_C40_#1         | 357 | C4D0_C40_#1         | 408 | V <sub>SS</sub> _DR |  |  |  |

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

## functional block diagram

The following terminals have 10-k $\Omega$  pullup resistors added within the module:

- CREQx\_C40\_#1, CACKx\_C40\_#1, CSTRBx\_C40\_#1, CRDYx\_C40\_#1, where x = 1, 2, 3, 4, or 5

- CREQy\_C40\_#2, CACKy\_C40\_#2, CSTRBy\_C40\_#2, CRDYy\_C40\_#2, where y = 0, 1, 2, 4, or 5

- LCE1\_C40\_#1, LCE2\_C40\_#2 (internal connections)

A total of 18 decoupling capacitors have been connected within the module.

Between clean power and ground, the following capacitors have been connected:

- Two 0.1-μF capacitors

- Two 0.01-μF capacitors

Between dirty power and ground, the following capacitors have been connected:

- Twelve 0.1-μF capacitors

- Two 0.01-μF capacitors

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

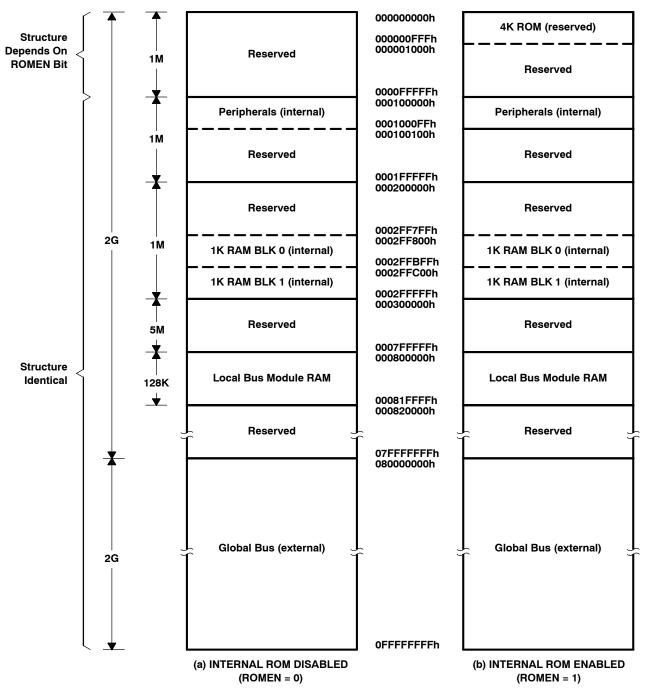

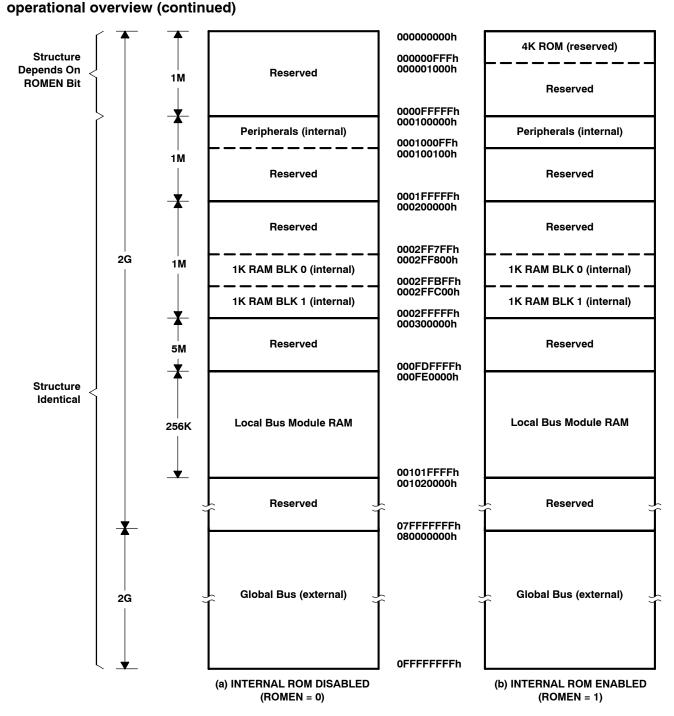

#### operational overview

Treatment of the detailed operation of the C40 device is not included in the scope of this document. See the *TMS320C4x User's Guide* (literature number SPRU063) for a detailed description of this DSP. See Figure 1 and Figure 2 for the memory map.

Figure 1. Memory Map for Each C40 Within the Multichip Module (42D)

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

Figure 2. Memory Map for Each C40 Within the Multichip Module (42C)

#### SGKS001D - JULY 1997 - REVISED OCTOBER 2001

#### application note

For all MCM42x product manufactured prior to August 1, 2001 (i.e., date codes older than 0131), users should reference the application note on page 10 of SGKS001B (July 1997 - Revised February 2000) for proper memory function.

The following application note applies to MCM42x product manufactured after August 1, 2001 (i.e., date codes newer than 0131). Changes to this application note from the previous data sheet revision impact the MCM42C only. Note: The information for the MCM42D below remains unchanged regardless of the date code.

For all MCM42C, the location of the local memory is different from that of the MCM42D. In addition, for proper use of the memory, it is necessary to understand how the memory is controlled.

For product manufactured with date codes newer than 0131, the following applies to the MCM42C only: The entire memory array is controlled by  $\overline{\text{LSTRB0}}$ . The value to be loaded to the STRB ACTIVE area (bits 28–24) should be 11110 (binary). This will require a code change for customers who developed code intended for use with MCM42C devices manufactured with date codes older than 0131.

For the MCM42D, <u>LSTRB0</u> controls the entire 128K. The default value loaded into the STRB ACTIVE area of the LMICR after reset is sufficient to control the memory. The default value is 11110, and tells the C40 that the entire local memory is controlled by <u>LSTRB0</u>.

This subject is discussed in depth in Chapter 9 of the *1996 TMS320C4x User's Guide* (literature number SPRU063). In particular, section 9.3 discusses the proper use of the memory interface control registers.

#### reference documentation and data sheet scope

The SMJ320MCM42 is qualified to MIL-PRF-38535. Electrical continuity of the module is ensured through the use of IEEE-1149.1-compatible boundary-scan testing and functional checkout of the local SRAM space.

KGD refers to TI known-good-die strategy. TI KGDs are fully tested over the military temperature range per MIL-PRF-38535 QML. Electrical tests ensure compliance of the C40 KGD components to the SMJ320C40 data sheet (literature number SGUS017) over the operating temperature range. Module timings are virtually unchanged from the SMJ320C40 data sheet timings. An SMJ320C40 data sheet is provided for customer reference only and does not imply MCM compliance to published timings.

For a description of the C40 operation and application information, see the *TMS320C4x User's Guide* (literature number SPRU063).

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

| absolute maximum ratings over operating free-air temperature range (unless otherw | /ise noted) <sup>†</sup> |

|-----------------------------------------------------------------------------------|--------------------------|

| Supply voltage range, V <sub>CC</sub> (see Note 1)                                | - 0.3 V to 7 V           |

| Voltage range on any terminal                                                     | - 0.3 V to 7 V           |

| Output voltage range, V <sub>O</sub>                                              | - 0.3 V to 7 V           |

| Operating free-air temperature range (commercial [L version]), T <sub>A</sub>     | . 0°C to 70°C            |

| (military [M version]), T <sub>A</sub>                                            | 55°C to 125°C            |

| Junction temperature, T <sub>J</sub>                                              | 150°C                    |

| Storage temperature range, T <sub>stg</sub>                                       | 65°C to 150°C            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTE 1: All voltage values are with respect to V<sub>SS</sub>.

### recommended operating conditions

|                 |                                      |                   |                             | MIN                   | MAX                   | UNIT |

|-----------------|--------------------------------------|-------------------|-----------------------------|-----------------------|-----------------------|------|

| .,              | Que a la constance                   | 42-33             | 4.5                         | 5.5                   |                       |      |

| V <sub>CC</sub> | Supply voltage                       | 42-40             |                             | 4.75                  | 5.25                  | V    |

|                 |                                      | CLKIN_COMM        |                             | 2.6                   | V <sub>CC</sub> + 0.3 |      |

| ViH             | High-level input voltage             | CSTRBx, CRDYx, CR | CSTRBx, CRDYx, CREQx, CACKx |                       |                       |      |

|                 |                                      | All others        | 2                           | V <sub>CC</sub> + 0.3 |                       |      |

| $V_{\text{IL}}$ | Low-level input voltage              |                   | - 0.3                       | 0.8                   | V                     |      |

| I <sub>OH</sub> | High-level output current            |                   |                             |                       | - 300                 | μA   |

| I <sub>OL</sub> | Low-level output current             |                   |                             |                       | 2                     | mA   |

| Ŧ               | Operating free-air temperature range |                   | L version                   | 0                     | 70                    | °C   |

| TA              | Operating nee-an temperature range   |                   | M version                   | - 55                  | 125                   | U    |

# electrical characteristics over recommended ranges of supply voltage and operating free-air temperature (see Note 2)

|                  | PARAMETER                              | TEST CONDITIONS <sup>†</sup> | MIN                          | ТҮР  | MAX | UNIT |    |

|------------------|----------------------------------------|------------------------------|------------------------------|------|-----|------|----|

| V <sub>OH</sub>  | High-level output voltage              | High-level output voltage    |                              |      | 3   |      | V  |

| V <sub>OL</sub>  | Low-level output voltage               |                              | $V_{CC} = MIN, I_{OL} = MAX$ |      | 0.3 | 0.6  | V  |

|                  |                                        | 42D                          |                              |      | 0.7 | 1.1  |    |

| ICC              | Supply current                         | 42C                          | V <sub>CC</sub> = MAX        |      | 0.8 | 1.5  | A  |

| Ι <sub>Ζ</sub>   | 3-state current                        | $V_{I} = V_{SS}$ to $V_{CC}$ | - 20                         |      | 20  | μA   |    |

| l <sub>l</sub>   | Input current                          |                              | $V_{I} = V_{SS}$ to $V_{CC}$ | - 10 |     | 10   | μA |

| $I_{12}$         | Input current, COMM signal (see N      | ote 3)                       | $V_{I} = V_{SS}$ to $V_{CC}$ | - 20 |     | 20   | μA |

| I <sub>IP</sub>  | Input current, internal pullup (see N  | $V_{I} = V_{SS}$ to $V_{CC}$ | - 400                        |      | 30  | μA   |    |

| I <sub>IP2</sub> | Input current, dual internal pullup (s | $V_{I} = V_{SS}$ to $V_{CC}$ | - 800                        |      | 60  | μA   |    |

| I <sub>IC</sub>  | Input current, CLKIN_COMM              | $V_{I} = V_{SS}$ to $V_{CC}$ | - 60                         |      | 60  | μA   |    |

<sup>†</sup> For conditions shown as MIN/MAX, use the appropriate value specified under recommended operating conditions.

NOTES: 2. Electrical characteristics are calculated algebraically from the SMJ320C40 data sheet limits.

3. Includes signals EMU0\_COMM, EMU1\_COMM, and RESET\_COMM

4. Applies to TDI\_C40\_#1

5. Includes signals TCK\_COMM, TMS\_COMM, and TRST\_COMM

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

#### capacitance

Capacitance of a C40 die is specified by design to be 15 pF maximum for both inputs and outputs. Module networks add up to 5 pF. Characterization of die or substance capacitance is performed after any design change. Power measurements taken for a C40 die are made with an additional 80-pF load capacitance. Refer to the SMJ320C40 data sheet (literature number SGUS017) for the test load circuit.

#### operational timings and module testing

Texas Instruments processing assures that operation is verified to published data sheet specifications on the C40 in die form. All voltage, timing, speed, and temperature specifications are met before any die is placed into a multichip module. For this reason, all C40 voltage and timing parameters at the module level need not be verified.

Characterization of the 42 substrate shows that the module performs as an equivalent system of discretely packaged C40 devices. This performance is assured through a full-frequency functional checkout of the module that verifies selected worst-case timings. An additional propagation delay is introduced by the substrate. This value is assured by design to be less than 1 ns, but it is not tested. See the SMJ320C40 data sheet (literature number SGUS017) for a complete listing of timing diagrams and limits.

### module test capability (future compatibility)

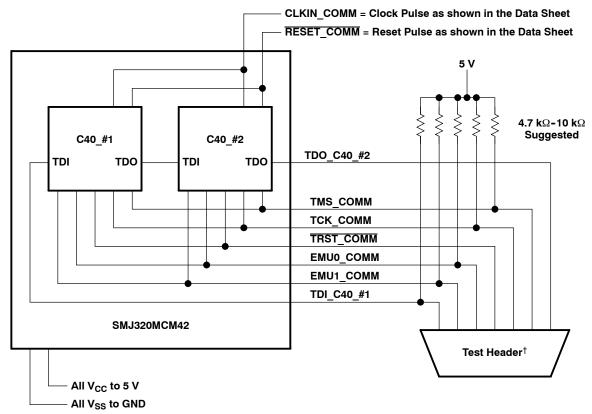

The C40 supports the IEEE-1149.1 testability standard, and the test access port (TAP) is brought out to the module footprint. TDI is connected to C40\_#1, TDO of C40\_#1 is connected to TDI of C40\_#2, and TDO of C40\_#2 is brought out to the TAP. TCK\_COMM, TMS\_COMM, and TRST\_COMM are routed to both C40s in the module. This configuration allows users to test the module using third-party JTAG testability tools or other boundary-scan control software. Proper software configuration allows users to debug or launch code on the module by way of the C40 emulator and extended development system (XDS<sup>TM</sup>) pod. Both of these tools are used as part of outgoing module testing.

The 42 supports third-party JTAG diagnostic families of products for verification and debug of boundary-scan circuits, boards, and systems. Further information on JTAG testability tools is available through any TI sales representative or authorized TI distributor.

XDS is a trademark of Texas Instruments Incorporated.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

#### module test circuit

Figure 3 illustrates the basic circuits for the 42. See the *TMS320C4x User's Guide* (literature number SPRU063) for more detailed information.

<sup>↑</sup> The test header normally consists of the XDS510<sup>™</sup> for the C40 emulation or ASSET hardware for interconnect testing.

Figure 3. Sample Test Circuit

XDS510 is a trademark of Texas Instruments Incorporated.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

#### thermal analysis

Thermal conduction of components in the SMJ320MCM42 is dependent on thermal resistance of the material under each die as well as die area thermally connected to the heat-dissipating medium. Since these properties vary with layout and die size, C40 and SRAM components should be considered separately. Table 2 lists primary parameters required for thermal analysis of the module. T<sub>J</sub>, the maximum junction temperature, is not to be exceeded for the C40s or the SRAM die.

|                       | PARAMETER                                                        | MIN | TYP  | MAX | UNIT |

|-----------------------|------------------------------------------------------------------|-----|------|-----|------|

| TJ                    | Maximum allowable junction temperature under operating condition |     |      | 150 | °C   |

| P <sub>MCM</sub>      | Module power dissipation                                         |     | 3.5  | 5.8 | W    |

| T <sub>JC_pkg</sub> † | Average thermal impedance (junction to case) for the package     |     | 2.1  |     | °C/W |

| T <sub>JA</sub>       | Thermal impedance (junction to ambient air, 0 cfm) of package    |     | 20.5 |     | °C/W |

| T <sub>SOL</sub>      | Maximum solder temperature (10 s duration)                       |     |      | 260 | °C   |

#### Table 2. Thermal Characteristics

<sup>+</sup> T<sub>JC</sub> package data was taken under the following conditions: two C40s dissipating 1.05 W each and eight SRAMs dissipating 0.175 W each.

#### power estimation

During the operation verification, the power requirements of the SMJ320MCM42 are characterized over the operating free-air temperature range. See the application report *Calculation of TMS320C40 Power Dissipation* (literature number SPRA032) as reference for power estimation of the C40 components.

Typical power dissipation is measured with both C40s executing a 64-point fast Fourier transform (FFT) algorithm. Input and output data arrays reside in module SRAM, and output data is written out to the global-address space. The global databus is loaded with 80-pF test loads, and both local and global writes are configured for zero-wait-state memory. Under typical conditions of 25°C, 5-V V<sub>CC</sub>, and 40-MHz CLKIN frequency, the power dissipation is measured to be 3.5 W.

Maximum power dissipation is measured under worst-case conditions. The global databus is loaded with 80-pF test loads, and simultaneous zero-wait-state writes are performed to both local and global buses. Under worst-case environment conditions of – 55°C, 5.25-VV<sub>CC</sub>, and 40-MHz CLKIN frequency, the power dissipation is determined to be 5.9 W. The algorithm executed during these tests consists of parallel writes of alternating 0xAAs and 0x55s to both local SRAM and global-address spaces. This algorithm is not considered to be a practical use of the C40's resources; therefore, the associated power measurement must be considered absolute maximum only.

SGKS001D - JULY 1997 - REVISED OCTOBER 2001

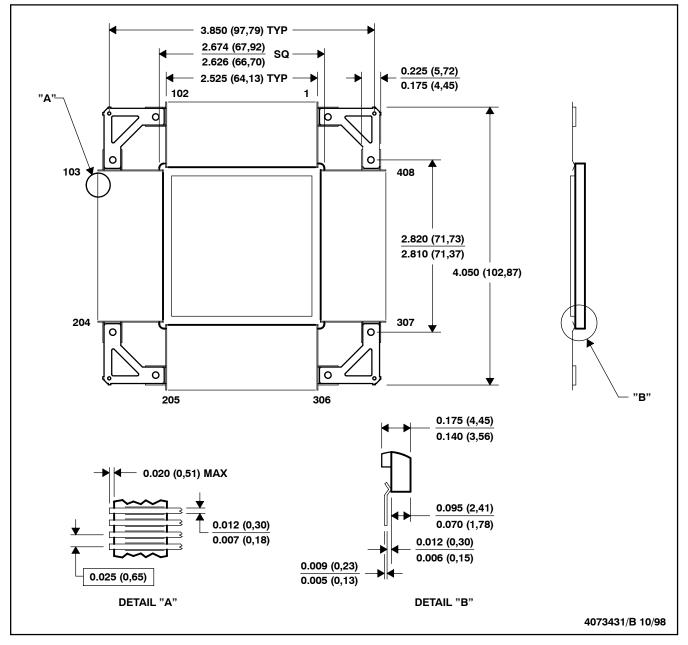

**MECHANICAL DATA**

#### **CERAMIC QUAD FLATPACK WITH TIE-BAR**

HFN (S-CQFP-F408)

17-Dec-2015

## PACKAGING INFORMATION

| Orderable Device  | Status  | Package Type | Package | Pins P | Package | Eco Plan | Lead/Ball Finish | MSL Peak Temp | Op Temp (°C) | Device Marking                                | Samples |

|-------------------|---------|--------------|---------|--------|---------|----------|------------------|---------------|--------------|-----------------------------------------------|---------|

|                   | (1)     |              | Drawing |        | Qty     | (2)      | (6)              | (3)           |              | (4/5)                                         |         |

| 5962-9678901QXC O | BSOLETE | CFP          | HFN     | 408    |         | TBD      | Call TI          | Call TI       | -55 to 125   | 5962-9678901QX<br>C<br>SMJ320MCM42DHF<br>NM40 |         |

<sup>(1)</sup> The marketing status values are defined as follows:

ACTIVE: Product device recommended for new designs.

LIFEBUY: TI has announced that the device will be discontinued, and a lifetime-buy period is in effect.

**NRND:** Not recommended for new designs. Device is in production to support existing customers, but TI does not recommend using this part in a new design.

**PREVIEW:** Device has been announced but is not in production. Samples may or may not be available.

**OBSOLETE:** TI has discontinued the production of the device.

<sup>(2)</sup> Eco Plan - The planned eco-friendly classification: Pb-Free (RoHS), Pb-Free (RoHS Exempt), or Green (RoHS & no Sb/Br) - please check http://www.ti.com/productcontent for the latest availability information and additional product content details.

**TBD:** The Pb-Free/Green conversion plan has not been defined.

**Pb-Free (RoHS):** TI's terms "Lead-Free" or "Pb-Free" mean semiconductor products that are compatible with the current RoHS requirements for all 6 substances, including the requirement that lead not exceed 0.1% by weight in homogeneous materials. Where designed to be soldered at high temperatures, TI Pb-Free products are suitable for use in specified lead-free processes. **Pb-Free (RoHS Exempt):** This component has a RoHS exemption for either 1) lead-based flip-chip solder bumps used between the die and package, or 2) lead-based die adhesive used between the die and leadframe. The component is otherwise considered Pb-Free (RoHS compatible) as defined above.

Green (RoHS & no Sb/Br): TI defines "Green" to mean Pb-Free (RoHS compatible), and free of Bromine (Br) and Antimony (Sb) based flame retardants (Br or Sb do not exceed 0.1% by weight in homogeneous material)

<sup>(3)</sup> MSL, Peak Temp. - The Moisture Sensitivity Level rating according to the JEDEC industry standard classifications, and peak solder temperature.

<sup>(4)</sup> There may be additional marking, which relates to the logo, the lot trace code information, or the environmental category on the device.

<sup>(5)</sup> Multiple Device Markings will be inside parentheses. Only one Device Marking contained in parentheses and separated by a "~" will appear on a device. If a line is indented then it is a continuation of the previous line and the two combined represent the entire Device Marking for that device.

<sup>(6)</sup> Lead/Ball Finish - Orderable Devices may have multiple material finish options. Finish options are separated by a vertical ruled line. Lead/Ball Finish values may wrap to two lines if the finish value exceeds the maximum column width.

Important Information and Disclaimer: The information provided on this page represents TI's knowledge and belief as of the date that it is provided. TI bases its knowledge and belief on information provided by third parties, and makes no representation or warranty as to the accuracy of such information. Efforts are underway to better integrate information from third parties. TI has taken and continues to take reasonable steps to provide representative and accurate information but may not have conducted destructive testing or chemical analysis on incoming materials and chemicals. TI and TI suppliers consider certain information to be proprietary, and thus CAS numbers and other limited information may not be available for release.

17-Dec-2015

In no event shall TI's liability arising out of such information exceed the total purchase price of the TI part(s) at issue in this document sold by TI to Customer on an annual basis.

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ctivity                       |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2016, Texas Instruments Incorporated