#### **Copyright Information**

© 2009 by Sigma Designs Inc. All rights reserved. No part of this document may be copied or reproduced in any form or by any means without the prior written consent of Sigma Designs Inc. The information in this document is subject to change without notice. Sigma Designs, REALmagic and the REALmagic logo are either registered trademarks or trademarks of Sigma Designs Inc. in the United States and/or other countries. Manufactured under license from Dolby Laboratories and Macrovision. Dolby, Pro Logic, and the double-D symbol are trademarks of Dolby Laboratories. All other trademarks or registered trademarks are the properties of their respective owners.

Sigma Designs products are sold by description only. Sigma Designs reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that the datasheet is current before placing orders. Information furnished by Sigma Designs is believed to be accurate and reliable. However, no responsibility is assumed by Sigma Designs or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Sigma Designs or its subsidiaries.

#### Disclaimer

Sigma Designs Inc. makes no warranty, express, statutory, implied or by description regarding the information set forth herein or regarding the freedom of the described devices from intellectual property infringement. Sigma Designs Inc. makes no warranty of merchantability or fitness for any purpose.

Sigma Designs Inc. shall not be responsible for any errors that may appear in this document. Sigma Designs Inc. makes no commitment to update or keep current the information contained in this document.

#### Confidentiality

This document contains confidential information, trade secrets or both that are the property of Sigma Designs Inc. It is to be treated as confidential under the Non Disclosure Agreement (NDA), which has been signed by the obtainer. Reproduction or transmission in any manner to others in whole or in part is prohibited without prior written permission from Sigma Designs Inc.

#### **Export Control**

Due to the inclusion of cryptographic functions, Sigma Designs has applied to the US Department of Commerce, Bureau of Industry and Security (BIS) for authorization to ship the SMP8654 and SMP8655 to customers around the world. These devices have been authorized by the BIS for license exception ENC under sections 740.17 (A) and (B3). The ECCN number under which this exception was granted is 5A002A.1. The following Web site lists all countries where this license exception applies (see *country group B*, *as in B3 above*): http://www.gpo.gov/bis/ear/pdf/740spir.pdf.

#### Life Support Policy

The product(s) described in this document is not intended for use as critical component(s) in life support devices or systems without prior written permission from Sigma Designs Inc.

- Life support devices or systems are devices or systems which, (a) are intended as surgical implant(s) into the body, or (b) support or sustain life, and whose failure to perform, when properly used in accordance with instructions for use provided in the labeling, can be reasonably expected to result in a significant injury to the user.

- A critical component is any component of a life support device or system whose failure to perform can be reasonably expected to

cause the failure of the life support device or system, or to affect its safety or effectiveness.

#### **Trademarks**

Secure Media Processor, SMP8654 and SMP8655 are trademarks of Sigma Designs Inc.

#### **Address**

Sigma Designs Inc. 1778 McCarthy Blvd. Milpitas CA USA - 95035 Tel: 408.262.9003 Fax: 408.262.9740 www.sigmadesigns.com

# **Table of Contents**

|   | Conventions  |        |                                 | .1  |

|---|--------------|--------|---------------------------------|-----|

|   | (            | 0.1    | Acronyms and Abbreviations      | . 1 |

|   |              | 0.2    | Units of Measurement            | .4  |

|   |              | 0.3    | General Conventions             | . 5 |

| 1 | Introduction |        |                                 | .7  |

|   |              | 1.1    | Block Diagram of SMP8654        | . 7 |

|   |              | 1.2    | Main Features of SMP8654        | .8  |

|   |              | 1.3    | Main Components of SMP8654      | 11  |

|   |              | 1.4    | Application Examples            | 15  |

| 2 | Host CPU BI  | ock .  |                                 | 17  |

|   | :            | 2.1    | Block Diagram of Host CPU Block | 17  |

|   | :            | 2.2    | Introduction                    | 18  |

|   |              | Centr  | al Processor Unit (CPU)         | 19  |

|   |              | 2.3    | Introduction                    | 19  |

|   | :            | 2.4    | Features                        | L9  |

|   | ;            | 2.5    | Block Diagram                   | 21  |

|   | :            | 2.6    | Functional Description          | 22  |

|   | 1            | Local  | Memory                          | 42  |

|   | :            | 2.7    | Introduction                    | 12  |

|   | :            | 2.8    | Features4                       | 12  |

|   | :            | 2.9    | Functional Description          | 12  |

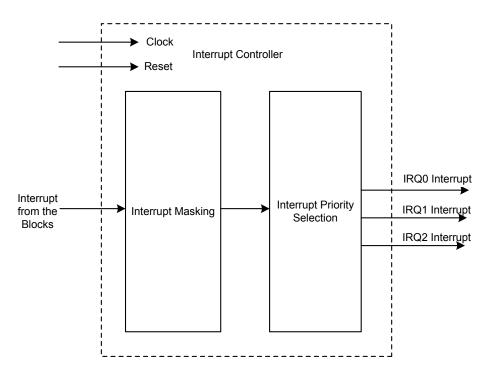

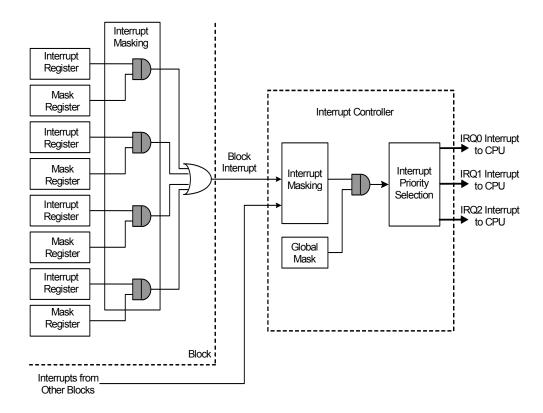

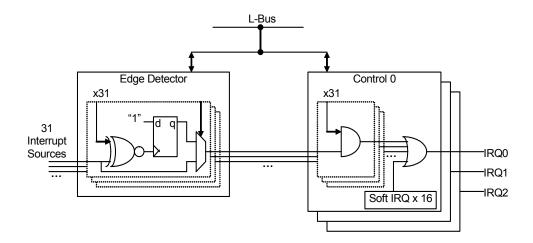

|   | I            | Interr | upt Controller                  |     |

|   | :            | 2.10   | Introduction                    |     |

|   | :            | 2.11   | Features                        |     |

|   | :            | 2.12   | Block Diagram                   |     |

|   |              | 2.13   | Functional Description          |     |

|   |              |        | 'S                              |     |

|   |              |        | Introduction                    |     |

|   |              |        | Features                        |     |

|   | :            | 2.16   | Block Diagram                   |     |

|   |              | 2.17   | Functional Description          |     |

|   | :            | 2.18   | Register Map                    | 54  |

|   |              |        | 's                              |     |

|   |              | 2.19   | Introduction                    | 54  |

|   | 2.20                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                       | 55                                                                   |

|---|-----------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------|

|   | 2.21                                                                                          | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                  | 56                                                                   |

|   | 2.22                                                                                          | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                         | 57                                                                   |

|   | 2.23                                                                                          | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                   | 61                                                                   |

|   | 2.24                                                                                          | Pin Description                                                                                                                                                                                                                                                                                                                                                                                                                | 62                                                                   |

|   | 2.25                                                                                          | Electrical Characteristics                                                                                                                                                                                                                                                                                                                                                                                                     | 62                                                                   |

|   | 2.26                                                                                          | Timing Diagrams                                                                                                                                                                                                                                                                                                                                                                                                                | 63                                                                   |

|   | Smar                                                                                          | tcard Interface                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

|   | 2.27                                                                                          | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

|   | 2.28                                                                                          | Features                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                      |

|   | 2.29                                                                                          | Block Diagram                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                      |

|   | 2.30                                                                                          | Functional Description                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                      |

|   | 2.31                                                                                          | Register Map                                                                                                                                                                                                                                                                                                                                                                                                                   |                                                                      |

|   | 2.32                                                                                          | Pin Description6                                                                                                                                                                                                                                                                                                                                                                                                               | 69                                                                   |

| 3 | Security Subsyst                                                                              | em                                                                                                                                                                                                                                                                                                                                                                                                                             | 71                                                                   |

|   |                                                                                               | Block Diagram of Security Subsystem                                                                                                                                                                                                                                                                                                                                                                                            |                                                                      |

|   | 3.2                                                                                           | Introduction                                                                                                                                                                                                                                                                                                                                                                                                                   | 72                                                                   |

|   | 3.3                                                                                           | Features                                                                                                                                                                                                                                                                                                                                                                                                                       | 73                                                                   |

|   | CPU                                                                                           | of the Security Subsystem (XPU)                                                                                                                                                                                                                                                                                                                                                                                                | 74                                                                   |

|   | 3.4                                                                                           | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 74                                                                   |

|   |                                                                                               |                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                      |

|   | Hardy                                                                                         | ware Cipher Block                                                                                                                                                                                                                                                                                                                                                                                                              | 75                                                                   |

|   |                                                                                               | ware Cipher Block                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                      |

|   | 3.5                                                                                           | ·                                                                                                                                                                                                                                                                                                                                                                                                                              | 75                                                                   |

|   | 3.5<br><b>Boot</b>                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br><b>77</b>                                                      |

|   | 3.5<br>Boot<br>Seria                                                                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br><b>77</b><br><b>78</b>                                         |

|   | 3.5<br>Boot<br>Seria<br>XPU                                                                   | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br><b>77</b><br><b>78</b><br><b>80</b>                            |

|   | 3.5  Boot  Seria  XPU  3.6                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br><b>77</b><br><b>78</b><br><b>80</b>                            |

|   | 3.5  Boot  Seria  XPU  3.6                                                                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br><b>77</b><br><b>78</b><br><b>80</b><br>80                      |

|   | 3.5  Boot Seria XPU 3.6 3.7 3.8                                                               | Description           ROM           I Flash           Timers           Introduction           Features                                                                                                                                                                                                                                                                                                                         | 75<br><b>77</b><br><b>78</b><br><b>80</b><br>80<br>80                |

|   | 3.5  Boot Seria XPU  3.6 3.7 3.8 3.9                                                          | Description         ROM           I Flash         Introduction           Features         8           Block Diagram         8                                                                                                                                                                                                                                                                                                  | 75<br>77<br>78<br>80<br>80<br>80<br>80                               |

|   | 3.5  Boot Seria XPU  3.6 3.7 3.8 3.9                                                          | Description         ROM           I Flash         Introduction           Introduction         8           Features         8           Block Diagram         8           Functional Description         8                                                                                                                                                                                                                      | 75<br>77<br>78<br>80<br>80<br>80<br>81<br>83                         |

|   | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9 XPU I                                                     | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>77<br>78<br>80<br>80<br>80<br>81<br>83                         |

|   | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9  XPU I 3.10                                               | Description  ROM  I Flash  Introduction  Features  Block Diagram  Functional Description  Interrupt Controller  Introduction                                                                                                                                                                                                                                                                                                   | 75 77 78 80 80 80 81 83 83                                           |

|   | 3.5  Boot Serial XPU 3.6 3.7 3.8 3.9  XPU I 3.10 3.11                                         | Description         ROM           I Flash         Introduction           Introduction         8           Features         8           Block Diagram         8           Functional Description         8           Interrupt Controller         8           Introduction         8           Features         8           Block Diagram         8                                                                             | 75<br>77<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>83             |

|   | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9  XPU I 3.10 3.11 3.12 3.13 Bus a                          | Description         ROM           I Flash         Introduction           Features         8           Block Diagram         8           Functional Description         8           Interrupt Controller         9           Introduction         10           Features         10           Block Diagram         10           Functional Description         10           Accessibility         10                            | 75<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>84<br>84<br>84       |

|   | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9  XPU I 3.10 3.11 3.12 3.13 Bus a                          | Description                                                                                                                                                                                                                                                                                                                                                                                                                    | 75<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>84<br>84<br>84       |

| 4 | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9  XPU I 3.10 3.11 3.12 3.13 Bus a 3.14                     | Description         ROM           I Flash         Introduction           Features         8           Block Diagram         8           Functional Description         8           Interrupt Controller         9           Introduction         10           Features         10           Block Diagram         10           Functional Description         10           Accessibility         10                            | 75<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>84<br>84<br>88       |

| 4 | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9 XPU I 3.10 3.11 3.12 3.13 Bus a 3.14  IPU Subsystem .     | Description         ROM           I Flash         Introduction           Features         8           Block Diagram         8           Functional Description         8           Interrupt Controller         9           Introduction         9           Features         8           Block Diagram         8           Functional Description         8           accessibility         9           Description         9 | 75<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>84<br>84<br>88<br>88 |

| 4 | 3.5  Boot Seria XPU 3.6 3.7 3.8 3.9 XPU I 3.10 3.11 3.12 3.13 Bus a 3.14  IPU Subsystem . 4.1 | Description  ROM  I Flash  Timers  Introduction  Features  Block Diagram  Functional Description  Introduction  Features  Soluterrupt Controller  Introduction  Features  Block Diagram  Functional Description  Soluterrupt  Features  Block Diagram  Features  Block Diagram  Functional Description  Soluterrupt  Functional Description  Soluterrupt  Functional Description  Soluterrupt  Functional Description          | 75<br>78<br>80<br>80<br>80<br>81<br>83<br>83<br>84<br>88<br>88<br>88 |

|   | IPU I          | Processor                              | 94         |

|---|----------------|----------------------------------------|------------|

|   | 4.4            | Description                            | 94         |

| 5 | DRAM Controlle | rs                                     | 95         |

|   | 5.1            |                                        |            |

|   | 5.2            | Introduction                           | 9 <i>6</i> |

|   | 5.3            | Features                               | 96         |

|   | 5.4            | Functional Description                 | 97         |

|   | 5.5            | Pin Description                        | 105        |

|   | 5.6            | Electrical Characteristics             | 111        |

| 6 | System Block   |                                        | 113        |

|   | 6.1            | Block Diagram of System Block          | 113        |

|   | 6.2            | Introduction                           | 114        |

|   | GPIC           | ) Block                                | 114        |

|   | 6.3            | General Purpose I/O (GPIO)             | 114        |

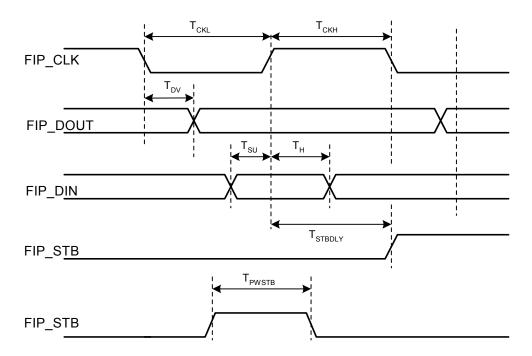

|   | 6.4            | Front Panel Controller Interface (FIP) | 122        |

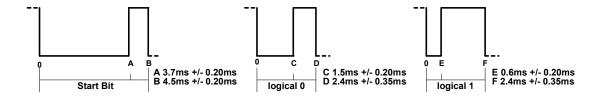

|   | 6.5            | Infrared Decoder                       | 126        |

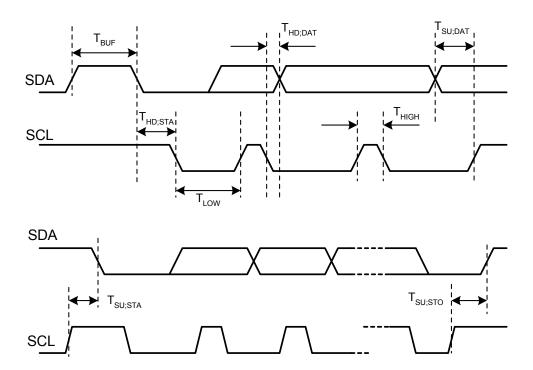

|   | Inter          | Integrated Circuits (I2C)              | 132        |

|   | 6.6            | Introduction                           | 132        |

|   | 6.7            | Features                               | 132        |

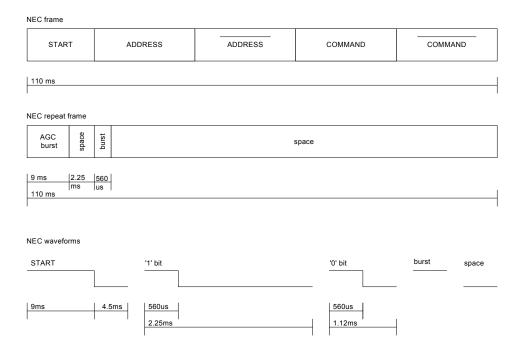

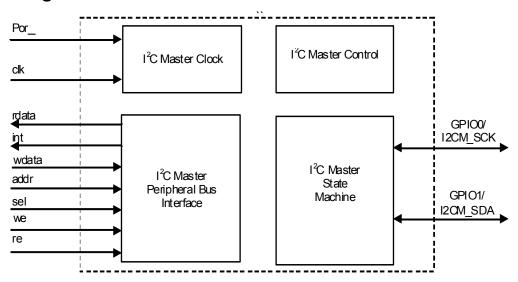

|   | 6.8            | Block Diagram                          | 133        |

|   | 6.9            | Functional Description                 | 134        |

|   | 6.10           | Register Maps                          | 138        |

|   | 6.11           | Pin Description                        | 139        |

|   | 6.12           | Electrical Characteristics             | 140        |

|   | 6.13           | Timing Diagrams                        | 140        |

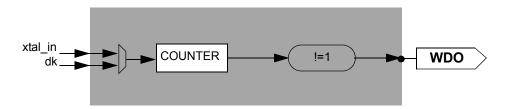

|   | Wate           | hdog                                   | 141        |

|   | 6.14           | Introduction                           | 141        |

|   | 6.15           | Block Diagram                          | 141        |

|   | 6.16           | Functional Description                 | 141        |

|   | 6.17           | Register Map                           | 143        |

|   | 6.18           | Pin Description                        | 143        |

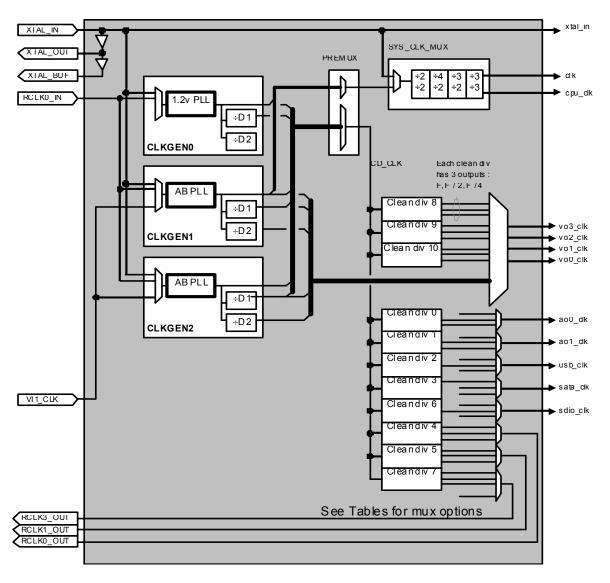

|   | Cloc           | k Generator                            | 143        |

|   | 6.19           | Introduction                           | 143        |

|   | 6.20           | Features                               | 144        |

|   | 6.21           | 3                                      |            |

|   | 6.22           |                                        |            |

|   | 6.23           | -3                                     |            |

|   | 6.24           |                                        |            |

|   | 6.25           | Electrical Characteristics             | 154        |

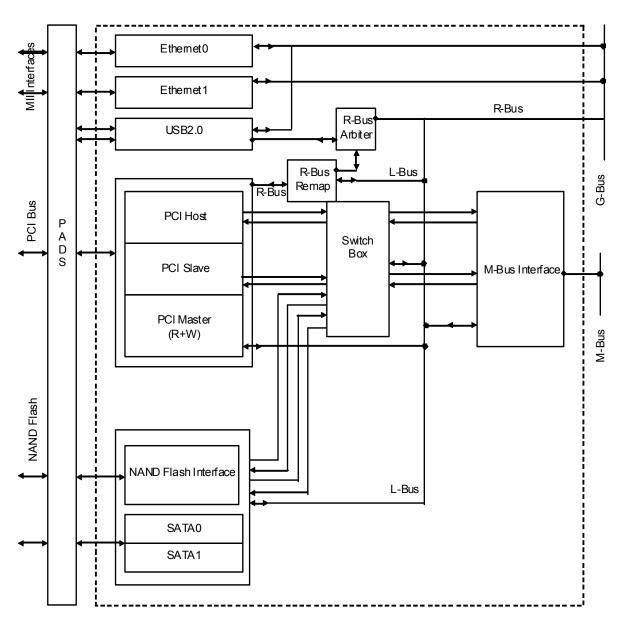

| 7 | Host Interface  |                                          | 155 |

|---|-----------------|------------------------------------------|-----|

|   | 7.1             | Block Diagram of Host Interface          | 155 |

|   | 7.2             | Introduction                             | 156 |

|   | PCI             | Master/Slave/Host Interface              | 156 |

|   | 7.3             | Introduction                             | 156 |

|   | 7.4             | Features                                 | 156 |

|   | 7.5             | Functional Description                   | 157 |

|   | 7.6             | Register Map                             | 163 |

|   | 7.7             | Pin Descriptions                         |     |

|   | 7.8             | Electrical Characteristics               | 169 |

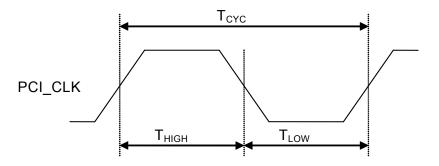

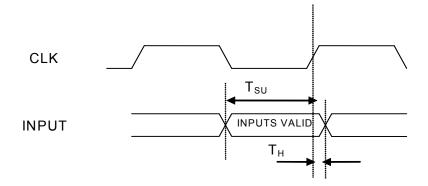

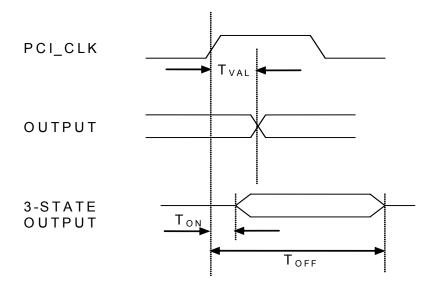

|   | 7.9             | Timing Diagrams                          | 170 |

|   | USB             | 2.0 Embedded Host Interface              | 172 |

|   | 7.10            | Functional Description                   | 172 |

|   | 7.11            | real Processing                          |     |

|   | 7.12            |                                          |     |

|   | Ethe            | rnet Interface                           |     |

|   | 7.13            | Pin Description                          | 179 |

|   | 7.14            |                                          |     |

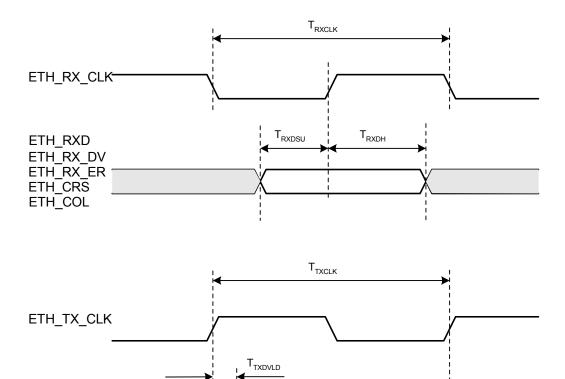

|   | 7.15            | Timing Diagram                           | 182 |

|   | NAN             | D Flash Interface                        | 183 |

|   | 7.16            | Introduction                             | 183 |

|   | 7.17            |                                          |     |

|   | 7.18            | Functional Description                   | 183 |

|   | 7.19            | -3                                       |     |

|   | 7.20            | real Processing                          |     |

|   | 7.21            |                                          |     |

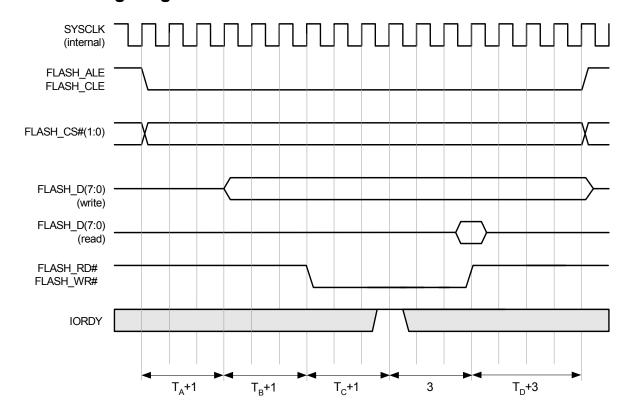

|   | 7.22            | 3 - 3 -                                  |     |

|   | SATA            | A Interface                              |     |

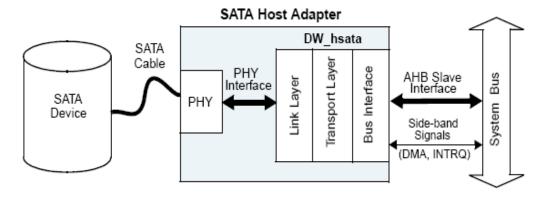

|   | 7.23            |                                          |     |

|   | 7.24            | Features                                 |     |

|   | 7.25            |                                          |     |

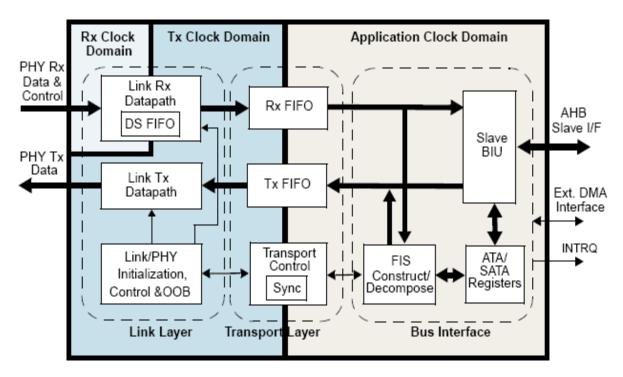

|   | 7.26            | •                                        |     |

|   | 7.27            |                                          |     |

|   | 7.28            |                                          |     |

| 8 | Video Decoder S | ubsystem                                 | 197 |

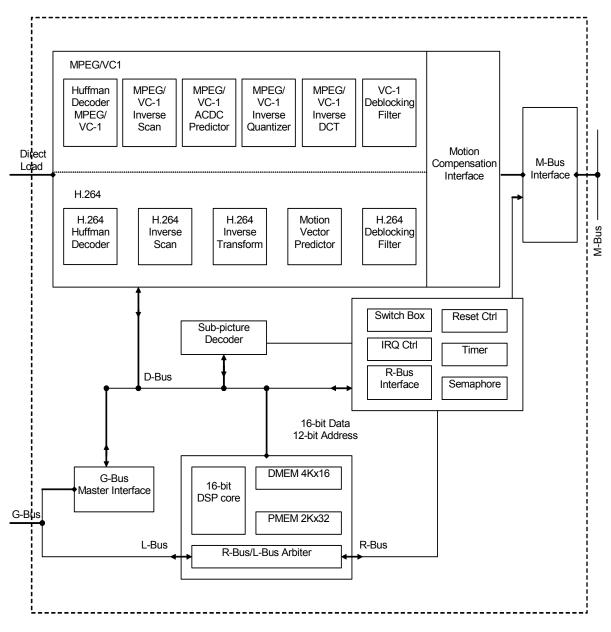

|   | 8.1             | Block Diagram of Video Decoder Subsystem | 197 |

|   | 8.2             | Introduction                             |     |

|   | 8.3             | Features                                 |     |

|   | 8.4             | Functional Description                   | 200 |

| 9  | Video Processing | g Subsystem                                 | 205   |

|----|------------------|---------------------------------------------|-------|

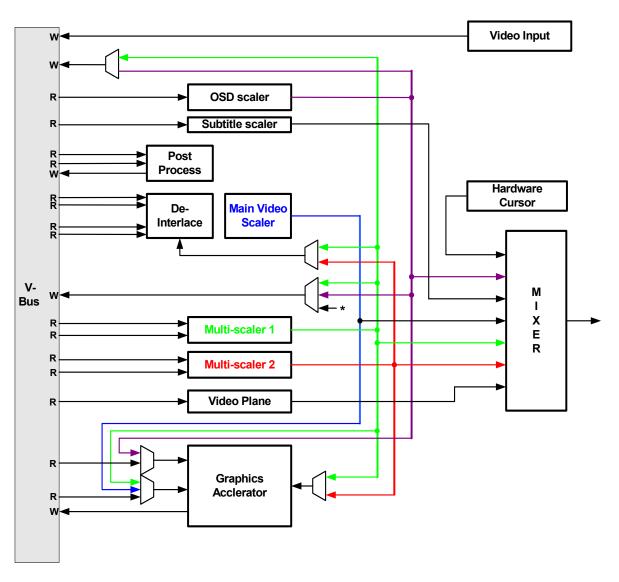

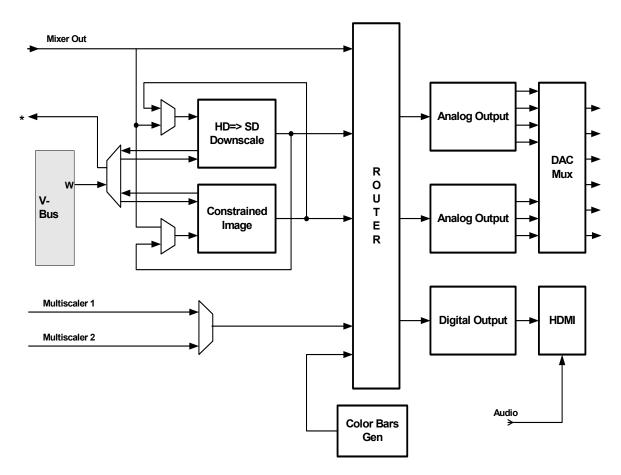

|    | 9.1              | Block Diagram of Video Processing Subsystem | . 205 |

|    | 9.2              | Introduction                                | 207   |

|    | 9.3              | Features                                    | . 208 |

|    | 9.4              | Functional Description                      | . 209 |

|    | 9.5              | Register Maps                               | . 278 |

|    | 9.6              | Pin Description                             | . 288 |

|    | 9.7              | Electrical Characteristics                  | . 292 |

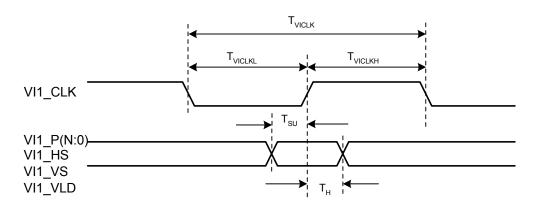

|    | 9.8              | Timing Diagrams                             | 294   |

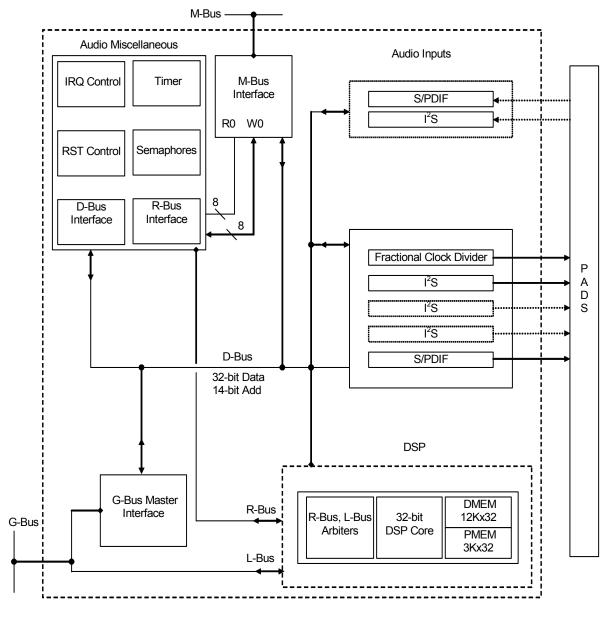

| 10 | Audio Processi   | ng Subsystem                                | 295   |

|    | 10.1             | Block Diagram of Audio Processing Subsystem | 295   |

|    | 10.2             | Introduction                                | 296   |

|    | 10.3             | Features                                    | 296   |

|    | 10.4             | Functional Description                      | 297   |

|    | 10.5             | Register Maps                               | . 309 |

|    | 10.6             | Pin Description                             | 312   |

|    | 10.7             | Electrical Characteristics                  | . 313 |

|    | 10.8             | Timing Diagram                              | 314   |

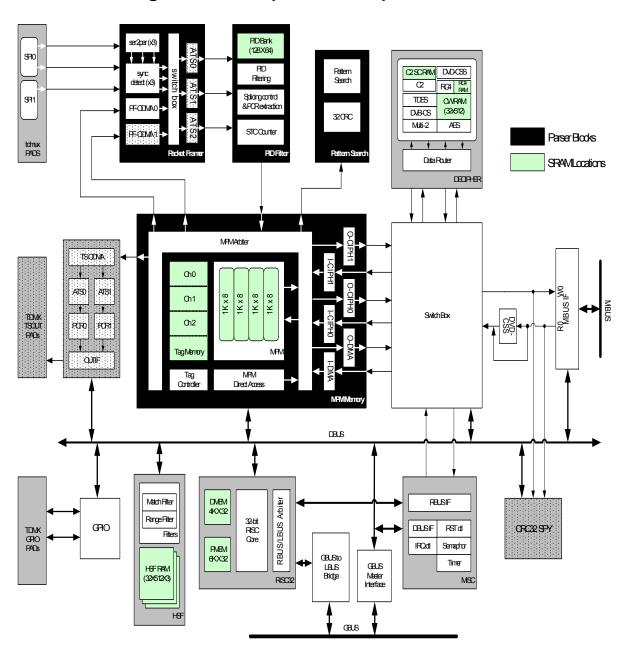

| 11 | Transport Demu   | ıltiplexer                                  | 315   |

|    | 11.1             | Block Diagram of Transport Demultiplexer    | 315   |

|    | 11.2             | Introduction                                | 316   |

|    | 11.3             | Features                                    | . 316 |

|    | 11.4             | Functional Description                      | 318   |

|    | 11.5             | Pin Description                             | 339   |

|    | 11.6             | Electrical Characteristics                  | 340   |

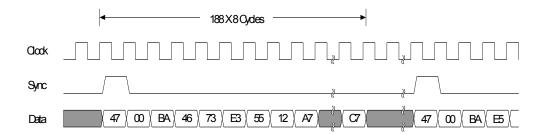

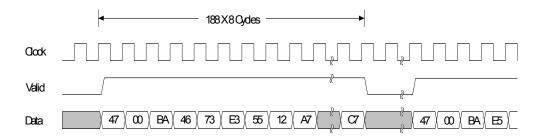

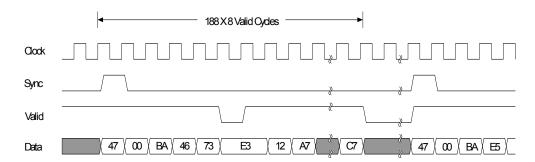

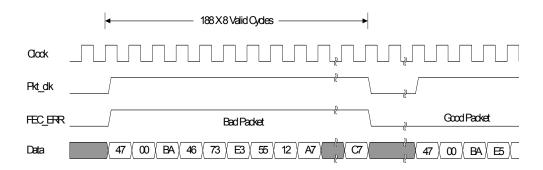

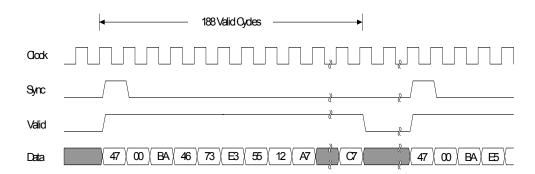

|    | 11.7             | Timing Diagrams                             | . 341 |

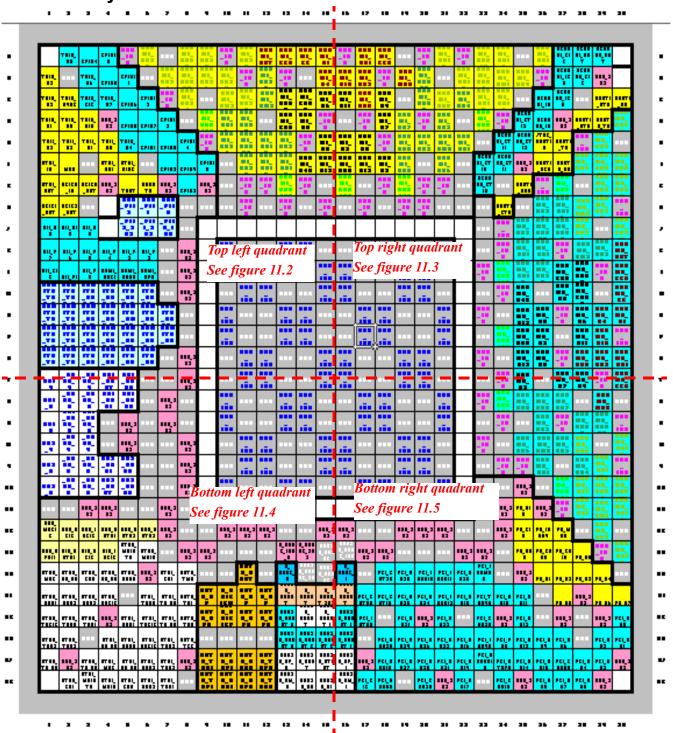

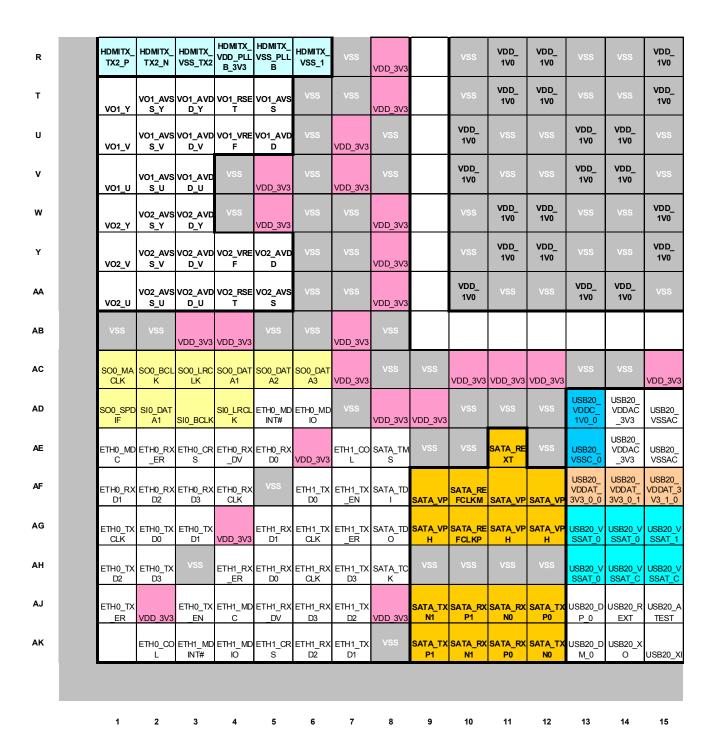

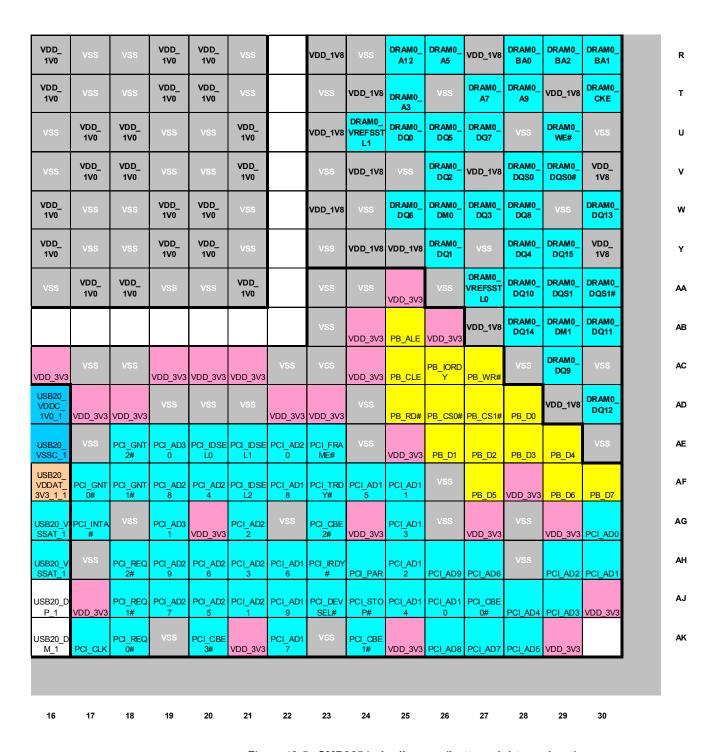

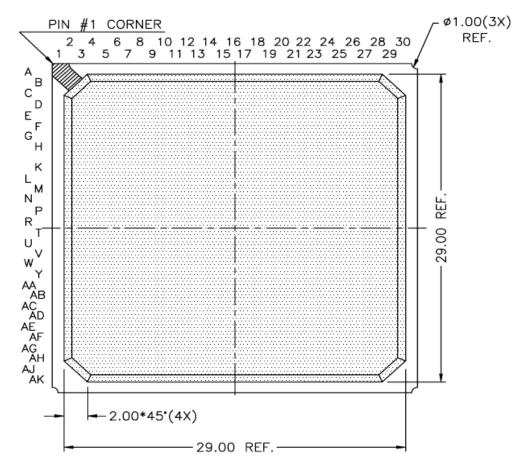

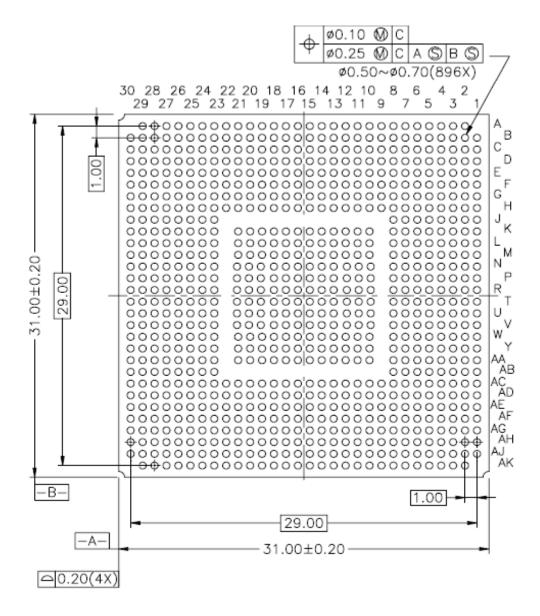

| 12 | Pin Information  |                                             | 345   |

|    | 12.1             | Pin Layout                                  |       |

|    | 12.2             | Pin Listing by Pin Id                       | 350   |

|    | 12.3             | Pin Listing by Pin Name                     | 360   |

|    | 12.4             | Miscellaneous Pins                          | 370   |

| 13 | System Specific  | cations                                     | 371   |

|    | 13.1             | Electrical Specifications                   | 371   |

|    | 13.2             | Power Consumption                           | 373   |

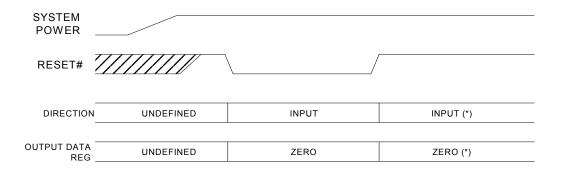

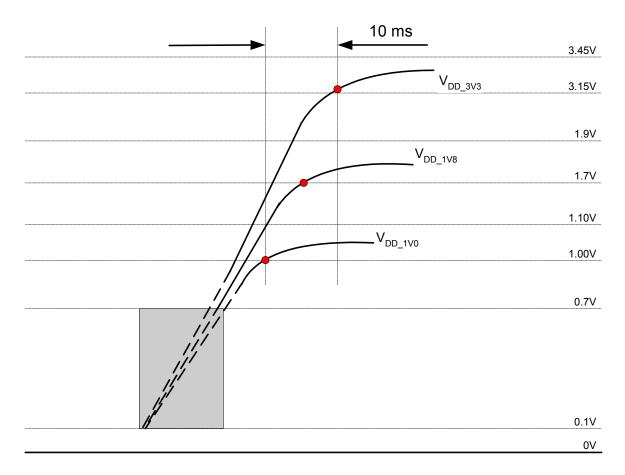

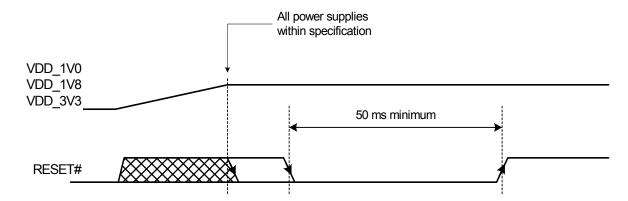

|    | 13.3             | Power Supply Sequencing                     | 374   |

|    | 13.4             | Thermal Specifications                      | 389   |

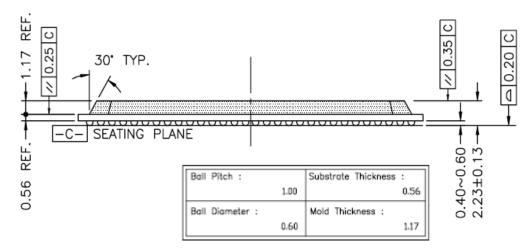

|    | 13.5             | Mechanical Specifications                   | 390   |

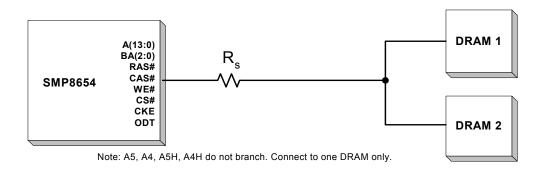

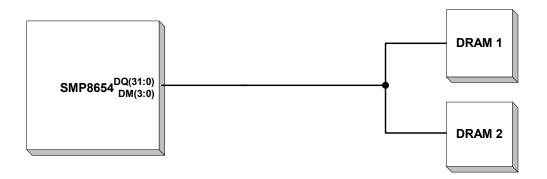

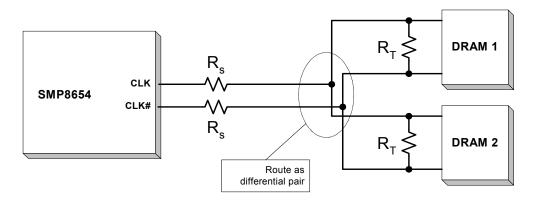

| 14 | DDR Implement    | ation                                       | 393   |

|    | •                | Memory System Implementation Guidelines     |       |

| 15  | Ordering I   | Inform  | ation                                 | 397 |

|-----|--------------|---------|---------------------------------------|-----|

|     |              | 15 (    | Ordering Information                  | 397 |

| 16  | Licensing    |         |                                       | 399 |

|     |              | 16.1    | Licensing                             | 399 |

| 17  | Appendix     |         |                                       | 403 |

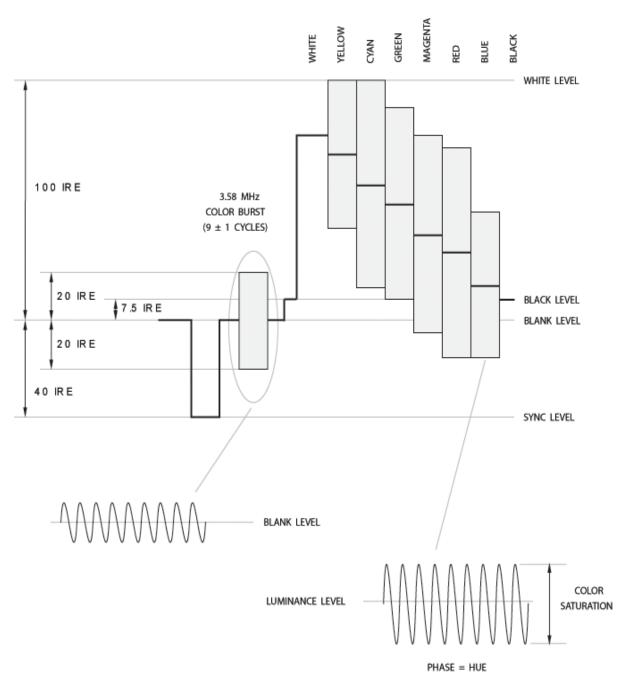

|     |              | 17.1    | Basic Analog Video Parameters         | 403 |

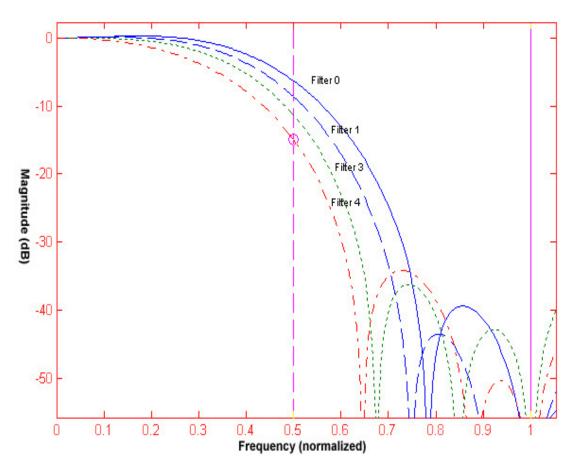

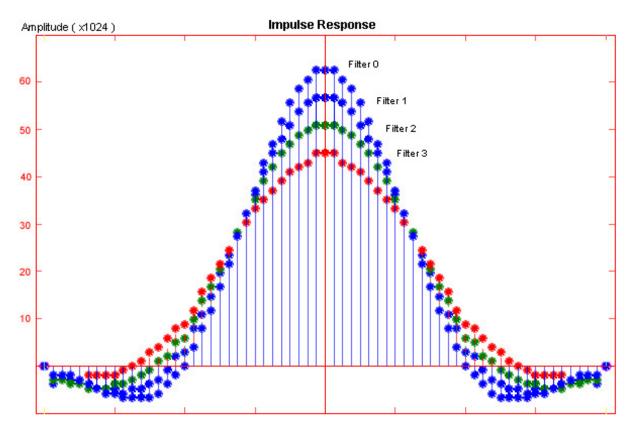

|     |              | 17.2    | Main Video Scaler Filters             | 405 |

|     |              | 17.3    | Color Space Conversion Basic Matrices | 407 |

|     |              |         | Video Output Scaling Examples         |     |

|     |              | 17.5    | SDTV vs. HDTV Colorimetry Example     | 412 |

|     |              |         | Supported Media Formats               |     |

|     |              |         | Supported File Formats                |     |

|     |              | 17.8    | Supported Broadcast Formats           | 422 |

|     |              |         | Raster Operations                     |     |

| Lis | t of Figures | <b></b> |                                       | 433 |

|     |              |         |                                       |     |

# **Conventions**

This section presents the acronyms, abbreviations, units of measurement and other conventions used in this datasheet.

# 0.1 Acronyms and Abbreviations

The acronyms and abbreviations used in this datasheet are listed alphabetically in the table below:

Table 0-1 Acronyms and abbreviations

| Acronym/Abbreviation | Definition                                          |

|----------------------|-----------------------------------------------------|

| 2D/3D                | 2 Dimensional/3 Dimensional                         |

| AC                   | Alternating Current                                 |

| ADC                  | Analog-to-Digital Converter                         |

| ATA                  | AT Attachment                                       |

| AV or A/V            | Audio Visual                                        |

| BGA                  | Ball Grid Array                                     |

| BPP                  | Bits per Pixel                                      |

| CMOS                 | Complementary Metal Oxide Semiconductor             |

| CODEC                | Coder/Decoder                                       |

| CPU                  | Central Processing Unit                             |

| CSS                  | Cascading Style Sheets or Content Scrambling System |

| D/A                  | Digital-to-Analog                                   |

| DAA                  | Data Access Arrangement                             |

| DAC                  | Digital-to-analog Converter                         |

| DC                   | Direct Current                                      |

| DDR SDRAM            | Double Data Rate Synchronous DRAM                   |

| DMA                  | Direct Memory Access                                |

| DRAM                 | Dynamic Random-access Memory                        |

| DSL                  | Digital Subscriber Line                             |

Table 0-1 Acronyms and abbreviations

| Acronym/Abbreviation | Definition                                     |

|----------------------|------------------------------------------------|

| DSP                  | Digital Signal Processor                       |

| DVD                  | Digital Versatile Disc or Digital Video Disc   |

| DVI                  | Digital Visual Interface                       |

| EHCI                 | Extended Host Controller Interface             |

| EJTAG                | Enhanced Joint Test Action Group               |

| EIA                  | Electronic Industries Alliance                 |

| FCS                  | Frame Check Sequence                           |

| FIFO                 | First In/First Out                             |

| GPIO                 | General Purpose Input/Output                   |

| HDMI                 | High-Definition Multimedia Interface           |

| HDTV                 | High-Definition Television                     |

| I                    | Input                                          |

| I/O                  | Input/Output                                   |

| I <sup>2</sup> C     | Inter Integrated Circuit                       |

| IDE                  | Integrated Drive Electronics                   |

| IEC                  | International Electrotechnical Commission      |

| IPTV                 | Internet Protocol TV                           |

| IR                   | Infrared                                       |

| IRQ                  | Interrupt Request Line                         |

| ISO                  | International Organization for Standardization |

| JPEG                 | Joint Photographic Experts Group               |

| LCD                  | Liquid Crystal Display                         |

| LSB                  | Least Significant Bit/Byte                     |

| MIPS                 | Millions of Instructions per Second            |

| MMU                  | Memory Management Unit                         |

| MPEG                 | Moving Picture Experts Group                   |

| MSB                  | Most Significant Bit/Byte                      |

| 0                    | Output                                         |

| OHCI                 | Open Host Controller Interface                 |

| OSD                  | On Screen Display                              |

# Table 0-1 Acronyms and abbreviations

| Acronym/Abbreviation | Definition                                                                         |

|----------------------|------------------------------------------------------------------------------------|

| P/U                  | Pull-up Resistor                                                                   |

| PCB                  | Printed Circuit Board                                                              |

| PCI                  | Peripheral Component Interconnect                                                  |

| PID                  | Program Id                                                                         |

| PIP                  | Picture In Picture                                                                 |

| PKI                  | public key infrastructure                                                          |

| PLL                  | Phase Locked Loop                                                                  |

| PVR                  | Personal Video Recorder                                                            |

| RAM                  | Random Access Memory                                                               |

| RGB                  | Red Green Blue                                                                     |

| RISC                 | Reduced Instruction Set Computer                                                   |

| ROM                  | Read Only Memory                                                                   |

| RTC                  | Real-time Clock                                                                    |

| S/PDIF               | Sony/Philips Digital Interface                                                     |

| SDTV                 | Standard Definition Television                                                     |

| SPI                  | Synchronous Parallel Interface                                                     |

| SRAM                 | Static Random Access Memory                                                        |

| SSI                  | Synchronous Serial Interface                                                       |

| SSI                  | Server-side Include or Single-system Image                                         |

| TDMX                 | Transport Demultiplexer                                                            |

| TLB                  | Translation Look-aside Buffer                                                      |

| TMDS                 | Transition Minimized Differential Signaling                                        |

| UART                 | Universal Asynchronous Receiver Transmitter                                        |

| USB                  | Universal Serial Bus                                                               |

| VOD                  | Video On Demand                                                                    |

| YCbCr                | Y is brightness (luma), Cb is blue minus luma (B-Y) and Cr is red minus luma (R-Y) |

# 0.2 Units of Measurement

The units of measurement used in this datasheet are listed alphabetically in the table below:

Table 0-2 Units of measurement

| Symbol         | Unit of measurement                  |

|----------------|--------------------------------------|

| μΑ             | microampere                          |

| μF             | microfarad                           |

| μs             | microsecond (1,000 nanoseconds)      |

| <sup>0</sup> C | degree Celsius                       |

| GB             | gigabyte                             |

| bpp            | Bits Per Pixel                       |

| Hz             | Hertz (cycles per second)            |

| kohm           | kiloohm                              |

| Kb             | kilobit                              |

| КВ             | kilobyte (1,024 Bytes)               |

| Kbps           | kilobit per second                   |

| KBps           | kilobyte per second                  |

| KHz            | kilohertz                            |

| mA             | milliampere                          |

| Mbps           | megabit per second                   |

| MBps           | megabyte (1,048,576 bits) per second |

| Mb             | megabit                              |

| MB             | megabyte (1,048,576 bytes)           |

| MHz            | megahertz (1,000 kilohertz)          |

| ms             | millisecond (1,000 micro seconds)    |

| ns             | nanosecond                           |

| V              | volt                                 |

| W              | watt                                 |

|                |                                      |

5

# 0.3 General Conventions

#### **Numbers and Number Bases**

- Binary numbers are enclosed in single quotation marks when in text, e.g., '1' designates a binary number.

- Binary numbers are written with a lower case 'b' suffix. e.g., 16b.

- Binary numbers larger than four digits are written with a space dividing each group of four digits, as in 1011 0101 1010b.

Note: All other numbers are decimal.

#### **Naming Conventions**

- The register acronyms appear in capital letters such as SDIOVH or SDIN\_EGD\_HDG

- Register bits are listed in square brackets MSB-to-LSB separated by a colon mark, e.g., SDHE[3:0].

- TBD indicated that the values are 'to be determined', NA or N/A indicate 'not available' and NC indicates that a pin is 'no connect'.

1 Introduction

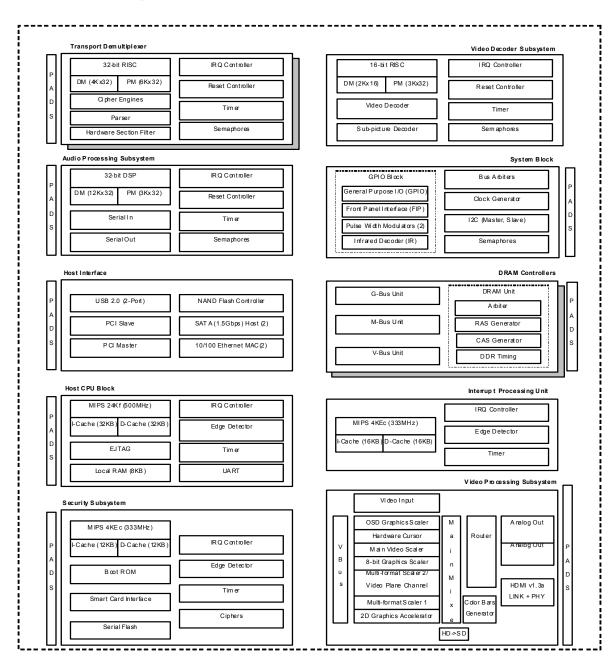

# 1.1 Block Diagram of SMP8654

Figure 1-1 SMP8654 block diagram

## 1.2 Main Features of SMP8654

#### Host CPU

- Embedded 500MHz MIPS 24Kf for operating system, middleware and applications

- 32KB instruction and 32KB data caches

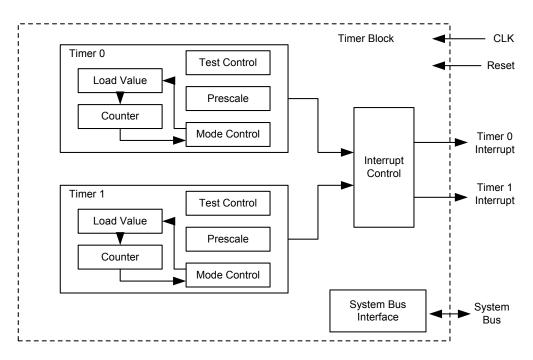

- Interrupt controller and timers

- Highly secure DRM/CA solution

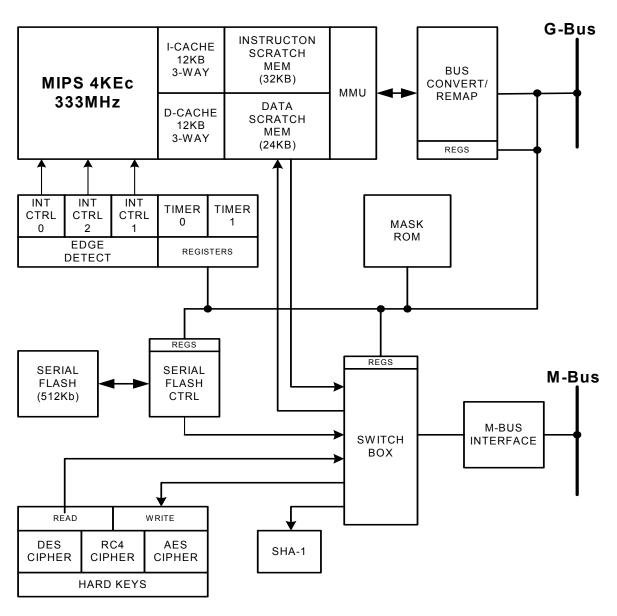

- Separate 333MHz MIPS 4KEc CPU to securely execute DRM and conditional access software

- 12KB instruction and 12KB data caches

- 32KB instruction scratch memory and 24KB data scratch memory

- Encrypted DRAM and flash memory, secure boot loader, secure PKI, encrypted I/O interfaces

- Supports a wide variety of DRM and conditional access solutions

#### IO standards

- 32-bit PCI v2.1 (33 or 66MHz) bus master/slave/host

- NAND Flash Interface supports up to 8GB of external memory (bootable)

- Dual SATA (1.5Gbps) host ports

- Supports Ethernet 10/100 (2 ports)

- Supports USB2.0 (2 ports)

- Front panel controller interface supports NEC uPD16311, NEC uPD16312, PTC PT6311 and PTC PT6312 front panel controllers

- Two ISO 7816 smartcard interfaces

- I<sup>2</sup>C master/slave interfaces

- 8-bit parallel DVB-SPI transport stream interface plus single serial interface, or triple serial transport stream interface

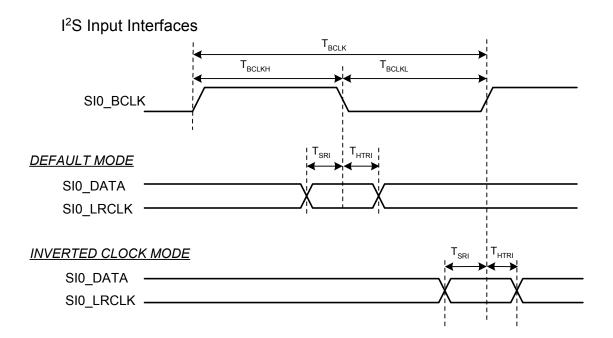

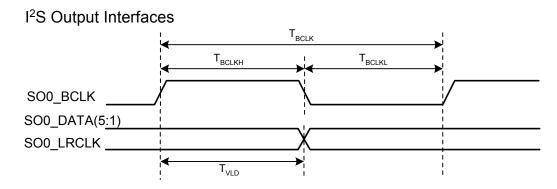

- I<sup>2</sup>S interface up to 20Mbps

- Two UARTs

- 16 dedicated general purpose I/O pins (up to 77 total GPIO)

#### Video decoding standards

- Video decoding of MPEG-1, MPEG-2 MP@HL, MPEG-4.2 ASP@L5 (720p), MPEG-4.10 (H.264) BP@L3, MP@L4.0 and HP@L4.0, WMV9 MP@HL, SMPTE 421M (VC-1) MP@HL, AP@L3, AVS Jizhun profile @ L2.0, 4.0, and 6.0

- Hardware accelerated Baseline JPEG decoding

- DVD-Video and Superbit DVD

- \* CSS decryption

- \* 16:9 and 4:3 playback, letterbox, 3:2 pull-down

- Multiple angles and sub-picture

- Error concealment, deblocking filter

- Elementary video stream bit rate

- \* MPEG-2 SDTV (HDTV): 20 (40) Mbps maximum

- \* MPEG-4.2 SDTV (HDTV): 20 (40) Mbps maximum

- \* MPEG-4.10 (H.264) SDTV (HDTV): 20 (40) Mbps maximum

- \* WMV9/SMPTE 421M (SMPTE 421M (VC-1)) SDTV (HDTV): 20 (40) Mbps maximum

#### Video processing

- Brightness, color and contrast controls for each output port

- Hardware cursor (4096 pixels, 4-bpp, up to 255 pixels horizontally and vertically)

- 2D graphics accelerator (up to 100M pixels per second operation for most operations)

- \* Line, Rectangle, Ellipse and Circle: generate a single-color line, rectangle, ellipse or circle with optional gradient fill

- \* Blend: alpha blend one rectangular region onto another

- \* Move: move a rectangular region to another location

- \* Replace: modified version of Move

- \* Raster Operations: standard 256 Boolean operations

- OpenType/TrueType font rendering acceleration

- 32-bit OSD with flicker filtering and scaling

- Optional deinterlacing of interlaced sources

- Arbitrary scaling of video and graphics up to 1920x1080 pixels

- Alpha mixing of video, graphics, cursor and OSD

- Picture-in-Picture (PIP) support

#### Video interfaces

- NTSC/PAL composite and s-video outputs with optional Macrovision protection

- 2 analog YPbPr/RGB video outputs with optional Macrovision protection in 480i, 576i, 480p and 576p YPbPr output modes (12-bit DACs, interlaced or progressive, SDTV or HDTV resolution)

- Integrated HDMI v1.3a A/V output interface includes 36-bpp deep color support, HDCP 1.3 content protection and integrated PHY

#### Audio processing and interfaces

- DSP based audio decoding

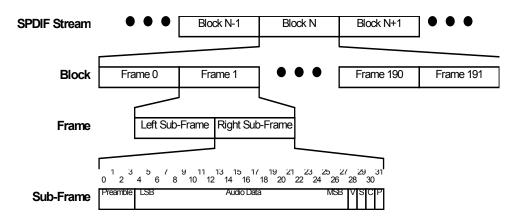

- I<sup>2</sup>S and S/PDIF digital audio input interface

- DSP includes 3 I<sup>2</sup>S serial digital outputs to support 5.1-channel audio output

- Digital serial S/PDIF (IEC 60958) audio output

#### Transport stream inputs

- Transport input interfaces

- \* One 8-bit DVB-SPI and one SSI, or 3 SSI, with polarity control of data valid signal

- \* PCI, SATA, Ethernet

- Transport demux supports 256 dedicated PIDs (aggregate)

- Transport input bit rate: 486Mbps maximum (aggregate)

- Dedicated MIPS 4KEc processor (IPU)

- Executes video display handler

- Can be optionally used for other main CPU off load and acceleration functions

- Media formats

- DVD-Video, SVCD (IEC 62107-2000), VCD 1.x and 2.0

- DVD-R, DVD-RW, DVD+R, DVD+RW (conditional)

- HDV

- Audio CD, CD-R, CD-RW, CompactFlash

- WMA, JPEG, MP3 and MPEG-4.2 AVI files using ISO 9660 format

- Picture CD (JPEG files using ISO 9660 format)

- Navigation software, HighMAT<sup>TM</sup> support

- Streaming formats

- ISMA (Internet Streaming Media Alliance) MPEG-4.2

- MPEG-2, MPEG-4

- WM9 with DRM

- MPEG-4.10 (H.264) and SMPTE 421M (VC-1) over MPEG-2 Transport

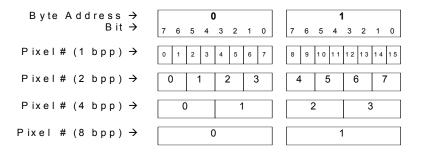

- On screen display

- High resolution, true-color OSD support

- 2, 4, 7, and 8-bpp from 24-bit palette

- Programmable OSD scaler

- Programmable flicker filter for interlaced output modes

- Alpha blending over video (8-bit)

- Operating system support

- Linux

- WinCE

# 1.3 Main Components of SMP8654

The SMP8654 is an advanced, single-chip audio/video decoder that provides highly-integrated solutions for HDTV, IPTV, MPEG-4.10 (H.264), WMV9, SMPTE 421M (VC-1) and AVS decoding. It incorporates flexible, advanced audio/video processing, enabling cost-effective solutions for consumer products, such as digital media adapters and IPTV set-top boxes.

The SMP8654 includes optimized features for tightly embedded applications such as TV/PDP integration, streaming video endpoints, and multifunction consumer appliances. The device also includes features that enable designers to easily incorporate advanced capabilities such as A/V streaming, Video-on-Demand (VOD) and Personal Video Recording (PVR) into their products.

In addition, the SMP8654 supports numerous popular media formats including DVD-Video, SVCD, VCD1.x, VCD2.0 and CD/CD-R/CD-RW (audio, JPEG, MP3 and MPEG-4 AVI files). It also supports ISMA MPEG-4 streaming format, and MPEG-4 over MPEG-2 transport streaming.

The SMP8654 architecture is composed of various hardware functional units – several incorporating custom-designed processor modules – interconnected by multiple high-speed synchronous data buses. Although the details of the on-chip buses are beyond the scope of this document, the primary buses and their functions are described below.

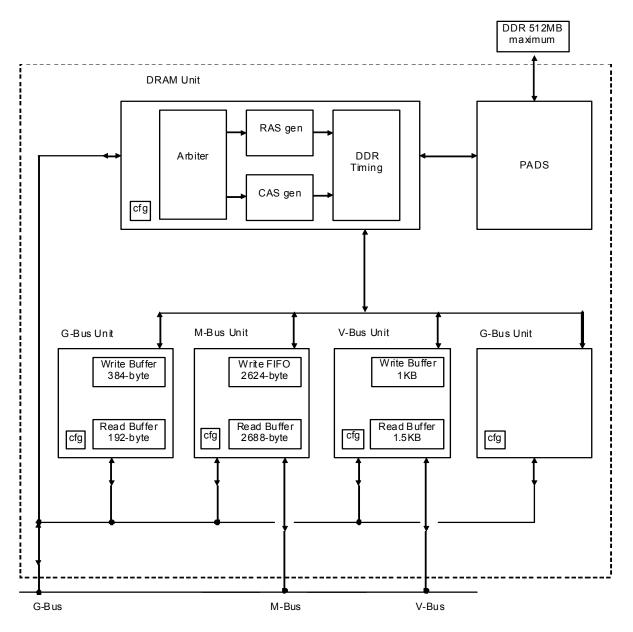

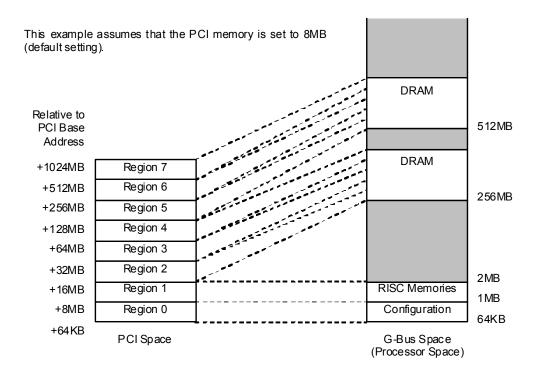

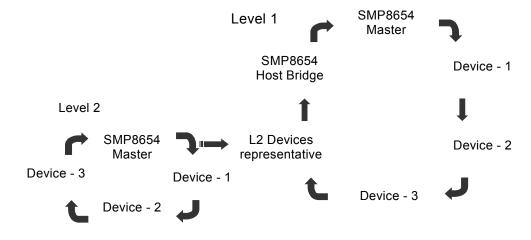

A 64-bit G-Bus connects the integrated MIPS host CPU with each functional unit. It provides access to the programmable configuration, control and status registers contained within each unit. The state of the device is initialized, controlled, and reconfigured as necessary through this bus. The G-Bus also supports direct access to the memory areas controlled by two memory controllers, PCI, flash memory areas and 32-bits of address and data (4G dwords addressable). It is an arbitrated, multi master bus.

The M-Bus provides the data path that allows each functional unit to communicate with the external memory controllers. It provides a 64-bit data path resulting in a peak data bandwidth of 2664MB/sec at a system clock frequency of 333MHz. The M-Bus arbitrates access among numerous DMA channels. An arbitration algorithm provides programmable bus bandwidth to be allocated and guaranteed to each DMA channel.

The V-Bus provides a dedicated high-speed data path between the video processing engine and the external memory controllers.

In addition to these device-wide buses, the various functional units typically have one or more dedicated local buses within the unit. These buses are not further described in this document.

The main modules of the SMP8654 are briefly described below. Each module is discussed in detail under their respective chapters.

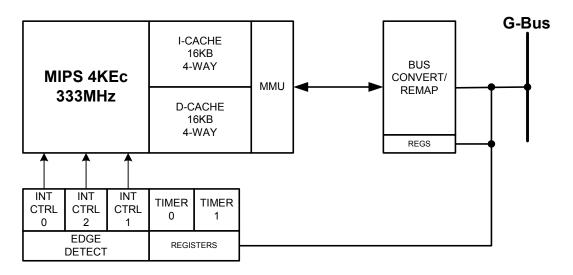

#### **Host CPU Block**

The host CPU block of the SMP8654 contains a 500MHz MIPS 24Kf CPU with its instruction and data cache to support the embedded operating system, middleware and applications required for consumer appliances. The supported operating systems include Linux and WinCE. The software for the CPU is loaded from an external flash using a secure boot loader.

In addition to the RISC processor itself, the host CPU block contains the following additional resources: 2K Dword (8KB) local memory, 3 interrupt controllers, edge detection logic, two programmable timers, two Universal Asynchronous Receiver/Transmitters (UARTs) and two ISO 7816 smartcard controllers.

#### **Security Processor Subsystem**

A separate 333MHz MIPS 4KEc CPU is used to securely execute conditional access and DRM software. The software for this CPU resides on an internal flash (encrypted and digitally signed) to facilitate upgrades and is loaded using a secure boot loader.

#### **DRAM Controllers**

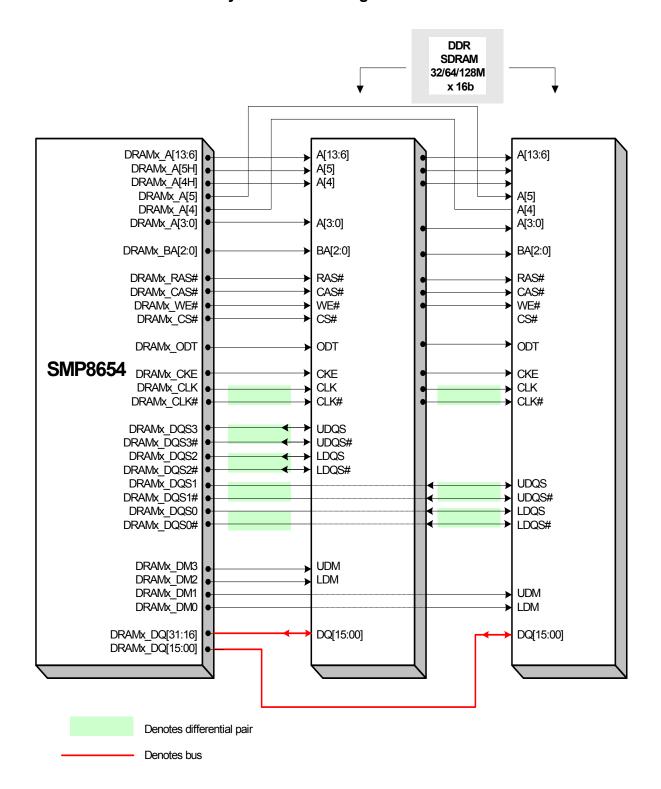

The SMP8654 contains two identical double-data rate synchronous DRAM (DDR-2) controllers operating at the memory clock rate (333MHz nominal). Because the DDR technology transfers data on both edges of the clock, the effective burst data bandwidth of each controller is 2.66GB/sec when using the full 32-bit interface (total peak bandwidth of 5.32GB/sec with 2 controllers). The DRAM controllers can each interface up to 512MB of external DDR-2 SDRAM.

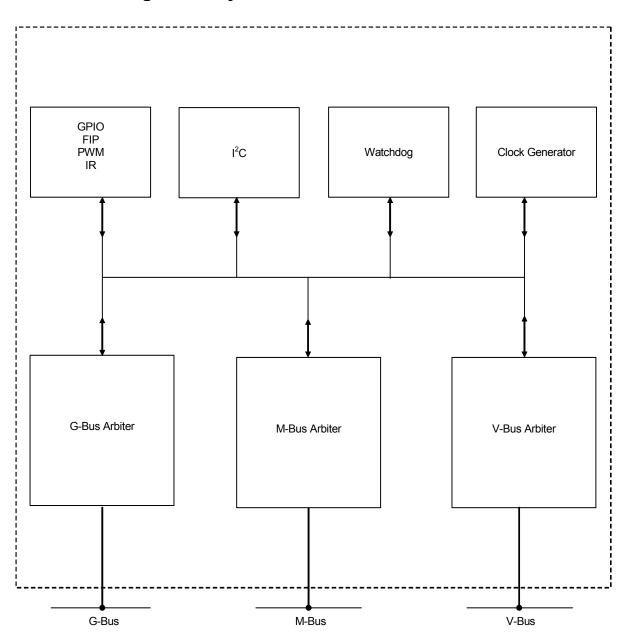

#### System Block

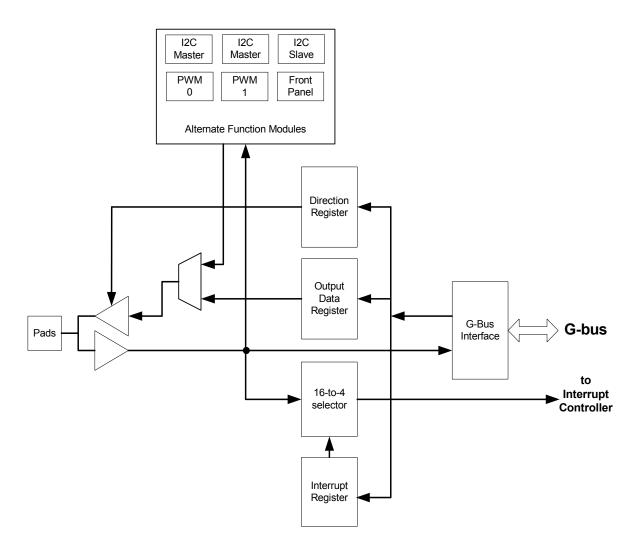

The SMP8654 system block contains the following modules: GPIO block, I<sup>2</sup>C master and slave controllers and a clock generator. The GPIO block in turn contains General Purpose I/O (GPIO) controller, Front Panel Interface (FIP) controller, Pulse Width Modulator (PWM) and an infrared decoder.

The general purpose I/O controller provides 16 pins of general purpose control signals and logic to help eliminate the glue logic necessary for system integration. Other interfaces can also be used to provide GPIO functionality (if not otherwise used); a total of 77 GPIO pins can be implemented.

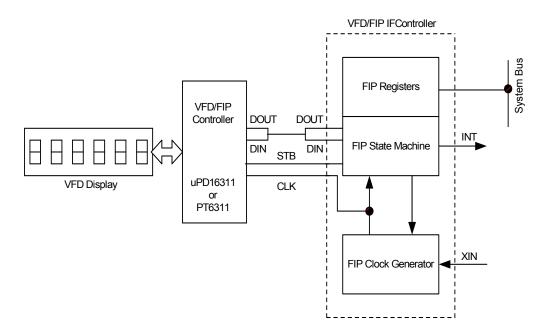

The Front Panel Interface (FIP) controller directly supports the NEC uPD16311, NEC uPD16312, PTC PT6311 and PTC PT6312. Other front panel controllers may be used by interfacing to the UART or the GPIO.

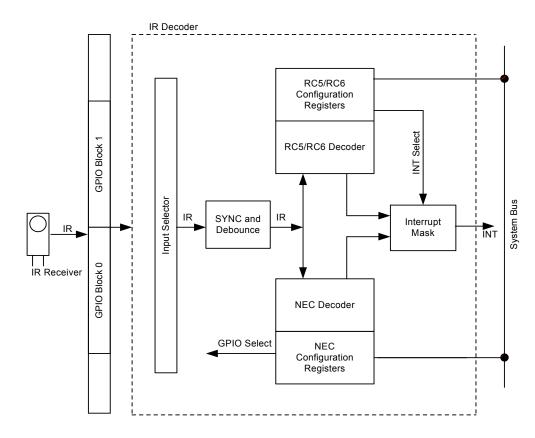

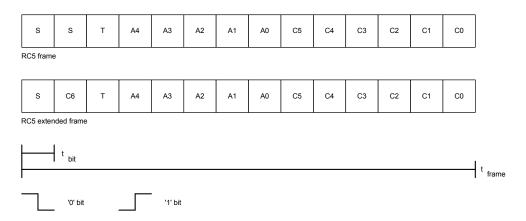

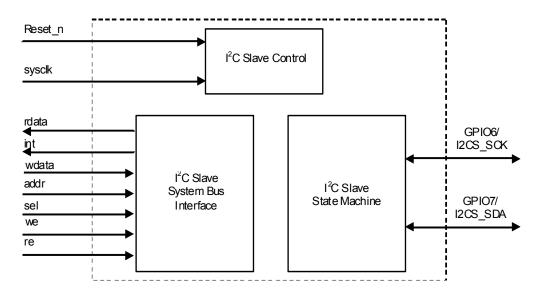

The infrared input allows the interfacing to an external IR receiver. The NEC and the Philips RC5/RC6 IR formats, commonly used by consumer equipment are supported.

The I<sup>2</sup>C master and slave interfaces enable the SMP8654 to read from and write to external devices. Two I<sup>2</sup>C master controllers, which support the synchronous Inter Integrated Circuits (I<sup>2</sup>C) serial protocol, enable the host CPU to access an external I<sup>2</sup>C slave device using a simplified register interface. A separate slave interface allows the SMP8654 to be the target of I<sup>2</sup>C transactions initiated by an external master.

The clock generator contains one audio clock, two video clocks, one system clock and one CPU clock. The clock generator creates two high speed clocks from a 27MHz external clock using two programmable PLLs, and creates the main system clock and multiple video and audio clocks by dividing either one of the high speed clocks or the 27MHz reference.

#### **Host Interface**

The host interface unit provides the interface between the primary internal buses (G-bus and M-bus) and the PCI, Ethernet and the USB 2.0.

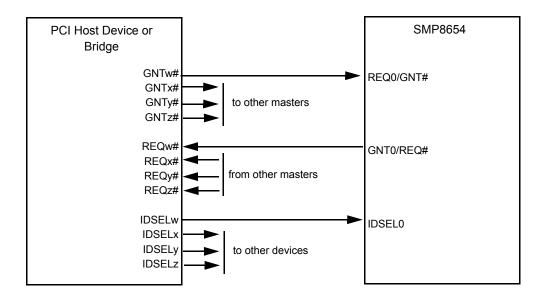

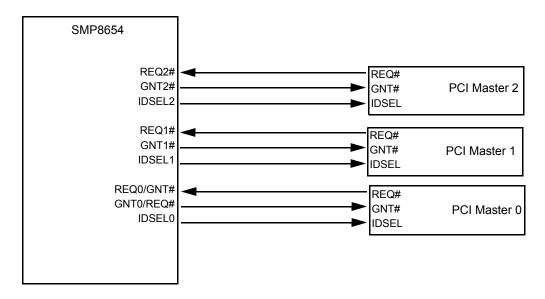

The SMP8654 supports a PCI bus for system-level interconnection. The PCI bus implementation is a version 2.1 compliant, 32-bit wide bus capable of operating at 33 or 66MHz.

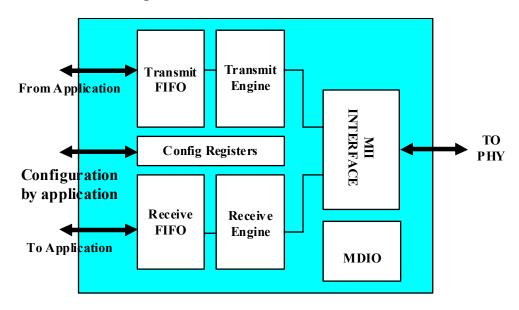

The SMP8654 includes a dual-port USB 2.0 Embedded Host Controller and integrated PHYs. It also includes 2 Ethernet 10/100 MACs with 2 MII (Media Independent Interface) interfaces to connect to an external PHY devices.

A NAND flash controller allows direct attachment of one or two NAND flash devices of up to 4GB capacity each for non-volatile storage of code and data. The NAND flash may be used as a boot device.

#### Video Decoder Subsystem

The SMP8654 contains a high-performance multi-codec video decoder. The video decoder subsystem executes the video decoding algorithms supported by the SMP8654. Its architecture is a hybrid of both processor-based and hardwired logic approaches.

The video decoder engine consists of a proprietary 16-bit RISC CPU which is augmented by a number of hardware functional units. These functional units perform the most compute-intensive portions of the video decompression algorithms supported by the SMP8654.

#### **Video Processing Subsystem**

The SMP8654 video processing engine provides sophisticated display processing, formatting and output capabilities. The video processing and display unit (VPD) has extensive capabilities for retrieving graphics and video images from the memory, formatting the images as needed, mixing the images and then presenting the video stream for display in a required format. Other capabilities provided by the VPD include hardware-assisted 2D graphics acceleration, and support for an external video input port.

The 3 available video outputs consist of 2 main analog outputs (6 DACs), and a digital HDMI interface. The 2 analog video outputs share the 6 DACs. The HDMI and analog component outputs can each support output formats up to 1920x1080p.

The SMP8654 contains an integrated HDMI transmitter. The HDMI transmitter block in the SMP8654 is HDMI v1.3a compliant, which transports consumer electronics standard digital video and digital audio over a TMDS interface. The HDMI unit supports the HDCP v1.3 content protection standard.

#### **Audio Processing Subsystem**

The SMP8654 contains an integrated audio subsystem based on a custom-designed 32-bit digital signal processor (DSP). Audio decoding and processing algorithms are fully executed on the DSP without special hardware support. This firmware-based approach gives great flexibility for accommodating future audio standards or specialized audio requirements. The audio unit provides 3 I<sup>2</sup>S output channels, one S/PDIF output channel, and one stereo I<sup>2</sup>S or S/PDIF audio input channel.

#### **Transport Demultiplexer**

The SMP8654 includes an on-chip, RISC processor-based transport demultiplexer (TDMX) unit. The transport demultiplexer block is capable of handling up to 6 multi-program bitstreams of up to 81Mbps each, with an aggregate total of up to 486Mbps.

#### Interrupt processing Unit (IPU)

A dedicated MIPS processor (32-bit 4KEc core) is integrated to off load certain low-latency processing requirements from the main CPU. Currently, the IPU primarily handles interrupts generated by the video processing subsystem, but may also be used to off load other system functions and accelerate performance-critical tasks. The IPU executes at 333MHz and includes 16KB instruction and data caches.

# 1.4 Application Examples

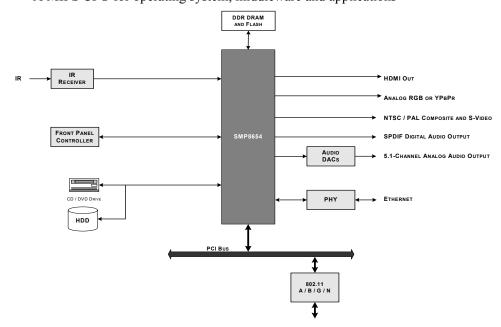

### 1.4.1 Networked DVD Player

The networked DVD player example below provides the typical functionality required for a networked DVD player. System integration requires very little external logic since the SMP8654 provides most of the features including:

- Progressive DVD-Video, MPEG4.10 (H.264), WMV9/SMPTE 421M (VC-1) playback

- Interlaced or progressive YPbPr or RGB video outputs

- NTSC/PAL composite and S-video outputs

- 5.1-channel and S/PDIF audio outputs

- I<sup>2</sup>C bus master function for controlling other chips

- A MIPS CPU for operating system, middleware and applications

Figure 1-2 Application example - networked DVD player

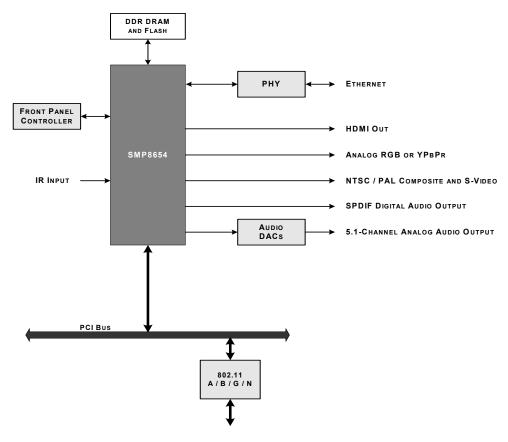

# 1.4.2 Digital Media Adapter or IPTV Set-top Box

The Digital Media Adapter or IPTV Set-top Box application requires very little external logic since the SMP8654 provides most of the features including:

- Decoding of MPEG-1, MPEG-2, MPEG-4.10 (H.264) and WMV9/SMPTE 421M (VC-1) content

- 2D graphics, OSD and deinterlacing

- Interlaced or progressive YPbPr or RGB video outputs

- NTSC/PAL composite and S-video outputs

- 5.1-channel and S/PDIF audio outputs

- A MIPS CPU for operating system, middleware and applications

Figure 1-3 Application example - digital media adapter or IPTV set-top box

2

# **Host CPU Block**

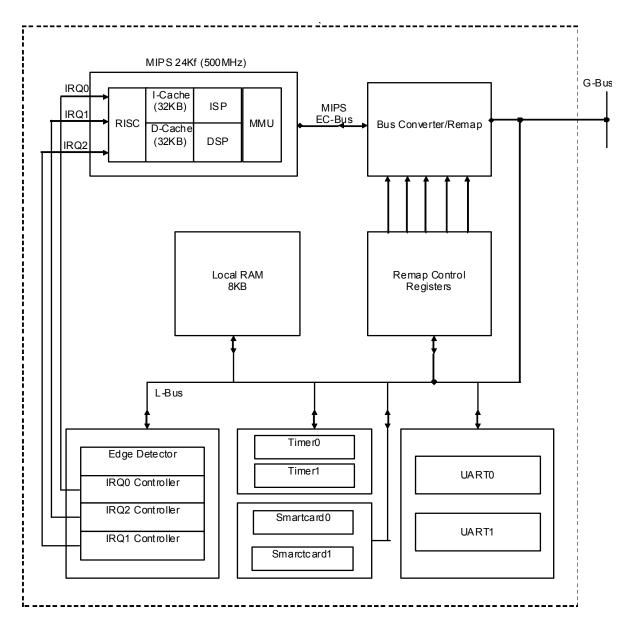

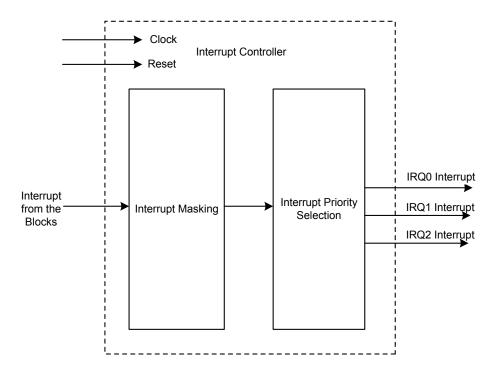

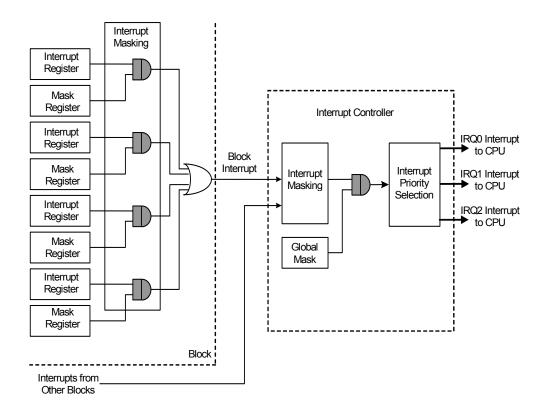

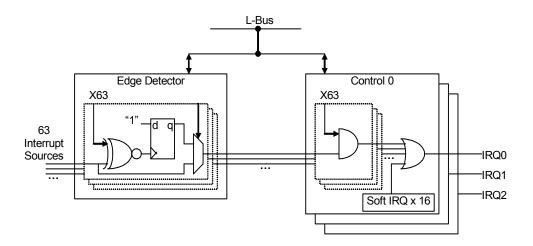

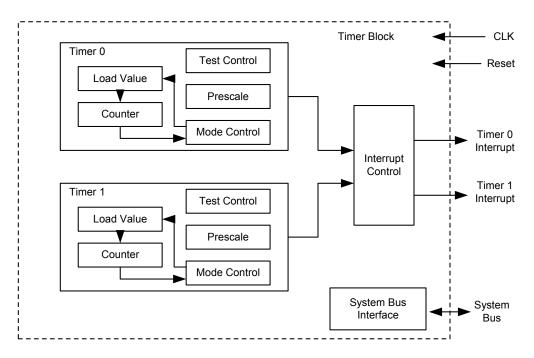

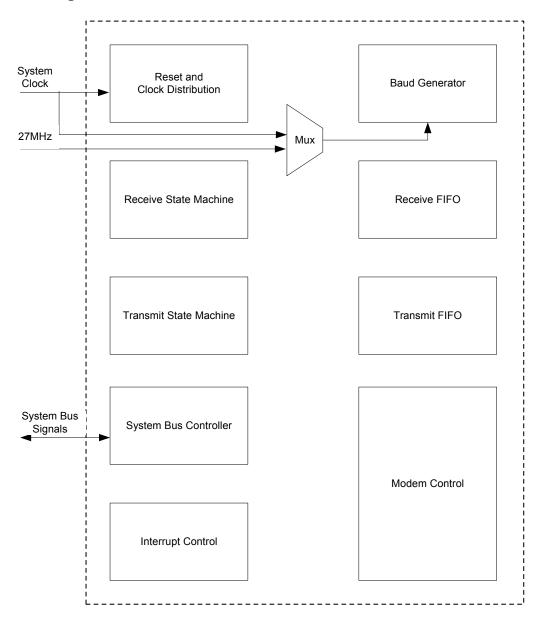

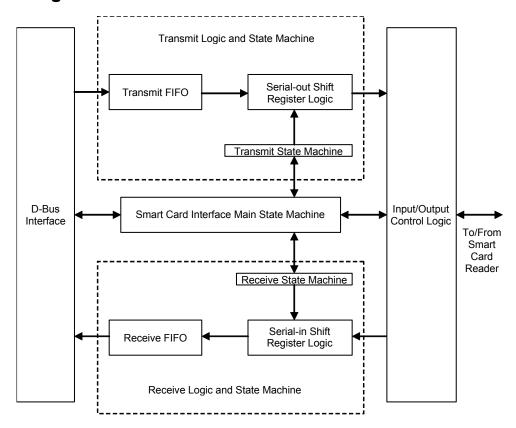

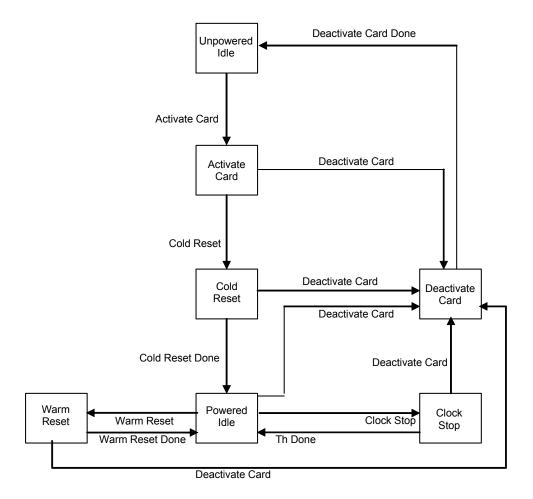

# 2.1 Block Diagram of Host CPU Block

Figure 2-1 Block diagram of host CPU block

### 2.2 Introduction

The host CPU block of the SMP8654 contains a 500MHz MIPS 24Kf + FPU (Floating Point Unit) with its instruction and data cache to support the embedded operating system, middleware and applications required for the consumer products. Supported operating systems include Linux and WinCE. Software for the CPU is loaded from an external flash using a secure boot loader.

The host CPU block contains the following additional resources:

- 32KB program and 32KB data caches

- 3 interrupt controllers

- Edge detection logic

- 2 programmable timers

- 2 Universal Asynchronous Receiver/Transmitter (UARTs)

- 2 ISO-7816 'Smartcard' controllers

The CPU accesses the G-Bus as a master. A bridge allows the CPU to access all the G-Bus mapped local resources through the L-Bus.

Other components of the host CPU block reside on a local bus and can be accessed by either the RISC or the other G-Bus master. Both the bridges in the host CPU block perform a bus protocol adaptation and a configurable address translation (remap). The host CPU block connects to the rest of the chip via the G-Bus.

Table 2-1 Remap registers

| Address <sup>1</sup> | Register Name | R/W/A <sup>2</sup> | Description          |

|----------------------|---------------|--------------------|----------------------|

| +F000                | CPU_REMAP0    | R/W                | CPU Remap 0 Register |

| +F004                | CPU_REMAP1    | R/W                | CPU Remap 1 Register |

| +F008                | CPU_REMAP2    | R/W                | CPU Remap 2 Register |

| +F00C                | CPU_REMAP3    | R/W                | CPU Remap 3 Register |

| +F010                | CPU_REMAP4    | R/W                | CPU Remap 4 Register |

| +F014                | CPU_REMAP5    | R/W                | CPU Remap 5 Register |

| +F018                | CPU_REMAP6    | R/W                | CPU Remap 6 Register |

| +F01C                | CPU_REMAP7    | R/W                | CPU Remap 7 Register |

<sup>1.</sup> G-Bus byte address relative to the host CPU block base (0x60000).

<sup>2.</sup> Read/write/auto update.

# **Central Processor Unit (CPU)**

### 2.3 Introduction

The MIPS32® 24Kf<sup>TM</sup> core (~720 conforming DMIPS at 500MHz) from MIPS Technologies is a high-performance, low-power, 32-bit MIPS RISC core designed for efficient embedded system-on-silicon applications. It implements the MIPS32 Release 2 Architecture in an 8-stage pipeline, and includes support for the MIPS16e<sup>TM</sup> application specific extension and the 32-bit privileged resource architecture. This standard architecture allows support by a wide range of industry standard tools and development systems.

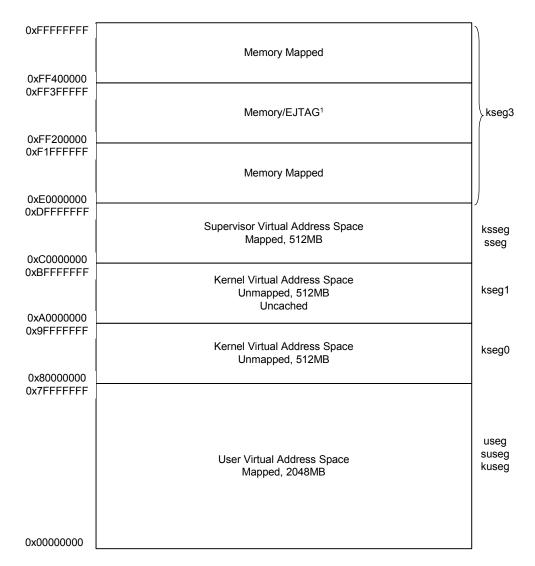

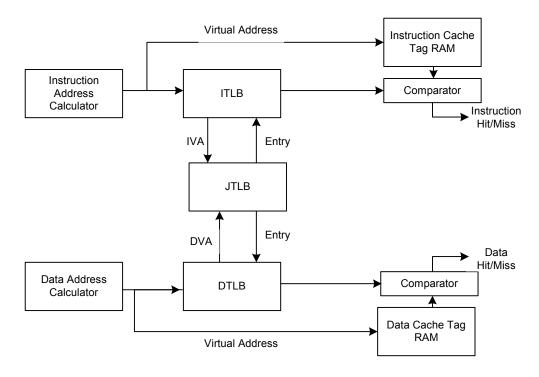

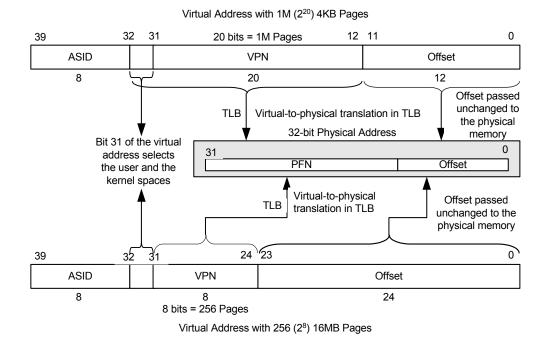

To maintain high pipeline utilization, dynamic branch prediction is included in the form of a Branch History Table and a Return Prediction Stack. The Memory Management Unit (MMU) contains 4-entry instruction and 8-entry data Translation Lookaside Buffers (ITLB/DTLB) and a configurable 32 dual-entry joint TLB (JTLB).

The 24Kf core also features an IEEE 754 compliant Floating Point Unit (FPU). The FPU supports both single and double precision instructions.

The core includes a high performance Multiply/Divide Unit (MDU). The MDU is fully pipelined to support a single cycle repeat rate for 32x32 MAC instructions, which enables multiply-intensive algorithms to be performed efficiently.

Instruction and data level-one caches are organized as 4-way set associative. Data cache misses are non-blocking and up to 4 may be outstanding. Two instruction cache misses can be outstanding. Both caches are virtually indexed and physically tagged to allow them to be accessed in the same cycle that the address is translated.

### 2.4 Features

- 8-stage pipeline

- 32-bit address paths

- 64-bit data paths to caches and system buses

- MIPS32-Compatible Instruction Set

- Multiply-Accumulate and Multiply-Subtract Instructions (MADD, MADDU, MSUB, MSUBU)

- Targeted Multiply Instruction (MUL)

- Zero/One Detect Instructions (CLZ, CLO)

- Wait Instruction (WAIT)

- Conditional Move Instructions (MOVZ, MOVN)

- Prefetch Instruction (PREF)

- MIPS32 Enhanced Architecture (Release 2) Features

- Vectored interrupts and support for external interrupt controller

- Programmable exception vector base

- Atomic interrupt enable/disable

- Bit field manipulation instructions

- MIPS32 Privileged Resource Architecture

- Programmable Memory Management Unit

- 32 dual-entry JTLB with variable page sizes

- 4-entry ITLB

- 8-entry DTLB

- MIPS16e<sup>™</sup> Code Compression

- 16 bit encoding of 32 bit instructions to improve code density

- Special PC-relative instructions for efficient loading of addresses and constants

- SAVE & RESTORE macro instructions for setting up and tearing down stack frames within subroutines

- Improved support for handling 8 and 16 bit data types

#### Caches

- Separate 32 KB Instruction and Data caches

- 4-Way Set Associative

- Up to 8 outstanding load misses

- Write-back and write-through support

- 32-byte cache line size

- Virtually indexed, physically tagged

- Cache line locking support

- Non-blocking prefetches

- Multiply/Divide Unit

- Maximum issue rate of one 32x32 multiply per clock

- 5 cycle multiply latency

- Early-in iterative divide. Minimum 12 and maximum 38 clock latency (dividend (rs) sign extension-dependent)

- Floating Point Unit (FPU)

- IEEE-754 compliant Floating Point Unit

- Compliant to MIPS 64b FPU standards

- Supports single and double precision data types

- Run at 2:1 core/FPU clock ratio (250MHz at 500MHz CPU clock)

- Power Control

- Power-down mode (triggered by WAIT instruction)

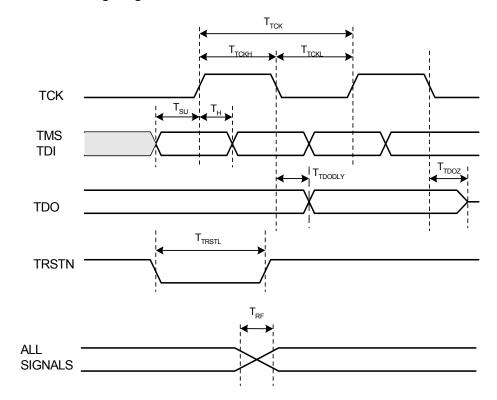

- EJTAG Debug

- Support for single stepping

- Virtual instruction and data address/value breakpoints

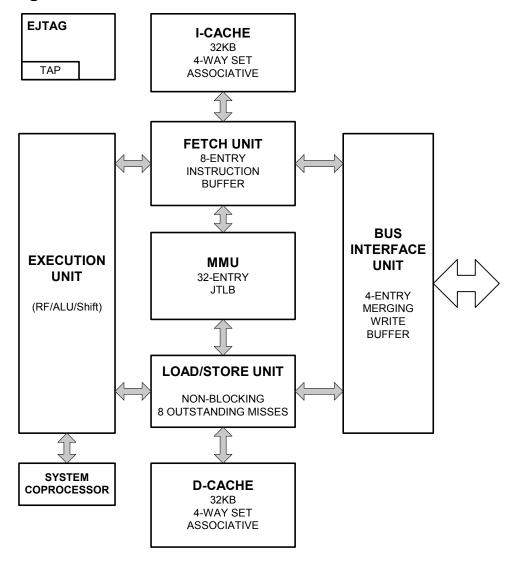

# 2.5 Block Diagram

Figure 2-2 24Kf core block diagram

# 2.6 Functional Description

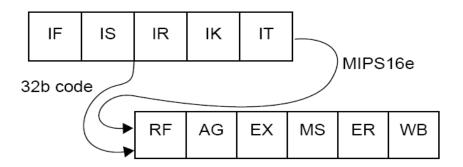

## 2.6.1 Pipeline Flow

The 24Kf core implements an 8-stage pipeline. Three extra fetch stages are conditionally added when executing MIPS16e instructions. This pipeline allows the processor to achieve a high frequency while maintaining reasonable area and power numbers.

The 24Kf core pipeline consists of the following stages:

- IF Instruction Fetch First

- IS Instruction Fetch Second

- IR Instruction Recode (MIPS16e only)

- IK Instruction Kill (MIPS16e only)

- IT Instruction Fetch Third (MIPS16e only)

- RF Register File access

- AG Address Generation

- EX Execute

- MS Memory Second

- ER Exception Resolution

- WB WriteBack

The 24Kf core implements a bypass mechanism that allows the result of an operation to be forwarded directly to the instruction that needs it without having to write the result to the register and then read it back.

Figure 2-3 24Kf™ core pipeline

## 2.6.2 24Kf™ Core Logic Blocks

The 24Kf core consists of the following logic blocks. These logic blocks are defined in the following subsections:

- Fetch Unit

- Execution Unit

- Floating Point Unit

- MIPS16e recode

- System Control Coprocessor (CP0)

- Memory Management Unit (MMU)

- Instruction/Data Cache

- Cache Controllers

- Power Management

- Enhanced JTAG (EJTAG) breakpoints

#### 2.6.2.1 Fetch Unit

The 24Kf core fetch unit is responsible for fetching instructions and providing them to the rest of the pipeline, as well as handling control transfer instructions (branches, jumps, etc.). It calculates the address for each instruction fetch and contains an instruction buffer that decouples the fetching of instructions from their execution.

The fetch unit contains two structures for the dynamic prediction of control transfer instructions. A 512-entry Branch History Table (BHT) is used to predict the direction of branch instructions. It uses a bimodal algorithm with two bits of history information per entry. Also, a 4-entry Return Prediction Stack (RPS) is a simple structure to hold the return address from the most recent subroutine calls. The link address is pushed onto the stack whenever a JAL, JALR, or BGEZAL instruction is seen. Then that address is popped when a JR instruction occurs.

#### 2.6.2.2 Execution Unit

The 24Kf core execution unit implements a load/store architecture with single-cycle ALU operations (logical, shift, add, subtract) and an autonomous multiply/divide unit. The 24Kf core contains thirty-two 32-bit general-purpose registers used for integer operations and address calculation. The register file consists of two read ports and one write port and is fully bypassed to minimize operation latency in the pipeline.

The execution unit includes:

- 32-bit adder used for calculating the data address

- Logic for verifying branch prediction

- Load aligner

- Bypass multiplexers used to avoid stalls when executing instructions streams where data producing instructions are followed closely by consumers of their results

- Leading Zero/One detect unit for implementing the CLZ and CLO instructions

- Arithmetic Logic Unit (ALU) for performing bitwise logical operations

- Shifter & Store Aligner

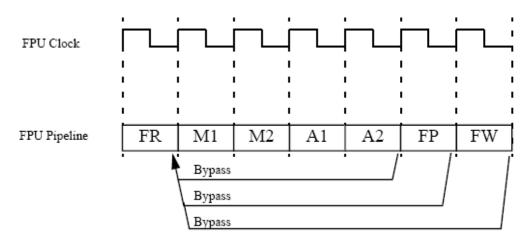

### 2.6.2.3 Floating Point Unit (FPU)/Coprocessor 1

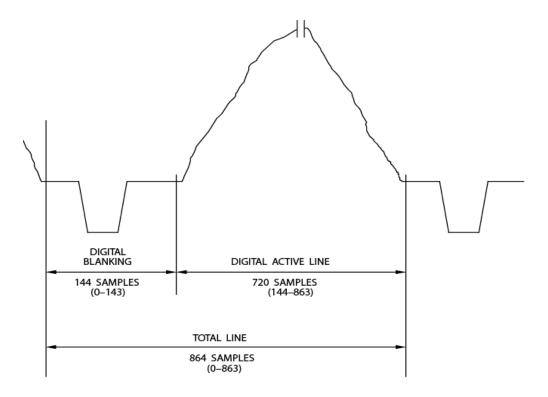

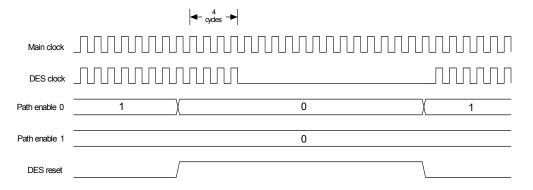

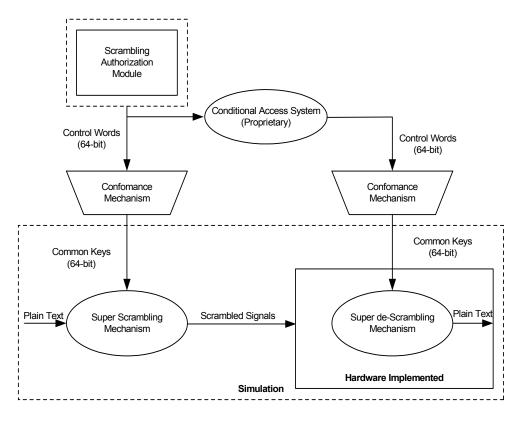

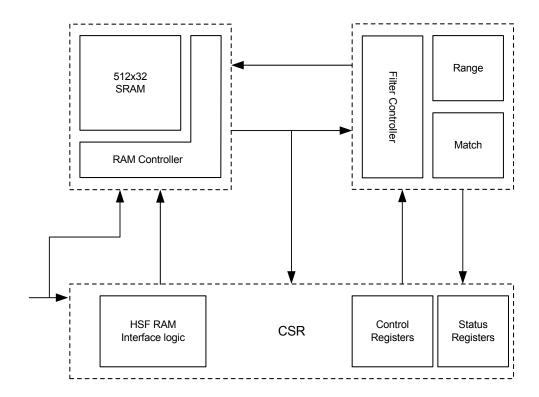

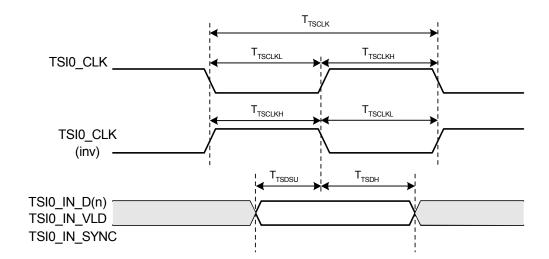

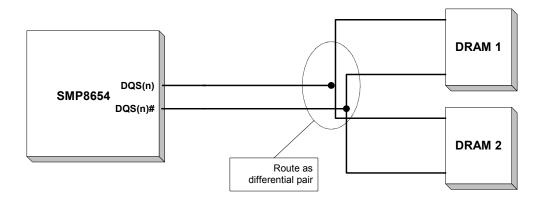

The 24Kf core Floating Point Unit (FPU) implements the MIPS64 ISA (Instruction Set Architecture) for floating-point computation. The implementation supports the ANSI/ IEEE Standard 754 (IEEE Standard for Binary Floating-Point Arithmetic) for single and double precision data formats. The FPU contains thirty-two 64-bit floating-point registers used for floating point operations.