### **USB PORT TRANSIENT SUPPRESSORS**

#### FEATURES

- Qualified for Automotive Applications

- Design to Protect Submicron 3-V or 5-V Circuits from Noise Transients

- Port ESD Protection Capability Exceeds:

15-kV Human Body Model

- 2-kV Machine Model

- Available in a WCSP Chip-Scale Package

- Stand-Off Voltage ... 6 V Min

- Low Current Leakage . . . 1  $\mu$ A Max at 6 V

- Low Capacitance . . . 35 pF Typ

### APPLICATIONS

• USB 1.1 Host, Hub, or Peripheral Ports

### DESCRIPTION

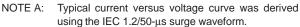

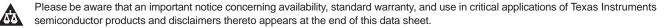

The SN65220 is a single transient voltage suppressor designed to provide electrical noise transient protection to universal serial bus (USB) 1.1 ports. Note that the input capacitance of the device makes it unsuitable for high-speed USB 2.0 applications.

Any cabled I/O can be subjected to electrical noise transients from various sources. These noise transients can cause damage to the USB transceiver and/or the USB ASIC if they are of sufficient magnitude and duration.

USB ports are typically implemented in 3-V or 5-V digital CMOS with limited ESD protection. The SN65220 can significantly increase the port ESD protection level and reduce the risk of damage to the circuits of the USB port. The IEC1000-4-2 ESD performance of the SN65220 is measured at the system level. Therefore, system design impacts the results of these tests. A high compliance level may be attained with proper board design and layout.

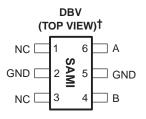

NC – No internal connection When read horizontally, pin 1 is the bottom left pin.

NOTE: All GND terminals should be connected to ground.

### SN65220-Q1

#### SGLS297A - FEBRUARY 2005 - REVISED JUNE 2008

This integrated circuit can be damaged by ESD. Texas Instruments recommends that all integrated circuits be handled with appropriate precautions. Failure to observe proper handling and installation procedures can cause damage.

#### IEC1000-4-2 COMPLIANCE LEVEL

| IEC1000-4-2 | MAXIMUM TEST VOLTAGE         |                          |  |  |  |  |  |

|-------------|------------------------------|--------------------------|--|--|--|--|--|

| COMPLIANCE  | CONTACT<br>DISCHARGE<br>(kV) | AIR<br>DISCHARGE<br>(kV) |  |  |  |  |  |

| 1           | 2                            | 2                        |  |  |  |  |  |

| 2           | 4                            | 4                        |  |  |  |  |  |

| 3           | 6                            | 8                        |  |  |  |  |  |

| 4           | 8                            | 15                       |  |  |  |  |  |

#### PACKAGE/ORDERING INFORMATION<sup>†</sup>

| PRODUCT | SUPRESSORS | т <sub>А</sub> | PACKAGE <sup>‡</sup> | PACKAGE<br>DESIGNATOR | MARKED<br>AS | ORDER NUMBER                  |

|---------|------------|----------------|----------------------|-----------------------|--------------|-------------------------------|

| SN65220 | 1          | –40°C to 85°C  | SOT23-6              | DBV                   | SAMI         | SN65220IDBVRQ1<br>(Mini Reel) |

For the most current package and ordering information, see the Package Option Addendum at the end of this document, or see the TI web site at http://www.ti.com.

<sup>‡</sup> Package drawings, thermal data, and symbolization are available at http://www.ti.com/packaging.

#### **ABSOLUTE MAXIMUM RATINGS**

over operating free-air temperature range unless otherwise noted<sup>(1)</sup>

|                                              | UNIT                         |

|----------------------------------------------|------------------------------|

| Continuous power dissipation                 | See Dissipation Rating Table |

| Electrostatic discharge                      | 15 kV(2), 2 kV(3)            |

| Peak power dissipation, PD(peak)             | 60 W                         |

| Peak forward surge current, I <sub>FSM</sub> | 3 A                          |

| Peak reverse surge current, IRSM             | –9 A                         |

| Storage temperature range, T <sub>Stg</sub>  | -65°C to 150°C               |

(1) Stresses above these ratings may cause permanent damage. Exposure to absolute maximum conditions for extended periods may degrade device reliability. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those specified is not implied.

(2) Human Body Model – Tested in accordance with JEDEC Standard 22, Test Method A114–A.

(3) Charged Device Model – Tested in accordance with JEDEC Standard 22, Test Method C101.

#### DISSIPATION RATING TABLE

| PACKAGE | $T_A \le 25^{\circ}C$ | DERATING FACTOR                          | T <sub>A</sub> = 70°C | T <sub>A</sub> = 85°C |

|---------|-----------------------|------------------------------------------|-----------------------|-----------------------|

|         | POWER RATING          | ABOVE T <sub>A</sub> = 25°C <sup>‡</sup> | POWER RATING          | POWER RATING          |

| DBV     | 385 mW                | 3.1 mW/°C                                | 246 mW                | 200 mW                |

<sup>‡</sup>This is the inverse of the junction-to-ambient thermal resistance when board-mounted and with no air flow.

#### recommended operating conditions

|                                                | MIN | MAX | UNIT |

|------------------------------------------------|-----|-----|------|

| Operating free-air temperature, T <sub>A</sub> | -40 | 85  | °C   |

### electrical characteristics over recommended operating conditions (unless otherwise noted)

|                  | PARAMETER                   | TEST CONDITIONS                          | MIN | TYP | MAX | UNIT |

|------------------|-----------------------------|------------------------------------------|-----|-----|-----|------|

| l <sub>lkg</sub> | Leakage current             | VI = 6 V at A, B, C, or D terminals      |     |     | 1   | μA   |

| V(BR)            | Breakdown voltage           | VI = 1 mA at A, B, C, or D terminals     | 6.5 | 7   | 8   | V    |

| CIN              | Input capacitance to ground | V <sub>I</sub> = 0.4 sin (4E6πt) + 0.5 V |     | 35  |     | pF   |

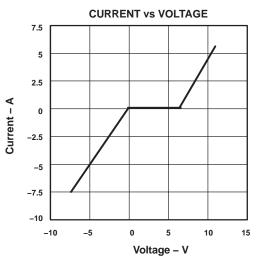

### **APPLICATION INFORMATION**

# PACKAGE MATERIALS INFORMATION

www.ti.com

Texas Instruments

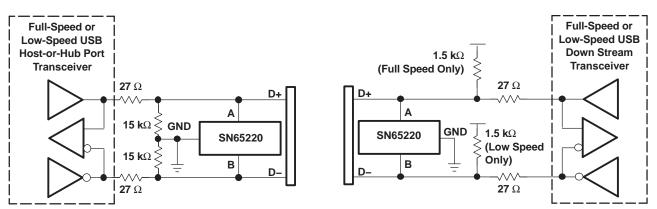

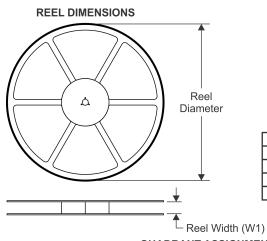

### TAPE AND REEL INFORMATION

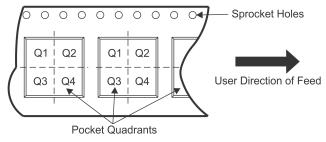

### QUADRANT ASSIGNMENTS FOR PIN 1 ORIENTATION IN TAPE

| *All dimensions are nominal |  |

|-----------------------------|--|

|                             |  |

| Device         | Package<br>Type | Package<br>Drawing |   | SPQ  | Reel<br>Diameter<br>(mm) | Reel<br>Width<br>W1 (mm) | A0<br>(mm) | B0<br>(mm) | K0<br>(mm) | P1<br>(mm) | W<br>(mm) | Pin1<br>Quadrant |

|----------------|-----------------|--------------------|---|------|--------------------------|--------------------------|------------|------------|------------|------------|-----------|------------------|

| SN65220IDBVRQ1 | SOT-23          | DBV                | 6 | 3000 | 180.0                    | 9.0                      | 3.15       | 3.2        | 1.4        | 4.0        | 8.0       | Q3               |

TEXAS INSTRUMENTS

www.ti.com

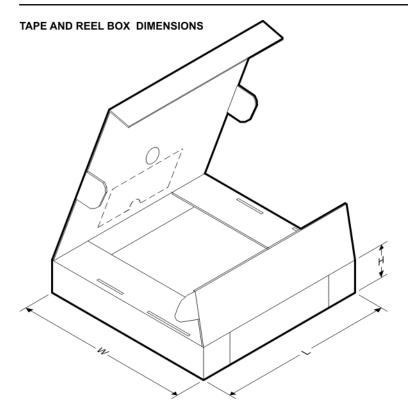

## PACKAGE MATERIALS INFORMATION

1-Nov-2019

\*All dimensions are nominal

| Device         | Package Type | Package Drawing | Pins | SPQ  | Length (mm) | Width (mm) | Height (mm) |

|----------------|--------------|-----------------|------|------|-------------|------------|-------------|

| SN65220IDBVRQ1 | SOT-23       | DBV             | 6    | 3000 | 182.0       | 182.0      | 20.0        |

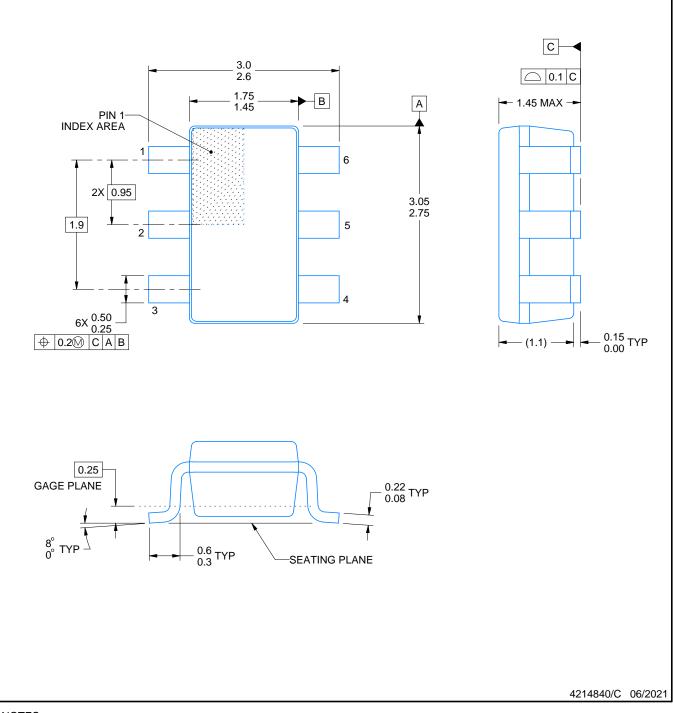

# **DBV0006A**

# **PACKAGE OUTLINE**

SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES:

- 1. All linear dimensions are in millimeters. Any dimensions in parenthesis are for reference only. Dimensioning and tolerancing per ASME Y14.5M.2. This drawing is subject to change without notice.3. Body dimensions do not include mold flash or protrusion. Mold flash and protrusion shall not exceed 0.25 per side.

- 4. Leads 1,2,3 may be wider than leads 4,5,6 for package orientation. 5. Refernce JEDEC MO-178.

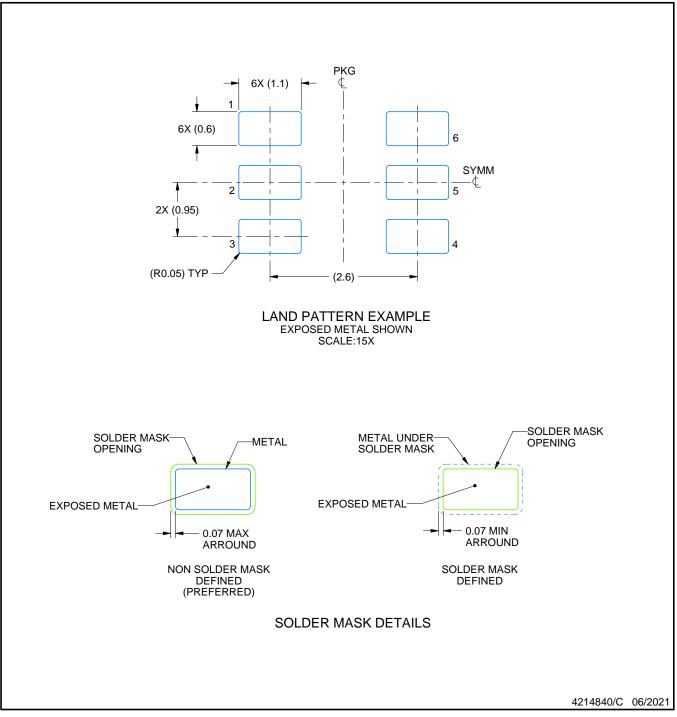

# **DBV0006A**

# **EXAMPLE BOARD LAYOUT**

### SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

6. Publication IPC-7351 may have alternate designs.

7. Solder mask tolerances between and around signal pads can vary based on board fabrication site.

# **DBV0006A**

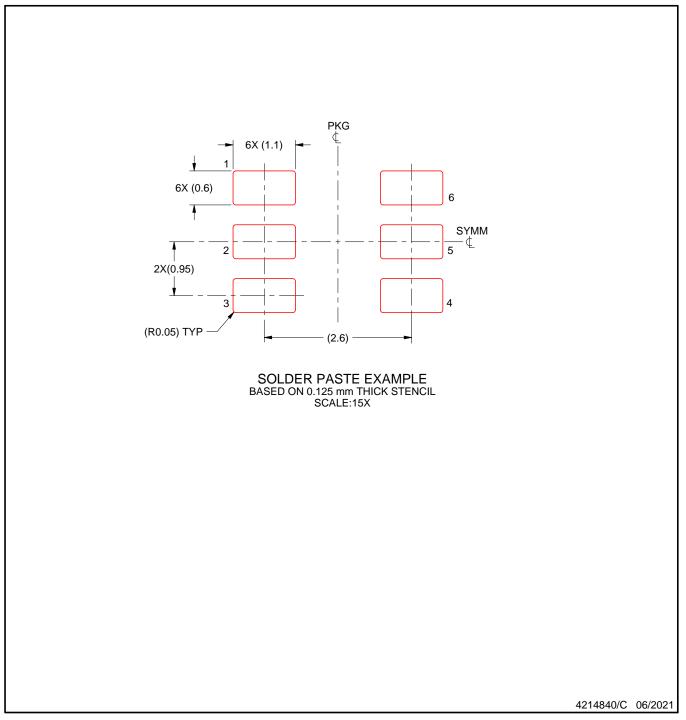

# **EXAMPLE STENCIL DESIGN**

### SOT-23 - 1.45 mm max height

SMALL OUTLINE TRANSISTOR

NOTES: (continued)

8. Laser cutting apertures with trapezoidal walls and rounded corners may offer better paste release. IPC-7525 may have alternate design recommendations.

9. Board assembly site may have different recommendations for stencil design.

### IMPORTANT NOTICE AND DISCLAIMER

TI PROVIDES TECHNICAL AND RELIABILITY DATA (INCLUDING DATASHEETS), DESIGN RESOURCES (INCLUDING REFERENCE DESIGNS), APPLICATION OR OTHER DESIGN ADVICE, WEB TOOLS, SAFETY INFORMATION, AND OTHER RESOURCES "AS IS" AND WITH ALL FAULTS, AND DISCLAIMS ALL WARRANTIES, EXPRESS AND IMPLIED, INCLUDING WITHOUT LIMITATION ANY IMPLIED WARRANTIES OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE OR NON-INFRINGEMENT OF THIRD PARTY INTELLECTUAL PROPERTY RIGHTS.

These resources are intended for skilled developers designing with TI products. You are solely responsible for (1) selecting the appropriate TI products for your application, (2) designing, validating and testing your application, and (3) ensuring your application meets applicable standards, and any other safety, security, or other requirements. These resources are subject to change without notice. TI grants you permission to use these resources only for development of an application that uses the TI products described in the resource. Other reproduction and display of these resources is prohibited. No license is granted to any other TI intellectual property right or to any third party intellectual property right. TI disclaims responsibility for, and you will fully indemnify TI and its representatives against, any claims, damages, costs, losses, and liabilities arising out of your use of these resources.

TI's products are provided subject to TI's Terms of Sale (https://www.ti.com/legal/termsofsale.html) or other applicable terms available either on ti.com or provided in conjunction with such TI products. TI's provision of these resources does not expand or otherwise alter TI's applicable warranties or warranty disclaimers for TI products.

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2021, Texas Instruments Incorporated