SLLS186B - OCTOBER 1994 - REVISED JULY 1997

- Provides Differential SCSI From Single-Ended Controller When Used With the SN75LBC970A Control Transceiver

- Designed to Operate at Fast-SCSI Speed of Ten Million Data Transfers per Second

- Meets or Exceeds the Requirements of EIA Standard RS-485 and ISO-8482 Standards

- Packaged in Shrink Small-Outline Package With 25-Mil Terminal Pitch

- Low Disabled-Supply Current 23 mA Typ

- Thermal Shutdown Protection

- Positive- and Negative-Current Limiting

- Power-Up/-Down Glitch Protection

#### description

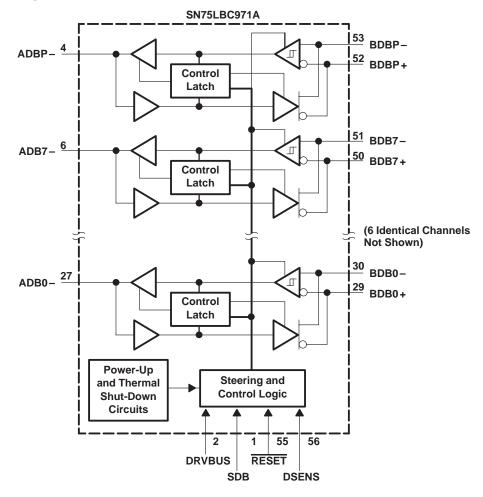

The SN75LBC971A SCSI differential converter-data is an adaptation of the industry's first 9-channel RS-485 transceiver, the SN75LBC976. When used in conjunction with its companion control transceiver, the SN75LBC970A, the resulting chip set provides the superior electrical performance of differential SCSI from a single-ended SCSI bus or controller. A 16-bit SCSI bus can be implemented with just three devices (two data and one control) in the space efficient, 56-pin, shrink small-outline package (SSOP) and a few external components. An 8-bit SCSI bus requires only one data and one control transceiver.

In a typical differential SCSI node, the SCSI controller provides an enable for each external RS-485 transceiver channel. This could require as many as 27 extra terminals for a 16-bit differential bus controller or relegate a 16-bit, single-ended controller to only an 8-bit differential bus. Using the standard nine SCSI

| DL PACKAGE<br>(TOP VIEW)                                                                                                     |                                                                                                 |                                                                                              |                                                                                                                                                                                    |  |  |  |

|------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| SDB [<br>DRVBUS [<br>GND [<br>ADBP- [<br>NC [<br>ADB7- [                                                                     | 1<br>2<br>3<br>4<br>5<br>6<br>7                                                                 | 56<br>55<br>54<br>53<br>52<br>51                                                             | ] DSENS<br>] RESET<br>] GND<br>] BDBP-<br>] BDBP+<br>] BDB7-                                                                                                                       |  |  |  |

| NC  <br>ADB6- [<br>ADB5- [<br>ADB5- [<br>Vcc [<br>GND [<br>GND [<br>GND [<br>GND [<br>GND [<br>ADB3- [<br>ADB3- [<br>ADB3- [ | 7<br>8<br>9<br>10<br>11<br>12<br>13<br>14<br>15<br>16<br>17<br>18<br>19<br>20<br>21<br>22<br>22 | 50<br>49<br>48<br>47<br>46<br>45<br>44<br>43<br>42<br>41<br>40<br>39<br>38<br>37<br>36<br>35 | BDB7+<br>  BDB6-<br>  BDB6+<br>  BDB5-<br>  BDB5+<br>  V <sub>CC</sub><br>  GND<br>  GND<br>  GND<br>  GND<br>  GND<br>  GND<br>  V <sub>CC</sub><br>  BDB4-<br>  BDB3-<br>  BDB3+ |  |  |  |

| ADB2- L<br>NC [<br>ADB1- [<br>NC [<br>ADB0- [<br>NC [                                                                        | 23<br>24<br>25<br>26<br>27<br>28                                                                | 34<br>33<br>32<br>31<br>30<br>29                                                             | BDB2-<br>  BDB2+<br>  BDB1-<br>  BDB1+<br>  BDB0-<br>  BDB0+                                                                                                                       |  |  |  |

Pins 13 - 17 and 40 - 44 are connected together to the package lead frame and to signal ground. NC - No internal connection

control signals, the SN75LBC970A control transceiver decodes the state of the bus and enables the SN75LBC971A data transceiver to transmit the single-ended SCSI input signals (A side) differentially to the cable or receive the differential cable signals (B side) and drive the single-ended outputs to the controller.

A reset function, which disables all outputs and clears internal latches, can be accomplished from two external inputs and two internally-generated signals. RESET (reset) and DSENS (differential sense) are available to external circuits for a bus reset or to disable all outputs should a single-ended cable be inadvertently connected to a differential connector. Internally-generated power-up and thermal-shutdown signals have the same affect when the supply voltage is below approximately 3.5 V or the junction temperature exceeds 175°C.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

#### description (continued)

The SCSI, differential, converter-data chip operates in two modes depending on the state of the DRVBUS input. With DRVBUS low, a bidirectional latch circuit sets the direction of data transfer. Each data bit has its own latch, and each bit's direction is independent of all other bits. When neither the single-ended nor the differential sides are asserted, the latch disables both A- and B-side output drivers. When the input to either side is asserted, the latch enables the opposite side's driver and sets data flow from the asserted input to the opposite side of the device. When the input deasserts, the latch maintains the direction until the receiver on the enabled driver detects a deassertion. The latch then returns to the initial state. No parity checking is done by this device; the parity signal passes through the device like other data signals do.

When DRVBUS is high, direction is determined by the SDB signal. However, a change in SDB does not always immediately change the direction. When DRVBUS first asserts, the direction indicated by SDB is latched and takes effect immediately. When SDB changes while DRVBUS is high, the drivers that were on immediately turn off. However, the other driver set does not turn on until the receivers sense a deasserted state on all nine data lines. This is done to prevent the active drivers from turning on until all other drivers are off and the terminators pull the lines to a deasserted state.

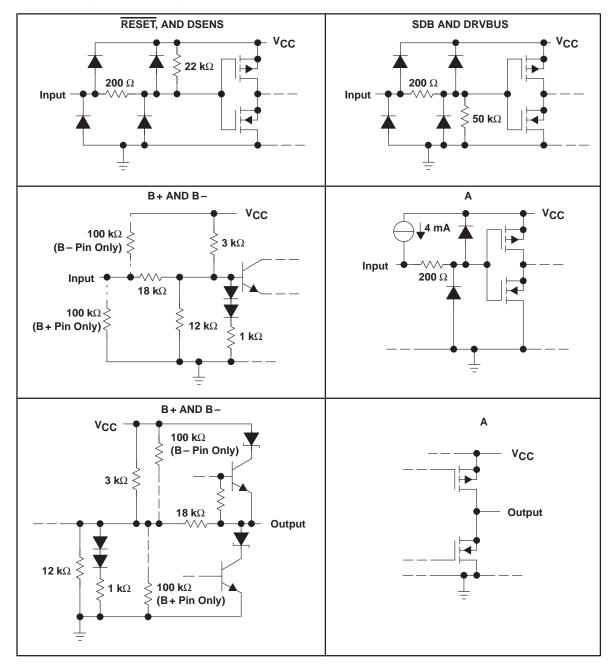

The single-ended SCSI bus interface consists of CMOS, bidirectional inputs and outputs. The drivers are rated to  $\pm 16$  mA of output current. The receiver inputs are pulled high with approximately 4 mA to eliminate the need for external pullup resistors for the open-drain outputs of most single-ended SCSI controllers. The single-ended side of the device is not intended to drive the SCSI bus directly.

The differential SCSI bus interface consists of bipolar, bidirectional inputs and outputs that meet or exceed the requirements of EIA-485 and ISO 8482-1982/TIA TR30.2 referenced by American National Standard of Information Systems (ANSI) X3.131-1994 Small Computer System Interface-2 (SCSI-2).

The SN75LBC971A is characterized for operation over the temperature range of 0°C to 70°C.

| TERMIN                                  | NAL                                   | 1/0                                                        | DESCRIPTION                                                                                                                                                                                                                   |  |  |  |  |

|-----------------------------------------|---------------------------------------|------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

| NAME                                    | NO.                                   | 1/0                                                        | DESCRIPTION                                                                                                                                                                                                                   |  |  |  |  |

| ADBn-, where<br>n = {0,1,2,3,4,5,6,7,P} | 4, 6, 8, 10, 19,<br>21, 23, 25, 27    | I/O, Single-ended<br>SCSI voltage levels,<br>Strong pullup | Bidirectional I/O for data and parity bits to and from the single-ended SCSI controller. As outputs, these terminals can source or sink 16 mA. As inputs, they are pulled up with about 4-mA to eliminate external resistors. |  |  |  |  |

| BDBn+, where<br>n = {0,1,2,3,4,5,6,7,P} | 29, 31, 33, 35,<br>37, 46, 48, 50, 52 | I/O, RS-485,<br>Weak pulldown                              | Bidirectional I/O for data and parity to and from the differential SCSI bus.                                                                                                                                                  |  |  |  |  |

| BDBn–, where<br>n = {0,1,2,3,4,5,6,7,P} | 30, 32, 34, 36,<br>38,47, 49, 51, 53  | I/O, RS-485,<br>Weak pulldown                              | Bidirectional I/O for the complement of data and parity to and from the differential SCSI bus.                                                                                                                                |  |  |  |  |

| DRVBUS                                  | 2                                     | Input, TTL levels,<br>Weak pulldown                        | A high-level logic signal from the control transceiver enables either the single-ended or differential drivers as directed by SDB.                                                                                            |  |  |  |  |

| DSENS                                   | 56                                    | Input, TTL levels,<br>Weak pullup                          | A low-level input initializes the internal latches and disables all drivers.                                                                                                                                                  |  |  |  |  |

| RESET                                   | 55                                    | Input, TTL levels,<br>Weak pullup                          | A low-level input initializes the internal latches and disables all drivers.                                                                                                                                                  |  |  |  |  |

| SDB                                     | 1                                     | Input, TTL levels,<br>Weak pulldown                        | A high-level logic signal from the control transceiver sends data from the differential bus to the single-ended bus. A low-level signal reverses the flow.                                                                    |  |  |  |  |

### TERMINAL FUNCTION

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

### functional block diagram

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

#### schematics of inputs and outputs

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

#### absolute maximum ratings over operating free-air temperature range (unless otherwise noted)<sup>†</sup>

| Supply voltage range, V <sub>CC</sub> (see Note 1)   -0     Differential bus voltage range (B side)   -15     Single-ended bus voltage range (A side and control inputs)   -0     Continuous total power dissipation (see Note 2)   Internally Limited (see Dissipation Ra     Electrostatic discharge (see Note 3):   Class 1 A (all pins)     Class 1 B (all pins)   Class 2 A (B-side and GND)     Class 2 B (B-side and GND)   0     Storage temperature range, T <sub>A</sub> 0     Storage temperature range, T <sub>stg</sub> 65°C | 5 V to 15 V<br>0.3 V to 7 V<br>ating Table)<br>500 V<br>200 V<br>2 kV<br>200 V<br>°C to 70°C<br>C to 150°C |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------|

| Lead temperature 1,6 mm (1/16 inch) from case for 10 seconds                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                            |

<sup>†</sup> Stresses beyond those listed under "absolute maximum ratings" may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under "recommended operating conditions" is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. All voltage values are with respect to GND.

- 2. The maximum operating junction temperature is internally limited. Use the dissipation rating table to operate below this temperature.

- 3. This absolute maximum rating is tested in accordance with MIL-STD-883C, Method 3015.7.

#### **DISSIPATION RATING TABLE**

| PACKAGE | T <sub>A</sub> ≤ 25°C | DERATING FACTOR <sup>‡</sup> | T <sub>A</sub> = 70°C |  |

|---------|-----------------------|------------------------------|-----------------------|--|

|         | NER RATING            | ABOVE T <sub>A</sub> = 25°C  | POWER RATING          |  |

| DL      | 2500 mW               | 20 mW/°C                     | 1600 mW               |  |

<sup>‡</sup>This is the inverse of the traditional junction-to-case thermal resistance ( $R_{\theta JA}$ ).

#### recommended operating conditions

|                                                                          | MIN    | NOM | MAX | UNIT     |     |

|--------------------------------------------------------------------------|--------|-----|-----|----------|-----|

| Supply voltage, V <sub>CC</sub>                                          |        |     |     | 5.25     | V   |

| High-level input voltage, V <sub>IH</sub> A side and control             |        | 2   |     |          | V   |

| Low-level input voltage, VIL A side and control                          |        |     |     | 0.8      | V   |

| Voltage at any bus terminal (separately or common-mode), VO or VI B side |        |     |     | 12<br>-7 | V   |

|                                                                          | B side |     |     | -60      | ~^^ |

| High-level output current, IOH                                           | A side |     |     | -16      | mA  |

| Low-level output current, IOI                                            | B side |     |     | 60       | mA  |

|                                                                          | A side |     |     | 16       | ША  |

| Operating case temperature, T <sub>C</sub>                               |        | 0   |     | 125      | °C  |

| Operating free-air temperature, T <sub>A</sub>                           |        |     |     | 70       | °C  |

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

### electrical characteristics over recommended operating conditions (unless otherwise noted)

| PARAMETER        |                                                                             |                   | TEST CONDITIONS                                   |                              |      | TYP†               | MAX   | UNIT |  |

|------------------|-----------------------------------------------------------------------------|-------------------|---------------------------------------------------|------------------------------|------|--------------------|-------|------|--|

| VOD(H)           | Driver high-level differential output voltage See Figure 1                  |                   |                                                   | 1                            | 1.8  |                    | V     |      |  |

| VOD(L)           | Driver low-level differential                                               | output voltage    | See Figure 1                                      |                              | - 1  | - 2.2              |       | V    |  |

|                  |                                                                             | A side            | $V_{ID} = -200 \text{ mV},$ $I_{OH} = -16$        |                              | 2.5  | 4.2                |       |      |  |

| Vон              | High-level output voltage                                                   | B side            | I <sub>OH</sub> = -60 mA                          |                              |      | 3.4                |       | - v  |  |

|                  |                                                                             | A side            | V <sub>ID</sub> = 200 mV,                         | I <sub>OL</sub> = 16 mA      |      | 0.4                | 0.8   | v    |  |

| VOL              | Low-level output voltage                                                    | B side            | I <sub>OL</sub> = 60 mA                           |                              |      | 1.6                |       |      |  |

| V <sub>IT+</sub> | Receiver positive-going<br>differential input<br>threshold voltage          |                   | I <sub>OH</sub> = -16 mA                          | See Figure 2                 |      |                    | 0.2   | V    |  |

| V <sub>IT-</sub> | Receiver negative-going<br>differential input<br>threshold voltage          | B side            | I <sub>OL</sub> = 16 mA                           | See Figure 2                 | -0.2 |                    |       | V    |  |

| V <sub>hys</sub> | Receiver input hysteresis<br>voltage (V <sub>IT+</sub> – V <sub>IT</sub> –) |                   |                                                   |                              | 35   | 45                 |       | mV   |  |

| łı               | Bus input current                                                           | B or B            | VI = 12 V,<br>Other input at 0 V                  | $V_{CC} = 5 V$               |      | 0.6                | 1     | mA   |  |

|                  |                                                                             |                   |                                                   | $V_{CC} = 0$                 |      | 0.7                | 1     |      |  |

|                  |                                                                             |                   | $V_I = -7 V$ ,<br>Other input at 0 V              | $V_{CC} = 5 V$               |      | -0.5               | -0.8  | mA   |  |

|                  |                                                                             |                   |                                                   | $V_{CC} = 0$                 |      | -0.4               | -0.8  | IIIA |  |

|                  | High-level input current                                                    | A side            |                                                   |                              |      | -5                 | -8    | mA   |  |

| IН               |                                                                             | RESET, DSENS      | $V_{IH} = 2 V$                                    |                              |      | -70                | -100  | μA   |  |

|                  |                                                                             | SDB, DRVBUS       |                                                   |                              |      | 8                  | 20    | μΛ   |  |

|                  |                                                                             | A side            |                                                   |                              |      | -6                 | -8    | mA   |  |

| ۱L               | Low-level input current                                                     | RESET, DSENS      | V <sub>IL</sub> = 0.8 V                           |                              |      | -66                | -100  |      |  |

|                  |                                                                             | SDB, DRVBUS       |                                                   |                              |      |                    | ±1    | μA   |  |

| los              | Short-circuit output<br>current                                             | B side            | $V_{O} = 5 V and 0$                               |                              |      |                    | ±250  | mA   |  |

| 107              | High-impedance-state                                                        | A side            |                                                   |                              | See  | IIH and            | l IIL |      |  |

| IOZ              | output current                                                              | B side            |                                                   |                              |      | See I <sub>I</sub> |       |      |  |

|                  | Supply current                                                              | Disabled          | RESET at 0.8 V,                                   | Others open                  |      | 23                 | 33    | mA   |  |

| ICC              |                                                                             | B to A<br>Enabled | SDB and DRVBUS at 2 V,<br>All other inputs open,  | $V_{ID} = -1 V$ ,<br>No load |      |                    | 36    |      |  |

|                  |                                                                             | A to B<br>Enabled | SDB at 0.8 V,<br>All other inputs open,           | DRVBUS at 2 V,<br>No load    |      | 4                  | 9     |      |  |

| CO               | Output capacitance                                                          |                   | $V_{I} = 0.6 \sin(2\pi \times 10^{6} t) + 1.5 V,$ | BDBn to GND                  |      | 19                 | 21    | pF   |  |

| <u> </u>         | Devues disaination are a dis                                                | t                 | B to A,                                           | One channel                  |      | 100                |       | pF   |  |

| Cpd              | Power dissipation capacitance <sup>‡</sup>                                  |                   | A to B,                                           | One channel                  |      | 450                |       | pF   |  |

<sup>†</sup> All typical values are at V<sub>CC</sub> = 5 V, T<sub>A</sub> = 25°C.

<sup>‡</sup> C<sub>pd</sub> determines the no-load dynamic current consumption, I<sub>S</sub> = C<sub>pd</sub> × V<sub>CC</sub> × f + I<sub>CC</sub> (I<sub>CC</sub> depends on the output states and load circuits and is not necessarily the I<sub>CC</sub> specified in the Electrical Characteristics Table).

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

### switching characteristics over recommended of operating conditions (unless otherwise noted)

|                                                                                         | PARAMETER TEST CONDITIONS                                              |                        |                        | MIN                    | MAX                 | UNIT |      |    |

|-----------------------------------------------------------------------------------------|------------------------------------------------------------------------|------------------------|------------------------|------------------------|---------------------|------|------|----|

|                                                                                         |                                                                        |                        | See Figures 3 and 4    |                        |                     | 8.5  | 25.3 | ns |

| t <sub>d1</sub> , t <sub>d2</sub> Delay time, A to B, high<br>low- to high-level output | 0                                                                      | V <sub>CC</sub> = 5 V, | T <sub>A</sub> = 25°C, | See Figures 3 and 4    | 10                  | 18   | ns   |    |

|                                                                                         |                                                                        | put                    | V <sub>CC</sub> = 5 V, | $T_A = 70^{\circ}C$ ,  | See Figures 3 and 4 | 12.5 | 20.5 | ns |

|                                                                                         | Delay time, B to A, high- to low-level or<br>low- to high-level output |                        | See Figures 5 and 6    |                        |                     | 21.5 | 36.2 | ns |

| td3, td4                                                                                |                                                                        |                        | V <sub>CC</sub> = 5 V, | T <sub>A</sub> = 25°C, | See Figures 5 and 6 | 23.6 | 32.6 | ns |

|                                                                                         |                                                                        |                        | V <sub>CC</sub> = 5 V, | $T_A = 70^{\circ}C$ ,  | See Figures 5 and 6 | 24.4 | 33.4 | ns |

| <sup>t</sup> sk(lim)                                                                    | Skew limit                                                             | A to B <sup>†</sup>    | See Figures 5 and 6    |                        |                     |      | 8    | ns |

|                                                                                         |                                                                        | B to A                 | See Figures 5 and 6    |                        |                     |      | 9    | ns |

| <sup>t</sup> sk(p)                                                                      | Pulse skew <sup>‡</sup>                                                |                        |                        |                        |                     |      | 6    | ns |

| <sup>t</sup> dis1                                                                       | Disable time, A to B                                                   |                        | See Figures 3 and 4    |                        |                     |      | 200  | ns |

| <sup>t</sup> dis2                                                                       | Disable time, B to A                                                   |                        | See Figures 5 and 6    |                        |                     |      | 35   | ns |

| ten1                                                                                    | Enable time, A to B                                                    |                        | See Figures 3 and 4    |                        |                     |      | 65   | ns |

| t <sub>en2</sub>                                                                        | Enable time, B to A                                                    |                        | See Figures 5 and 6    |                        |                     |      | 65   | ns |

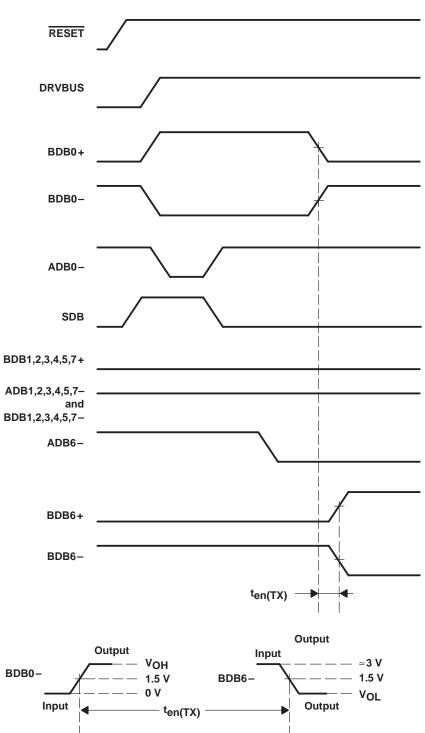

| ten(TX)                                                                                 | Enable time, receive-to-transmit                                       |                        | See Figure 7           |                        |                     |      | 142  | ns |

<sup>†</sup> This parameter is applicable at one V<sub>CC</sub> and operating temperature within the recommended operating conditions and to any two devices. <sup>‡</sup> Pulse skew is the difference between the high-to-low and low-to-high propagation delay times of any single channel.

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

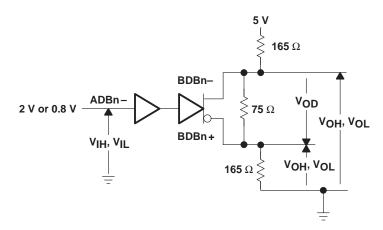

#### PARAMETER MEASUREMENT INFORMATION

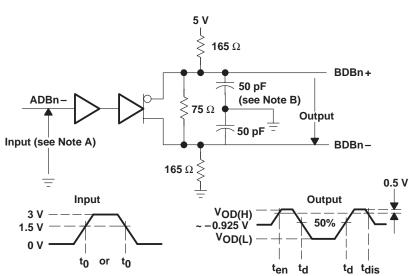

- NOTES: A. Resistance values are in ohms with a tolerance of  $\pm$  5%.

- B. All input voltage levels are held to within 0.01 V.

- C. The logical function is set with SDB at 0.8 V, DRVBUS at 3.5 V, and all others left open.

### Figure 1. Differential Driver $V_{\mbox{OD}}, V_{\mbox{OH}}, \mbox{and} \ V_{\mbox{OL}}$ Test Circuit

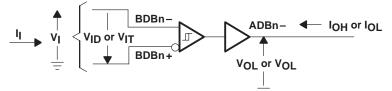

NOTES: A. Resistance values are in ohms with a tolerance of  $\pm$  5%.

- B. All input voltage levels are held to within 0.01 V.

- C. The logical function is set with SDB and DRVBUS at 3.5 V, and all others left open.

# Figure 2. Single-Ended Driver $V_{OH},\,V_{OL},\,V_{IT\,\text{+}},\,\text{and}\,\,V_{IT\,\text{-}}$ Test Circuit

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

#### PARAMETER MEASUREMENT INFORMATION

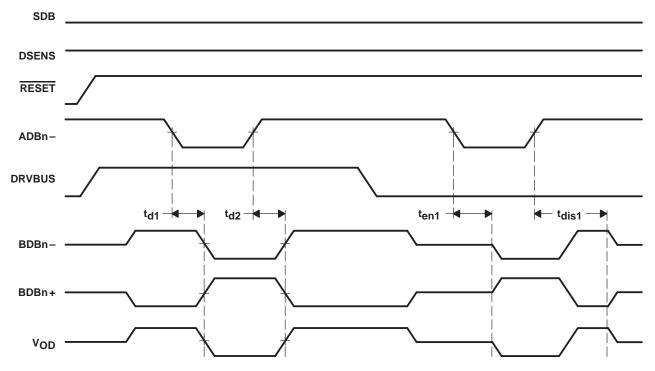

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 45% < duty cycle < 50%,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50~\Omega.$

- B. CL includes probe and jig capacitance.

- C. Resistance values are in ohms with a tolerance of  $\pm$  5%.

- D. All input voltage levels are held to within 0.01 V.

Figure 4. A to B Timing Waveforms

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

#### PARAMETER MEASUREMENT INFORMATION

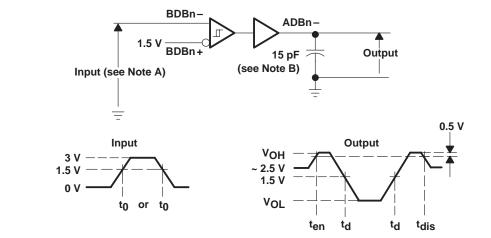

- NOTES: A. The input pulse is supplied by a generator having the following characteristics: PRR  $\leq$  1 MHz, 45% < duty cycle < 50%,  $t_f \leq$  6 ns,  $t_f \leq$  6 ns,  $Z_O = 50~\Omega$ .

- B. CL includes probe and jig capacitance.

- C. Resistance values are in ohms with a tolerance of  $\pm$  5%.

- D. All input voltage levels are held to within 0.01 V.

#### Figure 5. B to A Propagation Delay Time Test Circuit

#### Figure 6. B to A Timing Waveforms

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

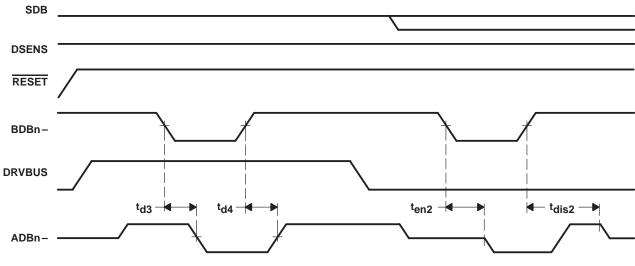

PARAMETER MEASUREMENT INFORMATION

Figure 7. Receive-to-Transmit (ten(TX)) Timing Waveforms

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

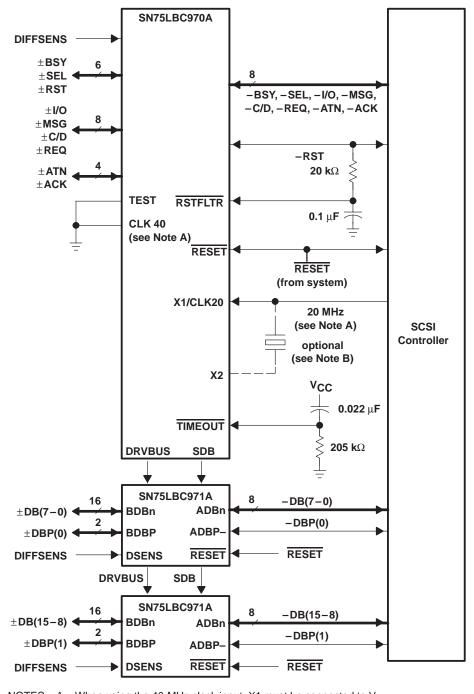

#### **APPLICATION INFORMATION**

NOTES: A. When using the 40-MHz clock input, X1 must be connected to V<sub>CC</sub>.

B. The oscillator cell of the SN75LBC970A is for a series-resonant crystal and requires approximately 10 pF (including fixture capacitance) from X1 and X2 to ground in order to function.

Figure 8. Typical Application of the SN75LBC970A and SN75LBC971A

SLLS186B - OCTOBER 1994 - REVISED JULY 1997

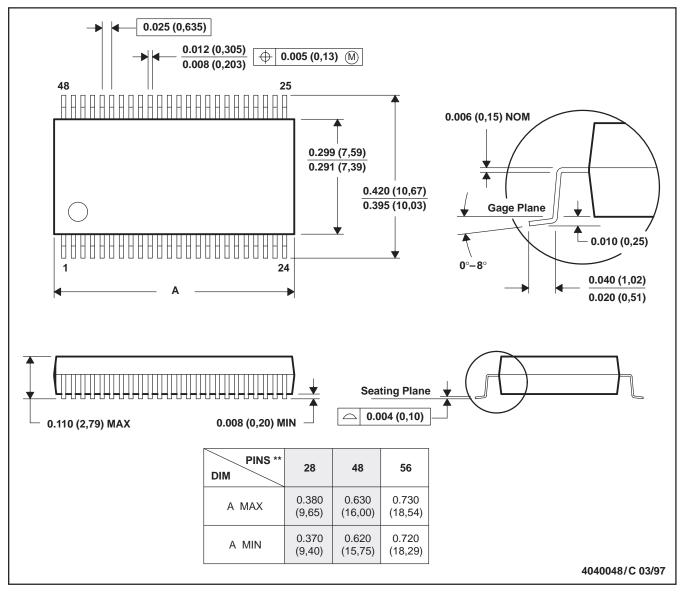

#### **MECHANICAL INFORMATION**

#### PLASTIC SMALL-OUTLINE PACKAGE

DL (R-PDSO-G\*\*) 48 PIN SHOWN

NOTES: E. All linear dimensions are in inches (millimeters).

- F. This drawing is subject to change without notice.

- G. Body dimensions do not include mold flash or protrusion not to exceed 0.006 (0,15).

- H. Falls within JEDEC MO-118

#### **IMPORTANT NOTICE**

Texas Instruments and its subsidiaries (TI) reserve the right to make changes to their products or to discontinue any product or service without notice, and advise customers to obtain the latest version of relevant information to verify, before placing orders, that information being relied on is current and complete. All products are sold subject to the terms and conditions of sale supplied at the time of order acknowledgement, including those pertaining to warranty, patent infringement, and limitation of liability.

TI warrants performance of its semiconductor products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are utilized to the extent TI deems necessary to support this warranty. Specific testing of all parameters of each device is not necessarily performed, except those mandated by government requirements.

CERTAIN APPLICATIONS USING SEMICONDUCTOR PRODUCTS MAY INVOLVE POTENTIAL RISKS OF DEATH, PERSONAL INJURY, OR SEVERE PROPERTY OR ENVIRONMENTAL DAMAGE ("CRITICAL APPLICATIONS"). TI SEMICONDUCTOR PRODUCTS ARE NOT DESIGNED, AUTHORIZED, OR WARRANTED TO BE SUITABLE FOR USE IN LIFE-SUPPORT DEVICES OR SYSTEMS OR OTHER CRITICAL APPLICATIONS. INCLUSION OF TI PRODUCTS IN SUCH APPLICATIONS IS UNDERSTOOD TO BE FULLY AT THE CUSTOMER'S RISK.

In order to minimize risks associated with the customer's applications, adequate design and operating safeguards must be provided by the customer to minimize inherent or procedural hazards.

TI assumes no liability for applications assistance or customer product design. TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right of TI covering or relating to any combination, machine, or process in which such semiconductor products or services might be or are used. TI's publication of information regarding any third party's products or services does not constitute TI's approval, warranty or endorsement thereof.

Copyright © 1998, Texas Instruments Incorporated