SLES104 - DECEMBER 2003

- Single Chip Mixer/Oscillator and Synthesizer

- 3-Band Local Oscillator

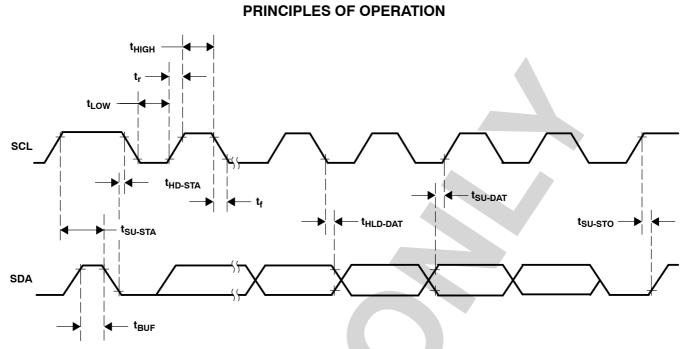

- I<sup>2</sup>C Bus Protocol

- Bidirectional Data Transmission

- 30-V Tuning Voltage Output

- 4-Channel NPN-Type Bandswitch Drivers

- Programmable Reference Divider Ratio (512, 640, or 1024)

- 5-V Power Supply

- 30-Pin TSSOP Package

#### description

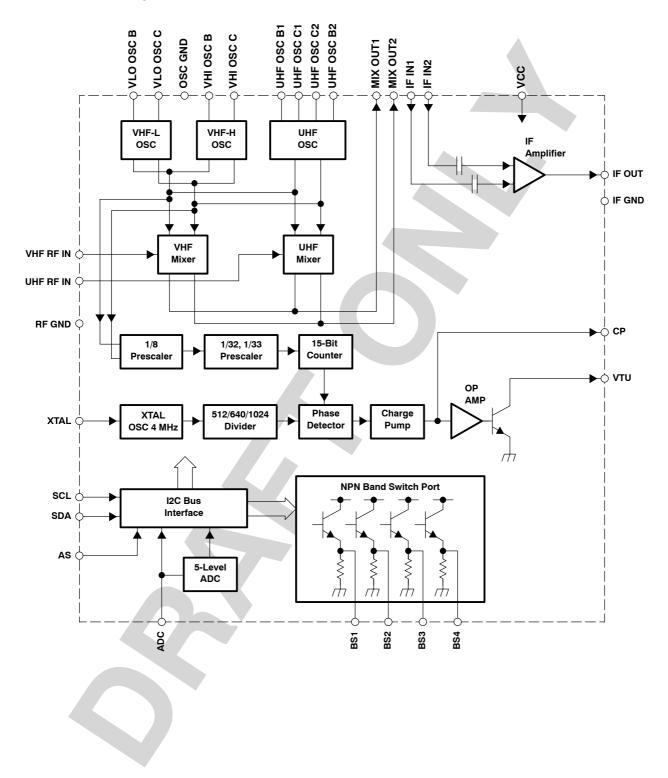

The SN761678 is a single-chip, synthesized tuner IC designed for TV/VCR tuning systems. The circuit consists of a PLL synthesizer, 3-band local oscillators and mixer, 30-V output tuning amplifier, four NPN band switch drivers, and is available in a small package outline. Fifteen-bit programmable counter and reference divider is controlled by I<sup>2</sup>C bus protocol. Tuning step frequency is selectable by this reference divider ratio for a 4-MHz XTAL oscillator.

**NOTE:** The products, their specifications, service and other information appearing in this publication are subjected to change by Texas Instruments without notice.

This device has limited built-in ESD protection. The leads should be shorted together or the device placed in conductive foam during storage or handling to prevent electrostatic damage to the MOS gates.

Please be aware that an important notice concerning availability, standard warranty, and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

PRODUCTION DATA information is current as of publication date. Products conform to specifications per the terms of Texas Instruments standard warranty. Production processing does not necessarily include testing of all parameters.

Copyright © 2003, Texas Instruments Incorporated

SLES104 - DECEMBER 2003

### functional block diagram

SLES104 - DECEMBER 2003

SLES104 - DECEMBER 2003

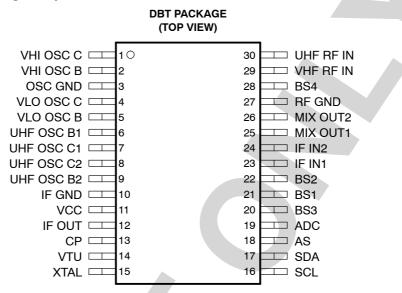

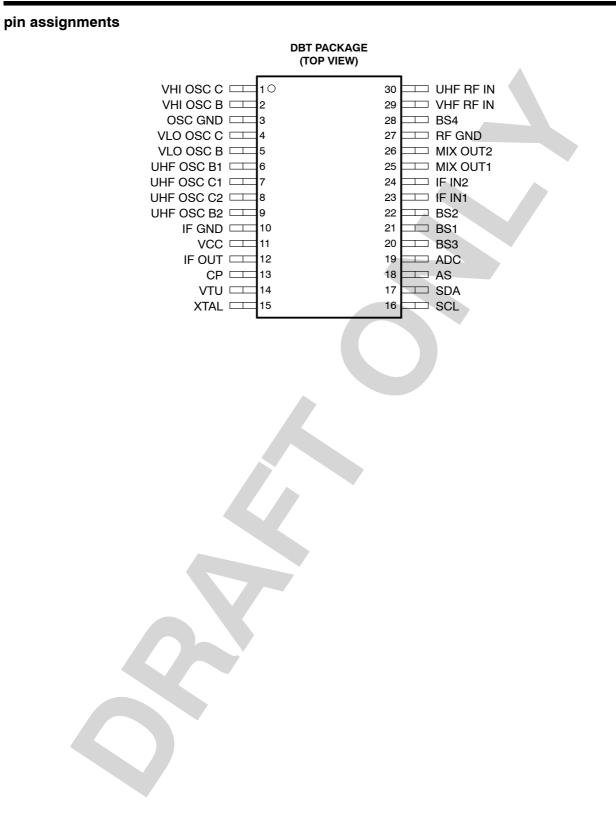

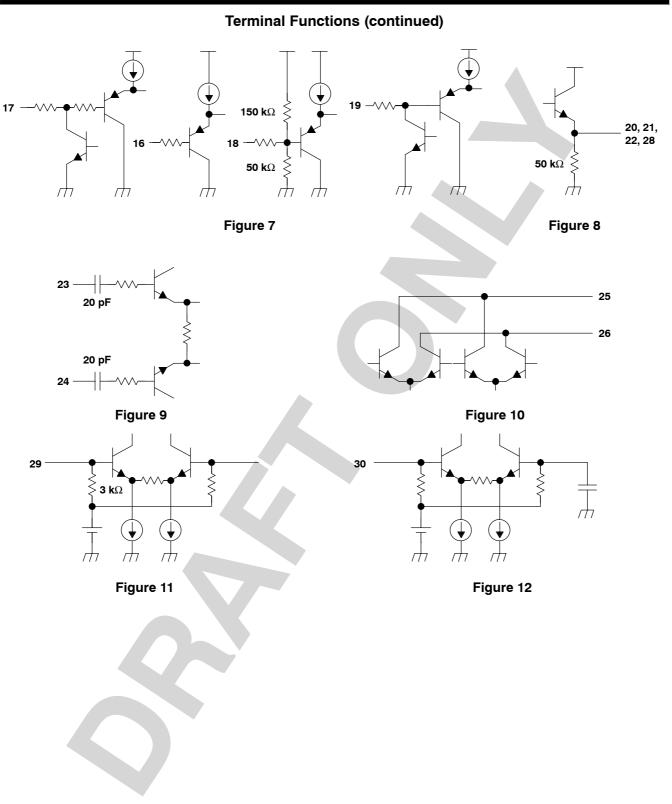

#### **Terminal Functions**

Table 1 provides a cross-reference between the terminal number and the signal name.

### Table 1. Signal Names Sorted by DBT Terminal Number

| Т      | ERMINAL     |                                                     |               |

|--------|-------------|-----------------------------------------------------|---------------|

| NUMBER | SIGNAL NAME | DESCRIPTION                                         | SCHEMATIC     |

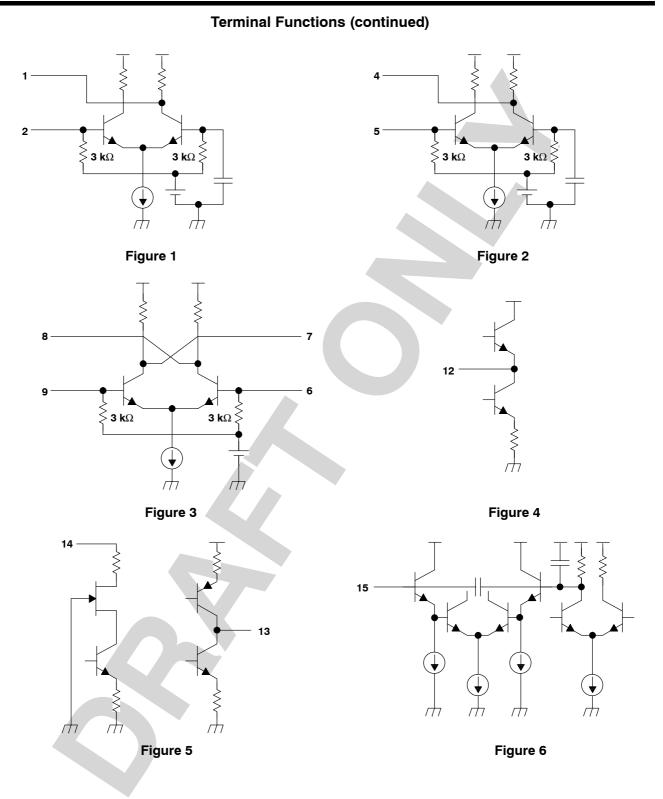

| 1      | VHI OSC C   | VHF HIGH oscillator collector                       | See Figure 1  |

| 2      | VHI OSC B   | VHF HIGH oscillator base                            | See Figure 1  |

| 3      | OSC GND     | OSC ground                                          |               |

| 4      | VLO OSC C   | VHF LOW oscillator collector                        | See Figure 2  |

| 5      | VLO OSC B   | VHF LOW oscillator base                             | See Figure 2  |

| 6      | UHF OSC B1  | UHF oscillator base 1                               | See Figure 3  |

| 7      | UHF OSC C1  | UHF oscillator collector 1                          | See Figure 3  |

| 8      | UHF OSC C2  | UHF oscillator collector 2                          | See Figure 3  |

| 9      | UHF OSC B2  | UHF oscillator base 2                               | See Figure 3  |

| 10     | IF GND      | IF ground                                           |               |

| 11     | VCC         | Supply voltage for mixer/oscillator/PLL: 5 V        |               |

| 12     | IF OUT      | IF output                                           | See Figure 4  |

| 13     | CP          | Charge pump output                                  | See Figure 5  |

| 14     | VTU         | Tuning voltage amplifier output                     | See Figure 5  |

| 15     | XTAL        | 4-MHz crystal oscillator input                      | See Figure 6  |

| 16     | SCL         | Serial data input/output                            | See Figure 7  |

| 17     | SDA         | Serial clock input                                  | See Figure 7  |

| 18     | AS          | Address selection input                             | See Figure 7  |

| 19     | ADC         | ADC input                                           | See Figure 7  |

| 20     | BS3 (FMST)  | Bandswitch 1 output/FM (NPN emitter follower)       | See Figure 8  |

| 21     | BS1 (VHFL)  | Bandswitch 2 output/VHF-LOW (NPN emitter follower)  | See Figure 8  |

| 22     | BS2 (VHFH)  | Bandswitch 3 output/VHF-HIGH (NPN emitter follower) | See Figure 8  |

| 23     | IF IN1      | IF amplifier input                                  | See Figure 9  |

| 24     | IF IN2      | IF amplifier input                                  | See Figure 9  |

| 25     | MIX OUT1    | Mixer output                                        | See Figure 10 |

| 26     | MIX OUT2    | Mixer output                                        | See Figure 10 |

| 27     | RF GND      | RF ground                                           |               |

| 28     | BS4 (UHF)   | Bandswitch 4 output/UHF (NPN emitter follower)      | See Figure 8  |

| 29     | VHF RF IN   | VHF RF input                                        | See Figure 11 |

| 30     | UHF RF IN   | UHF RF input                                        | See Figure 12 |

SLES104 - DECEMBER 2003

SLES104 - DECEMBER 2003

SLES104 - DECEMBER 2003

#### absolute maximum ratings over operating free-air temperature (unless otherwise noted)<sup>†</sup>

| Supply voltage, V <sub>CC</sub> (terminal 11) (Note 1)                                           | . –0.4 V to 6.5 V |

|--------------------------------------------------------------------------------------------------|-------------------|

| Input voltage 1, V <sub>GND</sub> (terminals 3 and 27) (Note 1)                                  | . –0.4 V to 0.4 V |

| Input voltage 2, V <sub>VTU</sub> (terminal 14) (Note 1)                                         | . –0.4 V to 35 V  |

| Input voltage 3, V <sub>IN</sub> (terminals 1, 2, 4–9, 12, 13, 15–26, 28–30) (Note 1)            | . –0.4 V to 6.5 V |

| Continuous total power dissipation, $T_A \le 25^{\circ}$ C, $P_D$ (Note 2)                       | 1071 mW           |

| Operating free-air temperature, T <sub>OPE</sub>                                                 |                   |

| Storage temperature range, T <sub>STG</sub>                                                      | –65 to 150°C      |

| Maximum junction temperature, T <sub>JC</sub>                                                    | 150°C             |

| Maximum lead temperature (1.6 mm (1/16 inch) from case for 10 seconds)                           |                   |

| Maximum short circuit time, t <sub>SC(max)</sub>                                                 |                   |

| (All terminals to V <sub>CC.</sub> All terminals to IFGND, OSCGND, RFGND except for terminal 26) | 10 s              |

<sup>†</sup> Stresses beyond those listed under *absolute maximum ratings* may cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those indicated under *recommended operating conditions* is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

NOTES: 1. Voltage values are with respect to the IF GND of the circuit.

2. Derating factor is 8.57 mW/°C for  $T_{A}{\leq}25^{\circ}C.$

#### recommended operating conditions

|                  | PARAMETER                      | CONDITIONS  | MIN | ТҮР | MAX | UNIT |

|------------------|--------------------------------|-------------|-----|-----|-----|------|

| V <sub>CC</sub>  | Supply voltage                 |             | 4.5 | 5   | 5.5 | V    |

| V <sub>TU</sub>  | Tuning supply voltage          |             |     | 30  | 33  | V    |

| I <sub>BS</sub>  | Output current of bandswitch   | One port On |     |     | 10  | mA   |

| T <sub>OPE</sub> | Operating free-air temperature |             | -20 |     | 85  | °C   |

CAUTION: It is advised that precautions be taken to avoid damage due to high static voltages or electrostatic fields in handling this device.

SLES104 - DECEMBER 2003

#### electrical characteristics

#### total device and serial interface

$V_{CC}$  = 4.5 to 5.5 V,  $T_{OPE}$  = –20 to 85°C, unless otherwise noted

| PARAMETER            |                                         | CONDITIONS                                                   |     | TYP | MAX             | UNIT |

|----------------------|-----------------------------------------|--------------------------------------------------------------|-----|-----|-----------------|------|

| lcc1                 | Supply current 1                        |                                                              |     | 60  |                 | mA   |

| lcc2                 | Supply current 2                        | One band switch On (I <sub>BS</sub> = 10 mA)                 |     | 70  |                 | mA   |

| V <sub>IH</sub>      | High level input voltage (SCL, SDA)     |                                                              | 2.8 |     | Vcc             | V    |

| V <sub>IL</sub>      | Low level input voltage (SCL, SDA)      |                                                              |     |     | 1.4             | V    |

| IIH                  | High level input current (SCL, SDA)     |                                                              |     | 2   | 10              | μA   |

| IIL                  | Low level input current (SCL, SDA)      |                                                              | -10 |     |                 | μA   |

| V <sub>POR</sub>     | Power on reset supply voltage           | Threshold of supply voltage between reset and operation mode | 2.1 | 2.8 | 3.5             | V    |

| I2C interfa          | ice                                     |                                                              |     |     |                 |      |

| V <sub>ASH</sub>     | Address select high input voltage (AS)  | $V_{CC} = 5 V$                                               | 4.5 |     | 5.0             | V    |

| V <sub>ASM1</sub>    | Address select mid1 input voltage (AS)  | $V_{CC} = 5 V$                                               | 2.0 |     | 3.0             | V    |

| V <sub>ASM2</sub>    | Address select mid2 input voltage (AS)  | $V_{CC} = 5 V$                                               | 1.0 |     | 1.5             | V    |

| V <sub>ASL</sub>     | Address select low input voltage (AS)   | $V_{CC} = 5 V$                                               |     |     | 0.5             | V    |

| I <sub>ASH</sub>     | Address select high input current (AS)  |                                                              |     |     | 120             | μA   |

| I <sub>ASL</sub>     | Address select low input current (AS)   |                                                              | -10 |     |                 | μA   |

| V <sub>ADC</sub>     | ADC input voltage                       | See Table 9                                                  | 0   |     | V <sub>CC</sub> | V    |

| I <sub>ADH</sub>     | ADC high level input current            | $V_{ADC} = V_{CC}$                                           |     |     | 10              | μA   |

| I <sub>ADL</sub>     | ADC low level input current             | V <sub>ADC</sub> = 0 V                                       | -10 |     |                 | μA   |

| F <sub>SCL</sub>     | Clock frequency (SCL)                   |                                                              |     | 100 | 400             | kHz  |

| V <sub>OL</sub>      | Low level output voltage (SDA)          | $V_{CC} = 5 \text{ V}, \text{ I}_{OL} = 3 \text{ mA}$        |     |     | 0.4             | V    |

| I <sub>SDAH</sub>    | High level output leakage current (SDA) | V <sub>SDA</sub> = 5.5 V                                     |     |     | 10              | μA   |

| t <sub>HLD-DAT</sub> | Data hold time                          | See timing chart, Figure 1                                   | 0   |     |                 | μs   |

| t <sub>BUF</sub>     | Bus free time                           |                                                              | 1.3 |     |                 | μs   |

| t <sub>HD-STA</sub>  | Start hold time                         |                                                              | 0.6 |     |                 | μs   |

| t <sub>LOW</sub>     | SCL low hold time                       |                                                              | 1.3 |     |                 | μs   |

| t <sub>HIGH</sub>    | SCL high hold time                      |                                                              | 0.6 |     |                 | μs   |

| t <sub>SU-STA</sub>  | Start setup time                        |                                                              | 0.6 |     |                 | μs   |

| t <sub>SU-DAT</sub>  | Data setup time                         |                                                              | 0.1 |     |                 | μs   |

| t <sub>R</sub>       | SCL, SDA rise time                      |                                                              |     |     | 0.3             | μs   |

| t <sub>F</sub>       | SCL, SDA fall time                      |                                                              |     |     | 0.3             | μs   |

| tst-sto              | Stop setup time                         |                                                              | 0.6 |     |                 | μs   |

SLES104 - DECEMBER 2003

### electrical characteristics (continued)

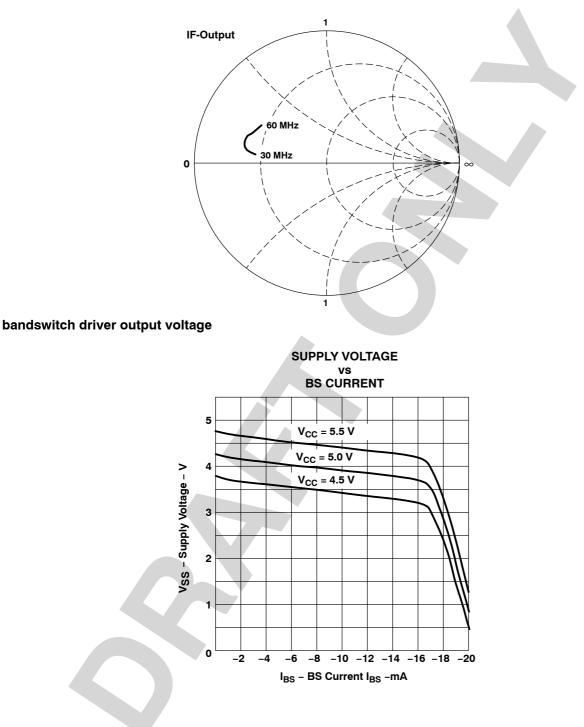

### PLL and bandswitch

$V_{CC}$  = 4.5 to 5.5 V,  $T_{OPE}$  = –20 to 85  $^{\circ}C,$  unless otherwise noted

|                     | PARAMETER                                  | CONDITION                                                                               | MIN | TYP  | MAX       | UNIT  |

|---------------------|--------------------------------------------|-----------------------------------------------------------------------------------------|-----|------|-----------|-------|

| Ν                   | Divider ratio                              | 15-bit frequency word                                                                   | 256 |      | 3276<br>7 |       |

| F <sub>XTAL</sub>   | Crystal oscillator                         | $R_{XTAL} = 25 \Omega$ to 300 $\Omega$                                                  | 3.2 | 4    | 4.48      | MHz   |

| Z <sub>XTAL</sub>   | Crystal oscillator input impedance         |                                                                                         |     | 1.6  |           | kΩ    |

| V <sub>IXTAL2</sub> | Minimum reference input sensitivity (XTAL) | 4 MHz, ac coupling with 0.1 $\mu F$                                                     |     |      | 100       | mVp-p |

| V <sub>VTUL</sub>   | Tuning amplifier low level output voltage  | $R_L = 27 \text{ k}\Omega, V_{TU} = 33 \text{ V}$                                       | 0.2 | 0.3  | 0.46      | V     |

| IVTUOFF             | Tuning amplifier leakage current (off)     | OS = 1, V <sub>TU</sub> = 33 V                                                          |     |      | 10        | μA    |

| I <sub>CPH</sub>    | Charge pump high level input current       | CP = 1                                                                                  |     | 280  |           | μA    |

| I <sub>CPL</sub>    | Charge pump low level input current        | CP = 0                                                                                  |     | 60   |           | μA    |

| V <sub>CP</sub>     | Charge pump output voltage                 | In-lock                                                                                 |     | 1.95 |           | V     |

| ICPOFF              | Charge pump leakage current                | T2 = 0, T1 = 1, $V_{CP}$ = 2 V, T <sub>A</sub> = 25°C                                   | -15 |      | +15       | nA    |

| I <sub>BS</sub>     | Band switch driver output current          |                                                                                         |     |      | 10        | mA    |

| V <sub>SBS1</sub>   | Band switch driver output voltage          | I <sub>BS</sub> = 10 mA                                                                 | 3.0 |      |           | V     |

| V <sub>SBS2</sub>   |                                            | $I_{BS} = 10 \text{ mA}, \text{ Vcc} = 5 \text{ V}, \text{ T}_{A} = 25^{\circ}\text{C}$ | 3.5 | 3.9  |           | V     |

| IBSOFF              | Band switch driver leakage current         | $V_{BS} = 0 V$                                                                          |     |      | 3         | μA    |

SLES104 - DECEMBER 2003

#### electrical characteristics (continued)

#### mixer, oscillator, IF amplifier

$V_{CC}$  = 5 V,  $T_A$  = 25°C, measured in reference measurement circuit at 50- $\Omega$  system, IF filter characteristics: fPEAK = 43 MHz; unless otherwise noted

|                                        | PARAMETER                                           | CONDITION                                                             | MIN      | TYP            | MAX      | UNIT   |

|----------------------------------------|-----------------------------------------------------|-----------------------------------------------------------------------|----------|----------------|----------|--------|

| G <sub>c1</sub><br>G <sub>c3</sub>     | Conversion gain<br>(mixer to IF amplifier) VHF-low  | F <sub>in</sub> = 58 MHz (Note 3)<br>F <sub>in</sub> = 130 MHz        | 22<br>22 | 25<br>25       | 28<br>28 | dB     |

| G <sub>c4</sub><br>G <sub>c6</sub>     | Conversion gain<br>(mixer to IF amplifier) VHF-high | F <sub>in</sub> = 136 MHz (Note 3)<br>F <sub>in</sub> = 364 MHz       | 22<br>22 | 25<br>25       | 28<br>28 | dB     |

| G <sub>c7</sub><br>G <sub>c9</sub>     | Conversion gain<br>(mixer to IF amplifier) VHF-UHF  | F <sub>in</sub> = 370 MHz (Note 3)<br>F <sub>in</sub> = 804 MHz       | 26<br>25 | 29<br>28       | 32<br>31 | dB     |

| NF <sub>1</sub><br>NF <sub>3</sub>     | Noise figure<br>VHF-low                             | F <sub>in</sub> = 55.25 MHz<br>F <sub>in</sub> = 127.25 MHz           |          | (9.5)<br>(9.5) |          | dB     |

| NF <sub>4</sub><br>NF <sub>6</sub>     | Noise figure<br>VHF-high                            | F <sub>in</sub> = 133.25 MHz<br>F <sub>in</sub> = 361.25 MHz          |          | (10)<br>(10)   |          | dB     |

| NF <sub>7</sub><br>NF <sub>9</sub>     | Noise figure<br>UHF                                 | F <sub>in</sub> = 367.25 MHz<br>F <sub>in</sub> = 801.25 MHz          |          | (11)<br>(11)   |          | dB     |

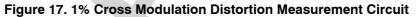

| CM <sub>1</sub><br>CM <sub>3</sub>     | 1% cross modulation distortion VHF-low              | F <sub>in</sub> = 55.25 MHz (Note 4)<br>F <sub>in</sub> = 127.25 MHz  |          | (89)<br>(89)   |          | dBμV   |

| CM <sub>4</sub><br>CM <sub>6</sub>     | 1% cross modulation distortion VHF-high             | F <sub>in</sub> = 133.25 MHz (Note 4)<br>F <sub>in</sub> = 361.25 MHz |          | (86)<br>(86)   |          | dBμV   |

| CM <sub>7</sub><br>CM <sub>9</sub>     | 1% cross modulation distortion UHF                  | F <sub>in</sub> = 367.25 MHz (Note 4)<br>F <sub>in</sub> = 801.25 MHz |          | (87)<br>(87)   |          | dBμV   |

| V <sub>IFO1</sub><br>V <sub>IFO3</sub> | IF output voltage<br>VHF-low                        | F <sub>in</sub> = 55.25 MHz (Note 5)<br>F <sub>in</sub> = 127.25 MHz  |          | 117<br>117     |          | dBμV   |

| V <sub>IFO4</sub><br>V <sub>IFO6</sub> | IF output voltage<br>VHF-high                       | F <sub>in</sub> = 133.25 MHz (Note 5)<br>F <sub>in</sub> = 361.25 MHz |          | 117<br>117     |          | dBμV   |

| V <sub>IFO7</sub><br>V <sub>IFO9</sub> | IF output voltage<br>UHF                            | F <sub>in</sub> = 367.25 MHz (Note 5)<br>F <sub>in</sub> = 801.25 MHz |          | 117<br>117     |          | dBμV   |

| $\Phi_{ m OSC1} \Phi_{ m OSC3}$        | Phase noise<br>VHF-low                              | F <sub>in</sub> = 55.25 MHz (Note 6)<br>F <sub>in</sub> = 127.25 MHz  |          | 88<br>88       |          | dBc/Hz |

| $\Phi_{OSC4}$<br>$\Phi_{OSC6}$         | Phase noise<br>VHF-high                             | F <sub>in</sub> = 133.25 MHz (Note 6)<br>F <sub>in</sub> = 361.25 MHz |          | 86<br>86       |          | dBc/Hz |

| $\Phi_{ m OSC7}$<br>$\Phi_{ m OSC9}$   | Phase noise<br>UHF                                  | F <sub>in</sub> = 367.25 MHz (Note 6)<br>F <sub>in</sub> = 801.25 MHz |          | 84<br>84       |          | dBc/Hz |

|                                        | Prescaler beat (Note 7)                             |                                                                       |          |                | (25)     | dBµV   |

NOTES: 3. IF = 43 MHz, RF input level = 80 dBµV

4.  $F_{undes} = F_{des}\pm 6$  MHz, Pin = 80 dBµV, AM 1 kHz, 30%, DES/CM = S/I = 46 dB

5. IF = 45.75 MHz

6. Offset = 10 kHz, RF input level = 70 dB $\mu$ V

7. Design parameter, not tested.

SLES104 - DECEMBER 2003

#### **PRINCIPLES OF OPERATION**

### I<sup>2</sup>C bus mode

### (1) $I^2C$ write mode (R/W = 0)

### Table 2. Write Data Format

|                      | MSB |     |     |     |     |     |     | LSB     |   |

|----------------------|-----|-----|-----|-----|-----|-----|-----|---------|---|

| Address byte (ADB)   | 1   | 1   | 0   | 0   | 0   | MA1 | MA0 | R/W = 0 | А |

| Divider byte 1 (DB1) | 0   | N14 | N13 | N12 | N11 | N10 | N9  | N8      | А |

| Divider byte 2 (DB2) | N7  | N6  | N5  | N4  | N3  | N2  | N1  | N0      | А |

| Control byte (CB)    | 1   | CP  | T2  | T1  | ТО  | RSA | RSB | OS      | А |

| Bandswitch byte (BB) | Х   | Х   | Х   | Х   | BS4 | BS3 | BS2 | BS1     | А |

#### A: Acknowledge

#### Table 3. Description of Data Symbols

| SYMBOL     | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | DEFAULT                |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------|

| MA1, MA0   | Address set bits (see Table 4)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |                        |

| N14N0      | Programmable counter set bits<br>N = N14*2^14 + N13*2^13 + + N1*2 + N0<br>Oscillation frequency = fr x 8 x N<br>fr = reference frequency = 4 MHz / Reference divider                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Nn = 0                 |

| CP         | Charge pump current set bit<br>$60 \ \mu A \ (CP = 0)$<br>$280 \ \mu A \ (CP = 1)$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | CP = 1                 |

| T2, T1, T0 | Test bits (see Table 5)<br>Normal mode: $T2 = 0$ , $T1 = 0$ , $T0 = 1/0$                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | T2 = 0, T1 = 0, T0 = 1 |

| RSA, RSB   | Reference divider ratio selection bits (see table 6 reference divider ratio)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | RSA = 0, RSB = 1       |

| OS         | Tuning amplifier control bit<br>Tuning voltage on (OS = 0)<br>Tuning voltage off, high impedance (OS = 1)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | OS = 0                 |

| BS4BS1     | Band switch ports control bitsBSn = 0: OFF, BSn = 1: ONBand selection by BS1, 2, 4 (x: don't care) $\frac{BS1 (VL)}{1}$ $\frac{BS2 (VH)}{0}$ $\frac{BS1 (VL)}{1}$ $\frac{BS2 (VH)}{1}$ $BS2 $ | BSn = 0                |

| Х          | Don't care                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |                        |

#### **Table 4. Address Selection**

| Table 4. Address Selection                       |     |     |  |  |  |  |  |  |  |

|--------------------------------------------------|-----|-----|--|--|--|--|--|--|--|

| VOLTAGE APPLIED ON AS INPUT                      | MA1 | MA0 |  |  |  |  |  |  |  |

| Low: 0 V to 0.1 V <sub>CC</sub>                  | 0   | 0   |  |  |  |  |  |  |  |

| MID2: Open, or, 0.2 $V_{CC}$ to 0.3 $V_{CC}$     | 0   | 1   |  |  |  |  |  |  |  |

| MID1: 0.4 V <sub>CC</sub> to 0.6 V <sub>CC</sub> | 1   | 0   |  |  |  |  |  |  |  |

| High: 0.9 V <sub>CC</sub> to V <sub>CC</sub>     | 1   | 1   |  |  |  |  |  |  |  |

SLES104 - DECEMBER 2003

### **PRINCIPLES OF OPERATION**

| T2 T | то | FUNCTION                      |

|------|----|-------------------------------|

| 0 0  | 0  | Normal operation              |

| 0 0  | 1  | Normal operation (default)    |

| 0 1  | Х  | Charge pump off               |

| 1 1  | 0  | Charge pump sink              |

| 1 1  | 1  | Charge pump source            |

| 1 0  | Х  | Test mode (not available ADC) |

#### Table 5. Test Bits (Note 8)

NOTE 8: Not used for other bit patterns.

#### **Table 6. Ratio Select Bits**

| RSA | RSB | REFERENCE DIVIDER RATIO |  |  |  |  |  |  |

|-----|-----|-------------------------|--|--|--|--|--|--|

| Х   | 0   | 640                     |  |  |  |  |  |  |

| 0   | 1   | 1024                    |  |  |  |  |  |  |

| 1   | 1   | 512                     |  |  |  |  |  |  |

## (2) $I^2C$ Read mode (R/W = 1)

#### Table 7. Read Data Format

|                    | MSB |    |   |   |   |     |     | LSB     |   |

|--------------------|-----|----|---|---|---|-----|-----|---------|---|

| Address byte (ADB) | 1   | 1  | 0 | 0 | 0 | MA1 | MA0 | R/W = 1 | А |

| Status byte (SB)   | POR | FL | 1 | 1 | 1 | A2  | A1  | A0      | А |

A: Acknowledge

#### Table 8. Description of Data Symbols

| SYMBOL   | DESCRIPTION                                                                                 | DEFAULT |

|----------|---------------------------------------------------------------------------------------------|---------|

| MA1, MA0 | Address set bits (see Table 4 address selection)                                            |         |

| POR      | Power-on reset flag<br>POR set = power on<br>POR reset = end-of-data transmission procedure | POR = 1 |

| FL       | In-lock flag<br>PLL lock (FL = 1) unlock (FL = 0)                                           |         |

| A2A0     | Digital data of ADC (see Table 9)                                                           |         |

#### Table 9. ADC Level

| VOLTAGE APPLIED ON ADC INPUT                | A2                                                                                                                                                                                                      | A1                                                                                                                                                                                                               | A0 |

|---------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

| 0.6 V <sub>CC</sub> to V <sub>CC</sub>      | 1                                                                                                                                                                                                       | 0                                                                                                                                                                                                                | 0  |

| 0.45 V <sub>CC</sub> to 0.6 V <sub>CC</sub> | 0                                                                                                                                                                                                       | 1                                                                                                                                                                                                                | 1  |

| 0.3 V <sub>CC</sub> to 0.45 V <sub>CC</sub> | 0                                                                                                                                                                                                       | 1                                                                                                                                                                                                                | 0  |

| 0.15 V <sub>CC</sub> to 0.3 V <sub>CC</sub> | 0                                                                                                                                                                                                       | 0                                                                                                                                                                                                                | 1  |

| 0 to 0.15 V <sub>CC</sub>                   | 0                                                                                                                                                                                                       | 0                                                                                                                                                                                                                | 0  |

|                                             | $\begin{array}{c} 0.6 \ V_{CC} \ \text{to} \ V_{CC} \\ 0.45 \ V_{CC} \ \text{to} \ 0.6 \ V_{CC} \\ 0.3 \ V_{CC} \ \text{to} \ 0.45 \ V_{CC} \\ 0.15 \ V_{CC} \ \text{to} \ 0.3 \ V_{CC} \\ \end{array}$ | 0.6 V <sub>CC</sub> to V <sub>CC</sub> 1           0.45 V <sub>CC</sub> to 0.6 V <sub>CC</sub> 0           0.3 V <sub>CC</sub> to 0.45 V <sub>CC</sub> 0           0.15 V <sub>CC</sub> to 0.3 V <sub>CC</sub> 0 |    |

NOTE 9: Note 9: Accuracy is 0.03 x V<sub>CC</sub>.

SLES104 - DECEMBER 2003

POST OFFICE BOX 655303 • DALLAS, TEXAS 75265

SLES104 - DECEMBER 2003

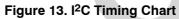

### **APPLICATION INFORMATION**

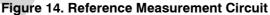

#### reference measurement circuit

NOTE 10: This application information is advisory and performance check is required at actual application circuits.

TI assumes no responsibility for the consequences of use of this circuit nor for any infringement of patent or patent rights of third parties which may result from its use.

SLES104 - DECEMBER 2003

#### **APPLICATION INFORMATION**

### component values for measurement circuit

| PARTS NAME | VALUE             | PARTS NAME | VALUE       |

|------------|-------------------|------------|-------------|

| U1         | SN761678          | C1         | 2 pF        |

|            |                   | C2         | 3 pF        |

| VC1        | 1T363A            | C3         | 68 pF       |

| VC2        | 1T363A            | C4         | open        |

| VC3        | 1T363A            | C5         | 1 pF        |

|            |                   | C6         | 1 pF        |

| L1         | φ2.4mm 4T 0.4mm   | C7         | 47 pF       |

| L2         | φ3.0mm 8T 0.32mm  | C8         | 3 pF        |

| L3         | φ3.0mm 2T 0.4mm   | C9         | 1.5 pF      |

| L4         | φ2.0mm 3T 0.4mm   | C10        | 1.5 pF      |

| L5         | ¢2.4mm 16T 0.26mm | C11        | 1.5 pF      |

| L6         | φ2.4mm 16T 0.26mm | C12        | 1.5 pF      |

| L7         | open              | C13        | 12 pF       |

| L8         | open              | C14        | 100 pF      |

|            |                   | C15        | -           |

| X1         | 4 MHz             | C16        | 2.2 nF/50 V |

|            |                   | C17        | 2.2 nF/50 V |

| R1         | 33 kΩ             | C18        | 2.2 nF/50 V |

| R2         | 33 kΩ             | C19        | -           |

| R3         | 22 kΩ             | C20        | 2.2 nF      |

| R4         | 33 kΩ             | C21        | 4.7 nF      |

| R5         | 22 kΩ             | C22        | 2.2 nF      |

| R6         | -                 | C23        | 0.1 μF/50 V |

| R7         | 22 kΩ             | C24        | 2.2 nF/50 V |

| R8         | 22 kΩ             | C25        | -           |

| R9         | -                 | C26        | -           |

| R10        | 330 Ω             | C27        | 68 pF       |

| R11        | 330 Ω             | C28        | open        |

| R12        | 330 Ω             | C29        | open        |

| R13        | short             | C30        | open        |

| R14        | short             | C31        | short       |

| R15        |                   | C32        | short       |

| R16        | open              | C33        | open        |

| R17        | open              | C34        | 22 pF       |

|            | 1                 | C35        | open        |

|            | 1                 | C36        | 4.7 nF      |

|            |                   | C37        | -           |

|            | 1                 | C38        | 2.2 nF      |

|            |                   | C39        | 2.2 nF      |

SLES104 - DECEMBER 2003

### **APPLICATION INFORMATION**

#### test circuit

Figure 15. Measurement Circuit of Conversion Gain

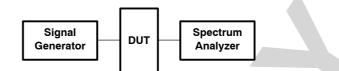

Figure 16. Noise Figure Measurement Circuit

SLES104 - DECEMBER 2003

### **APPLICATION INFORMATION**

### typical characteristics

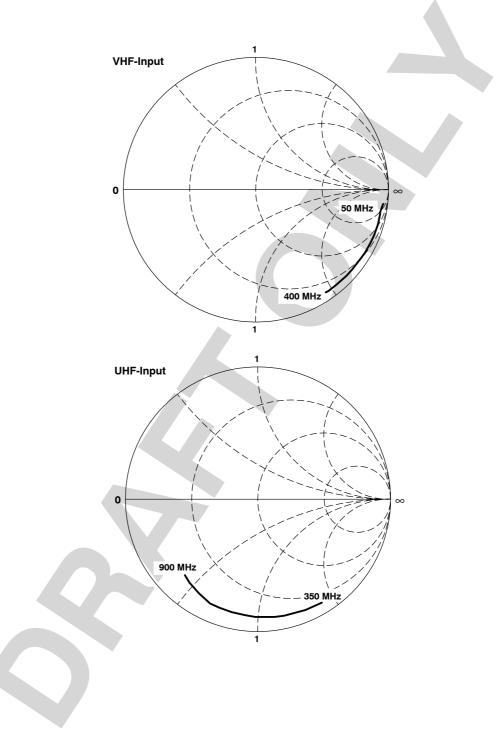

### S-parameter

SLES104 - DECEMBER 2003

### **APPLICATION INFORMATION**

#### **IF-output**

SLES104 - DECEMBER 2003

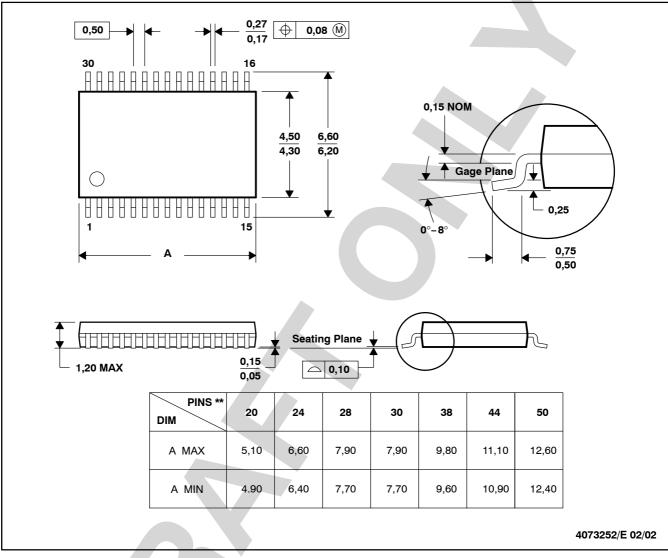

### **MECHANICAL DATA**

#### DBT (R-PDSO-G\*\*)

#### PLASTIC SMALL-OUTLINE PACKAGE

The SN761678 tuner is encased in a thin shrink small outline package (TSSOP).

NOTES: A. All linear dimensions are in millimeters.

- B. This drawing is subject to change without notice.

- C. Body dimensions do not include mold flash or protrusion.

- D. Falls within JEDEC MO-153

SLES104 - DECEMBER 2003

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, modifications, enhancements, improvements, and other changes to its products and services at any time and to discontinue any product or service without notice. Customers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All products are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its hardware products to the specifications applicable at the time of sale in accordance with TI's standard warranty. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by government requirements, testing of all parameters of each product is not necessarily performed.

TI assumes no liability for applications assistance or customer product design. Customers are responsible for their products and applications using TI components. To minimize the risks associated with customer products and applications, customers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any TI patent right, copyright, mask work right, or other TI intellectual property right relating to any combination, machine, or process in which TI products or services are used. Information published by TI regarding third-party products or services does not constitute a license from TI to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. Reproduction of this information with alteration is an unfair and deceptive business practice. TI is not responsible or liable for such altered documentation.

Resale of TI products or services with statements different from or beyond the parameters stated by TI for that product or service voids all express and any implied warranties for the associated TI product or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Following are URLs where you can obtain information on other Texas Instruments products and application solutions:

| Products         |                        | Applications       |                           |

|------------------|------------------------|--------------------|---------------------------|

| Amplifiers       | amplifier.ti.com       | Audio              | www.ti.com/audio          |

| Data Converters  | dataconverter.ti.com   | Automotive         | www.ti.com/automotive     |

| DSP              | dsp.ti.com             | Broadband          | www.ti.com/broadband      |

| Interface        | interface.ti.com       | Digital Control    | www.ti.com/digitalcontrol |

| Logic            | logic.ti.com           | Military           | www.ti.com/military       |

| Power Mgmt       | power.ti.com           | Optical Networking | www.ti.com/opticalnetwork |

| Microcontrollers | microcontroller.ti.com | Security           | www.ti.com/security       |

|                  |                        | Telephony          | www.ti.com/telephony      |

|                  |                        | Video & Imaging    | www.ti.com/video          |

|                  |                        | Wireless           | www.ti.com/wireless       |

|                  |                        |                    |                           |

Mailing Address:

Post Office Box 655303 Dallas, Texas 75265

**Texas Instruments**

Copyright © 2003, Texas Instruments Incorporated

#### **IMPORTANT NOTICE**

Texas Instruments Incorporated and its subsidiaries (TI) reserve the right to make corrections, enhancements, improvements and other changes to its semiconductor products and services per JESD46, latest issue, and to discontinue any product or service per JESD48, latest issue. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products (also referred to herein as "components") are sold subject to TI's terms and conditions of sale supplied at the time of order acknowledgment.

TI warrants performance of its components to the specifications applicable at the time of sale, in accordance with the warranty in TI's terms and conditions of sale of semiconductor products. Testing and other quality control techniques are used to the extent TI deems necessary to support this warranty. Except where mandated by applicable law, testing of all parameters of each component is not necessarily performed.

TI assumes no liability for applications assistance or the design of Buyers' products. Buyers are responsible for their products and applications using TI components. To minimize the risks associated with Buyers' products and applications, Buyers should provide adequate design and operating safeguards.

TI does not warrant or represent that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right relating to any combination, machine, or process in which TI components or services are used. Information published by TI regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from TI under the patents or other intellectual property of TI.

Reproduction of significant portions of TI information in TI data books or data sheets is permissible only if reproduction is without alteration and is accompanied by all associated warranties, conditions, limitations, and notices. TI is not responsible or liable for such altered documentation. Information of third parties may be subject to additional restrictions.

Resale of TI components or services with statements different from or beyond the parameters stated by TI for that component or service voids all express and any implied warranties for the associated TI component or service and is an unfair and deceptive business practice. TI is not responsible or liable for any such statements.

Buyer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of TI components in its applications, notwithstanding any applications-related information or support that may be provided by TI. Buyer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Buyer will fully indemnify TI and its representatives against any damages arising out of the use of any TI components in safety-critical applications.

In some cases, TI components may be promoted specifically to facilitate safety-related applications. With such components, TI's goal is to help enable customers to design and create their own end-product solutions that meet applicable functional safety standards and requirements. Nonetheless, such components are subject to these terms.

No TI components are authorized for use in FDA Class III (or similar life-critical medical equipment) unless authorized officers of the parties have executed a special agreement specifically governing such use.

Only those TI components which TI has specifically designated as military grade or "enhanced plastic" are designed and intended for use in military/aerospace applications or environments. Buyer acknowledges and agrees that any military or aerospace use of TI components which have *not* been so designated is solely at the Buyer's risk, and that Buyer is solely responsible for compliance with all legal and regulatory requirements in connection with such use.

TI has specifically designated certain components as meeting ISO/TS16949 requirements, mainly for automotive use. In any case of use of non-designated products, TI will not be responsible for any failure to meet ISO/TS16949.

| Products                     |                          | Applications                  |                                   |

|------------------------------|--------------------------|-------------------------------|-----------------------------------|

| Audio                        | www.ti.com/audio         | Automotive and Transportation | www.ti.com/automotive             |

| Amplifiers                   | amplifier.ti.com         | Communications and Telecom    | www.ti.com/communications         |

| Data Converters              | dataconverter.ti.com     | Computers and Peripherals     | www.ti.com/computers              |

| DLP® Products                | www.dlp.com              | Consumer Electronics          | www.ti.com/consumer-apps          |

| DSP                          | dsp.ti.com               | Energy and Lighting           | www.ti.com/energy                 |

| Clocks and Timers            | www.ti.com/clocks        | Industrial                    | www.ti.com/industrial             |

| Interface                    | interface.ti.com         | Medical                       | www.ti.com/medical                |

| Logic                        | logic.ti.com             | Security                      | www.ti.com/security               |

| Power Mgmt                   | power.ti.com             | Space, Avionics and Defense   | www.ti.com/space-avionics-defense |

| Microcontrollers             | microcontroller.ti.com   | Video and Imaging             | www.ti.com/video                  |

| RFID                         | www.ti-rfid.com          |                               |                                   |

| OMAP Applications Processors | www.ti.com/omap          | TI E2E Community              | e2e.ti.com                        |

| Wireless Connectivity        | www.ti.com/wirelessconne | ectivity                      |                                   |

Mailing Address: Texas Instruments, Post Office Box 655303, Dallas, Texas 75265 Copyright © 2014, Texas Instruments Incorporated