## **SN8P2711A**

**USER'S MANUAL**

Version 1.6

SN8P2711A

## **SONIX 8-Bit Micro-Controller**

SONIX reserves the right to make change without further notice to any products herein to improve reliability, function or design. SONIX does not assume any liability arising out of the application or use of any product or circuit described herein; neither does it convey any license under its patent rights nor the rights of others. SONIX products are not designed, intended, or authorized for us as components in systems intended, for surgical implant into the body, or other applications intended to support or sustain life, or for any other application in which the failure of the SONIX product could create a situation where personal injury or death may occur. Should Buyer purchase or use SONIX products for any such unintended or unauthorized application. Buyer shall indemnify and hold SONIX and its officers, employees, subsidiaries, affiliates and distributors harmless against all claims, cost, damages, and expenses, and reasonable attorney fees arising out of, directly or indirectly, any claim of personal injury or death associated with such unintended or unauthorized use even if such claim alleges that SONIX was negligent regarding the design or manufacture of the part.

## AMENDENT HISTORY

| Version | Date      | Description                                                                    |

|---------|-----------|--------------------------------------------------------------------------------|

| VER 0.1 | Jun. 2007 | First issue.                                                                   |

| VER 1.0 | Dec. 2010 | Add ADC internal reference voltage range.                                      |

| VER 1.1 | Aug. 2011 | Modify "Chapter1.4 PIN DESCRIPTIONS" description: P0.1/INT1 is Schmitt trigger |

|         |           | structure as input mode.                                                       |

| VER 1.2 | Dec. 2011 | Modify "ELECTRICAL CHARACTERICS" chapter operating temperature from 0~70℃ to   |

|         |           | -20~70℃.                                                                       |

| VER 1.3 | Dec. 2011 | Modify "ELECTRICAL CHARACTERICS" Chapter: IHRC frequency range and graphs.     |

| VER 1.4 | Apr. 2012 | Modify oscillator warm-up time of power down mode wake-up and others.          |

| VER 1.5 | Sep. 2012 | Modify "ELECTRICAL CHARACTERICS" chapter operating temperature from -10~70℃    |

|         |           | to -20~85℃ and others.                                                         |

| VER 1.6 | Feb. 2013 | Add Package Type: SN8P27113AA (MSOP10)                                         |

|         |           |                                                                                |

## **Table of Content**

|   | AMENDENT HISTORY                          | 2  |

|---|-------------------------------------------|----|

| 1 | PRODUCT OVERVIEW                          | 6  |

|   | .1 FEATURES                               | 6  |

|   | .2 SYSTEM BLOCK DIAGRAM                   | 7  |

|   | .3 PIN ASSIGNMENT                         | 8  |

|   | .4 PIN DESCRIPTIONS                       |    |

|   | .5 PIN CIRCUIT DIAGRAMS                   |    |

| 2 | CENTRAL PROCESSOR UNIT (CPU)              |    |

|   | 2.1 PROGRAM MEMORY (ROM)                  |    |

|   | 2.1.1 RESET VECTOR (0000H)                |    |

|   | 2.1.2 INTERRUPT VECTOR (0008H)            |    |

|   | 2.1.3 LOOK-UP TABLE DESCRIPTION           |    |

|   | 2.1.4 JUMP TABLE DESCRIPTION              |    |

|   | 2.1.5 CHECKSUM CALCULATION                |    |

|   | 2.1.5 CHECKSOM CALCULATION                |    |

|   | 2.2.1 SYSTEM REGISTER                     |    |

|   |                                           |    |

|   | 2.2.1.1 SYSTEM REGISTER TABLE             |    |

|   |                                           |    |

|   | 2.2.1.3 BIT DEFINITION of SYSTEM REGISTER |    |

|   | 2.2.2 ACCUMULATOR                         |    |

|   | 2.2.3 PROGRAM FLAG                        |    |

|   | 2.2.4 PROGRAM COUNTER                     |    |

|   | 2.2.5 Y, Z REGISTERS                      |    |

|   | 2.2.6 R REGISTER                          |    |

|   | 2.3 ADDRESSING MODE                       |    |

|   | 2.3.1 IMMEDIATE ADDRESSING MODE           |    |

|   | 2.3.2 DIRECTLY ADDRESSING MODE            |    |

|   | 2.3.3 INDIRECTLY ADDRESSING MODE          |    |

|   | 2.4 STACK OPERATION                       |    |

|   | 2.4.1 OVERVIEW                            |    |

|   | 2.4.2 STACK REGISTERS                     |    |

|   | 2.4.3 STACK OPERATION EXAMPLE             |    |

|   | 2.5 CODE OPTION TABLE                     |    |

|   | 2.5.1 Fcpu code option                    |    |

|   | 2.5.2 Reset_Pin code option               |    |

|   | 2.5.3 Security code option                |    |

|   | 2.5.4 Noise Filter code option            | 30 |

| 3 | RESET                                     | 31 |

|   | 3.1 OVERVIEW                              |    |

|   | 3.2 POWER ON RESET                        | 32 |

|   | 3.3 WATCHDOG RESET                        | 32 |

|   | 3.4 BROWN OUT RESET                       |    |

|   | 3.5 THE SYSTEM OPERATING VOLTAGE          | 33 |

|   | 3.6 LOW VOLTAGE DETECTOR (LVD)            |    |

|   | 3.7 BROWN OUT RESET IMPROVEMENT           | 35 |

|   | 3.8 EXTERNAL RESET                        | 36 |

|   | 3.9 EXTERNAL RESET CIRCUIT                | 36 |

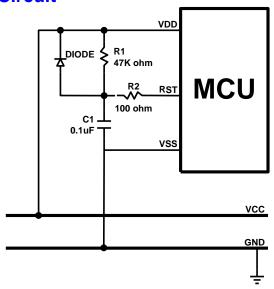

|   | 3.9.1 Simply RC Reset Circuit             |    |

|   | * *                                       |    |

|          | 3.9.2          | Diode & RC Reset Circuit                      |    |

|----------|----------------|-----------------------------------------------|----|

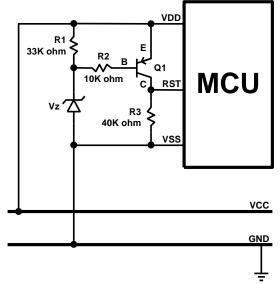

|          | 3.9.3          | Zener Diode Reset Circuit                     | 37 |

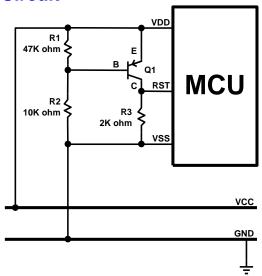

|          | 3.9.4          | Voltage Bias Reset Circuit                    |    |

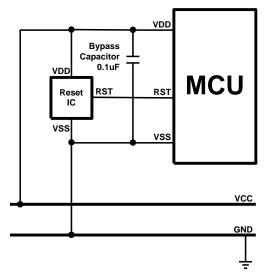

|          | 3.9.5          | External Reset IC                             |    |

| 4        |                | CM CLOCK                                      |    |

|          |                | VERVIEW                                       |    |

|          |                | PU (INSTRUCTION CYCLE)                        |    |

|          |                | OISE FILTER                                   |    |

|          |                | STEM HIGH-SPEED CLOCK                         |    |

|          | 4.4.1          | HIGH_CLK CODE OPTION                          |    |

|          | 4.4.2          | INTERNAL HIGH-SPEED OSCILLATOR RC TYPE (IHRC) |    |

|          | 4.4.3          | EXTERNAL HIGH-SPEED OSCILLATOR                |    |

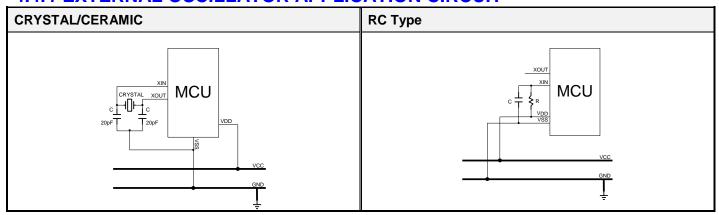

|          | 4.4.4          | EXTERNAL OSCILLATOR APPLICATION CIRCUIT       |    |

|          |                | STEM LOW-SPEED CLOCK                          |    |

|          |                | SCM REGISTER                                  |    |

|          |                | STEM CLOCK MEASUREMENT                        |    |

| <b>=</b> |                | YSTEM CLOCK TIMING<br>ZM OPERATION MODE       |    |

| Ð        |                | VERVIEW                                       |    |

|          |                | ORMAL MODE                                    |    |

|          |                | OW MODE                                       |    |

|          |                | OWER DOWN MODE                                |    |

|          |                | REEN MODE                                     |    |

|          |                | PERATING MODE CONTROL MACRO                   |    |

|          |                | AKEUP                                         |    |

|          | 5.7.1          | OVERVIEW                                      |    |

|          | 5.7.2          | WAKEUP TIME                                   |    |

| 6        | INTER          | RRUPT                                         |    |

|          |                | VERVIEW                                       |    |

|          | 6.2 IN         | TEN INTERRUPT ENABLE REGISTER                 | 52 |

|          | 6.3 IN         | TRQ INTERRUPT REQUEST REGISTER                | 53 |

|          | 6.4 GI         | E GLOBAL INTERRUPT OPERATION                  | 54 |

|          |                | JSH, POP ROUTINE                              |    |

|          |                | KTERNAL INTERRUPT OPERATION (INT0)            |    |

|          |                | T1 (P0.1) INTERRUPT OPERATION                 |    |

|          |                | CO INTERRUPT OPERATION                        |    |

|          |                | C1 INTERRUPT OPERATION                        |    |

|          |                | OC INTERRUPT OPERATION                        |    |

| _        |                | ULTI-INTERRUPT OPERATION                      |    |

| 7/       | _,             | RT                                            |    |

|          |                | VERVIEW                                       |    |

|          |                | O PORT MODE                                   |    |

|          |                | PULL UP REGISTER                              |    |

|          |                | O PORT DATA REGISTER                          |    |

| ø        |                | ORT 0/4 ADC SHARE PIN                         |    |

| Ø        |                | ATCHDOC TIMED                                 |    |

|          |                | ATCHDOG TIMER                                 |    |

|          |                | MER/COUNTER 0 (TC0)                           |    |

|          | 8.2.1          | OVERVIEWTC0 TIMER OPERATION                   |    |

|          | 8.2.2<br>8.2.3 | TC0 TIMER OPERATIONTC0M MODE REGISTER         |    |

|          | 8.2.3<br>8.2.4 | TC0X8, TC0GN FLAGS                            |    |

|          | 0.4.4          | ICUAO, ICUUN ILAUS                            |    |

| 8.2  |                                               |     |

|------|-----------------------------------------------|-----|

| 8.2  |                                               |     |

| 8.2  |                                               |     |

| 8.2  |                                               |     |

| 8.2  |                                               |     |

| 8.2  | 2.10 TC0 TIMER OPERATION EXPLAME              | 79  |

| 8.3  | TIMER/COUNTER 1 (TC1)                         | 81  |

| 8.3  |                                               |     |

| 8.3  | 3.2 TC1 TIMER OPERATION                       | 82  |

| 8.3  | 3.3 TC1M MODE REGISTER                        | 83  |

| 8.3  | 3.4 TC1X8 FLAG                                | 84  |

| 8.3  | 3.5 TC1C COUNTING REGISTER                    | 84  |

| 8.3  |                                               |     |

| 8.3  | 3.7 TC1 EVENT COUNTER FUNCTION                | 86  |

| 8.3  | 3.8 TC1 CLOCK FREQUENCY OUTPUT (BUZZER)       | 86  |

| 8.3  |                                               |     |

| 8.3  | 3.10 TC1 TIMER OPERATION EXPLAME              |     |

| 9 5+ | 1 CHANNEL ANALOG TO DIGITAL CONVERTER         | 91  |

| 9.1  | OVERVIEW                                      |     |

| 9.2  | ADC MODE REGISTER                             |     |

| 9.3  | ADC DATA BUFFER REGISTERS                     |     |

| 9.4  | ADC REFERENCE VOLTAGE REGISTER                |     |

| 9.5  | ADC OPERATION DESCRIPTION AND NOTIC           |     |

| 9.5  |                                               |     |

| 9.5  |                                               |     |

| 9.5  |                                               |     |

| 9.6  | ADC OPERATION EXAMLPE                         |     |

| 9.7  | ADC APPLICATION CIRCUIT                       |     |

|      | INSTRUCTION TABLE                             |     |

|      | ELECTRICAL CHARACTERISTIC                     |     |

| 11.1 |                                               |     |

| 11.1 | ELECTRICAL CHARACTERISTIC                     |     |

|      | CHARACTERISTIC GRAPHS                         |     |

|      | DEVELOPMENT TOOL                              |     |

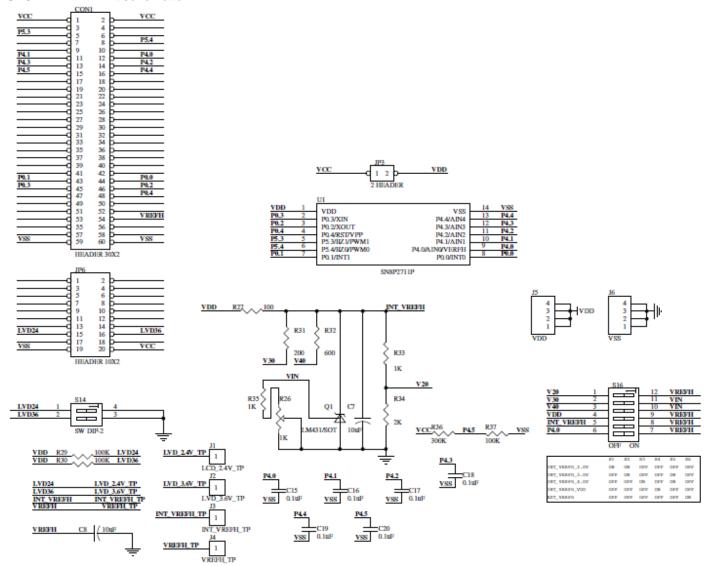

| 12.1 |                                               |     |

|      | ICE AND EV-KIT APPLICATION NOTIC              |     |

|      | OTP PROGRAMMING PIN                           |     |

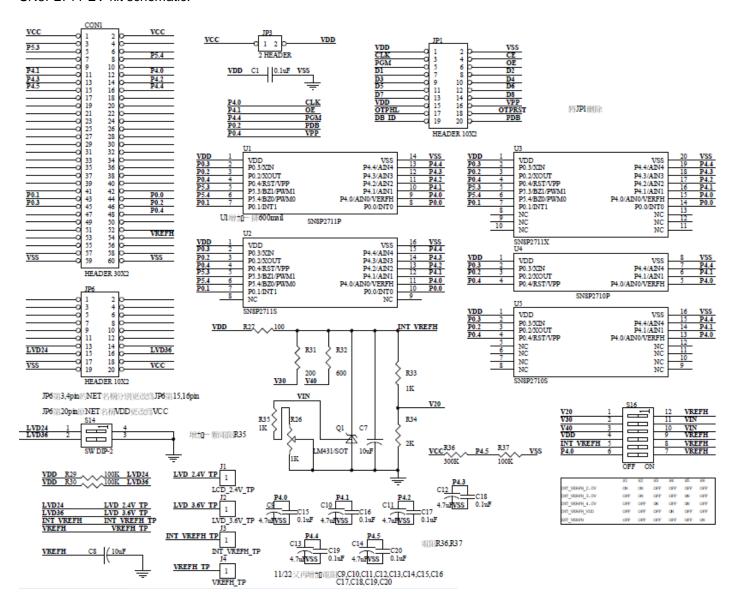

| 13.1 | WRITER TRANSITION BOARD SOCKET PIN ASSIGNMENT |     |

|      | PROGRAMMING PIN MAPPING:                      |     |

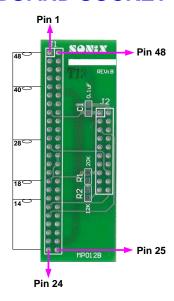

|      | MARKING DEFINITION                            |     |

| 14.1 | INTRODUCTION                                  |     |

|      | MARKING INDETIFICATION SYSTEM                 |     |

| 14.2 |                                               |     |

| 14.3 | MARKING EXAMPLE                               |     |

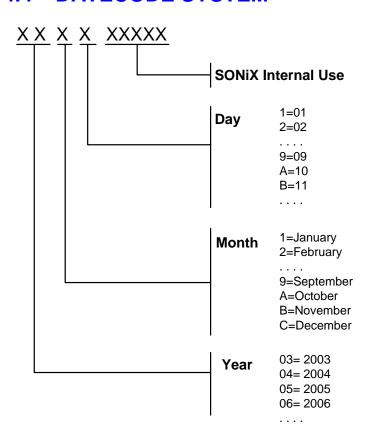

| 14.4 | DATECODE SYSTEM                               |     |

|      | PACKAGE INFORMATION                           |     |

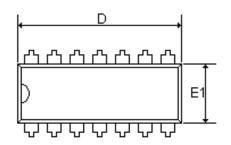

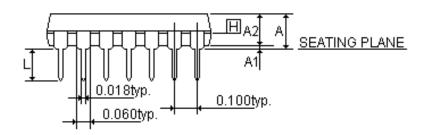

| 15.1 | P-DIP 14 PIN                                  |     |

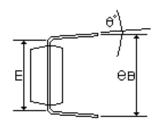

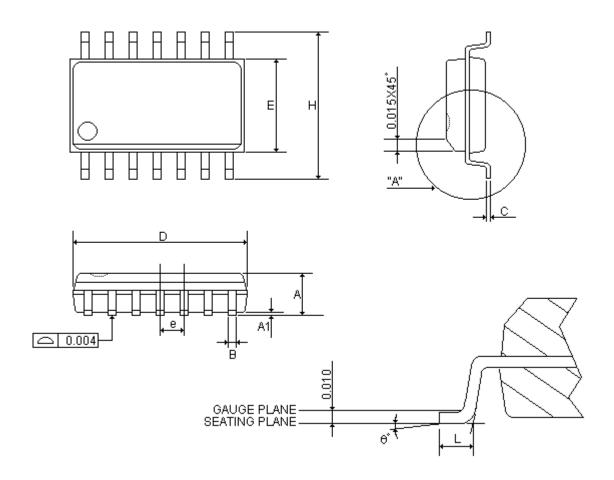

| 15.2 | SOP 14 PIN                                    |     |

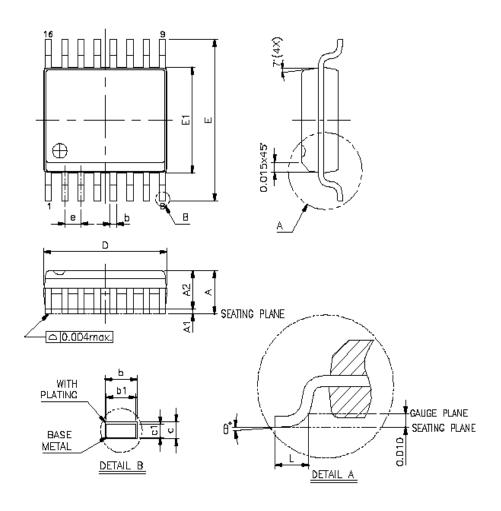

| 15.3 | SSOP 16 PIN                                   |     |

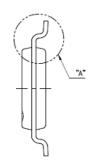

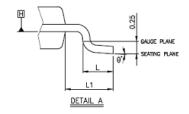

| 15.4 | MSOP 10 PIN                                   | 115 |

# 1 PRODUCT OVERVIEW

## 1.1 FEATURES

♦ Memory configuration

ROM size: 1K \* 16 bits. RAM size: 64 \* 8 bits.

♦ 4 levels stack buffer.

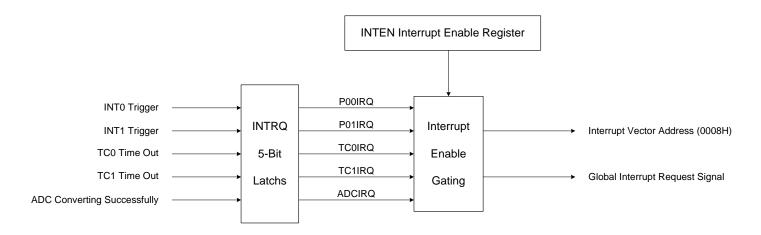

♦ 5 interrupt sources

3 internal interrupts: TC0, TC1, ADC 2 external interrupt: INT0, INT1

♦ I/O pin configuration

Bi-directional: P0, P4, P5.

Input only: P0.4.

Pull-up resisters: P0, P4, P5. Wakeup: P0 level change. ADC input pin: P4.0~P4.4. External Interrupt trigger edge:

P0.0 controlled by PEDGE register. P0.1 is falling edge trigger only.

3-Level LVD

Reset system and power monitor.

♦ Powerful instructions

Instruction's length is one word.

Most of instructions are one cycle only.

All ROM area JMP/CALL instruction.

All ROM area lookup table function (MOVC).

♦ Fcpu (Instruction cycle)

Fcpu = Fosc/1, Fosc/2, Fosc/4, Fosc/8, Fosc/16,

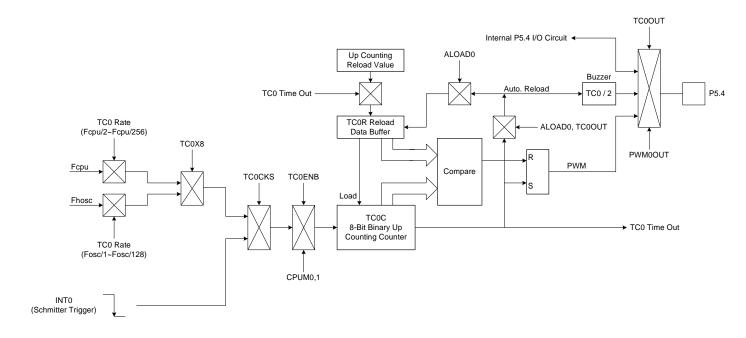

Two 8-bit Timer/Counter

One 8-bit timer with external event counter, Buzzer0 and PWM0. (TC0). One 8-bit timer with external event counter, Buzzer1 and PWM1. (TC1).

◆ 5+1 channel 12-bit SAR ADC.

Five external ADC input

One internal battery measurement

Internal AD reference voltage (VDD, 4V, 3V, 2V).

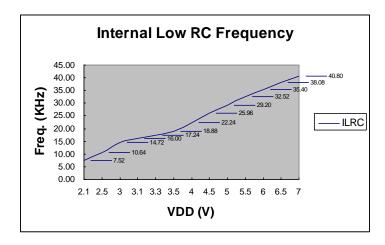

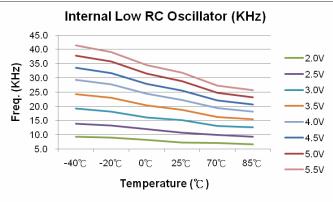

On chip watchdog timer and clock source is Internal low clock RC type (16KHz(3V), 32KHz(5V))

♦ 4 system clocks

External high clock: RC type up to 10 MHz External high clock: Crystal type up to 16 MHz

Internal high clock: 16MHz RC type

Internal low clock: RC type 16KHz(3V), 32KHz(5V)

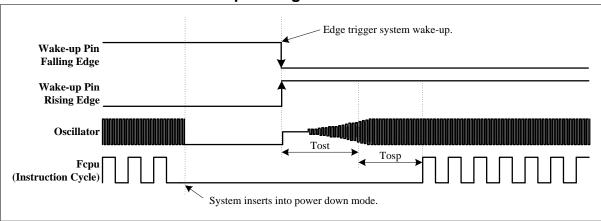

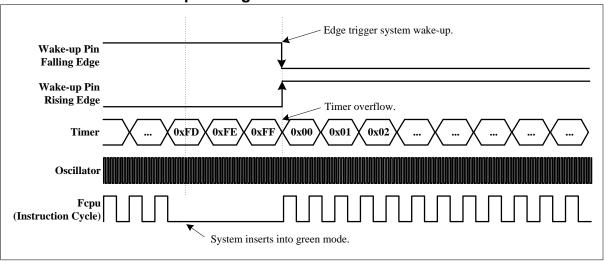

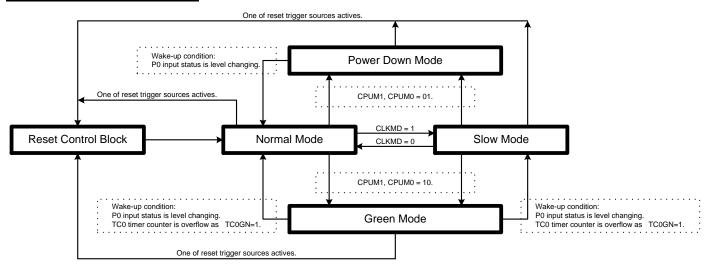

♦ 4 operating modes

Normal mode: Both high and low clock active

Slow mode: Low clock only.

Sleep mode: Both high and low clock stop Green mode: Periodical wakeup by TC0 timer

♦ Package (Chip form support)

DIP 14 pin SOP 14 pin SSOP 16 pin

#### Features Selection Table

| CHIP      | ROM | RAM | Stack | Tin<br>TC0 | ner<br>TC1 | I/O | ADC | ADC<br>Int. Ref. | Green<br>Mode | PWM<br>Buzzer | Wake-up<br>Pin No. | Package      |

|-----------|-----|-----|-------|------------|------------|-----|-----|------------------|---------------|---------------|--------------------|--------------|

| SN8P2711A | 1K  | 64  | 4     | 100        | \ \/       | 12  | F.1 | \/               | Wiode         | Duzzei        | F III NO.          | DIP14/SOP14/ |

| SNOPZITIA | IN  | 04  | 4     | V          | V          | 12  | 5+1 | V                | V             |               | Э                  | SSOP16       |

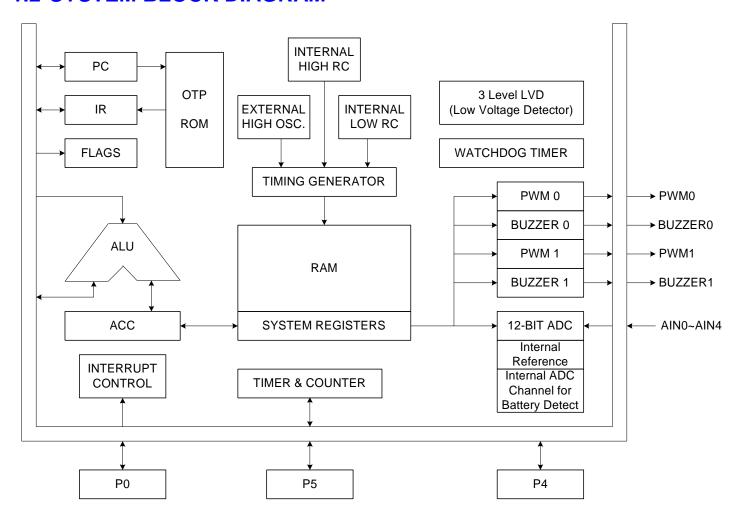

## 1.2 SYSTEM BLOCK DIAGRAM

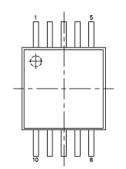

## 1.3 PIN ASSIGNMENT

SN8P2711AP (P-DIP 14 pins) SN8P2711AS (SOP 14 pins)

| VDD           | 1 | U | 14 | vss             |

|---------------|---|---|----|-----------------|

| P0.3/XIN      | 2 |   | 13 | P4.4/AIN4       |

| P0.2/XOUT     | 3 |   | 12 | P4.3/AIN3       |

| P0.4/RST/VPP  | 4 |   | 11 | P4.2/AIN2       |

| P5.3/BZ1/PWM1 | 5 |   | 10 | P4.1/AIN1       |

| P5.4/BZ0/PWM0 | 6 |   | 9  | P4.0/AIN0/VREFH |

| P0.1/INT1     | 7 |   | 8  | P0.0/INT0       |

SN8P2711AP SN8P2711AS

## SN8P2711AX (SSOP 16 pins)

| VDD           | 1 | U | 16 | vss             |  |  |  |

|---------------|---|---|----|-----------------|--|--|--|

| P0.3/XIN      | 2 |   | 15 | P4.4/AIN4       |  |  |  |

| P0.2/XOUT     | 3 |   | 14 | P4.3/AIN3       |  |  |  |

| P0.4/RST/VPP  | 4 |   | 13 | P4.2/AIN2       |  |  |  |

| P5.3/BZ1/PWM1 | 5 |   | 12 | P4.1/AIN1       |  |  |  |

| P5.4/BZ0/PWM0 | 6 |   | 11 | P4.0/AIN0/VREFH |  |  |  |

| P0.1/INT1     | 7 |   | 10 | P0.0/INT0       |  |  |  |

| NC 8 9 NC     |   |   |    |                 |  |  |  |

| SN8P2711AX    |   |   |    |                 |  |  |  |

## **SN8P27113AA (MSOP 10 pins)**

| <del>-</del>  | SN8 | 3P2711 | 3AA | _               |

|---------------|-----|--------|-----|-----------------|

| P5.4/BZ0/PWM0 | 5   |        | 6   | P4.0/AIN0/VREFH |

| P5.3/BZ1/PWM1 | 4   |        |     | P4.1/AIN1       |

| P0.4/RST/VPP  | 3   |        | 8   | P4.2/AIN2       |

| P0.2/XOUT     | 2   |        | 9   | P4.4/AIN4       |

| VDD           | 1   | U      | 10  | VSS             |

|               |     |        |     |                 |

## 1.4 PIN DESCRIPTIONS

| PIN NAME            | TYPE | DESCRIPTION                                                                                  |  |  |  |

|---------------------|------|----------------------------------------------------------------------------------------------|--|--|--|

| VDD, VSS            | Р    | Power supply input pins for digital and analog circuit.                                      |  |  |  |

|                     |      | RST: System external reset input pin. Schmitt trigger structure, active "low", normal stay   |  |  |  |

|                     |      | to "high".                                                                                   |  |  |  |

| P0.4/RST/VPP        | I, P | VPP: OTP 12.3V power input pin in programming mode.                                          |  |  |  |

|                     |      | P0.4: Input only pin with Schmitt trigger structure and no pull-up resistor. Level change    |  |  |  |

|                     |      | wake-up.                                                                                     |  |  |  |

|                     |      | XIN: Oscillator input pin while external oscillator enable (crystal and RC).                 |  |  |  |

| P0.3/XIN            | I/O  | P0.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

|                     |      | Level change wake-up.                                                                        |  |  |  |

|                     |      | XOUT: Oscillator output pin while external crystal enable.                                   |  |  |  |

| P0.2/XOUT           | I/O  | P0.2: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

|                     |      | Level change wake-up.                                                                        |  |  |  |

|                     | I/O  | P0.0: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

| P0.0/INT0           |      | Level change wake-up.                                                                        |  |  |  |

|                     |      | INT0: External interrupt 0 input pin.                                                        |  |  |  |

|                     |      | P0.1: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

| P0.1/INT1           | I/O  | Level change wake-up.                                                                        |  |  |  |

|                     |      | INT1: External interrupt 1 input pin.                                                        |  |  |  |

|                     |      | P4.0: Bi-direction pin. No Schmitt trigger structure. Built-in pull-up resisters.            |  |  |  |

| P4.0/AIN0/AVREFH    | I/O  | AIN0: ADC analog input pin.                                                                  |  |  |  |

|                     |      | AVREFH: ADC reference high voltage input pin.                                                |  |  |  |

| P4.[4:1]/AIN[4:1]   | I/O  | P4.[4:1]: Bi-direction pin. No Schmitt trigger structure. Built-in pull-up resisters.        |  |  |  |

| 1 4.[4.1]/////[4.1] | 1/ 0 | AIN[4:1]: ADC analog input pin.                                                              |  |  |  |

|                     |      | P5.3: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

| P5.3/PWM1/BZ1       | I/O  | PWM1: PWM output pin.                                                                        |  |  |  |

|                     |      | BZ1: Buzzer TC1/2 output pin.                                                                |  |  |  |

|                     |      | P5.4: Bi-direction pin. Schmitt trigger structure as input mode. Built-in pull-up resisters. |  |  |  |

| P5.4/PWM0/BZ0       | I/O  | PWM0: PWM output pin.                                                                        |  |  |  |

|                     |      | BZ0: Buzzer TC0/2 output pin.                                                                |  |  |  |

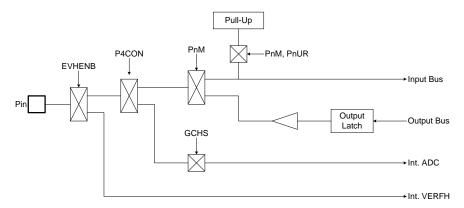

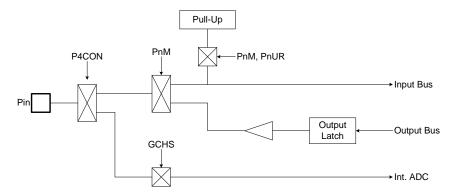

## 1.5 PIN CIRCUIT DIAGRAMS

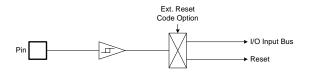

## • Reset shared pin structure:

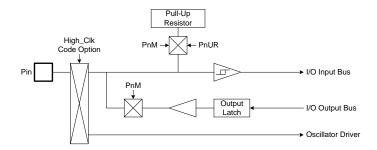

## Oscillator shared pin structure:

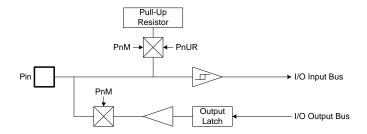

#### GPIO structure:

## • ADC shared pin with reference high voltage structure:

#### ADC shared pin structure:

# 2

# **CENTRAL PROCESSOR UNIT (CPU)**

## 2.1 PROGRAM MEMORY (ROM)

#### **☞** 1K words ROM

|                                                      | ROM                  | _                                            |

|------------------------------------------------------|----------------------|----------------------------------------------|

| 0000H                                                | Reset vector         | User reset vector Jump to user start address |

| 0001H                                                |                      |                                              |

|                                                      | General purpose area |                                              |

| 0007H                                                |                      |                                              |

| H8000                                                | Interrupt vector     | User interrupt vector                        |

| 0009H<br>:<br>:<br>000FH<br>0010H<br>0011H<br>:<br>: | General purpose area | User program                                 |

| 03FCH                                                |                      | End of user program                          |

| 03FDH<br>03FEH<br>03FFH                              | Reserved             |                                              |

The ROM includes Reset vector, Interrupt vector, General purpose area and Reserved area. The Reset vector is program beginning address. The Interrupt vector is the head of interrupt service routine when any interrupt occurring. The General purpose area is main program area including main loop, sub-routines and data table.

START:

## 2.1.1 RESET VECTOR (0000H)

A one-word vector address area is used to execute system reset.

- Power On Reset (NT0=1, NPD=0).

- Watchdog Reset (NT0=0, NPD=0).

- External Reset (NT0=1, NPD=1).

After power on reset, external reset or watchdog timer overflow reset, then the chip will restart the program from address 0000h and all system registers will be set as default values. It is easy to know reset status from NT0, NPD flags of PFLAG register. The following example shows the way to define the reset vector in the program memory.

; End of program

#### Example: Defining Reset Vector

**ENDP**

| ORG<br>JMP | 0<br>START | ; 0000H<br>; Jump to user program address.           |

|------------|------------|------------------------------------------------------|

| ORG        | 10H        | ; 0010H, The head of user program.<br>; User program |

|            |            |                                                      |

## 2.1.2 INTERRUPT VECTOR (0008H)

A 1-word vector address area is used to execute interrupt request. If any interrupt service executes, the program counter (PC) value is stored in stack buffer and jump to 0008h of program memory to execute the vectored interrupt. Users have to define the interrupt vector. The following example shows the way to define the interrupt vector in the program memory.

Note: "PUSH", "POP" instructions save and load ACC/PFLAG without (NT0, NPD). PUSH/POP buffer is a unique buffer and only one level.

> Example: Defining Interrupt Vector. The interrupt service routine is following ORG 8.

.CODE

ORG 0 ; 0000H

JMP START ; Jump to user program address.

• • •

ORG 8 ; Interrupt vector.

PUSH ; Save ACC and PFLAG register to buffers.

• •

POP ; Load ACC and PFLAG register from buffers.

RETI ; End of interrupt service routine

. . .

START: ; The head of user program.

.. ; User program

JMP START ; End of user program

• • •

ENDP ; End of program

Example: Defining Interrupt Vector. The interrupt service routine is following user program.

.CODE

ORG 0 ; 0000H

JMP START ; Jump to user program address.

ORG 8 ; Interrupt vector.

JMP MY\_IRQ ; 0008H, Jump to interrupt service routine address.

ORG 10H

START: ; 0010H, The head of user program.

; User program.

•••

JMP START ; End of user program.

MY\_IRQ: ;The head of interrupt service routine.

PUSH ; Save ACC and PFLAG register to buffers.

• • •

POP ; Load ACC and PFLAG register from buffers.

RETI ; End of interrupt service routine.

...

ENDP ; End of program.

- \* Note: It is easy to understand the rules of SONIX program from demo programs given above. These points are as following:

- 1. The address 0000H is a "JMP" instruction to make the program starts from the beginning.

- 2. The address 0008H is interrupt vector.

- 3. User's program is a loop routine for main purpose application.

#### 2.1.3 LOOK-UP TABLE DESCRIPTION

In the ROM's data lookup function, Y register is pointed to middle byte address (bit 8~bit 15) and Z register is pointed to low byte address (bit 0~bit 7) of ROM. After MOVC instruction executed, the low-byte data will be stored in ACC and high-byte data stored in R register.

> Example: To look up the ROM data located "TABLE1".

$\begin{array}{lll} B0MOV & Y, \#TABLE1\$M & ; To set lookup table1's middle address \\ B0MOV & Z, \#TABLE1\$L & ; To set lookup table1's low address. \\ MOVC & ; To lookup data, R = 00H, ACC = 35H \end{array}$

; Increment the index address for next address.

INCMS Z ; Z+1 JMP @F ; Z is not overflow. INCMS Y ; Z overflow (FFH  $\rightarrow$  00),  $\rightarrow$  Y=Y+1 NOP :

@@: MOVC ; To lookup data, R = 51H, ACC = 05H.

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H

DW 2012H

Note: The Y register will not increase automatically when Z register crosses boundary from 0xFF to 0x00. Therefore, user must be take care such situation to avoid look-up table errors. If Z register is overflow, Y register must be added one. The following INC\_YZ macro shows a simple method to process Y and Z registers automatically.

> Example: INC\_YZ macro.

INC\_YZ MACRO

INCMS Z : Z+1

JMP @F ; Not overflow

INCMS Y ; Y+1

NOP ; Not overflow

@ @:

ENDM

#### Example: Modify above example by "INC\_YZ" macro.

BOMOV Y, #TABLE1\$M ; To set lookup table1's middle address BOMOV Z, #TABLE1\$L ; To set lookup table1's low address. MOVC ; To lookup data, R = 00H, ACC = 35H

INC\_YZ ; Increment the index address for next address.

@@: MOVC ; To lookup data, R = 51H, ACC = 05H.

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

...

The other example of look-up table is to add Y or Z index register by accumulator. Please be careful if "carry" happen.

#### Example: Increase Y and Z register by B0ADD/ADD instruction.

B0MOV Y, #TABLE1\$M ; To set lookup table's middle address. B0MOV Z, #TABLE1\$L ; To set lookup table's low address.

B0MOV A, BUF ; Z = Z + BUF. B0ADD Z, A

B0BTS1 FC ; Check the carry flag.

JMP GETDATA ; FC = 0 INCMS Y ; FC = 1. Y+1.

NOP

MOVC ; To lookup data. If BUF = 0, data is 0x0035

; If BUF = 1, data is 0x5105 ; If BUF = 2, data is 0x2012

---

**GETDATA:**

TABLE1: DW 0035H ; To define a word (16 bits) data.

DW 5105H DW 2012H

...

## 2.1.4 JUMP TABLE DESCRIPTION

The jump table operation is one of multi-address jumping function. Add low-byte program counter (PCL) and ACC value to get one new PCL. If PCL is overflow after PCL+ACC, PCH adds one automatically. The new program counter (PC) points to a series jump instructions as a listing table. It is easy to make a multi-jump program depends on the value of the accumulator (A).

- Note: PCH only support PC up counting result and doesn't support PC down counting. When PCL is carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL-ACC, PCH keeps value and not change.

- Example: Jump table.

```

ORG

0X0100

; The jump table is from the head of the ROM boundary

BOADD

PCL, A

; PCL = PCL + ACC, PCH + 1 when PCL overflow occurs.

JMP

A0POINT

; ACC = 0, jump to A0POINT

JMP

A1POINT

; ACC = 1, jump to A1POINT

JMP

A2POINT

; ACC = 2, jump to A2POINT

JMP

A3POINT

; ACC = 3, jump to A3POINT

```

SONIX provides a macro for safe jump table function. This macro will check the ROM boundary and move the jump table to the right position automatically. The side effect of this macro maybe wastes some ROM size.

> Example: If "jump table" crosses over ROM boundary will cause errors.

```

@JMP_A MACRO VAL

IF (($+1)!& 0XFF00)!!= (($+(VAL))!& 0XFF00)

JMP ($|0XFF)

ORG ($|0XFF)

ENDIF

B0ADD PCL, A

ENDM

```

- Note: "VAL" is the number of the jump table listing number.

- Example: "@JMP A" application in SONIX macro file called "MACRO3.H".

```

A, BUF0

; "BUF0" is from 0 to 4.

B0MOV

@JMP_A

; The number of the jump table listing is five.

5

JMP

A0POINT

; ACC = 0, jump to A0POINT

JMP

A1POINT

; ACC = 1, jump to A1POINT

JMP

A2POINT

; ACC = 2, jump to A2POINT

JMP

; ACC = 3, jump to A3POINT

A3POINT

JMP

A4POINT

; ACC = 4, jump to A4POINT

```

If the jump table position is across a ROM boundary (0x00FF~0x0100), the "@JMP\_A" macro will adjust the jump table routine begin from next RAM boundary (0x0100).

## > Example: "@JMP\_A" operation.

## ; Before compiling program.

| <b>ROM</b> | address |

|------------|---------|

|------------|---------|

|        | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|--------|--------|---------|-------------------------------------------------|

|        | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X00FD | JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X00FE | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X00FF | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0100 | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0101 | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

#### ; After compiling program.

#### ROM address

| I COM addices |        |         |                                                 |

|---------------|--------|---------|-------------------------------------------------|

|               | B0MOV  | A, BUF0 | ; "BUF0" is from 0 to 4.                        |

|               | @JMP_A | 5       | ; The number of the jump table listing is five. |

| 0X0100        | JMP    | A0POINT | ; ACC = 0, jump to A0POINT                      |

| 0X0101        | JMP    | A1POINT | ; ACC = 1, jump to A1POINT                      |

| 0X0102        | JMP    | A2POINT | ; ACC = 2, jump to A2POINT                      |

| 0X0103        | JMP    | A3POINT | ; ACC = 3, jump to A3POINT                      |

| 0X0104        | JMP    | A4POINT | ; ACC = 4, jump to A4POINT                      |

|               |        |         |                                                 |

## 2.1.5 CHECKSUM CALCULATION

The last ROM address are reserved area. User should avoid these addresses (last address) when calculate the Checksum value.

> Example: The demo program shows how to calculated Checksum from 00H to the end of user's code.

|               | MOV<br>B0MOV<br>MOV<br>B0MOV<br>CLR<br>CLR | A,#END_USER_CODE\$L<br>END_ADDR1, A<br>A,#END_USER_CODE\$M<br>END_ADDR2, A<br>Y<br>Z | ; Save low end address to end_addr1<br>; Save middle end address to end_addr2<br>; Set Y to 00H<br>; Set Z to 00H         |

|---------------|--------------------------------------------|--------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------|

| @@:           | MOVC                                       |                                                                                      |                                                                                                                           |

|               | B0BSET<br>ADD<br>MOV                       | FC<br>DATA1, A<br>A, R                                                               | ; Clear C flag<br>; Add A to Data1                                                                                        |

|               | ADC                                        | DATA2, A                                                                             | ; Add R to Data2                                                                                                          |

| AAA:          | JMP                                        | END_CHECK                                                                            | ; Check if the YZ address = the end of code                                                                               |

|               | INCMS<br>JMP<br>JMP                        | @B                                                                                   | ; Z=Z+1<br>; If Z != 00H calculate to next address<br>; If Z = 00H increase Y                                             |

| END_CHECK:    | MOV                                        | A END ADDD4                                                                          |                                                                                                                           |

|               | MOV<br>CMPRS<br>JMP<br>MOV                 | A, END_ADDR1<br>A, Z<br>AAA<br>A, END_ADDR2                                          | ; Check if Z = low end address<br>; If Not jump to checksum calculate                                                     |

|               | CMPRS<br>JMP<br>JMP                        | A, Y<br>AAA<br>CHECKSUM_END                                                          | ; If Yes, check if Y = middle end address<br>; If Not jump to checksum calculate<br>; If Yes checksum calculated is done. |

| Y_ADD_1:      |                                            |                                                                                      |                                                                                                                           |

|               | INCMS<br>NOP                               | Υ                                                                                    | ; Increase Y                                                                                                              |

|               | JMP                                        | @B                                                                                   | ; Jump to checksum calculate                                                                                              |

| CHECKSUM_END: |                                            |                                                                                      |                                                                                                                           |

END\_USER\_CODE:

; Label of program end

## 2.2 DATA MEMORY (RAM)

#### 64 X 8-bit RAM

|        | Address           | RAM Location         | ]                                                       |

|--------|-------------------|----------------------|---------------------------------------------------------|

|        | 000h              |                      | RAM Bank 0                                              |

|        | "                 | General Purpose Area |                                                         |

| BANK 0 | 03Fh<br>080h<br>" | System Register      | 080h~0FFh of Bank 0 store system registers (128 bytes). |

|        | 0FFh              |                      | End of Bank 0                                           |

The 64-byte general purpose RAM is in Bank 0. Sonix provides "Bank 0" type instructions (e.g. b0mov, b0add, b0bts1, b0bset...) to control Bank 0 RAM in non-zero RAM bank condition directly.

#### 2.2.1 SYSTEM REGISTER

#### 2.2.1.1 SYSTEM REGISTER TABLE

|   | 0    | 1   | 2   | 3   | 4    | 5    | 6     | 7   | 8     | 9     | Α     | В     | С     | D     | Е     | F     |

|---|------|-----|-----|-----|------|------|-------|-----|-------|-------|-------|-------|-------|-------|-------|-------|

| 8 | -    | =   | R   | Z   | Y    | -    | PFLAG | -   | -     | -     | -     | -     | -     | -     | -     | -     |

| 9 | -    | =   | -   | -   | -    |      | -     | -   | -     | -     | -     | i     | -     | -     | -     | -     |

| Α | -    | -   | -   | -   | -    | ı    | -     | -   | -     | -     | -     | i     | -     | -     | P4CON | VREFH |

| В | -    | ADM | ADB | ADR |      |      | -     | -   | P0M   | -     | -     | i     | -     | -     | -     | PEDGE |

| С | -    | =   | =   | -   | P4M  | P5M  | -     | -   | INTRQ | INTEN | OSCM  | -     | WDTR  | TC0R  | PCL   | PCH   |

| D | P0   | -   | -   | -   | P4   | P5   | -     | -   | TOM   | -     | TC0M  | TC0C  | TC1M  | TC1C  | TC1R  | STKP  |

| Ε | P0UR | =   | =   | -   | P4UR | P5UR | -     | @YZ | -     | -     | -     | ı     | -     | -     | -     | -     |

| F |      |     |     |     |      |      |       |     | STK3L | STK3H | STK2L | STK2H | STK1L | STK1H | STK0L | STK0H |

#### 2.2.1.2 SYSTEM REGISTER DESCRIPTION

R = Working register and ROM look-up data buffer.

PFLAG = Special flag register.

VREFH = ADC reference voltage control register.

ADB = ADC data buffer.

PEDGE = P0.0 edge direction register.

INTEN = Interrupt enable register.

WDTR = Watchdog timer clear register.

Pn = Port n data buffer.

PCH, PCL = Program counter.

TC0M = TC0 mode register.

TC0R = TC0 auto-reload data buffer.

TC1C = TC1 counting register.

@YZ = RAM YZ indirect addressing index pointer.

STK0~STK3 = Stack 0 ~ stack 3 buffer.

Y, Z = Working, @YZ and ROM addressing register.

P4CON = P4 configuration register.

ADM = ADC mode register.

ADR = ADC resolution select register.

INTRQ = Interrupt request register.

OSCM = Oscillator mode register.

PnM = Port n input/output mode register.

PnUR = Port n pull-up resister control register.

T0M = T0 mode register.

TC0C = TC0 counting register.

TC1M = TC1 mode register.

TC1R = TC1 auto-reload data buffer.

STKP = Stack pointer buffer.

## 2.2.1.3 BIT DEFINITION of SYSTEM REGISTER

| Address | Bit7   | Bit6     | Bit5     | Bit4     | Bit3   | Bit2   | Bit1   | Bit0    | R/W | Remarks |

|---------|--------|----------|----------|----------|--------|--------|--------|---------|-----|---------|

| 082H    | RBIT7  | RBIT6    | RBIT5    | RBIT4    | RBIT3  | RBIT2  | RBIT1  | RBIT0   | R/W | R       |

| 083H    | ZBIT7  | ZBIT6    | ZBIT5    | ZBIT4    | ZBIT3  | ZBIT2  | ZBIT1  | ZBIT0   | R/W | Z       |

| 084H    | YBIT7  | YBIT6    | YBIT5    | YBIT4    | YBIT3  | YBIT2  | YBIT1  | YBIT0   | R/W | Y       |

| 086H    | NT0    | NPD      | LVD36    | LVD24    |        | С      | DC     | Z       | R/W | PFLAG   |

| 0AEH    |        |          |          | P4CON4   | P4CON3 | P4CON2 | P4CON1 | P4CON0  | W   | P4CON   |

| 0AFH    | EVHENB |          |          |          |        |        | VHS1   | VHS0    | R/W | VREFH   |

| 0B1H    | ADENB  | ADS      | EOC      | GCHS     |        | CHS2   | CHS1   | CHS0    | R/W | ADM     |

| 0B2H    | ADB11  | ADB10    | ADB9     | ADB8     | ADB7   | ADB6   | ADB5   | ADB4    | R   | ADB     |

| 0B3H    |        | ADCKS1   |          | ADCKS0   | ADB3   | ADB2   | ADB1   | ADB0    | R/W | ADR     |

| 0B8H    |        |          |          |          | P03M   | P02M   | P01M   | P00M    | R/W | P0M     |

| 0BFH    |        |          |          | P00G1    | P00G0  |        |        |         | R/W | PEDGE   |

| 0C4H    |        |          |          | P44M     | P43M   | P42M   | P41M   | P40M    | R/W | P4M     |

| 0C5H    |        |          |          | P54M     | P53M   |        |        |         | R/W | P5M     |

| 0C8H    | ADCIRQ | TC1IRQ   | TC0IRQ   |          |        |        | P01IRQ | P00IRQ  | R/W | INTRQ   |

| 0C9H    | ADCIEN | TC1IEN   | TC0IEN   |          |        |        | P01IEN | P00IEN  | R/W | INTEN   |

| 0CAH    |        |          |          | CPUM1    | CPUM0  | CLKMD  | STPHX  |         | R/W | OSCM    |

| 0CCH    | WDTR7  | WDTR6    | WDTR5    | WDTR4    | WDTR3  | WDTR2  | WDTR1  | WDTR0   | W   | WDTR    |

| 0CDH    | TC0R7  | TC0R6    | TC0R5    | TC0R4    | TC0R3  | TC0R2  | TC0R1  | TC0R0   | W   | TC0R    |

| 0CEH    | PC7    | PC6      | PC5      | PC4      | PC3    | PC2    | PC1    | PC0     | R/W | PCL     |

| 0CFH    |        |          |          |          |        |        | PC9    | PC8     | R/W | PCH     |

| 0D0H    |        |          |          | P04      | P03    | P02    | P01    | P00     | R/W | P0      |

| 0D4H    |        |          |          | P44      | P43    | P42    | P41    | P40     | R/W | P4      |

| 0D5H    |        |          |          | P54      | P53    |        |        |         | R/W | P5      |

| 0D8H    |        |          |          |          | TC1X8  | TC0X8  | TC0GN  |         | R/W | TOM     |

| 0DAH    | TC0ENB | TC0rate2 | TC0rate1 | TC0rate0 | TC0CKS | ALOAD0 | TC0OUT | PWM0OUT | R/W | TC0M    |

| 0DBH    | TC0C7  | TC0C6    | TC0C5    | TC0C4    | TC0C3  | TC0C2  | TC0C1  | TC0C0   | R/W | TC0C    |

| 0DCH    | TC1ENB | TC1rate2 | TC1rate1 | TC1rate0 | TC1CKS | ALOAD1 | TC1OUT | PWM1OUT | R/W | TC1M    |

| 0DDH    | TC1C7  | TC1C6    | TC1C5    | TC1C4    | TC1C3  | TC1C2  | TC1C1  | TC1C0   | R/W | TC1C    |

| 0DEH    | TC1R7  | TC1R6    | TC1R5    | TC1R4    | TC1R3  | TC1R2  | TC1R1  | TC1R0   | W   | TC1R    |

| 0DFH    | GIE    |          |          |          |        | STKPB2 | STKPB1 | STKPB0  | R/W | STKP    |

| 0E0H    |        |          |          |          | P03R   | P02R   | P01R   | P00R    | W   | P0UR    |

| 0E4H    |        |          |          | P44R     | P43R   | P42R   | P41R   | P40R    | W   | P4UR    |

| 0E5H    |        |          |          | P54R     | P53R   |        |        |         | W   | P5UR    |

| 0E7H    | @YZ7   | @YZ6     | @YZ5     | @YZ4     | @YZ3   | @YZ2   | @YZ1   | @YZ0    | R/W | @YZ     |

| 0F8H    | S3PC7  | S3PC6    | S3PC5    | S3PC4    | S3PC3  | S3PC2  | S3PC1  | S3PC0   | R/W | STK3L   |

| 0F9H    |        |          |          |          |        |        | S3PC9  | S3PC8   | R/W | STK3H   |

| 0FAH    | S2PC7  | S2PC6    | S2PC5    | S2PC4    | S2PC3  | S2PC2  | S2PC1  | S2PC0   | R/W | STK2L   |

| 0FBH    |        |          |          |          |        |        | S2PC9  | S2PC8   | R/W | STK2H   |

| 0FCH    | S1PC7  | S1PC6    | S1PC5    | S1PC4    | S1PC3  | S1PC2  | S1PC1  | S1PC0   | R/W | STK1L   |

| 0FDH    |        |          |          |          |        |        | S1PC9  | S1PC8   | R/W | STK1H   |

| 0FEH    | S0PC7  | S0PC6    | S0PC5    | S0PC4    | S0PC3  | S0PC2  | S0PC1  | S0PC0   | R/W | STK0L   |

| 0FFH    |        |          |          |          |        |        | S0PC9  | S0PC8   | R/W | STK0H   |

#### \* Note:

- 1. To avoid system error, make sure to put all the "0" and "1" as it indicates in the above table.

- 2. All of register names had been declared in SN8ASM assembler.

- 3. One-bit name had been declared in SN8ASM assembler with "F" prefix code.

- 4. "b0bset", "b0bclr", "bset", "bclr" instructions are only available to the "R/W" registers.

## 2.2.2 ACCUMULATOR

The ACC is an 8-bit data register responsible for transferring or manipulating data between ALU and data memory. If the result of operating is zero (Z) or there is carry (C or DC) occurrence, then these flags will be set to PFLAG register. ACC is not in data memory (RAM), so ACC can't be access by "B0MOV" instruction during the instant addressing mode.

| ➤ Ex | ample: | Read | and | write | ACC | value. |

|------|--------|------|-----|-------|-----|--------|

|------|--------|------|-----|-------|-----|--------|

; Read ACC data and store in BUF data memory.

MOV BUF, A

; Write a immediate data into ACC.

MOV A, #0FH

; Write ACC data from BUF data memory.

MOV A, BUF

; or

B0MOV A, BUF

The system doesn't store ACC and PFLAG value when interrupt executed. ACC and PFLAG data must be saved to other data memories. "PUSH", "POP" save and load ACC, PFLAG data into buffers.

> Example: Protect ACC and working registers.

INT\_SERVICE:

PUSH ; Save ACC and PFLAG to buffers.

. . .

POP ; Load ACC and PFLAG from buffers.

RETI ; Exit interrupt service vector

## 2.2.3 PROGRAM FLAG

The PFLAG register contains the arithmetic status of ALU operation, system reset status and LVD detecting status. NT0, NPD bits indicate system reset status including power on reset, LVD reset, reset by external pin active and watchdog reset. C, DC, Z bits indicate the result status of ALU operation. LVD24, LVD36 bits indicate LVD detecting power voltage status.

| 086H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG       | NT0   | NPD   | LVD36 | LVD24 | -     | С     | DC    | Z     |

| Read/Write  | R/W   | R/W   | R     | R     | -     | R/W   | R/W   | R/W   |

| After reset | -     | -     | 0     | 0     | -     | 0     | 0     | 0     |

Bit [7:6] NT0, NPD: Reset status flag.

| NT0 | NPD | Reset Status                |

|-----|-----|-----------------------------|

| 0   | 0   | Watch-dog time out          |

| 0   | 1   | Reserved                    |

| 1   | 0   | Reset by LVD                |

| 1   | 1   | Reset by external Reset Pin |

Bit 5 LVD36: LVD 3.6V operating flag and only support LVD code option is LVD\_H.

0 = Inactive (VDD > 3.6V).

$1 = Active (VDD \le 3.6V).$

Bit 4 LVD24: LVD 2.4V operating flag and only support LVD code option is LVD\_M.

0 = Inactive (VDD > 2.4V).

$1 = Active (VDD \le 2.4V).$

Bit 2 C: Carry flag

- 1 = Addition with carry, subtraction without borrowing, rotation with shifting out logic "1", comparison result ≥ 0.

- 0 = Addition without carry, subtraction with borrowing signal, rotation with shifting out logic "0", comparison result < 0.

- Bit 1 DC: Decimal carry flag

- 1 = Addition with carry from low nibble, subtraction without borrow from high nibble.

- 0 = Addition without carry from low nibble, subtraction with borrow from high nibble.

- Bit 0 **Z**: Zero flag

- 1 = The result of an arithmetic/logic/branch operation is zero.

- 0 = The result of an arithmetic/logic/branch operation is not zero.

- ★ Note: Refer to instruction set table for detailed information of C, DC and Z flags.

## 2.2.4 PROGRAM COUNTER

The program counter (PC) is a 10-bit binary counter separated into the high-byte 2 and the low-byte 8 bits. This counter is responsible for pointing a location in order to fetch an instruction for kernel circuit. Normally, the program counter is automatically incremented with each instruction during program execution.

Besides, it can be replaced with specific address by executing CALL or JMP instruction. When JMP or CALL instruction is executed, the destination address will be inserted to bit 0 ~ bit 9.

|       | Bit 15 | Bit 14 | Bit 13 | Bit 12 | Bit 11 | Bit 10 | Bit 9 | Bit 8 | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------|--------|--------|--------|--------|--------|--------|-------|-------|-------|-------|-------|-------|-------|-------|-------|-------|

| PC    | -      | -      | -      | -      | -      | -      | PC9   | PC8   | PC7   | PC6   | PC5   | PC4   | PC3   | PC2   | PC1   | PC0   |

| After | _      | _      | -      | _      | _      | _      | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

| reset | _      | _      | -      | -      | •      | _      | U     | U     | 0     | U     | 0     | 0     | 0     | 0     | 0     | O     |

|       | PCH    |        |        |        |        |        |       |       |       |       |       | P(    | CL    |       |       |       |

#### **ONE ADDRESS SKIPPING**

There are nine instructions (CMPRS, INCS, INCMS, DECS, DECMS, BTS0, BTS1, B0BTS0, B0BTS1) with one address skipping function. If the result of these instructions is true, the PC will add 2 steps to skip next instruction.

If the condition of bit test instruction is true, the PC will add 2 steps to skip next instruction.

**B0BTS1** FC ; To skip, if Carry\_flag = 1

JMP C0STEP ; Else jump to C0STEP.

. . .

COSTEP: NOP

B0MOV A, BUF0 ; Move BUF0 value to ACC. **B0BTS0** FZ ; To skip, if Zero flag = 0.

JMP C1STEP ; Else jump to C1STEP.

• • •

C1STEP: NOP

If the ACC is equal to the immediate data or memory, the PC will add 2 steps to skip next instruction.

CMPRS A, #12H ; To skip, if ACC = 12H.

JMP COSTEP ; Else jump to COSTEP.

• • •

COSTEP: NOP

If the destination increased by 1, which results overflow of 0xFF to 0x00, the PC will add 2 steps to skip next instruction.

**INCS** instruction:

INCS BUF0

JMP COSTEP ; Jump to COSTEP if ACC is not zero.

• • •

COSTEP: NOP

**INCMS** instruction:

INCMS BUF0

JMP COSTEP ; Jump to COSTEP if BUF0 is not zero.

. . .

COSTEP: NOP

If the destination decreased by 1, which results underflow of 0x01 to 0x00, the PC will add 2 steps to skip next instruction.

**DECS** instruction:

**DECS** BUF0

JMP COSTEP ; Jump to COSTEP if ACC is not zero.

• • •

COSTEP: NOP

**DECMS** instruction:

**DECMS** BUF0

JMP COSTEP ; Jump to COSTEP if BUF0 is not zero.

• • •

COSTEP: NOP

#### **MULTI-ADDRESS JUMPING**

Users can jump around the multi-address by either JMP instruction or ADD M, A instruction (M = PCL) to activate multi-address jumping function. Program Counter supports "ADD M,A", "ADC M,A" and "B0ADD M,A" instructions for carry to PCH when PCL overflow automatically. For jump table or others applications, users can calculate PC value by the three instructions and don't care PCL overflow problem.

Note: PCH only support PC up counting result and doesn't support PC down counting. When PCL is carry after PCL+ACC, PCH adds one automatically. If PCL borrow after PCL-ACC, PCH keeps value and not change.

#### Example: If PC = 0323H (PCH = 03H, PCL = 23H)

PC = 0323H

MOV A, #28H

B0MOV PCL, A ; Jump to address 0328H

. . .

; PC = 0328H

MOV A, #00H

B0MOV PCL, A ; Jump to address 0300H

...

## Example: If PC = 0323H (PCH = 03H, PCL = 23H)

PC = 0323H

B0ADD PCL, A ; PCL = PCL + ACC, the PCH cannot be changed. JMP A0POINT ; If ACC = 0, jump to A0POINT

JMP A1POINT ; If ACC = 0, jump to A0POINT

JMP A1POINT ; ACC = 1, jump to A1POINT

JMP A2POINT ; ACC = 2, jump to A2POINT

JMP A3POINT ; ACC = 3, jump to A3POINT

...

## 2.2.5 Y, Z REGISTERS

The Y and Z registers are the 8-bit buffers. There are three major functions of these registers.

- Can be used as general working registers

- Can be used as RAM data pointers with @YZ register

- Can be used as ROM data pointer with the MOVC instruction for look-up table

| 084H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Υ           | YBIT7 | YBIT6 | YBIT5 | YBIT4 | YBIT3 | YBIT2 | YBIT1 | YBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

| 083H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| Z           | ZBIT7 | ZBIT6 | ZBIT5 | ZBIT4 | ZBIT3 | ZBIT2 | ZBIT1 | ZBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

Example: Uses Y, Z register as the data pointer to access data in the RAM address 025H of bank0.

B0MOV Y, #00H ; To set RAM bank 0 for Y register B0MOV Z, #25H ; To set location 25H for Z register

B0MOV A, @YZ ; To read a data into ACC

> Example: Uses the Y, Z register as data pointer to clear the RAM data.

B0MOV Y, #0; Y = 0, bank 0

BOMOV Z, #07FH ; Z = 7FH, the last address of the data memory area

CLR\_YZ\_BUF:

CLR @YZ ; Clear @YZ to be zero

DECMS Z; Z - 1, if Z = 0, finish the routine

JMP CLR\_YZ\_BUF ; Not zero

CLR @YZ

END\_CLR: ; End of clear general purpose data memory area of bank 0

. . .

## 2.2.6 R REGISTER

R register is an 8-bit buffer. There are two major functions of the register.

- Can be used as working register

- For store high-byte data of look-up table

(MOVC instruction executed, the high-byte data of specified ROM address will be stored in R register and the

low-byte data will be stored in ACC).

| 082H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| R           | RBIT7 | RBIT6 | RBIT5 | RBIT4 | RBIT3 | RBIT2 | RBIT1 | RBIT0 |

| Read/Write  | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | -     | -     |

Note: Please refer to the "LOOK-UP TABLE DESCRIPTION" about R register look-up table application.

## 2.3 ADDRESSING MODE

## 2.3.1 IMMEDIATE ADDRESSING MODE

The immediate addressing mode uses an immediate data to set up the location in ACC or specific RAM.

> Example: Move the immediate data 12H to ACC.

MOV A, #12H ; To set an immediate data 12H into ACC.

Example: Move the immediate data 12H to R register.

BOMOV R, #12H ; To set an immediate data 12H into R register.

Note: In immediate addressing mode application, the specific RAM must be 0x80~0x87 working register.

#### 2.3.2 DIRECTLY ADDRESSING MODE

The directly addressing mode moves the content of RAM location in or out of ACC.

> Example: Move 0x12 RAM location data into ACC.

B0MOV A, 12H ; To get a content of RAM location 0x12 of bank 0 and save in

ACC.

Example: Move ACC data into 0x12 RAM location.

B0MOV 12H, A ; To get a content of ACC and save in RAM location 12H of

bank 0

#### 2.3.3 INDIRECTLY ADDRESSING MODE

The indirectly addressing mode is to access the memory by the data pointer registers (Y/Z).

> Example: Indirectly addressing mode with @YZ register.

B0MOV Y, #0 ; To clear Y register to access RAM bank 0.

BOMOV Z, #12H ; To set an immediate data 12H into Z register.

B0MOV A, @YZ ; Use data pointer @YZ reads a data from RAM location

; 012H into ACC.

## 2.4 STACK OPERATION

#### 2.4.1 OVERVIEW

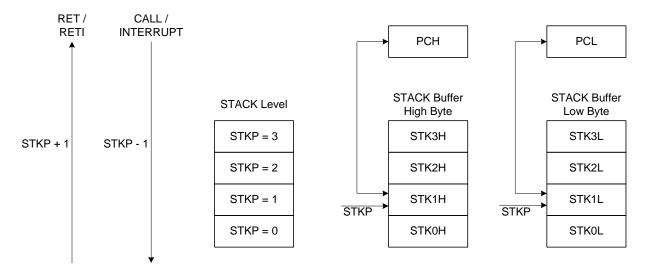

The stack buffer has 4-level. These buffers are designed to push and pop up program counter's (PC) data when interrupt service routine and "CALL" instruction are executed. The STKP register is a pointer designed to point active level in order to push or pop up data from stack buffer. The STKnH and STKnL are the stack buffers to store program counter (PC) data.

## 2.4.2 STACK REGISTERS

The stack pointer (STKP) is a 3-bit register to store the address used to access the stack buffer, 10-bit data memory (STKnH and STKnL) set aside for temporary storage of stack addresses.

The two stack operations are writing to the top of the stack (push) and reading from the top of stack (pop). Push operation decrements the STKP and the pop operation increments each time. That makes the STKP always point to the top address of stack buffer and write the last program counter value (PC) into the stack buffer.

The program counter (PC) value is stored in the stack buffer before a CALL instruction executed or during interrupt service routine. Stack operation is a LIFO type (Last in and first out). The stack pointer (STKP) and stack buffer (STKnH and STKnL) are located in the system register area bank 0.

| 0DFH        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2  | Bit 1  | Bit 0  |

|-------------|-------|-------|-------|-------|-------|--------|--------|--------|

| STKP        | GIE   | -     | -     | -     | -     | STKPB2 | STKPB1 | STKPB0 |

| Read/Write  | R/W   | -     | -     | -     | -     | R/W    | R/W    | R/W    |

| After reset | 0     | -     | -     | -     | -     | 1      | 1      | 1      |

Bit[2:0] **STKPBn:** Stack pointer  $(n = 0 \sim 2)$

Bit 7 **GIE:** Global interrupt control bit.

0 = Disable.

1 = Enable. Please refer to the interrupt chapter.

Example: Stack pointer (STKP) reset, we strongly recommended to clear the stack pointers in the beginning of the program.

> MOV A, #00000111B B0MOV STKP, A

| 0F0H~0FFH   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| STKnH       | -     | -     | -     | -     | -     | -     | SnPC9 | SnPC8 |

| Read/Write  | -     | -     | -     | -     | -     | -     | R/W   | R/W   |

| After reset | -     | -     | -     | -     | -     | -     | 0     | 0     |

| 0F0H~0FFH   | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| STKnL       | SnPC7 | SnPC6 | SnPC5 | SnPC4 | SnPC3 | SnPC2 | SnPC1 | SnPC0 |

| Read/Write  | R/W   |

| After reset | 0     | 0     | 0     | 0     | 0     | 0     | 0     | 0     |

STKn = STKnH, STKnL  $(n = 3 \sim 0)$

#### 2.4.3 STACK OPERATION EXAMPLE

The two kinds of Stack-Save operations refer to the stack pointer (STKP) and write the content of program counter (PC) to the stack buffer are CALL instruction and interrupt service. Under each condition, the STKP decreases and points to the next available stack location. The stack buffer stores the program counter about the op-code address. The Stack-Save operation is as the following table.

| Stack Level | S      | STKP Registe | er     | Stack     | Buffer   | Dosorintion       |

|-------------|--------|--------------|--------|-----------|----------|-------------------|

| Stack Level | STKPB2 | STKPB1       | STKPB0 | High Byte | Low Byte | Description       |

| 0           | 1      | 1            | 1      | Free      | Free     | -                 |

| 1           | 1      | 1            | 0      | STK0H     | STK0L    | -                 |

| 2           | 1      | 0            | 1      | STK1H     | STK1L    | -                 |

| 3           | 1      | 0            | 0      | STK2H     | STK2L    | -                 |

| 4           | 0      | 1            | 1      | STK3H     | STK3L    | -                 |

| > 4         | 0      | 1            | 0      | -         | -        | Stack Over, error |

There are Stack-Restore operations correspond to each push operation to restore the program counter (PC). The RETI instruction uses for interrupt service routine. The RET instruction is for CALL instruction. When a pop operation occurs, the STKP is incremented and points to the next free stack location. The stack buffer restores the last program counter (PC) to the program counter registers. The Stack-Restore operation is as the following table.

| Stack Level | S      | STKP Registe | er     | Stack     | Buffer   | Description |  |

|-------------|--------|--------------|--------|-----------|----------|-------------|--|

| Stack Level | STKPB2 | STKPB1       | STKPB0 | High Byte | Low Byte | Description |  |

| 4           | 0      | 1            | 1      | STK3H     | STK3L    | -           |  |

| 3           | 1      | 0            | 0      | STK2H     | STK2L    | -           |  |

| 2           | 1      | 0            | 1      | STK1H     | STK1L    | -           |  |

| 1           | 1      | 1            | 0      | STK0H     | STK0L    | -           |  |

| 0           | 1      | 1            | 1      | Free      | Free     | -           |  |

## 2.5 CODE OPTION TABLE

The code option is the system hardware configurations including oscillator type, watchdog timer operation, LVD option, reset pin option and OTP ROM security control. The code option items are as following table:

| Code Option     | Content   | Function Description                                                                                                       |  |  |  |  |

|-----------------|-----------|----------------------------------------------------------------------------------------------------------------------------|--|--|--|--|

|                 | IHRC_16M  | High speed internal 16MHz RC. XIN/XOUT pins are bi-direction GPIO mode.                                                    |  |  |  |  |

|                 | RC        | Low cost RC for external high clock oscillator. XIN pin is connected to RC oscillator. XOUT pin is bi-direction GPIO mode. |  |  |  |  |

| High_Clk        | 32K X'tal | Low frequency, power saving crystal (e.g. 32.768KHz) for external high clock oscillator.                                   |  |  |  |  |

|                 | 12M X'tal | High speed crystal /resonator (e.g. 12MHz) for external high clock oscillator.                                             |  |  |  |  |

|                 | 4M X'tal  | Standard crystal /resonator (e.g. 4M) for external high clock oscillator.                                                  |  |  |  |  |

|                 | Always_On | Watchdog timer is always on enable even in power down and green mode.                                                      |  |  |  |  |

| Watch_Dog       | Enable    | Enable watchdog timer. Watchdog timer stops in power down mode and green mode.                                             |  |  |  |  |

| Disable         |           | Disable Watchdog function.                                                                                                 |  |  |  |  |

|                 | Fosc/1    | Instruction cycle is 1 oscillator clocks. Noise Filter must be disabled.                                                   |  |  |  |  |

|                 | Fosc/2    | Instruction cycle is 2 oscillator clocks. Noise Filter must be disabled                                                    |  |  |  |  |

| Fcpu            | Fosc/4    | Instruction cycle is 4 oscillator clocks.                                                                                  |  |  |  |  |

|                 | Fosc/8    | Instruction cycle is 8 oscillator clocks.                                                                                  |  |  |  |  |

|                 | Fosc/16   | Instruction cycle is 16 oscillator clocks.                                                                                 |  |  |  |  |

| Reset Pin       | Reset     | Enable External reset pin.                                                                                                 |  |  |  |  |

| Neset_i iii     | P04       | Enable P0.4 input only without pull-up resister.                                                                           |  |  |  |  |

| Security        | Enable    | Enable ROM code Security function.                                                                                         |  |  |  |  |

| Security        | Disable   | Disable ROM code Security function.                                                                                        |  |  |  |  |

| Noise_Filter    | Enable    | Enable Noise Filter and Fcpu is Fosc/4~Fosc/16.                                                                            |  |  |  |  |

| INDISE_I III.EI | Disable   | Disable Noise Filter and Fcpu is Fosc/1~Fosc/16.                                                                           |  |  |  |  |

|                 | LVD_L     | LVD will reset chip if VDD is below 2.0V                                                                                   |  |  |  |  |

| LVD             | LVD_M     | LVD will reset chip if VDD is below 2.0V Enable LVD24 bit of PFLAG register for 2.4V low voltage indicator.                |  |  |  |  |

|                 | LVD_H     | LVD will reset chip if VDD is below 2.4V Enable LVD36 bit of PFLAG register for 3.6V low voltage indicator.                |  |  |  |  |

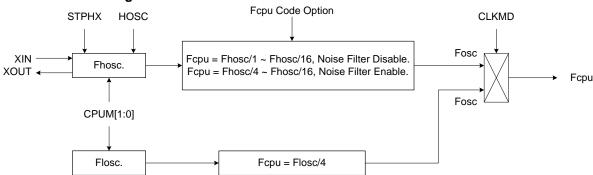

## 2.5.1 Fcpu code option

Fcpu means instruction cycle of normal mode (high clock). In slow mode, the system clock source is internal low speed RC oscillator. The Fcpu of slow mode isn't controlled by Fcpu code option and fixed Flosc/4 (16KHz/4 @3V, 32KHz/4 @5V).

## 2.5.2 Reset\_Pin code option

The reset pin is shared with general input only pin controlled by code option.

- Reset: The reset pin is external reset function. When falling edge trigger occurring, the system will be reset.

- P04: Set reset pin to general input only pin (P0.4). The external reset function is disabled and the pin is input pin.

## 2.5.3 Security code option

Security code option is OTP ROM protection. When enable security code option, the ROM code is secured and not dumped complete ROM contents.

## 2.5.4 Noise Filter code option

Noise Filter code option is a power noise filter manner to reduce noisy effect of system clock. If noise filter enable, Fcpu is limited below Fosc/1 and Fosc/2. The fast Fcpu rate is Fosc/4. If noise filter disable, the Fosc/1 and Fosc/2 options are released. In high noisy environment, enable noise filter, enable watchdog timer and select a good LVD level can make whole system work well and avoid error event occurrence.

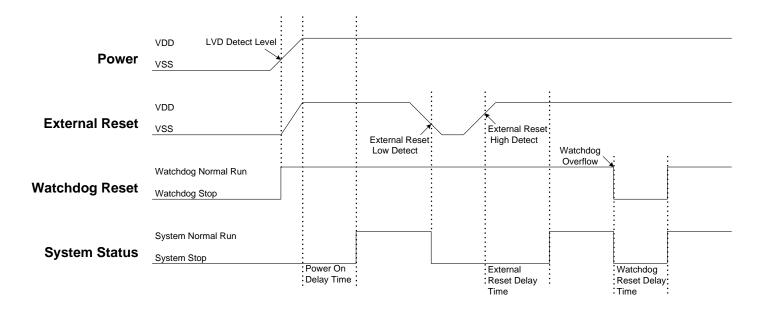

# 3 RESET

## 3.1 OVERVIEW

The system would be reset in three conditions as following.

- Power on reset

- Watchdog reset

- Brown out reset

- External reset (only supports external reset pin enable situation)

When any reset condition occurs, all system registers keep initial status, program stops and program counter is cleared. After reset status released, the system boots up and program starts to execute from ORG 0. The NT0, NPD flags indicate system reset status. The system can depend on NT0, NPD status and go to different paths by program.

| 086H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG       | NT0   | NPD   | LVD36 | LVD24 | -     | С     | DC    | Z     |

| Read/Write  | R/W   | R/W   | R     | R     | -     | R/W   | R/W   | R/W   |

| After reset | -     | -     | 0     | 0     | -     | 0     | 0     | 0     |

Bit [7:6] NTO, NPD: Reset status flag.

| NT0 | NPD | Condition                     | Description                                      |

|-----|-----|-------------------------------|--------------------------------------------------|

| 0   | 0   | Watchdog reset                | Watchdog timer overflow.                         |

| 0   | 1   | Reserved                      | -                                                |

| 1   | 0   | Power on reset and LVD reset. | Power voltage is lower than LVD detecting level. |

| 1   | 1   | External reset                | External reset pin detect low level status.      |

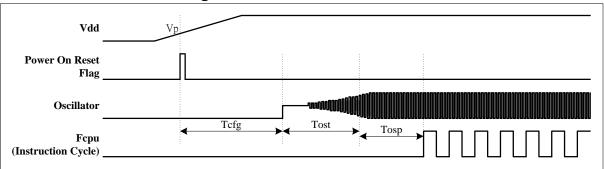

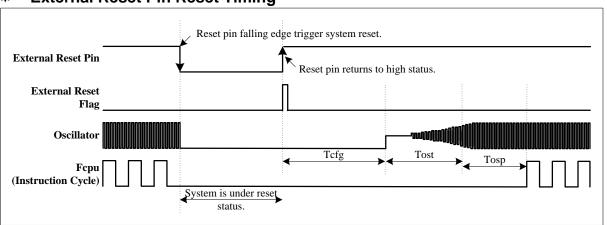

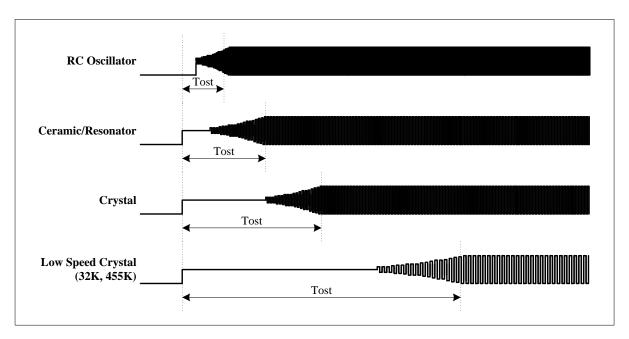

Finishing any reset sequence needs some time. The system provides complete procedures to make the power on reset successful. For different oscillator types, the reset time is different. That causes the VDD rise rate and start-up time of different oscillator is not fixed. RC type oscillator's start-up time is very short, but the crystal type is longer. Under client terminal application, users have to take care the power on reset time for the master terminal requirement. The reset timing diagram is as following.

## 3.2 POWER ON RESET

The power on reset depend no LVD operation for most power-up situations. The power supplying to system is a rising curve and needs some time to achieve the normal voltage. Power on reset sequence is as following.

- **Power-up:** System detects the power voltage up and waits for power stable.

- External reset (only external reset pin enable): System checks external reset pin status. If external reset pin is not high level, the system keeps reset status and waits external reset pin released.

- System initialization: All system registers is set as initial conditions and system is ready.

- Oscillator warm up: Oscillator operation is successfully and supply to system clock.

- Program executing: Power on sequence is finished and program executes from ORG 0.

## 3.3 WATCHDOG RESET

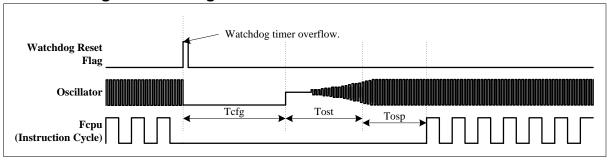

Watchdog reset is a system protection. In normal condition, system works well and clears watchdog timer by program. Under error condition, system is in unknown situation and watchdog can't be clear by program before watchdog timer overflow. Watchdog timer overflow occurs and the system is reset. After watchdog reset, the system restarts and returns normal mode. Watchdog reset sequence is as following.

- Watchdog timer status: System checks watchdog timer overflow status. If watchdog timer overflow occurs, the system is reset.

- System initialization: All system registers is set as initial conditions and system is ready.

- Oscillator warm up: Oscillator operation is successfully and supply to system clock.

- **Program executing:** Power on sequence is finished and program executes from ORG 0.

Watchdog timer application note is as following.

- Before clearing watchdog timer, check I/O status and check RAM contents can improve system error.

- Don't clear watchdog timer in interrupt vector and interrupt service routine. That can improve main routine fail.

- Clearing watchdog timer program is only at one part of the program. This way is the best structure to enhance the watchdog timer function.

- Note: Please refer to the "WATCHDOG TIMER" about watchdog timer detail information.

## 3.4 BROWN OUT RESET

The brown out reset is a power dropping condition. The power drops from normal voltage to low voltage by external factors (e.g. EFT interference or external loading changed). The brown out reset would make the system not work well or executing program error.

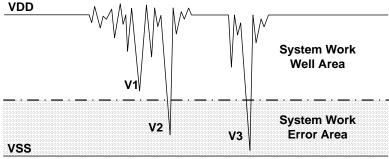

**Brown Out Reset Diagram**

The power dropping might through the voltage range that's the system dead-band. The dead-band means the power range can't offer the system minimum operation power requirement. The above diagram is a typical brown out reset diagram. There is a serious noise under the VDD, and VDD voltage drops very deep. There is a dotted line to separate the system working area. The above area is the system work well area. The below area is the system work error area called dead-band. V1 doesn't touch the below area and not effect the system operation. But the V2 and V3 is under the below area and may induce the system error occurrence. Let system under dead-band includes some conditions.

#### DC application:

The power source of DC application is usually using battery. When low battery condition and MCU drive any loading, the power drops and keeps in dead-band. Under the situation, the power won't drop deeper and not touch the system reset voltage. That makes the system under dead-band.

#### AC application:

In AC power application, the DC power is regulated from AC power source. This kind of power usually couples with AC noise that makes the DC power dirty. Or the external loading is very heavy, e.g. driving motor. The loading operating induces noise and overlaps with the DC power. VDD drops by the noise, and the system works under unstable power situation.

The power on duration and power down duration are longer in AC application. The system power on sequence protects the power on successful, but the power down situation is like DC low battery condition. When turn off the AC power, the VDD drops slowly and through the dead-band for a while.

## 3.5 THE SYSTEM OPERATING VOLTAGE

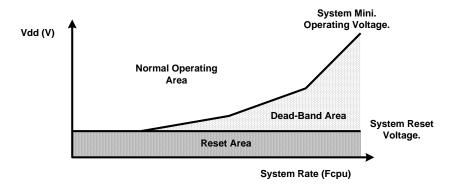

To improve the brown out reset needs to know the system minimum operating voltage which is depend on the system executing rate and power level. Different system executing rates have different system minimum operating voltage. The electrical characteristic section shows the system voltage to executing rate relationship.

Normally the system operation voltage area is higher than the system reset voltage to VDD, and the reset voltage is decided by LVD detect level. The system minimum operating voltage rises when the system executing rate upper even higher than system reset voltage. The dead-band definition is the system minimum operating voltage above the system reset voltage.

## 3.6 LOW VOLTAGE DETECTOR (LVD)

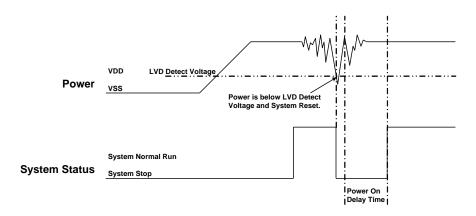

The LVD (low voltage detector) is built-in Sonix 8-bit MCU to be brown out reset protection. When the VDD drops and is below LVD detect voltage, the LVD would be triggered, and the system is reset. The LVD detect level is different by each MCU. The LVD voltage level is a point of voltage and not easy to cover all dead-band range. Using LVD to improve brown out reset is depend on application requirement and environment. If the power variation is very deep, violent and trigger the LVD, the LVD can be the protection. If the power variation can touch the LVD detect level and make system work error, the LVD can't be the protection and need to other reset methods. More detail LVD information is in the electrical characteristic section.

The LVD is three levels design (2.0V/2.4V/3.6V) and controlled by LVD code option. The 2.0V LVD is always enable for power on reset and Brown Out reset. The 2.4V LVD includes LVD reset function and flag function to indicate VDD status function. The 3.6V includes flag function to indicate VDD status. LVD flag function can be an **easy low battery detector**. LVD24, LVD36 flags indicate VDD voltage level. For low battery detect application, only checking LVD24, LVD36 status to be battery status. This is a cheap and easy solution.

| 086H        | Bit 7 | Bit 6 | Bit 5 | Bit 4 | Bit 3 | Bit 2 | Bit 1 | Bit 0 |

|-------------|-------|-------|-------|-------|-------|-------|-------|-------|

| PFLAG       | NT0   | NPD   | LVD36 | LVD24 | -     | C     | DC    | Z     |

| Read/Write  | R/W   | R/W   | R     | R     | -     | R/W   | R/W   | R/W   |

| After reset | -     | -     | 0     | 0     | -     | 0     | 0     | 0     |

Bit 5 LVD36: LVD 3.6V operating flag and only support LVD code option is LVD\_H.

0 = Inactive (VDD > 3.6V).

$1 = Active (VDD \le 3.6V).$

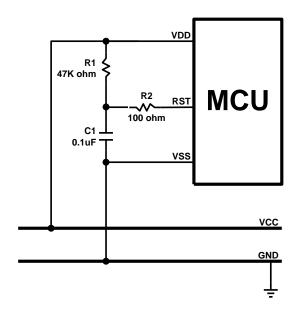

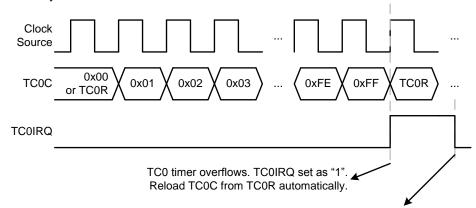

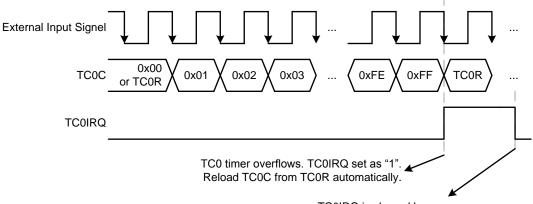

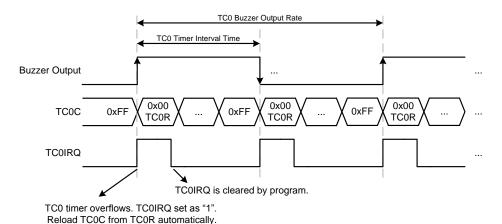

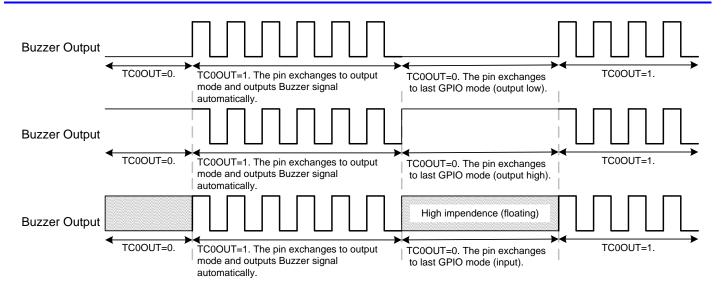

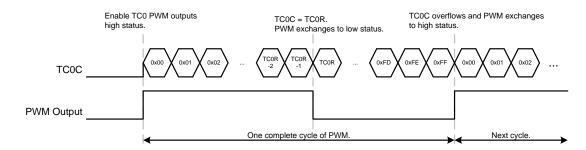

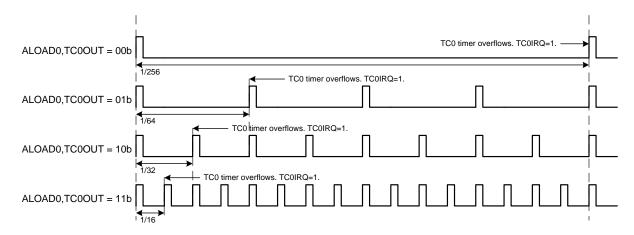

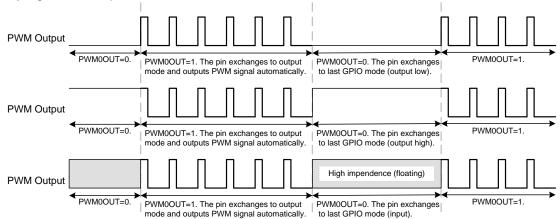

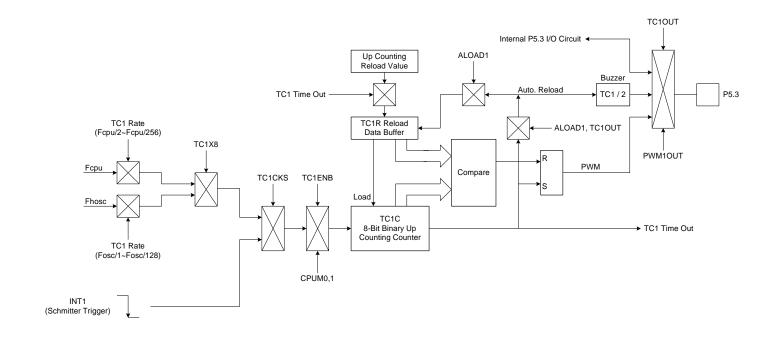

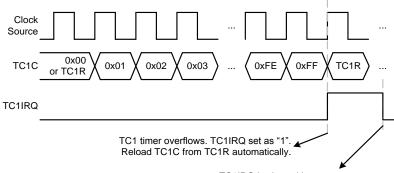

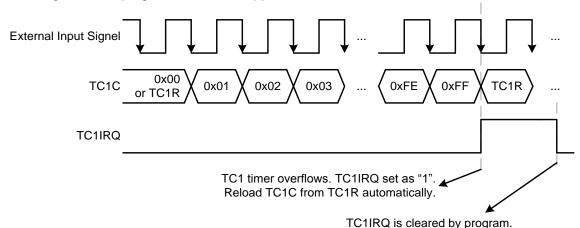

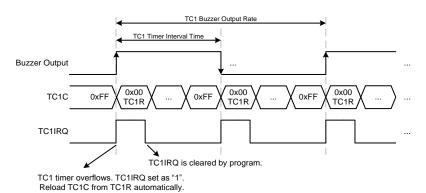

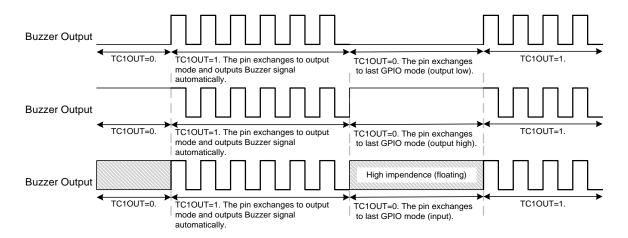

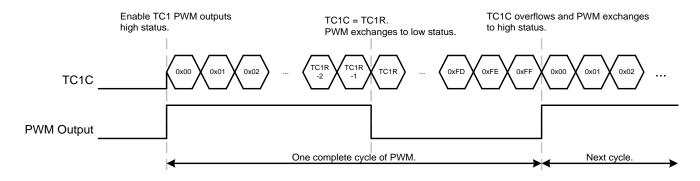

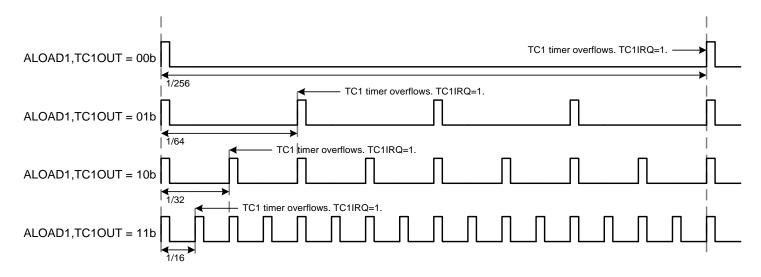

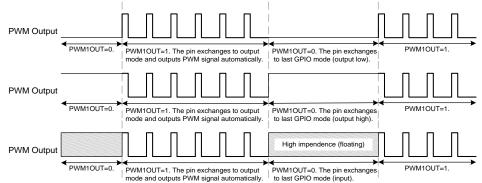

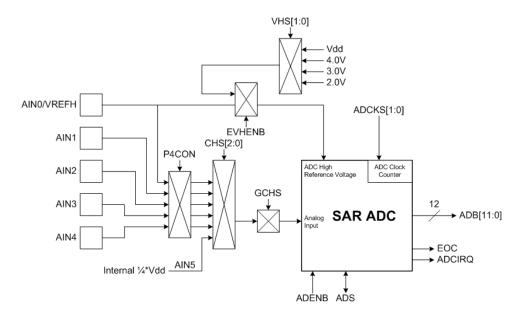

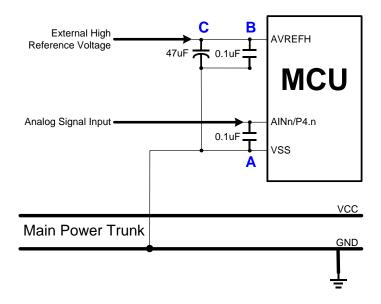

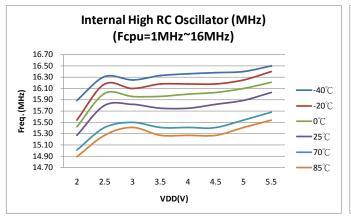

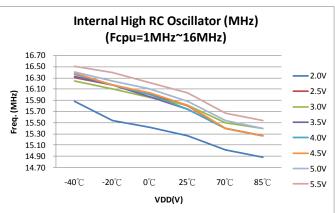

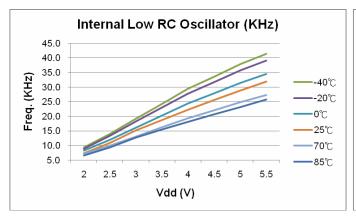

Bit 4 LVD24: LVD 2.4V operating flag and only support LVD code option is LVD\_M.