#### **ELECTRICAL CHARACTERISTICS**

| L  | l a | ٧i | m   | ur | n I | 2. | Ħ | n | 10 | * |

|----|-----|----|-----|----|-----|----|---|---|----|---|

| 71 | лα  | ΧI | *** | u, |     | 10 | ш | ш | 19 |   |

V<sub>D1</sub>, V<sub>DD</sub>

−0.3V to +12V

Storage Temperature

−25° C to +125° C

Clock

Crystal Frequency ...... 3.12MHz

#### **DC CHARACTERISTICS**

Operating Temperature T<sub>A</sub> = 0°C to +70°C

\* Exceeding these ratings could cause permanent damage to the device. This is a stress rating only and functional operation of this device at these conditions is not implied-operating ranges are specified in Standard Conditions. Exposure to absolute maximum rating conditions for extended periods may affect device reliability. Data labeled "typical" is presented for design guidance only and is not guaranteed.

| Characteristics                                                                                   | Sym              | Min | Тур | Max             | Units | Conditions                                                      |

|---------------------------------------------------------------------------------------------------|------------------|-----|-----|-----------------|-------|-----------------------------------------------------------------|

| Primary Supply Voltage                                                                            | V <sub>DD</sub>  | 4.6 | _   | 7               | V     |                                                                 |

| Standby Supply Voltage                                                                            | V <sub>D1</sub>  | 4.6 |     | 7               | V     |                                                                 |

| Primary Supply Current                                                                            | I <sub>DD</sub>  | _   | _   | 90              | mA    | V <sub>D1</sub> , V <sub>DD</sub> = 7.0V, T <sub>A</sub> = 25°C |

| Standby Supply Current                                                                            | I <sub>D1</sub>  | _   | _   |                 | mA    | V <sub>SS</sub> = 0.0V, T <sub>A</sub> = 25°C                   |

| Inputs A1-A8, ALD, SER IN, TEST, SE Logic 0                                                       | V <sub>IL</sub>  | o   | _   | 0.6             | v     |                                                                 |

| et4Logic 11                                                                                       | V <sub>IH</sub>  | 2.4 | _   | V <sub>D1</sub> | V     |                                                                 |

| Capacitance                                                                                       | CIN              | _   | _   | 10              | pf    |                                                                 |

| Leakage                                                                                           | I <sub>LC</sub>  | _   | _   | ±10             | μΑ    |                                                                 |

| RESET, SBY RESET<br>Logic 0                                                                       | V <sub>IL1</sub> | 0   | _   | 0.6             | v     |                                                                 |

| Logic 1                                                                                           | V <sub>IH1</sub> | 3.6 |     | V <sub>D1</sub> | ٧     |                                                                 |

| Oscillator Leakage<br>OSC 1                                                                       | _                | 1.0 | _   | 10              | μΑ    | No Load, OSC1 = 7.0V                                            |

| Outputs SBY, DIGITAL OUT, C1, C2, C3, \(\overline{LRQ}\), ROM DISABLE, ROM CLOCK, SER OUT Logic 0 | VoL              | 0   |     | 0.6             | v     | 0.72mA (2 LS TTL Loads)                                         |

| Logic 1                                                                                           | V <sub>OH</sub>  | 3.5 |     | V <sub>D1</sub> | V     | -50µA (2 LS TTL Loads)                                          |

#### **AC CHARACTERISTICS**

Operating Temperature: T<sub>A</sub> = 0°C to +70°C

| Characteristics  | Sym              | Min  | Тур          | Max | Units | Conditions |  |  |

|------------------|------------------|------|--------------|-----|-------|------------|--|--|

| Clock Frequency  | _                | _    | 3.120        | _   | MHz   | Crystal    |  |  |

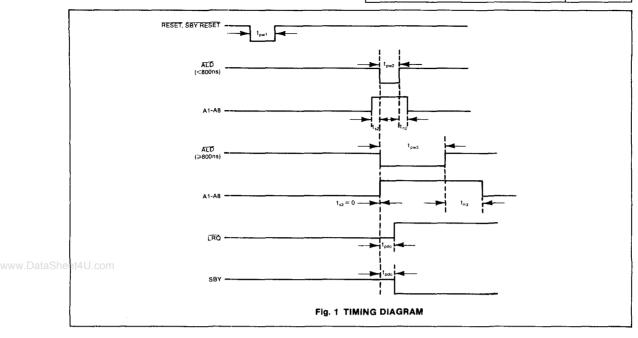

| Reset, SBY Reset | t <sub>pw1</sub> | 100  | _            |     | μs    |            |  |  |

| ALD (<800ns)     | t <sub>pw2</sub> | 200  | _            | 800 | ns    |            |  |  |

| A1-A8 Set Up     | t <sub>s2</sub>  | 160  | _            |     | ns    |            |  |  |

| A1-A8 Hold       | t <sub>h2</sub>  | 160  | _            | _   | ns    |            |  |  |

| ALD (≥800ns)     | t <sub>pw3</sub> | 800  | _            |     | ns    |            |  |  |

| A1-A8 Set Up     | t <sub>s3</sub>  | 0    | <del>-</del> | _   | ns    |            |  |  |

| A1-A8 Hold       | t <sub>h3</sub>  | 1200 | _            | _   | ns    |            |  |  |

| LRQ              | t <sub>pd0</sub> | _    | I -          | 640 | ns    |            |  |  |

| SBY              | t <sub>pd0</sub> |      | _            | 640 | ns    |            |  |  |

### PIN FUNCTIONS

| Pin Number                  | Name                        | Function  Ground                                                                                                                                                                                                                       |  |  |  |  |  |  |

|-----------------------------|-----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|--|

| 1                           | V <sub>ss</sub>             |                                                                                                                                                                                                                                        |  |  |  |  |  |  |

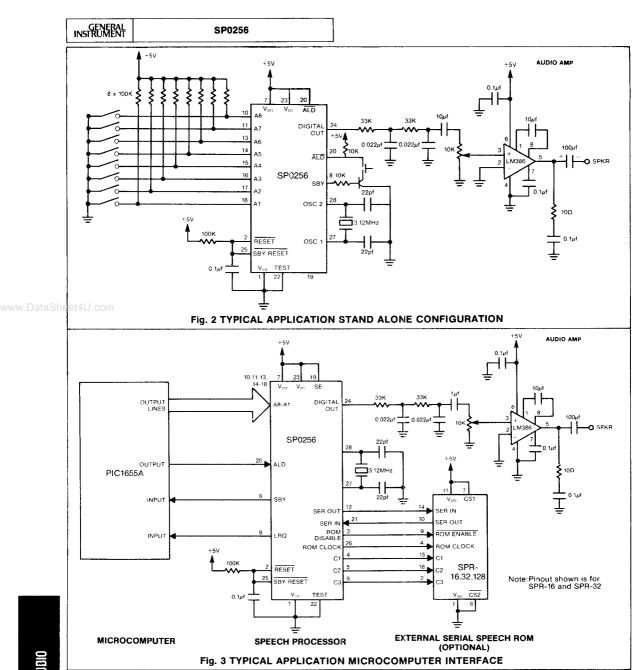

| 2                           | RESET                       | A logic 0 resets the SP. Must be returned to a logic 1 for normal operation.                                                                                                                                                           |  |  |  |  |  |  |

| 3                           | ROM DISABLE                 | For use with an external serial speech ROM. A logic 1 disables the external ROM.                                                                                                                                                       |  |  |  |  |  |  |

| 4,5,6                       | C1,C2,C3                    | Output control lines used by an external serial speech ROM.                                                                                                                                                                            |  |  |  |  |  |  |

| 7                           | V <sub>DD</sub>             | Primary power supply.                                                                                                                                                                                                                  |  |  |  |  |  |  |

| 8                           | SBY                         | STANDBY. A logic 1 output indicates that the SP is inactive (i.e., not talking) and V <sub>DD</sub> can be powered down externally to conserve power. When the SP is reactivated by an address being loaded, SBY will go to a logic 0. |  |  |  |  |  |  |

| 9                           | LRQ                         | LOAD REQUEST. LRQ is a logic 1 output whenever the input buffer is full. When LRQ goes to a logic 0, the input port is loaded by placing the 8 address bits on A1-A8 and pulsing the ALD input.                                        |  |  |  |  |  |  |

| 10,11,13,14,<br>15,16,17,18 | A8,A7,A6,A5,<br>A4,A3,A2,A1 | 8-bit address which defines any one of 256 speech entry points.                                                                                                                                                                        |  |  |  |  |  |  |

| 12                          | SER OUT                     | SERIAL ADDRESS OUT. This output transfers a 16-bit address serially to external speech ROM.                                                                                                                                            |  |  |  |  |  |  |

| 19                          | SE                          | STROBE ENABLE. Normally held in a logic 1 state. When tied to ground, ALI is disabled and the SP will automatically latch in the address on the input but approximately 1µs after detecting a logic 1 on any address line.             |  |  |  |  |  |  |

| 20                          | ALD                         | ADDRESS LOAD. A negative pulse on this input loads the 8 address bits into the input port. The leading edge of this pulse causes LRQ to go high.                                                                                       |  |  |  |  |  |  |

| 21                          | SER IN                      | SERIAL IN. This is an 8-bit serial data input from an external speech ROM.                                                                                                                                                             |  |  |  |  |  |  |

| 22                          | TEST                        | A logic 1 places the SP in test mode. This pin should normally be grounded.                                                                                                                                                            |  |  |  |  |  |  |

| 23                          | V <sub>D1</sub>             | Standby power supply for the interface logic and controller.                                                                                                                                                                           |  |  |  |  |  |  |

| 24                          | DIGITAL OUT                 | Pulse width modulated digital speech output which, when filtered by a 5kHz low pass filter and amplified, will drive a loudspeaker.                                                                                                    |  |  |  |  |  |  |

| 25                          | SBY RESET                   | STANDBY RESET. A logic 0 resets the interface logic. Normally should be a logic 1.                                                                                                                                                     |  |  |  |  |  |  |

| 26                          | ROM CLOCK                   | 1.56MHz clock for an external serial speech ROM.                                                                                                                                                                                       |  |  |  |  |  |  |

| 27                          | OSC 1                       | XTAL IN. Input connection for a 3.12MHz crystal.                                                                                                                                                                                       |  |  |  |  |  |  |

| 28                          | OSC 2                       | XTAL OUT. Output connection for a 3.12MHz crystal.                                                                                                                                                                                     |  |  |  |  |  |  |

### SP0256-AL2

## **Aliophone Based Speech Processor**

#### DESCRIPTION

This product is the SP0256 Speech Processor preprogrammed with a standard ROM Pattern containing 64 allophones. Through the concatenation of selected allophones the user can construct any word in the English language, thereby providing an unlimited vocabulary at a data rate of less than 100 bits/second.

#### **DATA MANUAL**

A complete description of the SP0256-AL2 is contained in the Allophone Speech Synthesis Manual.

ww DataShee

†SP0232

## 32K Speech Processor

#### DESCRIPTION

This product is pin for pin compatible with the SP0256 Speech Processor. This enhanced version of the SP0256 contains 32K of internal ROM.

†For future release.

**SPR000**

# **Speech Interface Chip**

#### **DESCRIPTION**

The SPR000 is designed to interface a standard ROM, PROM, or EPROM to the SP0256 Speech Processor to provide a large amount of vocabulary expansion. This interface contains all the logic necessary to allow data communication under control of the Speech Processor. Two chip selects are provided, (CS1 and CS2), for use in systems where it is desirable to bank blocks of memory under external control. With the capability of addressing 64K bytes of memory the SPR000 is ideal for applications such as SP0256 testing, and speech ROM emulation.