### Offline Current Mode PWM Controller with Built-in CC Regulation

#### **FEATURES**

- General Primary Side Constant-Current (CC)

Control Supports DCM and CCM Operation

- ±5% CC Regulation, ±1% CV Regulation with Fast Dynamic Response

- CC Algorithm Compensates for Line Variation and Transformer Inductance Tolerance

- Less than 75mW Standby Power for sub 30W Application

- Current Mode Control

- Built-in Frequency Shuffling

- Fixed 65KHz Switching Frequency

- Green Mode and Burst Mode Control

- On-chip Thermal Shutdown

- Cycle-by-Cycle Current Limiting

- Built-in Leading Edge Blanking

- Built-in Slope Compensation

- Very Low Startup and Operation Current

- Available with SOT23-6 Package

### **APPLICATIONS**

- Chargers and Adapter

- Motor Driver Power Supply

### **GENERAL DESCRIPTION**

SP201 is a high performance current mode PWM controller for offline flyback converter applications. The IC has built-in General Primary Side CC control, which simplifies isolated power supply design that requires CC regulation of the output.

In SP201, PWM switching frequency with shuffling is fixed to 65KHz and is trimmed to tight range. The IC has built-in green and burst mode control for light and zero loadings, which can achieve less than 75mW standby power for sub 30W applications.

SP201 integrates functions and protections of Under Voltage Lockout (UVLO), VDD over Voltage Protection (VDD OVP), Cycle-by-cycle Current Limiting (OCP), Short Load Protection (SLP), Over Load Protection (OLP), On-Chip Thermal Shutdown (OTP), Soft Start, VDD Clamping, etc.

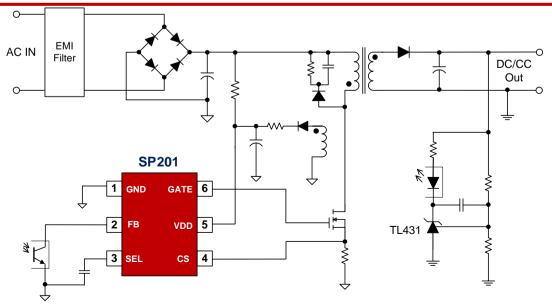

## TYPICAL APPLICATION CIRCUIT (For Applications with CC/CV Control)

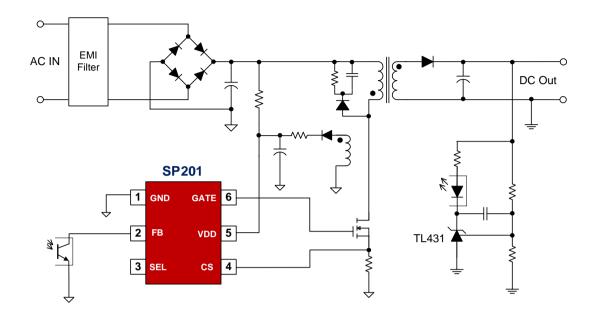

# **TYPICAL APPLICATION CIRCUIT (For Applications with Only CV Control)**

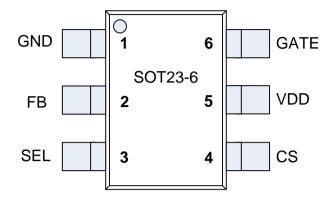

# **Pin Configuration**

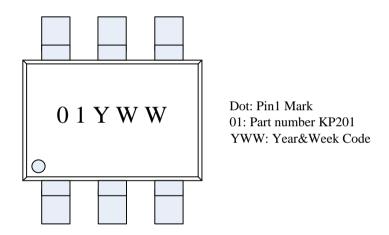

# **Marking Information**

Pin Description (KP201A)

| i iii bescription (Ki 201A) |             |     |                                                                                                                                                                                  |  |  |  |

|-----------------------------|-------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| Pin<br>Number               | Pin<br>Name | I/O | Description                                                                                                                                                                      |  |  |  |

| 1                           | GND         | Р   | The ground of the IC                                                                                                                                                             |  |  |  |

| 2                           | FB          | I   | Feedback pin. The loop regulation is achieved by connecting a photo-coupler to this pin. PWM duty cycle is determined by this pin voltage and the current sense signal at Pin 4. |  |  |  |

| 3                           | SEL         | I   | Connect a capacitor between SEL and GND, the IC will work in CC/CV mode. If SEL pin is floating, the IC will work in CV mode only.                                               |  |  |  |

| 4                           | CS          | I   | Current sense input pin.                                                                                                                                                         |  |  |  |

| 5                           | VDD         | Р   | IC power supply pin.                                                                                                                                                             |  |  |  |

| 6                           | GATE        | 0   | Totem-pole gate driver output to drive the external MOSFET.                                                                                                                      |  |  |  |

**Absolute Maximum Ratings** (Note 1)

| Parameter                              | Value      | Unit |

|----------------------------------------|------------|------|

| VDD DC Supply Voltage                  | 35         | V    |

| VDD DC Clamp Current                   | 10         | mA   |

| FB, CS, SEL voltage range              | -0.3 to 7  | V    |

| GATE voltage range                     | 20         | V    |

| Package Thermal Resistance (SOT23-6)   | 250        | °C/W |

| Maximum Junction Temperature           | 150        | °C   |

| Operating Temperature Range            | -40 to 85  | °C   |

| Storage Temperature Range              | -65 to 150 | °C   |

| Lead Temperature (Soldering, 10sec.)   | 260        | °C   |

| ESD Capability, HBM (Human Body Model) | 3          | kV   |

| ESD Capability, MM (Machine Model)     | 250        | V    |

**Recommended Operation Conditions** (Note 2)

| Parameter                     | Value        | Unit |  |

|-------------------------------|--------------|------|--|

| Supply Voltage, VDD           | 10.5 to 28.5 | V    |  |

| Operating Ambient Temperature | -40 to 85    | °C   |  |

ELECTRICAL CHARACTERISTICS (T<sub>A</sub> = 25°C, VDD=22V, if not otherwise noted)

| Symbol                          | Parameter                       | Test Conditions              | Min  | Тур. | Max  | Unit |  |

|---------------------------------|---------------------------------|------------------------------|------|------|------|------|--|

| Supply Voltage Section(VDD Pin) |                                 |                              |      |      |      |      |  |

| I <sub>VDD_st</sub>             | Start-up current into VDD pin   |                              |      | 2    | 20   | uA   |  |

| I <sub>VDD_Op</sub>             | Operation Current               | V <sub>FB</sub> =3V,GATE=1nF |      | 1.2  | 2    | mA   |  |

| I <sub>VDD_standby</sub>        | Standby Current                 |                              |      | 0.6  | 1    | mA   |  |

| $V_{DD\_ON}$                    | VDD Under Voltage Lockout Exit  |                              | 19   | 21   | 23   | V    |  |

| $V_{DD\_OFF}$                   | VDD Under Voltage Lockout Enter |                              | 8.2  | 9.3  | 10.2 | >    |  |

| $V_{DD\_OVP}$                   | VDD OVP Threshold               |                              | 29   | 31.5 | 33   | >    |  |

| $V_{DD\_Clamp}$                 | VDD Zener Clamp Voltage         | $I(V_{DD}) = 7 \text{ mA}$   | 33.5 | 35.5 | 37.5 | >    |  |

| Feedback Input Section (FB Pin) |                                 |                              |      |      |      |      |  |

| V <sub>FB_Open</sub>            | FB Open Voltage                 |                              | 4.5  | 5.4  | 6    | V    |  |

|                                | I                                              |                                         |      | T    | 1    | T    |  |  |  |

|--------------------------------|------------------------------------------------|-----------------------------------------|------|------|------|------|--|--|--|

| I <sub>FB_Short</sub>          | FB Short Circuit Current                       | Short FB Pin to GND,<br>Measure Current |      | 0.4  |      | mA   |  |  |  |

| $Z_{FB\_IN}$                   | FB Input Impedance                             |                                         |      | 25   |      | Kohm |  |  |  |

| A <sub>CS</sub>                | PWM Gain                                       | $\DeltaV_{FB}/\DeltaV_{CS}$             |      | 2.0  |      | V/V  |  |  |  |

| $V_{skip}$                     | FB Under Voltage GATE Clock is OFF             |                                         |      | 1.0  |      | V    |  |  |  |

| V <sub>TH_OLP</sub>            | Power Limiting FB Threshold Voltage            |                                         |      | 3.6  |      | V    |  |  |  |

| $T_{D\_OLP}$                   | Power Limiting Debounce Time                   | SEL Pin is floating                     |      | 75   |      | ms   |  |  |  |

| Current Se                     | nse Input Section (CS Pin)                     |                                         |      |      |      |      |  |  |  |

| $T_{LEB}$                      | CS Input Leading Edge<br>Blanking Time         |                                         |      | 250  |      | ns   |  |  |  |

| $V_{cs(max)}$                  | Current limiting threshold                     |                                         | 0.97 | 1.0  | 1.03 | V    |  |  |  |

| $T_{D\_OC}$                    | Over Current Detection and Control Delay       | GATE=1nF                                |      | 70   |      | ns   |  |  |  |

| Oscillator S                   | Oscillator Section                             |                                         |      |      |      |      |  |  |  |

| F <sub>osc</sub>               | Normal Oscillation Frequency                   |                                         | 60   | 65   | 70   | KHz  |  |  |  |

| $\Delta$ F(shuffle) $/F_{OSC}$ | Frequency Shuffling Range                      |                                         | -4   |      | 4    | %    |  |  |  |

| T(shuffle)                     | Frequency Shuffling Period                     |                                         |      | 32   |      | ms   |  |  |  |

| D <sub>MAX</sub>               | Maximum Switching Duty<br>Cycle                |                                         |      | 66.7 |      | %    |  |  |  |

| F <sub>Bust</sub>              | Burst Mode Base Frequency                      |                                         |      | 22   |      | KHz  |  |  |  |

| CC Loop R                      | CC Loop Regulation Section (SEL = Capacitor)   |                                         |      |      |      |      |  |  |  |

| $V_{CC\_Reg}$                  | Internal Reference for CC Loop Regulation      | SEL Pin=Capacitor                       | 194  | 200  | 206  | mV   |  |  |  |

| I <sub>CC_SEL_Source</sub>     | Internal Source Current for CC Loop Regulation | SEL Pin=Capacitor                       |      | 20   |      | uA   |  |  |  |

| V <sub>CC_SLP_SEL</sub>        | Short Load Protection (SLP)<br>Threshold       | SEL Pin=Capacitor                       |      | 0.7  |      | V    |  |  |  |

| T <sub>CC_Short_SEL</sub>      | Short Load Protection (SLP)<br>Debounce Time   | SEL Pin=Capacitor                       |      | 210  |      | ms   |  |  |  |

| On-Chip Thermal Shutdown       |                                                |                                         |      |      |      |      |  |  |  |

| T <sub>SD</sub>                | Thermal Shutdown                               | (Note 3)                                |      | 165  |      | ° C  |  |  |  |

|                                | 1                                              | 1                                       |      | 1    | 1    | 1    |  |  |  |

| T <sub>RC</sub>                         | Thermal Recovery           | (Note 3)          |     | 140 |   | ° C |  |

|-----------------------------------------|----------------------------|-------------------|-----|-----|---|-----|--|

| GATE Driver Section (GATE Pin) (Note 3) |                            |                   |     |     |   |     |  |

| V <sub>OL</sub>                         | Output Low Level           | Igate_sink=20mA   |     |     | 1 | V   |  |

| V <sub>OH</sub>                         | Output High Level          | Igate_source=20mA | 7.5 |     |   | V   |  |

| $V_{G\_Clamp}$                          | Output Clamp Voltage Level | VDD=24V           |     | 16  |   | V   |  |

| T_r                                     | Output Rising Time         | GATE=1nF          |     | 150 |   | ns  |  |

| T_f                                     | Output Falling Time        | GATE=1nF          |     | 60  |   | ns  |  |

**Note1.** Stresses listed as the above "Maximum Ratings" may cause permanent damage to the device. These are for stress ratings. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specifications is not implied. Exposure to maximum rating conditions for extended periods may remain possibility to affect device reliability.

Note2. The device is not guaranteed to function outside its operating conditions.

Note3. Guaranteed by the Design.