# Monolithic, 12-Bit Data Acquisition System

- Complete Monolithic 8-Channel, 12-Bit DAS

- 100kHz Throughput

- 16-Bit Microprocessor Bus Interface

- MUX Inputs Overvoltage Protected

- Parallel 8/4-Bit Nibble Output

- Tri-State Latched Output

- No Missing Codes to 12-Bits

- 28-pin SOIC and PDIP package

- 200mW Max Power Dissipation (140mw Typ.)

\*Formerly part of the SP410 Series.

#### DESCRIPTION...

The **SP8480 Series** are complete monolithic data acquisition systems, featuring 8-channel multiplexer, internal reference and 12-bit sampling A/D converter in 28–pin plastic DIP or SOIC packages. Linearity errors of  $\pm 0.5$  and  $\pm 1.0$  LSB, and Differential Non-linearity to 12-bits are guaranteed, with no missing codes over temperature. Multiplexer settling plus acquisition time is  $1.9\mu s$  maximum; A/D conversion time is  $8.1\mu s$  maximum.

# **ABSOLUTE MAXIMUM RATINGS**

| V <sub>cc</sub> to Common Ground         | 0V to +16.5V                    |

|------------------------------------------|---------------------------------|

| V <sub>Logic</sub> to Common Ground      | 0V to +7V                       |

| Analog Common to Digital Common Ground . | 0.5V to +1V                     |

| Digital Inputs to Common Ground          | 0.5V to V <sub>1000</sub> +0.5V |

| Digital Outputs to Common Ground         | 0.5V to V +0.5V                 |

| Multiplexer Analog Inputs                | 16.5V to +31.5V                 |

| Gain and Offset Adjustment               | 0.5V to V +0.5V                 |

| Analog Input Maximum Current             | 25mA                            |

| Temperature with Bias Applied            | 55°C to +125°C                  |

| Storage Temperature                      | 65°C to +150°C                  |

| Lead Temperature, Soldering              | 300°C, 10sec                    |

|                                          |                                 |

CAUTION: www. DataSheet 4U.com

ESD (ElectroStatic Discharge) sensitive

device. Permanent damage may occur on

unconnected devices subject to high energy

electrostatic fields. Unused devices must be

stored in conductive foam or shunts.

Personnel should be properly grounded prior

to handling this device. The protective foam

should be discharged to the destination

socket before devices are removed.

### **SPECIFICATIONS**

(T<sub>A</sub>= 25°C and nominal supply voltages unless otherwise noted)

|                                                                               | MIN.         | TYP.                                | MAX.                     | UNIT                       | CONDITIONS                                                                                                               |

|-------------------------------------------------------------------------------|--------------|-------------------------------------|--------------------------|----------------------------|--------------------------------------------------------------------------------------------------------------------------|

| ANALOG INPUTS Input Voltage Range Multiplexer Inputs Configuration            | 9            | 0 to +5<br>Single-ende              | 8<br>ed                  | V                          |                                                                                                                          |

| Input Impedance<br>ON Channel<br>OFF Channel<br>Input Bias Current            |              | 10 <sup>9</sup><br>10 <sup>10</sup> |                          | $\Omega \Omega$            | Parallel with 30pF<br>Parallel with 5pF                                                                                  |

| Per Channel Crosstalk                                                         |              |                                     | ±10<br>±250              | nA<br>nA                   | 25°C<br>-55°C to +125°C                                                                                                  |

| OFF to ON Channel                                                             |              |                                     | -90<br>-80<br>-70        | dB<br>dB<br>dB             | 10kHz, 0V to +5V $_{pk\text{-to-pk}}$<br>50kHz, 0V to +5V $_{pk\text{-to-pk}}$<br>100kHz, 0V to +5V $_{pk\text{-to-pk}}$ |

| ACCURACY Resolution Linearity Error                                           | 12           |                                     |                          | Bits                       |                                                                                                                          |

| −K, −B<br>−J, −A<br>Differential Non-Linearity                                |              |                                     | ±0.5<br>±1               | LSB<br>LSB                 |                                                                                                                          |

| -K, -B<br>-J, -A<br>Offset Error<br>www.⊅atGaineError.com<br>No Missing Codes |              | ±2<br>±0.3                          | ±1<br>±2                 | LSB<br>LSB<br>LSB<br>%FSR  | Adjustable to zero<br>Adjustable to zero                                                                                 |

| –K, –B                                                                        |              | Guarantee                           | d                        |                            |                                                                                                                          |

| TRANSFER CHARACTERIS Throughput Rate MUX Settling/Acquisition A/D Conversion  | 100          |                                     | 1.9<br>8.1               | kHz<br>μs<br>μs            |                                                                                                                          |

| STABILITY Linearity Offset Gain                                               |              | ±0.5<br>±5<br>±10                   | ±2.5<br>±25<br>±50       | ppm/°C<br>ppm/°C<br>ppm/°C |                                                                                                                          |

| DIGITAL INPUTS Capacitance Logic Levels                                       |              | 5                                   |                          | pF                         |                                                                                                                          |

| V <sub>IH</sub> V <sub>IL</sub> I <sub>IH</sub> I <sub>IL</sub>               | +2.4<br>-0.5 |                                     | +5.5<br>+0.8<br>±5<br>±5 | V<br>V<br>μΑ<br>μΑ         |                                                                                                                          |

$(T_{\rm A}{=}~25^{\circ}{\rm C}$  and nominal supply voltages unless otherwise noted)

|                                          | MIN.     | TYP.               | MAX.       | UNIT     | CONDITIONS                     |

|------------------------------------------|----------|--------------------|------------|----------|--------------------------------|

| DIGITAL OUTPUTS                          |          |                    |            |          |                                |

| Capacitance Logic Levels                 |          | 5                  |            | pF       |                                |

| V <sub>OH</sub>                          | +2.4     |                    |            | V        | I <sub>OH</sub> ≤ 500μA        |

| l V <sub>OI</sub>                        |          |                    | +0.4       | V        | I o ≤ 1.6mA                    |

| Leakage Current Data Output              |          | ±40<br>lffset Bina | <br>       | μΑ       | High impedance, data bits only |

| POWER REQUIREMENTS                       |          | iliset billa       | y          |          |                                |

| V <sub>LOGIC</sub>                       | +4.5     |                    | +5.5       | V        |                                |

| Logic                                    |          | 0.8                | 4          | mA       |                                |

| Vcc                                      | +11.4    | 0                  | +16.5      | V        |                                |

| Power Dissipation                        |          | 9<br>140           | 12<br>200  | mA<br>mW |                                |

| ENVIRONMENTAL                            |          |                    |            |          |                                |

| Operating Temperature                    |          |                    |            |          |                                |

| Commercial; –J, –K<br>Industrial; –A, –B | 0<br>-40 |                    | +70<br>+85 | °C<br>°C |                                |

| Storage Temperature                      | -65      |                    | +150       | °C       |                                |

|                                          |          |                    |            |          |                                |

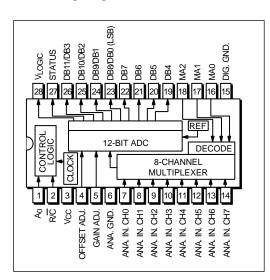

## PIN FUNCTION...

A<sub>0</sub> — Device Address — Logic low enables 8 MSB read; logic high enables 4 LSB read

STATUS — Identifies valid data output; goes to logic high during conversion; goes to logic low when conversion is completed and data is valid

R/C — Read/Convert — Initiates conversion on the high-to-low transition; logic low disconnects data bus; logic high initiates read

CE — Chip Enable — Logic www DataSheet4U.com or convert; logic high enables read or convert

${\rm MA_0}, {\rm MA_1}, {\rm MA_2}$  — MUX Address 0, 1 & 2 — Selects analog input channels  ${\rm CH_0}$  through  ${\rm CH_7}$

${\rm DB_0}$  through  ${\rm DB_{11}}$  — Data Outputs — Logic high is binary true; logic low binary false

#### **CONTROL TRUTH TABLE**

| A <sub>°</sub> | R/C   | OPERATION        |  |  |  |

|----------------|-------|------------------|--|--|--|

| Х              | H ->L | Start Conversion |  |  |  |

| 0              | 1     | Enable 8 MSBs    |  |  |  |

| 1              | 1     | Enable 4 LSBs    |  |  |  |

#### **MULTIPLEXER TRUTH TABLE**

| MA <sub>2</sub> | MA <sub>1</sub> | MΑ <sub>o</sub> | OPERATION                |

|-----------------|-----------------|-----------------|--------------------------|

| 0               | 0               | 0               | CH₀ Selected             |

| 0               | 0               | 1               | CH₁ Selected             |

| 0               | 1               | 0               | CH <sub>2</sub> Selected |

| 0               | 1               | 1               | CH₃ Selected             |

| 1               | 0               | 0               | CH₄ Selected             |

| 1               | 0               | 1               | CH₅ Selected             |

| 1               | 1               | 0               | CH <sub>6</sub> Selected |

| 1               | 1               | 1               | CH <sub>7</sub> Selected |

#### FEATURES...

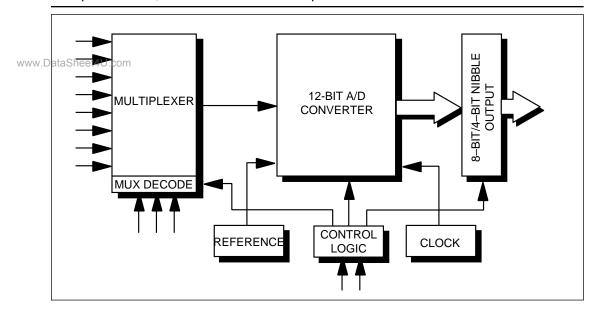

The **SP8480 Series** are complete data acquisition systems, featuring 8-channel multiplexer, internal reference and 12-bit sampling A/D converter implemented as a single monolithic IC. The analog multiplexer accepts 0V to +5V unipolar full scale inputs. Output data is formatted as an 8-bit/4-bit nibble.

Linearity errors of ±0.5 and ±1.0 LSB, and Differential Non-linearity to 12-bits is guaranteed, with no missing codes over temperature. Channel-to-channel crosstalk is typically -85dB. Multiplexer settling plus acquisition time is 1.9μs maximum; A/D conversion time is 8.1μs maximum.

Versions of the **SP8480** are available in 28-pin plastic DIP, ceramic DIP or SOIC packages. Operating temperature ranges are 0°C to +70°C commercial and -40°C to +85°C industrial.

#### CIRCUIT OPERATION...

The **SP8480** is a complete 8-channel data acquisition systems (DAS), with on-board multiplexer, voltage reference, sample-and-hold, clock and tri-state outputs. The digital control architecture is very similar to the industry-standard 574-type A/D, and uses identical control lines and digital states.

The multiplexer for the **SP8480** is identical in operation to many discrete devices available today, except that it has been integrated into the single-chip DAS. The appropriate channel is selected using the MUX address lines MA<sub>0</sub>, MA<sub>1</sub>, and MA<sub>2</sub> per the truth table. The selected analog input is fed through to the ADC. The input impedance into any MUX channel will be on the order to 10<sup>9</sup> ohms, since it is connected to the integral sampling structure of the capacitor DAC. Crosstalk is kept to -85dB at 0V to 5V<sub>pp</sub> over an input frequency range of 10kHz to 50kHz.

When the internal control section of the **SP8480** initiates a conversion command the internal clock is enabled, and the successive approximation register (SAR) is reset to all zeros. Once the conversion has been started it cannot be stopped or restarted. Data is not available at the output buffers until the conversion has been completed.

The SAR, timed by the clock, sequences through the conversion cycle and www.BataSheet4D.com convert flag to the control section of the ADC. The clock is then disabled by the control section, which puts the STATUS output line low. The control section is enabled to allow the data to be read by external command  $(R/\overline{C})$ .

#### **Multiplexer Control and Inputs**

On the **SP8480** the multiplexer is independent of any other control line. The address line latches MA, MA, and MA, are hard-wired in an enabled mode in the **SP8480**, and are therefore transparent. Data setup time for these inputs is 50ns. If a device is required with additional MUX control, please refer to the Sipex SP8481 DAS. Since the latches are enabled, MUX channel select data need not be held by the bus for a minimum period of 3.0µs after the conversion has been initiated. This is the time required for the MUX and Sample and Hold to settle. However it is advisable that the MUX not be changed at all during the full 10us conversion time due to capacitive coupling effects of digital edges through the silicon.

The **SP8480** multiplexer inputs have been designed to allow substantial overvoltage conditions to occur without any damage. The inputs are diode-clamped and further protected with a  $200\Omega$  series resistor. As a result, momentary (10 seconds) input voltages can be as low as -16.5V or as high as +31.5V with no change or degradation in multiplexer performance or crosstalk. This feature allows the output voltage of an externally connected op amp to swing to  $\pm 15$ V supply levels with no multiplexer damage. Complicated power-up sequencing is not required to protect the **SP8480**. The multiplexer inputs may be damaged, however, if the inputs are allowed to either source or sink greater than 100mA.

## **Initiating A Conversion**

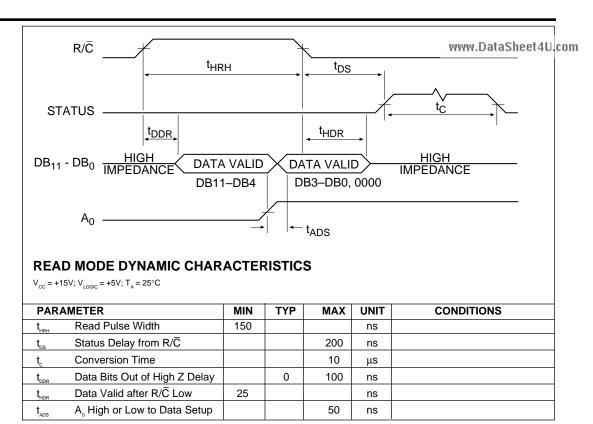

Please refer to Figure 4. The **SP8480** was designed to require a minimum of control to perform a 12-bit conversion. The control input used is R/C which tri-states the outputs and starts the conversion when low. The STATUS line indicates when a conversion is in process and when it is complete. The  $A_{\scriptscriptstyle 0}$  control input is used to

latch the 8 MSB's and 4 LSB's of output data on the 8-bit wide output data bus.

The conversion cycle is started when  $R/\bar{C}$  is brought low and must be held low for a minimum of 50ns. The  $R/\bar{C}$  signal will also cause the output latches to be in a tri-state mode when low. Approximately 200ns after  $R/\bar{C}$  is low, STATUS will change from low to high. This output signal will stay high while the **SP8480** is performing a conversion. Valid data will be latched to the output bus, through internal control, 500ns prior to the STATUS line transitioning from a high to low.

## Reading the Data

Please refer to Figure 5. To read data from the **SP8480**, the  $R/\overline{C}$  and  $A_{\circ}$  control lines are used.  $R/\overline{C}$  must be high a minimum of 50ns prior to reading the data to allow time for the output latches to come out of the high impedance tri-state mode.  $A_{\circ}$  is used to access the data. The first 8 MSBs will be on pins 26 through 19, with pin 26 being the MSB. The remaining 4 LSBs will be on pins 23 through 26 with pin 23 being the LSB. When  $A_{\circ}$  is switched from one state to the next, there is a 50ns output latch propagation delay between the MSBs and LSBs being present on the output pins.

#### **CALIBRATION**

The calibration procedure for the **SP8480** consists of adjusting the most negative input voltage (0V) to the ideal output code for offset adjustment, and then adjusting the most positive input www. Voltage (5.0V) to its ideal output code for gain adjustment.

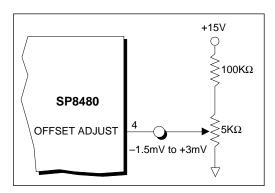

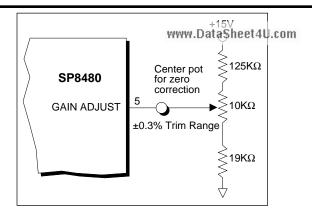

Figure 1. Offset Adjust

Figure 2. Gain Adjust

## Offset Adjustment

The offset adjustment must be completed first. Please refer to *Figure 1*. Apply an input voltage of 0.5LSB or 610µV to any multiplexer input. Adjust the offset potentiometer so that the output code fluctuates evenly between 000...000 and 000...001. It is only necessary to observe the lower eight LSB's during this procedure.

## **Gain Adjustment**

With the offset adjusted, the gain error can now be trimmed to zero (see *Figure 2*). The ideal input voltage corresponding to 1.5 LSB's below the nominal full scale input value, or +4.988V, is applied to any multiplexer input. The gain potentiometer is adjusted so that the output code alternates evenly between 111...111 and 111...110. Again, only the lower eight LSB's need be observed during this procedure. With the above adjustment made, the converter is now calibrated.

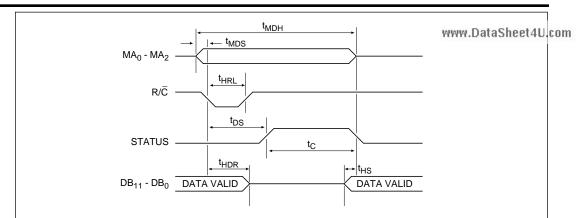

# LOW PULSE FOR R/C DYNAMIC CHARACTERISTICS

$V_{CC} = +15V; V_{LOGIC} = +5V; T_A = 25^{\circ}C$

| PARA             | METER                              | MIN | TYP | MAX | UNIT | CONDITIONS |

|------------------|------------------------------------|-----|-----|-----|------|------------|

| t <sub>hrl</sub> | Low R/C Pulse Width                | 50  |     |     | ns   |            |

| t <sub>os</sub>  | Status Delay from $R/\overline{C}$ |     |     | 200 | ns   |            |

| t <sub>HDR</sub> | Data Valid after R/C Low           | 25  |     |     | ns   |            |

| t <sub>HS</sub>  | Status Delay after Data Valid      | 500 |     |     | ns   |            |

| t <sub>mds</sub> | MUX Data Setup                     | 50  |     |     | ns   |            |

| t <sub>mdh</sub> | MUX Data Valid                     | 3   |     | 10  | μs   |            |

Figure 3. Low Pulse for  $R/\overline{C}$  Timing

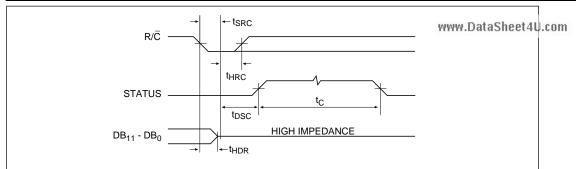

# **CONVERT MODE DYNAMIC CHARACTERISTICS**

$V_{cc} = +15V; V_{LOGIC} = +5V; T_{A} = 25^{\circ}C$

| PAR              | AMETER                 | MIN | TYP | MAX | UNIT | CONDITIONS |

|------------------|------------------------|-----|-----|-----|------|------------|

| t <sub>SRC</sub> | R/C to CE Setup        | 50  |     |     | ns   |            |

| t <sub>HRC</sub> | R/C Low during CE High | 50  |     |     | ns   |            |

| t <sub>DSC</sub> | Status Delay from CE   |     |     | 200 | ns   |            |

Figure 4. Convert Mode Timing

Figure 5. Read Mode Timing

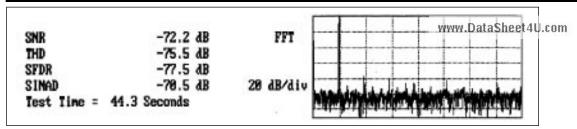

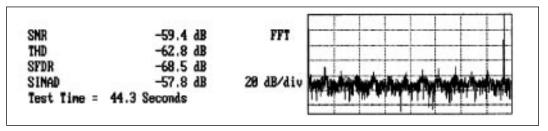

Figure 6. FFT; 6kHz 5V (0dB) Full Scale Input; F<sub>s</sub>=10kHz

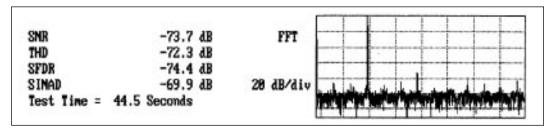

Figure 7. FFT; 12kHz 5V (0dB) Full Scale Input; F<sub>s</sub>=10kHz

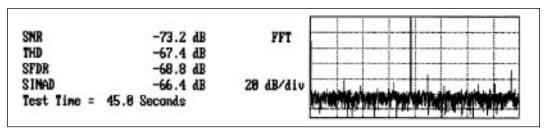

Figure 8. FFT; 24kHz 5V (0dB) Full Scale Input; F<sub>s</sub>=10kHz

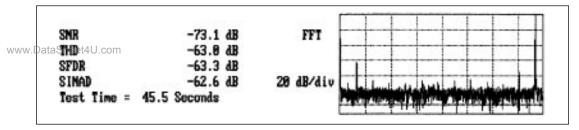

Figure 9. FFT; 48kHz 5V (0dB) Full Scale Input; F<sub>s</sub>=10kHz

Figure 10. FFT; 48kHz 1V (-14dB) Input; F<sub>s</sub>=10kHz

| ORDERING INFORMATION                           |                     |                          |  |  |  |

|------------------------------------------------|---------------------|--------------------------|--|--|--|

| 12-Bit Data Acquisition System with 12-Bit Par | rallel Data Output: |                          |  |  |  |

| Commercial (0°C to +70°C):                     | Non-Linearity       | Package                  |  |  |  |

| SP8480JP                                       | ±1.0LSB INL         | 28-pin, 0.6" Plastic DIF |  |  |  |

| SP8480KP                                       | ±0.5LSB INL         | 28-pin, 0.6" Plastic DIF |  |  |  |

| SP8480JS                                       | ±1.0LSB INL         |                          |  |  |  |

| SP8480KS                                       | ±0.5LSB INL         |                          |  |  |  |

| Industrial (-40°C to +85°C):                   | Non-Linearity       | Package                  |  |  |  |

| SP8480AP                                       | ±1.0LSB INL         | 28-pin, 0.6" Plastic DIF |  |  |  |

| SP8480BP                                       | ±0.5LSB INL         | 28-pin, 0.6" Plastic DIF |  |  |  |

| SP8480AS                                       | ±1.0LSB INL         |                          |  |  |  |

| SP8480BS                                       | ±0.5LSB INL         |                          |  |  |  |

www.DataSheet4U.com

THIS PAGE LEFT INTENTIONALLY BLANK