SPCA533A User Guide

### **DIGITAL STILL CAMERA CONTROLLER**

# Sunplus Camera Solution

June 14, 2002

*Scatch*<sup>™</sup> is a trade mark of Sunplus.

SUNPLUS TECHNOLOGY CO. reserves the right to change this documentation without prior notice. Information provided by SUNPLUS TECHNOLOGY CO. is believed to be accurate and reliable. However, SUNPLUS TECHNOLOGY CO. makes no warranty for any errors which may appear in this document. Contact SUNPLUS TECHNOLOGY CO. to obtain the latest version of device specifications before placing your order. No responsibility is assumed by SUNPLUS TECHNOLOGY CO. for any infringement of patent or other rights of third parties which may result from its use. In addition, SUNPLUS products are not authorized for use as critical components in life support devices/ systems or aviation devices/systems, where a malfunction or failure of the product may reasonably be expected to result in significant injury to the user, without the express written approval of Sunplus.

### SPCA533A

#### Contents

| 1. OPERATIONAL DESCRIPTIONS                                                            | 5  |

|----------------------------------------------------------------------------------------|----|

| 1.1 Operation modes                                                                    | 5  |

| 1.1.1 Preview mode                                                                     | 5  |

| 1.1.2 Capture mode                                                                     | 5  |

| 1.1.3 Continuous shot                                                                  | 6  |

| 1.1.4 Video Clip                                                                       | 6  |

| 1.1.5 Playback                                                                         | 7  |

| 1.2 GLOBAL                                                                             | 7  |

| 1.2.1 Clocks                                                                           |    |

| 1.2.2 Power On Sequence                                                                |    |

| 1.2.3 Suspend/resume control                                                           |    |

| Sensor interface                                                                       |    |

| RTC                                                                                    |    |

| USB interface                                                                          |    |

| 1.2.4 Power Saving Consideration                                                       | 14 |

| 1.2.5 User Interface                                                                   |    |

| 1.2.6 Global Timer Control                                                             |    |

| 1.2.7 RTC                                                                              |    |

| 1.2.8 Pattern Generator                                                                |    |

| 1.2.9 Interrupt Events                                                                 |    |

| 1.3 CDSP                                                                               |    |

| 1.3.1 Image size limitation                                                            |    |

| 1.3.2 Horizontal Mirror on Raw Data                                                    |    |

| 1.3.3 Horizontal Scale Down on Raw Data                                                |    |

| 1.3.4 Hardwired Color Processor                                                        |    |

| 1.4 DMA CONTROLLER                                                                     |    |

| 1.4.1 Direction of the DMA<br>1.4.2 Page size adjustment of the DMA                    |    |

| 1.4.2 Page size adjustment of the DMA<br>1.4.3 Matching pattern in DMA                 |    |

| 1.4.5 Matching patient in DWA                                                          |    |

| 1.5 STORAGE MEDIA                                                                      |    |

| 1.5.1 PIO mode and DMA mode                                                            |    |

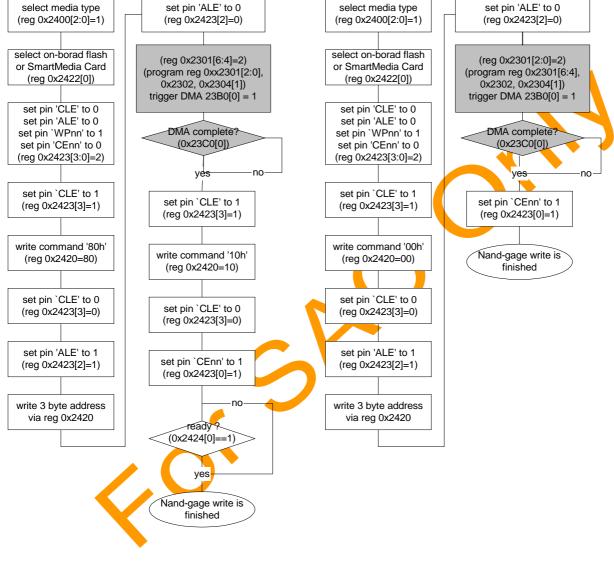

| 1.5.2 Nand-gate flash memory and SmartMediaCard                                        |    |

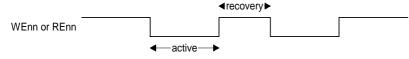

| 1.5.2 Nand-gate flash memory and smartineau Cara<br>1.5.3 CompactFlash cards interface | 40 |

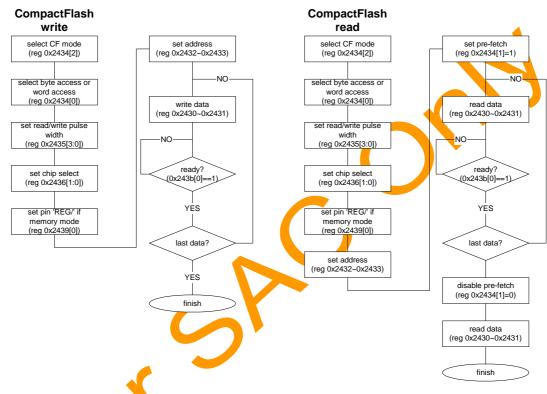

| 1.5.5 Compact tash curas interface<br>1.5.4 SPI interface to the Serial flash memory   |    |

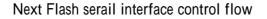

| 1.5.5 Next flash serial interface control                                              |    |

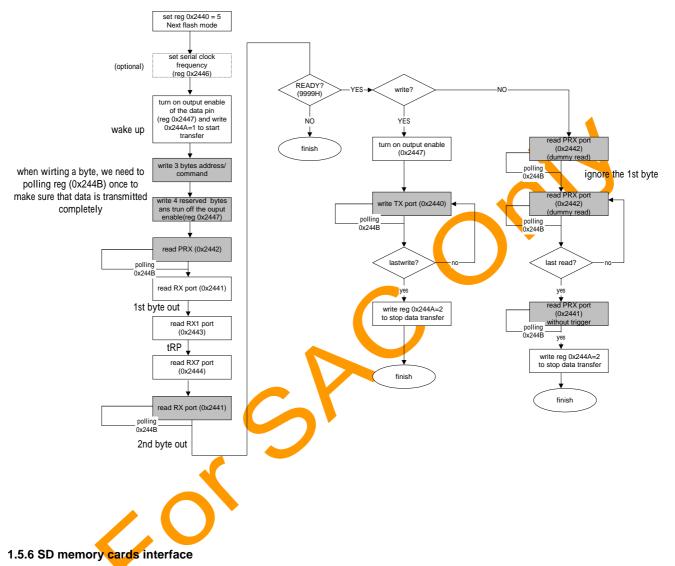

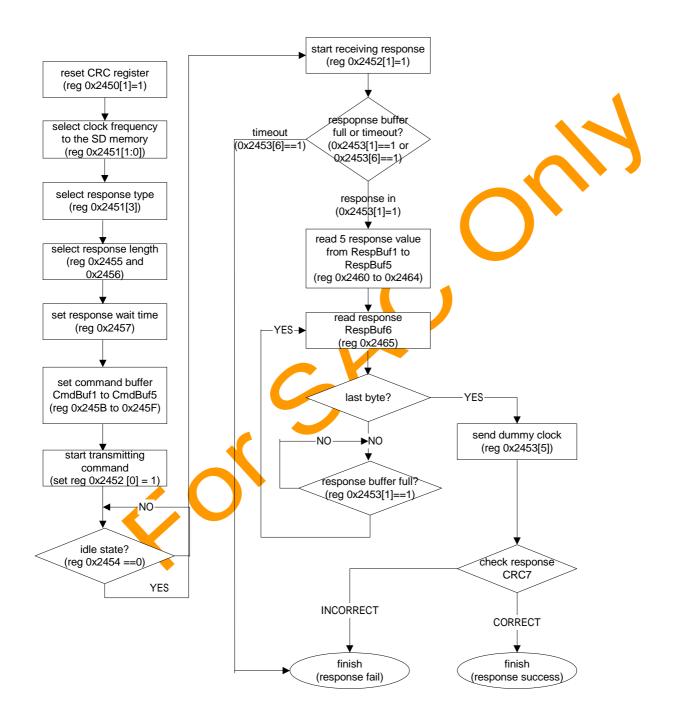

| 1.5.6 SD memory cards interface                                                        |    |

| 1.5.7 The ECC generation                                                               |    |

| 1.6 JPEG ENGINE                                                                        |    |

| 1.6.1 Quantization table                                                               |    |

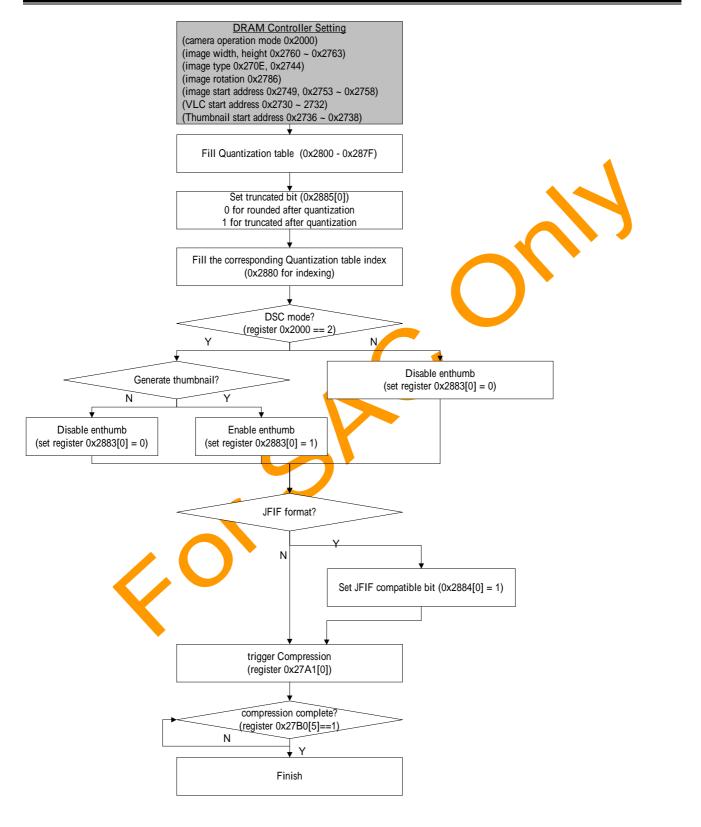

| 1.6.2 JPEG compression                                                                 |    |

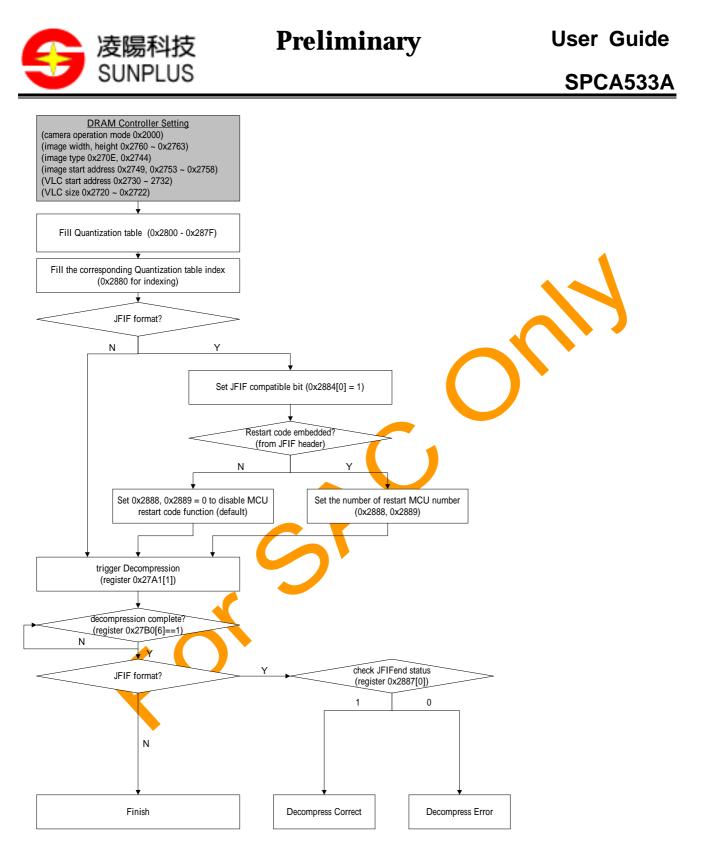

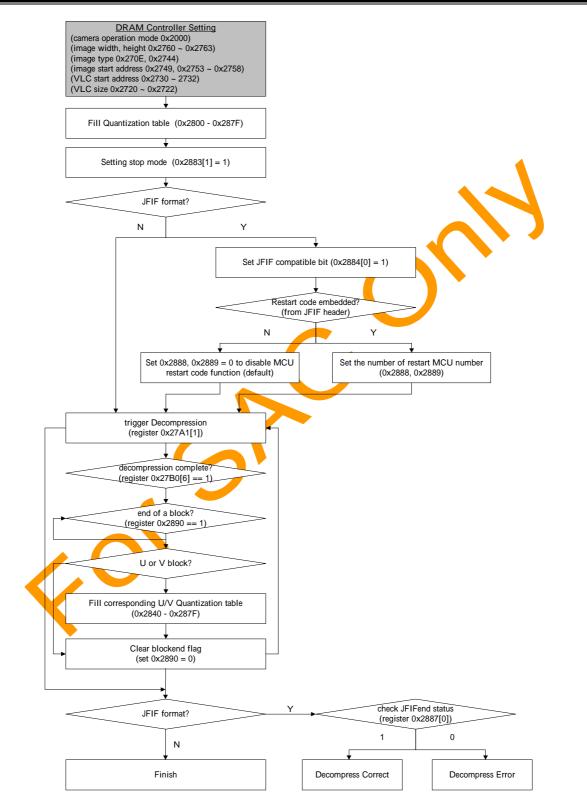

| 1.6.3 JPEG decompression                                                               |    |

| 1.7 USB BUS INTERFACE                                                                  |    |

| 1.7.1 USB Vendor Command                                                               |    |

| 1.7.2 USB Packet Format                                                                |    |

| 1.7.2.1 USB Video Iso-in Packet (endpoint 1)                                           |    |

| 1.7.2.2 USB BULK-IN Packet (endpoint 2, 7)                                             |    |

| 1.7.2.3 USB BULK-OUT Packet (endpoint 3, 8)                                            | 61 |

| 1.7.2.4 USB Interrupt-IN Packet (endpoint 4, 9)                                        | 61 |

| 1.7.2.5 Audio INTERRUPT-IN pipe (endpoint 5)                                           | 61 |

|                                                                                        |    |

Jun. 14, 2001 Preliminary Version: 0.2.0

### **User Guide**

### SPCA533A

| 1.7.2.6 Audio ISO-IN Pipe (endpoint 6)                                 | 61 |

|------------------------------------------------------------------------|----|

| 1.7.3 Bulk-Only Protocol Support                                       | 62 |

| 1.7.4 Waking up the camera by the USB plug in/out                      | 64 |

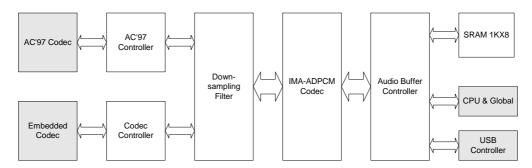

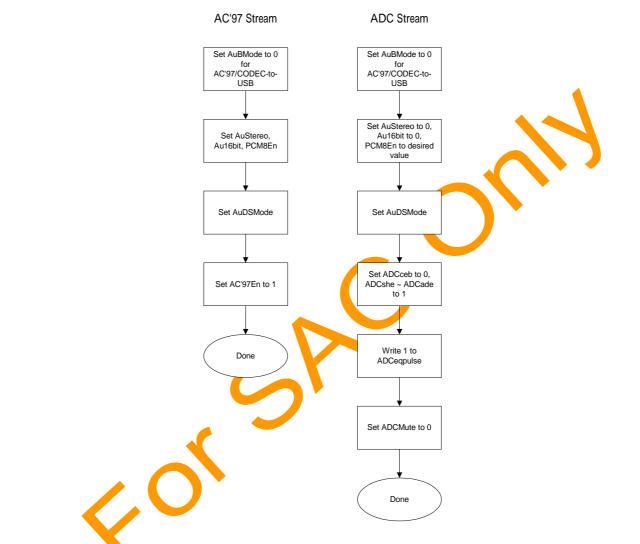

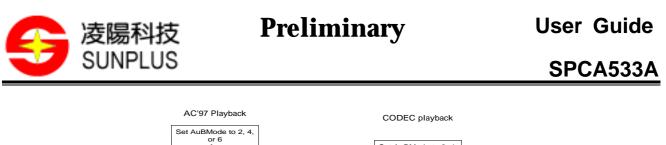

| 1.8 AUDIO FUNCTION                                                     |    |

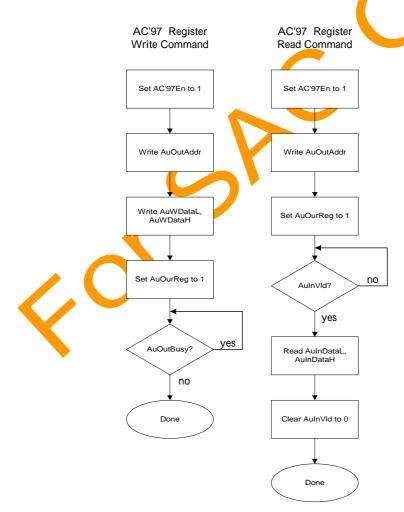

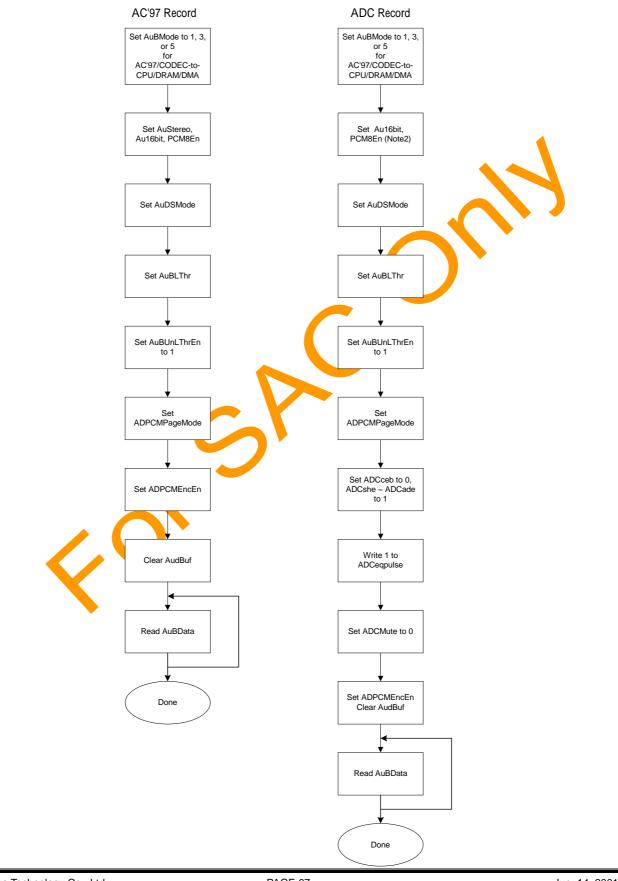

| 1.8.1 AC '97 Controller                                                | 65 |

| 1.8.2 Codec Controller                                                 | 65 |

| 1.8.3 Down-sampling Filter                                             |    |

| 1.8.4 ADPCM Codec                                                      |    |

| 1.8.5 Audio Buffer Controller                                          |    |

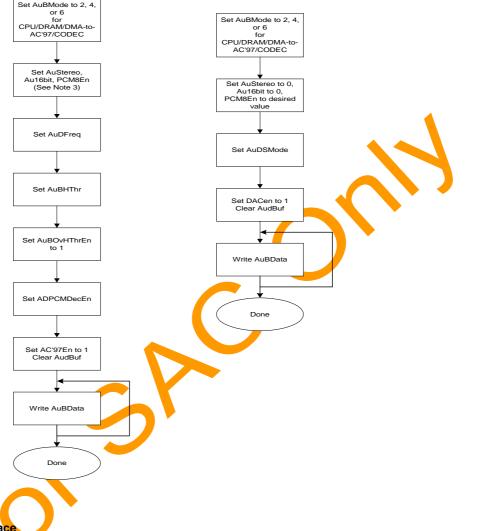

| 1.8.6 MP3 Processor Interface                                          | 69 |

| 1.8.7 Programming flow of the MP3 processor serial interface           |    |

| 1.9 SDRAM CONTROLLER                                                   | 71 |

| 1.9.1 SDRAM initialization                                             |    |

| 1.9.2 SDRAM refresh                                                    |    |

| 1.9.3 CPU access SDRAM                                                 |    |

| 1.9.4 Filling constant data to the SDRAM                               |    |

| 1.9.5 Interface with DMA controller                                    |    |

| 1.9.6 Image data input control                                         |    |

| 1.9.7 Data format                                                      |    |

| 1.9.8 JPEG interface                                                   |    |

| 1.9.9 Thumbnail generation                                             |    |

| 1.9.10 Image-Processing engine                                         | 76 |

| 1.9.10.1 Image-scaling operation                                       | 76 |

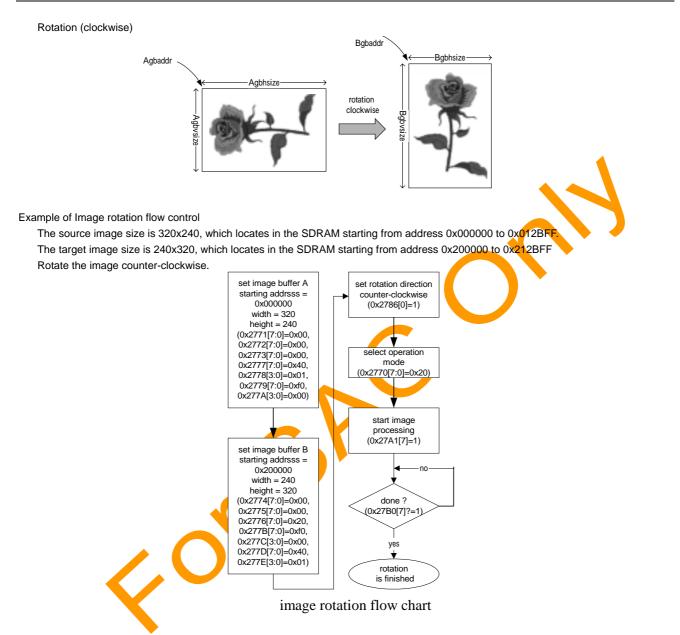

| 1.9.10.2 Image rotation operation                                      |    |

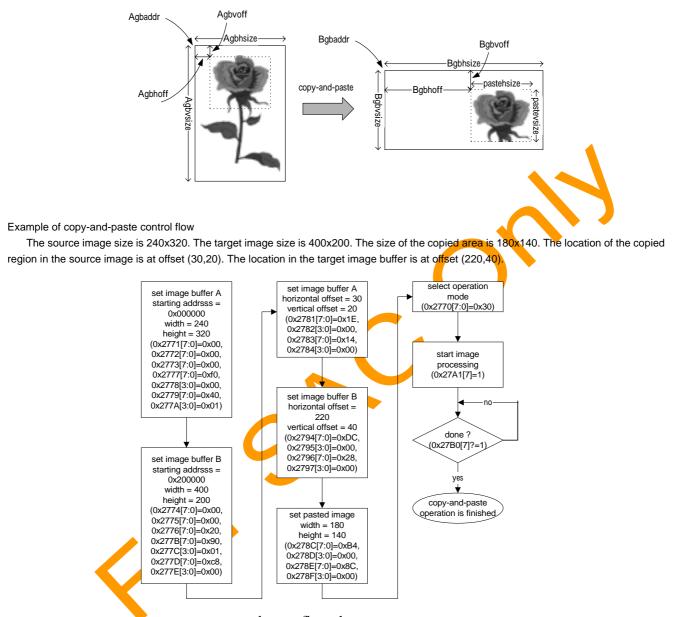

| 1.9.10.3 Copy & paste operation                                        | 79 |

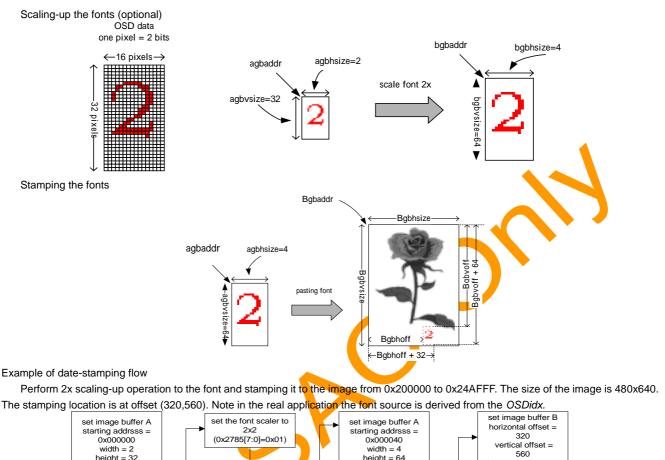

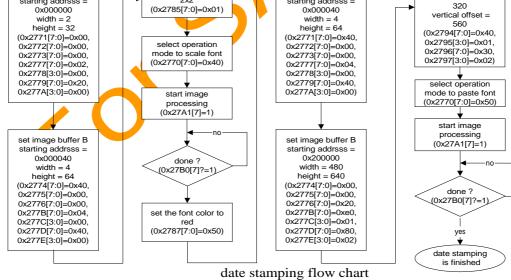

| 1.9.10.4 Date stamping operation                                       |    |

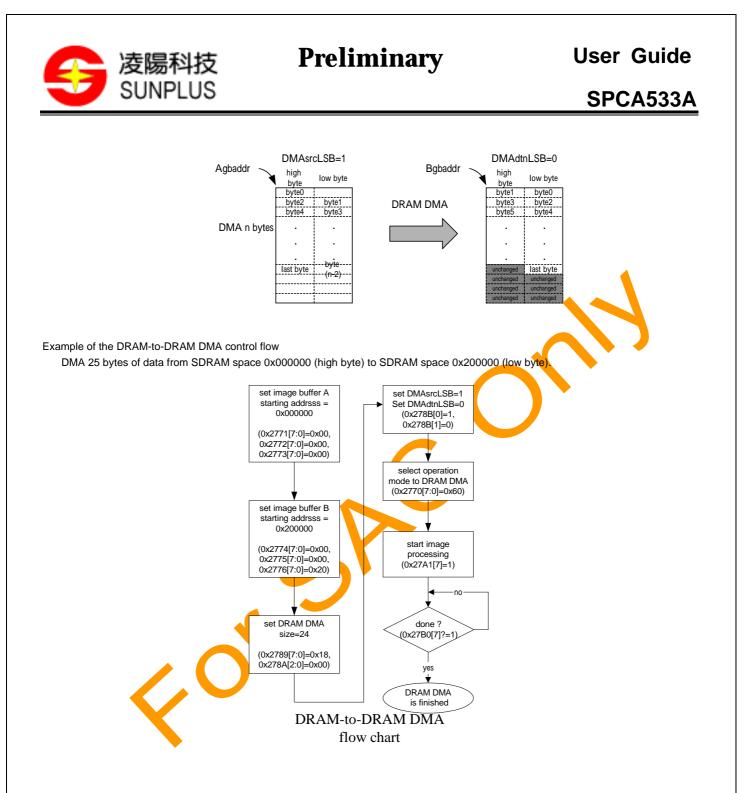

| 1.9.10.5 DRAM-to-DRAM DMA operation                                    |    |

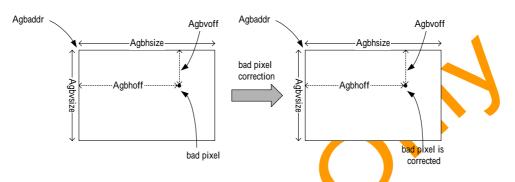

| 1.9.10.6 Bad-Pixel correction                                          |    |

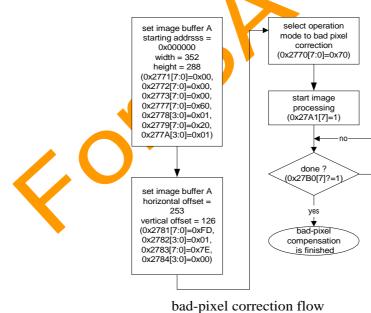

| 1.9.10.7 Inter-frame raw data subtraction operation                    |    |

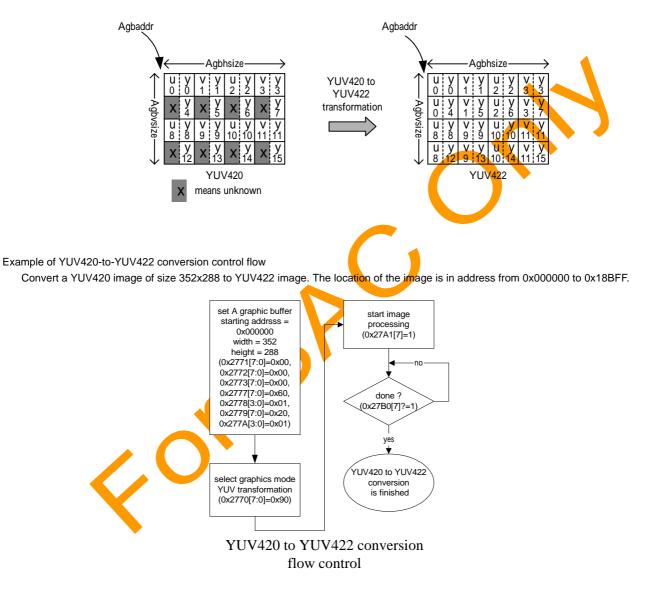

| 1.9.10.8 YUV420-to-YUV422 conversion                                   |    |

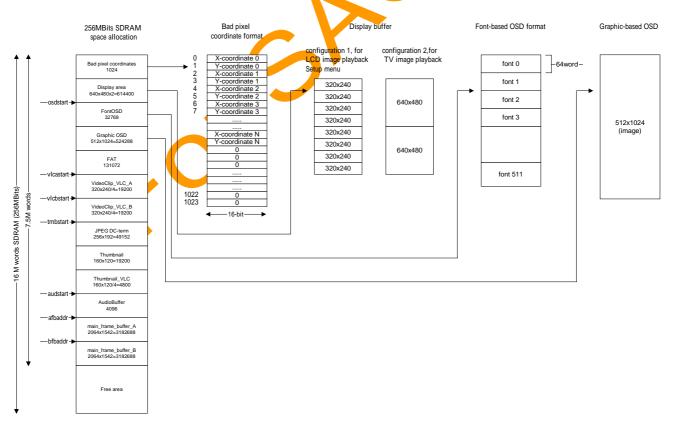

| 1.9.11 SDRAM space partition in <mark>di</mark> fferent operation mode |    |

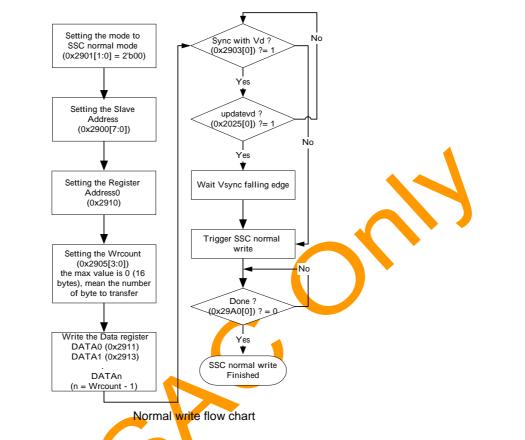

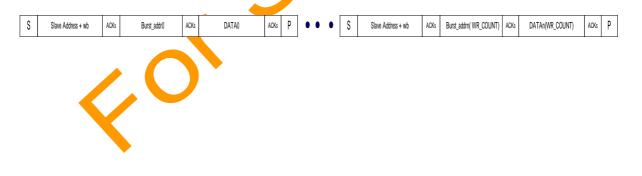

| 1.10 Serial interface                                                  | 93 |

| 1.10.1 Synchronous Serial interface (SSC)                              |    |

| 1.10.2 Three-wire interfa <mark>ce</mark>                              |    |

| 1.10.3 Manual control of the serial interface                          |    |

| 1.11 TV-IN / CMOS SENSOR INTERFACE                                     |    |

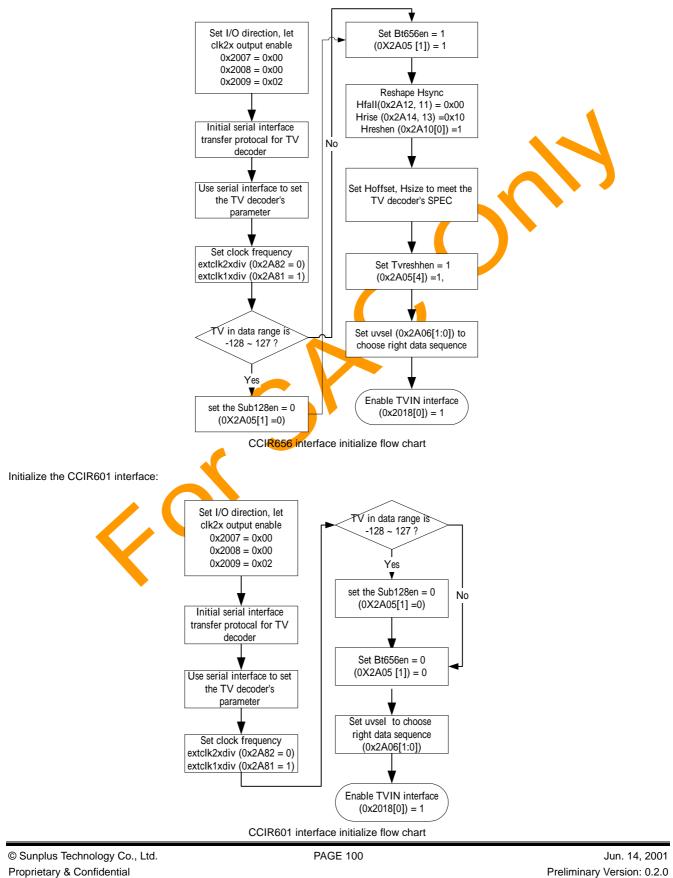

| 1.11.1 TV input interface                                              |    |

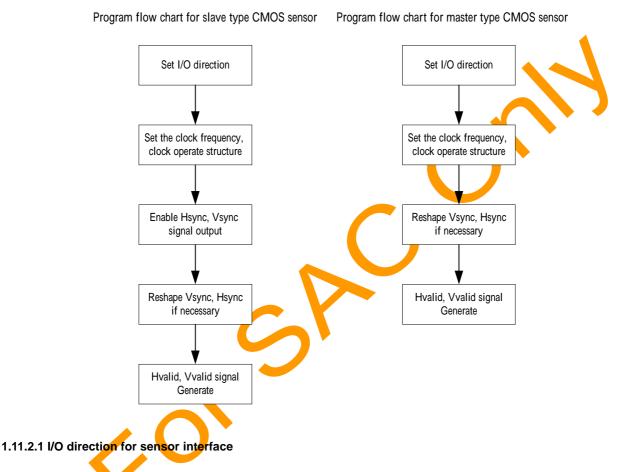

| 1.11.2 CMOS inte <mark>rfac</mark> e                                   |    |

| 1.11.2.1 I/O direction for sensor interface                            |    |

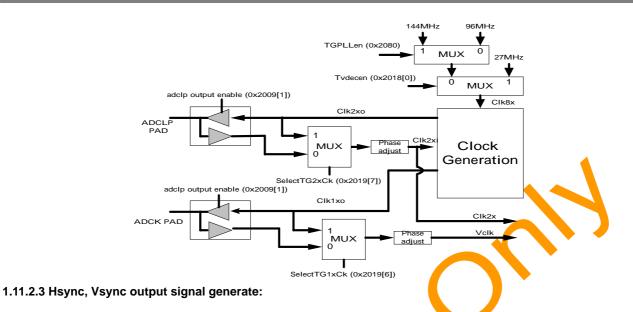

| 1.11.2.2 Clock system for sensor interface                             |    |

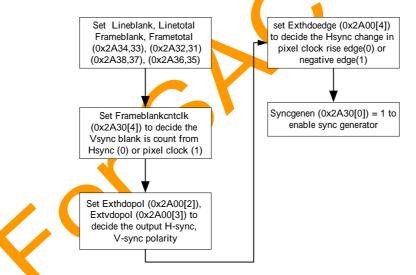

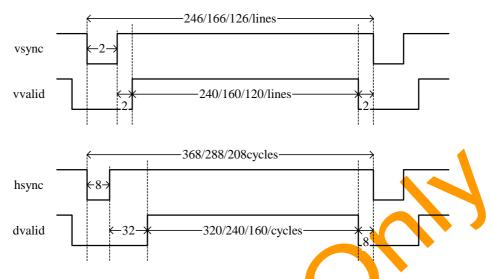

| 1.11.2.3 Hsync, Vsync output signal generate:                          |    |

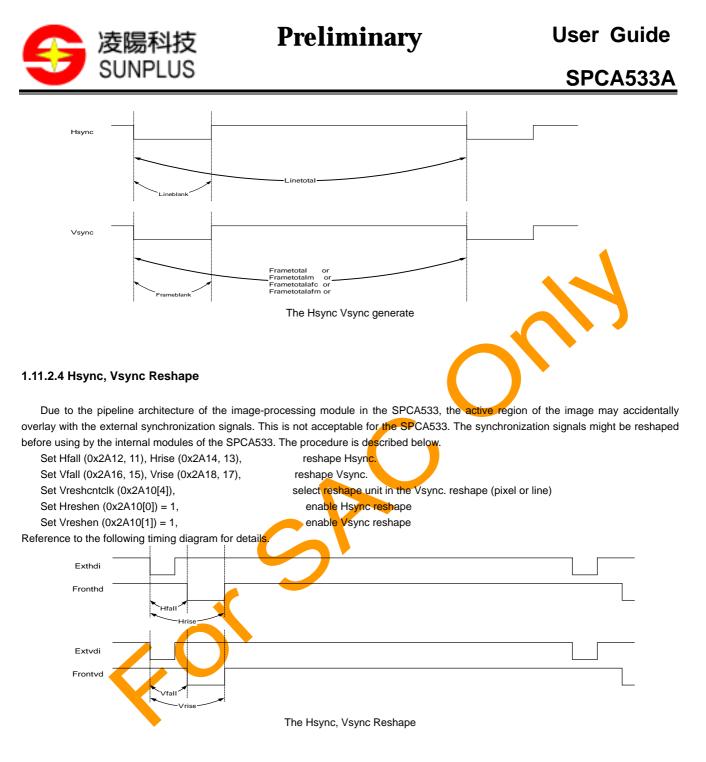

| 1.11.2.4 Hsync, Vsync Reshape                                          |    |

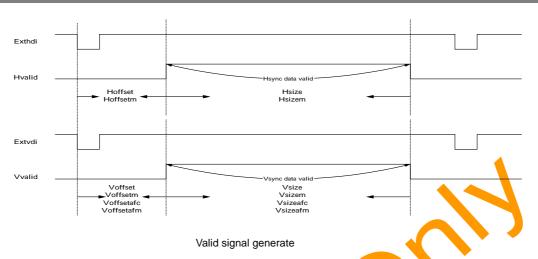

| 1.11.2.5 Hvalid, Vvalid generation                                     |    |

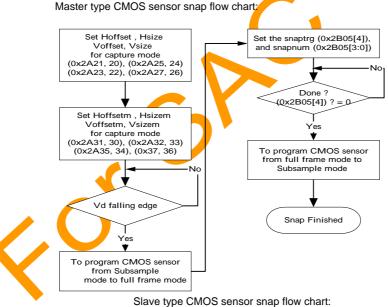

| 1.11.3 Image Capture:                                                  |    |

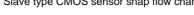

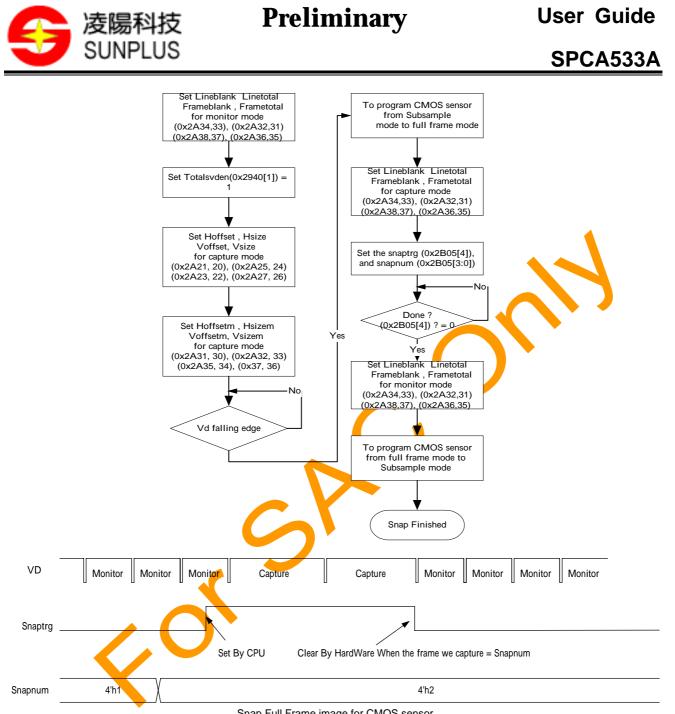

| 1.11.4 Flash light control for CMOS sensor                             |    |

| 1.11 CCD INTERFACE.                                                    |    |

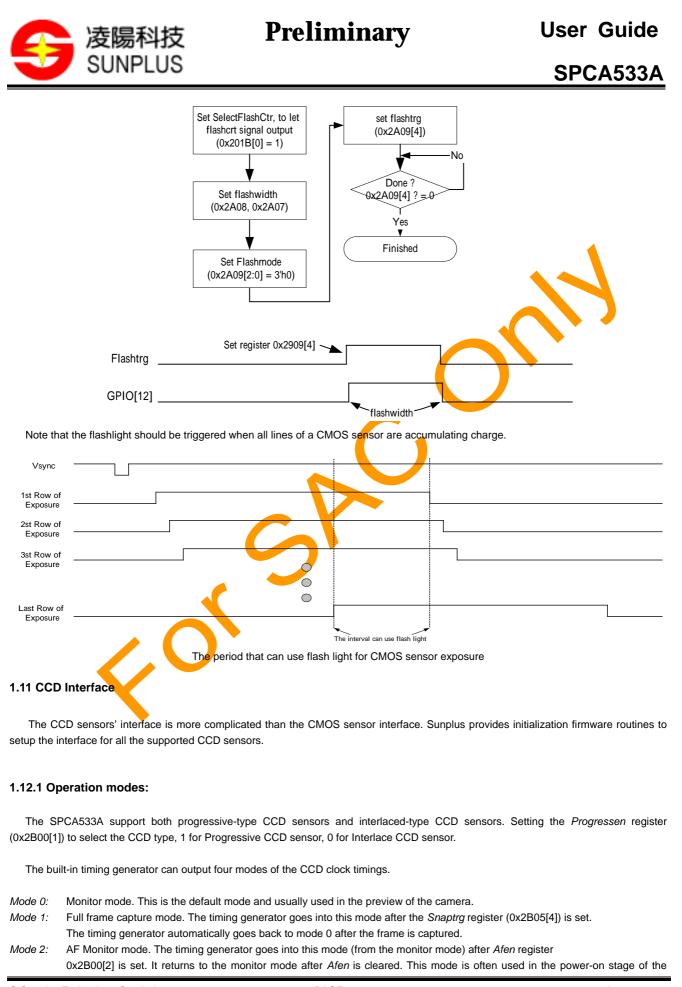

| 1.12.1 Operation modes:                                                |    |

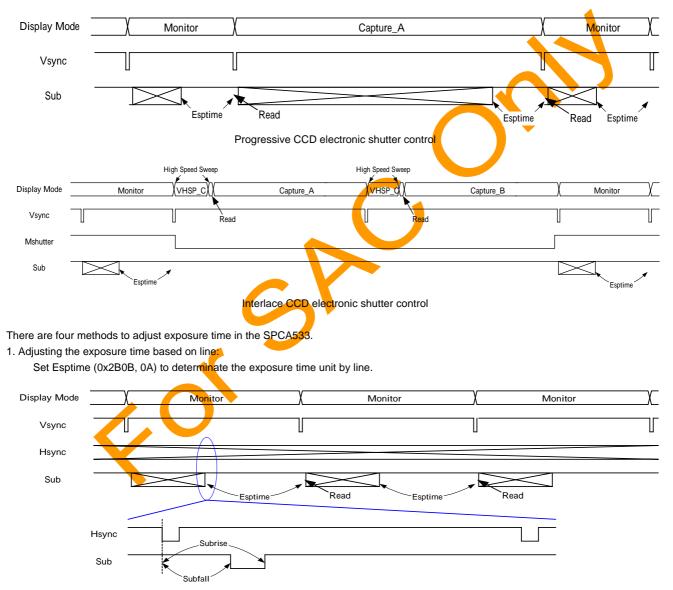

| 1.12.2 Electronic shutter control                                      |    |

| 1.12.3 Mechanical shutter control                                      |    |

| 1.12.4 Flash light control for the CCD sensor                          |    |

| 1.12.5 Image capture                                                   |    |

| 1.13 EMBEDDED MICRO-CONTROLLER                                         |    |

| 1.13.1 Hardware interface                                              |    |

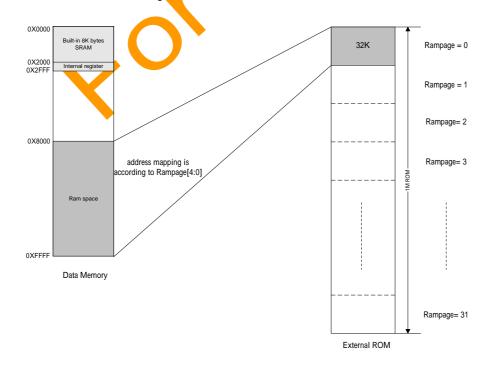

| 1.13.2 RAM space                                                       |    |

|                                                                        |    |

Jun. 14, 2001 Preliminary Version: 0.2.0

### **User Guide**

### SPCA533A

| 1.13.3 ROM space                                                       |  |

|------------------------------------------------------------------------|--|

| 1.13.4 ISP (In-system-programming)                                     |  |

| 1.13.5 The difference between the standard 8032 and the embedded 8032  |  |

| 1.13.6 Suspend state power control of CPU                              |  |

| 1.14 TV OUTPUT INTERFACE                                               |  |

| 1.14.1 Analog TV interface (tvdspmode=0~1, register 0X2D00)            |  |

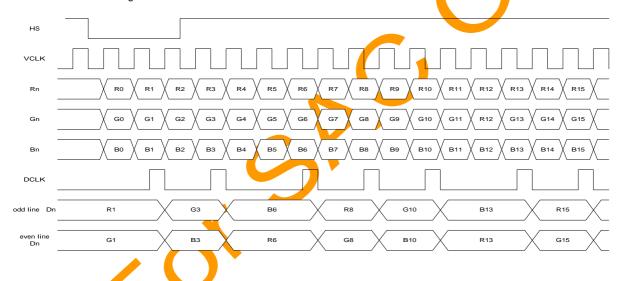

| 1.14.2 Digital TV interface                                            |  |

| 5.14.2.1 CCIR 656 interface (dspmode=2~3, register 0X2D00)             |  |

| 5.14.2.2 CCIR 601 interface (tvdspmode=4~7, register 0X2D00)           |  |

| 1.14.2.3 Unipac UPS051 (TFT-LCD interface, dspmode=8, register 0X2D00) |  |

| 1.14.2.4 EPSON D-TFD LCD interface (tvdspmode=10, register 0X2D00)     |  |

| 1.14.2.5 CASIO TFD LCD interface (tvdspmode=11, register 0X2D00)       |  |

| 1.14.2.6 GIANTPLUS STN-LCD interface (tvdspmode=12, register 0X2D00)   |  |

| 1.14.2.7 PRIME VIEW TFT-LCD interface (tvdspmode=14, register 0X2D00)  |  |

| 1.14.2.8 User define output interface (tvdspmode=15, register 0X2D00)  |  |

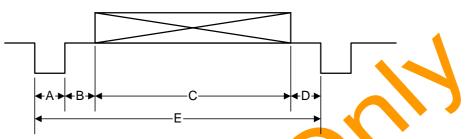

| 1.14.2.9 Horizontal and Vertical Timing and Corresponding Register     |  |

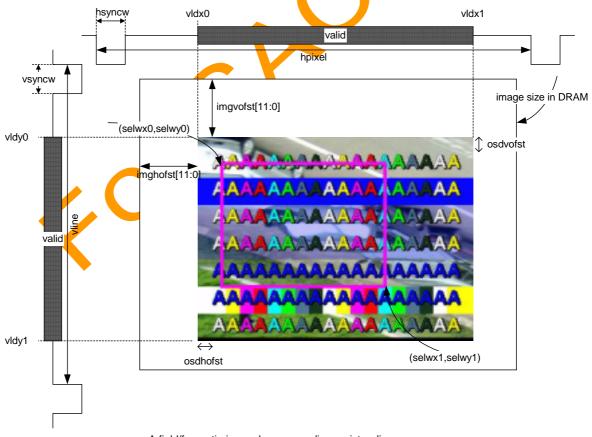

| 1.14.3 On Screen Display (OSD)                                         |  |

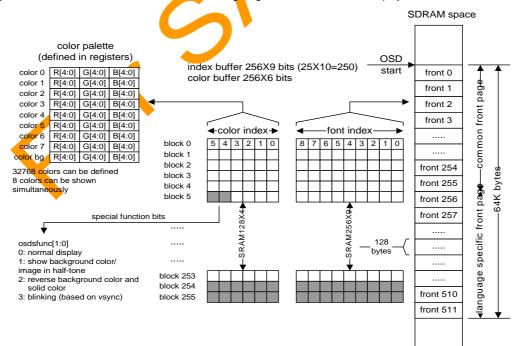

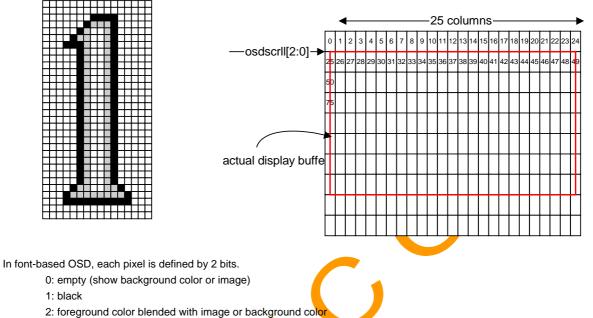

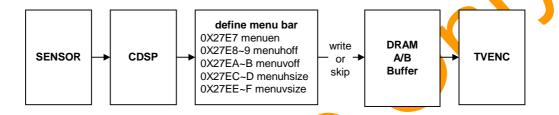

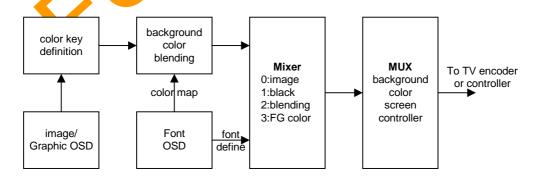

| 1.14.3.1 Font-Based OSD                                                |  |

| 1.14.3.2 graphic-based OSD                                             |  |

| 1.14.4 Gamma correction                                                |  |

| 1.14.4 vertical and horizontal scaling function                        |  |

| 2. REGISTER DESCRIPTIONS                                               |  |

| 2.1 REGISTER CATEGORY                                                  |  |

| 2.2 GLOBAL REGISTERS                                                   |  |

| 2.3 CDSP Registers                                                     |  |

| 2.4 CDSP WINDOW REGISTERS                                              |  |

| 2.5 DMA Controller Registers                                           |  |

| 2.6 FLASH MEMORY CONTROL REGISTERS                                     |  |

| 2.7 USB Control Registers                                              |  |

| 2.8 Audio Control Registers                                            |  |

| 2.9 SDRAM CONTROL REGISTERS                                            |  |

| 2.10 JPEG CONTROL REGISTERS                                            |  |

| 2.11 SERIAL INTERFACE CONTROL REGISTERS                                |  |

| 2.12 TV-IN / CMOS SENSOR CONTROL REGISTER                              |  |

| 2.13 CCD CONTROL REGISTERS                                             |  |

| 2.14 CPU Control Registers                                             |  |

| 2.15 TV OUTPUT INTERFACE REGISTERS                                     |  |

| 3. APPLICATION/USAGE DESCRIPTIONS (BY FAE)                             |  |

|                                                                        |  |

| REVISION HISTORY                                                       |  |

### **User Guide**

#### SPCA533A

#### 1. Operational Descriptions

#### 1.1 Operation modes

The main operation modes of the SPCA533A are *preview, capture, videoclip* and *playback* modes. These modes are mutually exclusive. The SPCA533A can only operated in one of these modes at a time. There are many tasks that can be excuted concurrently with these modes. For example, data transfer between the PC and the camera can take place while the camera is in any of these operation modes. Also, data transfer between the camera and the storage media can also be performed while the SPCA533A is operated in any operation modes. These concurrence operations are useful when the application need to put the time-consuming tasks to the background execution.

#### 1.1.1 Preview mode

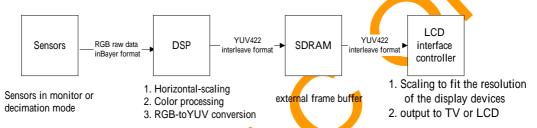

In the preview mode, the SPCA533A receives raw image data from the sensor. It processes the data in real time with the CDSP (Color DSP) and stores the data in the frame buffer of the SDRAM. Then, the data is read from the SDRAM and sent to the display device. The SPCA533A supports TFT LCD panels, STN LCD panels, digital TV output and analog TV output. The following diagram demonstrates the data flow in the preview mode.

The sensor's fame rate are normally adjusted to 30 fps in the preview mode. For the CCD sensors, the user need to adjust the parameters in the built-in timing generator to make the SPCA533A drive out 30 fps timing. For the CMOS sensors, the frame rate may be dominated by the SPCA533A or by the sensors, depending on the operation mode of the CMOS sensors. If the CMOS sensors is operated in the master mode, the SPCA533A programs the internal registers of the sensors to control the timing. On the other hand, if CMOS sensors is operated is operated in the slave mode, the users need to adjust the parameters in the CMOS interface controller of the SPCA533A to control the frame rate. Mega-pixel sensors usually supports monitor mode (CCD) or decimation mode (CMOS) to allow the pixel data to be read at 30 fps frame rate.

The SPCA533A provides many programmable parameters in the CDSP to achieve the best image quality. The image is horizontally scaled-down by the CDSP, too. The horizontal scaling-down function in the DSP not only reduces the bandwidth requirement of the SDRAM but also maintain the appropriate aspect ratio of the image in a CCD system. For example, if the a CCD sensor vertically subsampled the image by 4, then the CDSP will need to scale down the image horizontally by 4 to maintain the correct aspect ratio. After color processing, the CDSP convert the image data from the RGB domain to the YUV domain. The AE (auto-exposure) and AWB (auto-white balance firmware) algorithm is executed at the background in the preview mode. The CDSP provides statistics on the image data for the AE/AWB algorithm's reference.

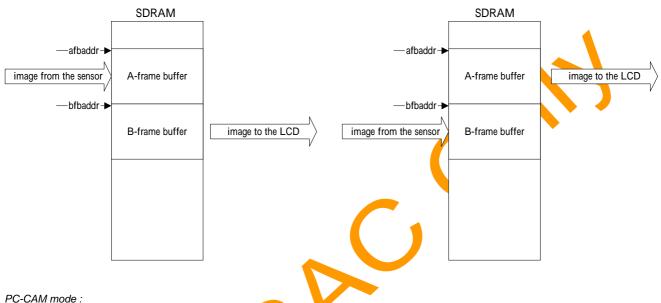

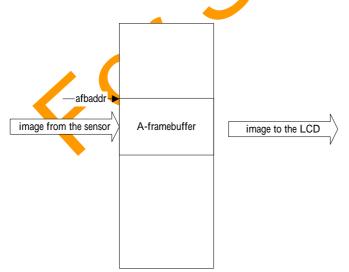

The data stored in the SDRAM is in YUV422 format. The SDRAM controller maintains two frame buffers to convert the frame rate if the sensor's frame rate is different from the frame rate of the display device.

To fit a wide range of the resolutions of the display devices, The LCD/TV interface controller has built-in scaling function. The scaling ratio of the LCD/TV scaling function can be adjusted independently in the vertical direction and the horizontal direction. However, it is important to maintain the appropriate aspect ratio of the original image. For TV output, the PAL frame rate fixed at 25 fps, the NTSC is 30fps. The frame rates of the LCD panels are usually fiexed by the panel makers.

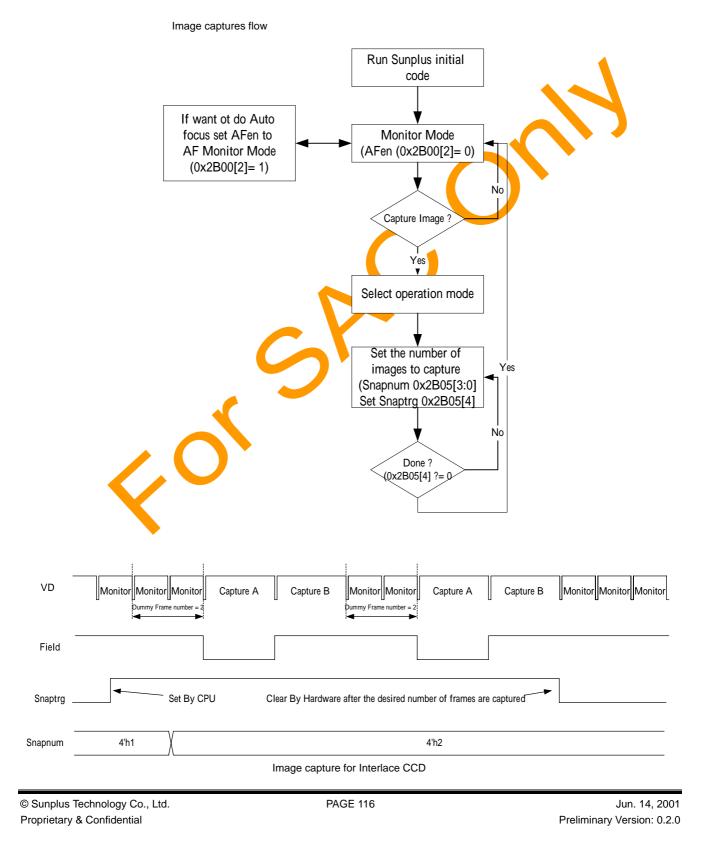

#### 1.1.2 Capture mode

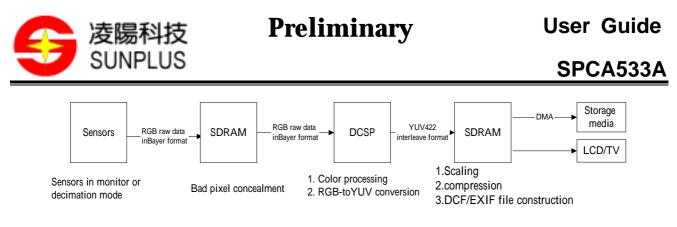

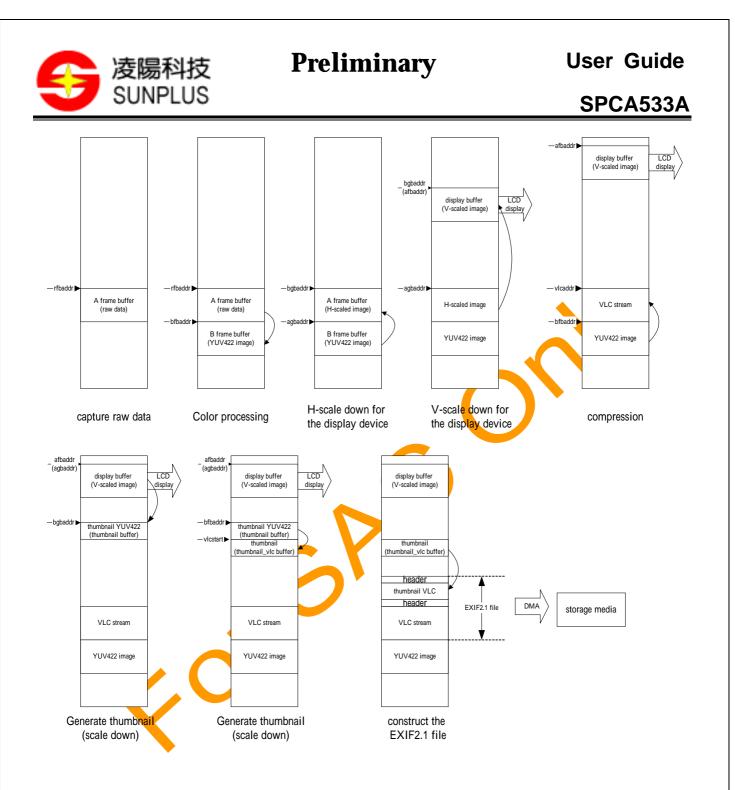

The capture mode allows the user to capture image output from the sensors. Depending on the setting of the camera, the SPCA533A is able to capture a single image, multiple images and video. The simplest flow is the single image capture. The following diagram shows the data flow of snapping a single image.

In the capture mode, the sensor should be operated in the full resolution mode. This requires adjusting the parameters in the timing generator in the CCD system. In the CMOS system, the sensor's control registers must be adjusted accordingly.

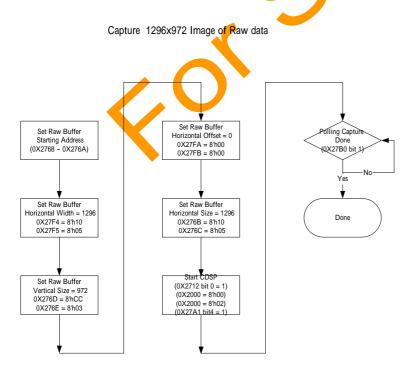

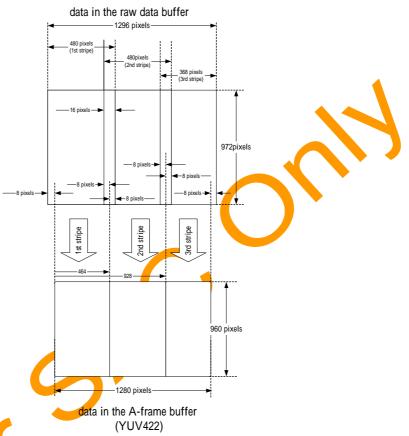

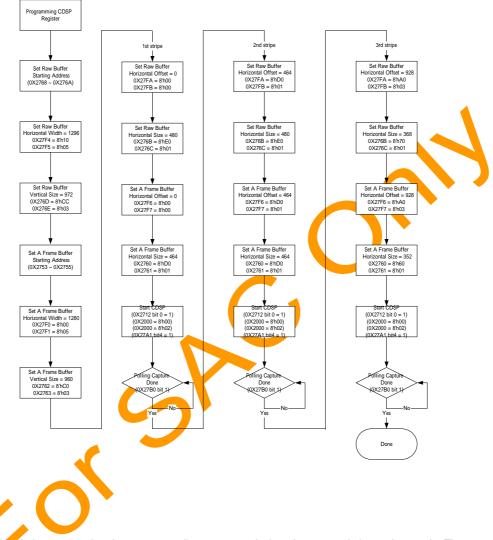

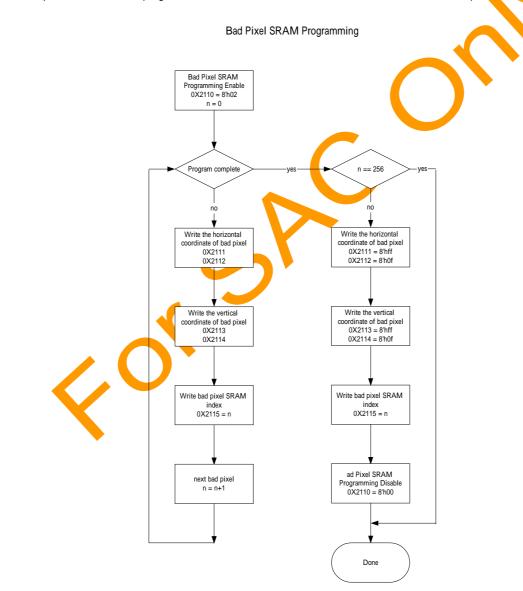

The RGB raw data (in Bayer pattern format) is stored in the SDRAM frame buffer without any image processing. Only optical black value is measured when the data is written into the SDRAM. For interlace CCD sensors, the data sequnce of the image data is re-arranged at the same time when the raw data is written into the SDRAM. This is necessary because the this type of sensors separate the image into R-field and B-field. Also, 12 extra lines must be captured. This is necessary for the color processing in the SPCA533. For example, to get a 1280 by 960 final image, the users must capture a 1296 by 972 image first. Some sensors might not have enough number of valid pixels to meet the requirement of the SPCA533's color processing. An altenative approach is to mirror the image at the boundaries of the incoming data. Please reference to the CDSP section for details. The bad pixel concealment can be done in the SDRAM before color processing. The coordinates of the bad pixels are usually stored in the external ROM. The SPCA533A has built-in a hardwired engine for the bad pixel concealment to speed up this step.

After bad pixel concealment, the data is sent to the CDSP for color processing. In the color processing, the optical black value measure in the previous step is used. The color processing can be done many times with different parameter setting of the CDSP. This is useful when the flash light is applied to the image in which the preview mode AE/AWB window statistics cannot be used in the image precessing.

After the image processing, the image is converted into YUV422 format and stored in the SDRAM again. The YUV422 image may be optionally scaled to the desired size. This step is necessary when the image is digitally zoomed or when a lowe resolution image is required. The scale function can be used to generate the thumbnail data too. If a *quick-view of the* snapped image is requires, the YUV422 image should be scaled to fit the resolution of the display device before viewing. Image compression and file format (EXIF2.1, DCF) construction are also done in the SDRAM. The SPCA533's JPEG engine process only the VLC stream. If the users intend to generate the DCF/EXIF file, the header must be generated and combined in the SDRAM. The files is then saved to the storage media via the SPCA533's built-in DMA controller. The file saing can be execured in the background, meaning the SPCA533A may switch back to the preview mode before the file is not completed written to the storage media.

#### 1.1.3 Continuous shot

The continuous shot is also supported by the SPCA533. To minimize the time interval between frame, the multiple raw images are stored in the SDRAM before any processing. The size of the SDRAM determines the maximum number of the raw images in the continuous shot. The maximum frame rate in the continuous shot is the maximum frame rate of the sensors. After the required raw images are captured, they are process one by one. The precessing includes bad pixel concealment, all the color processing, scaling, compression, and file saving. It is exactly the same as snapping a single image.

In the CCD system, there is usually an exposure frame between data dumping frames. In the exposure frame, no data is read out from the sensos. This exposure frame can be used to perform CDSP color processing. In this case, the overall performace of the continuous shot will be improved. Also the images after CDSP color processing can be sent to the display device. The SPCA533's LCD/TV controller can only display the iamge in YUV422 format. RGB data can not be viewed.

There are many possibilities for the display in the continuous shot. The snapped image can be shown one by one on the LCD(or TV) after they are captured. Alternatively, the thumbnails can be shown together. This is up to the system application.

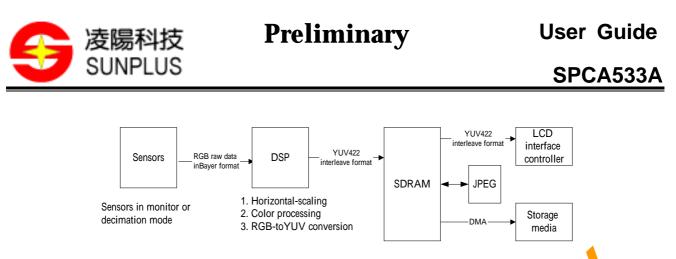

#### 1.1.4 Video Clip

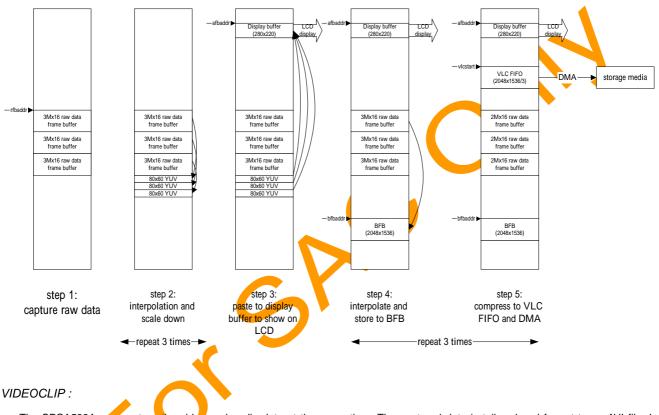

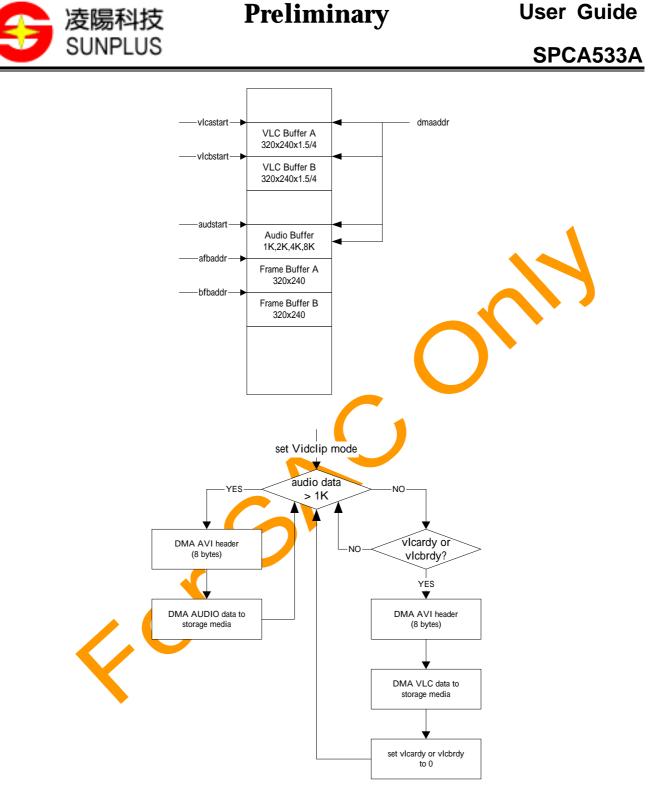

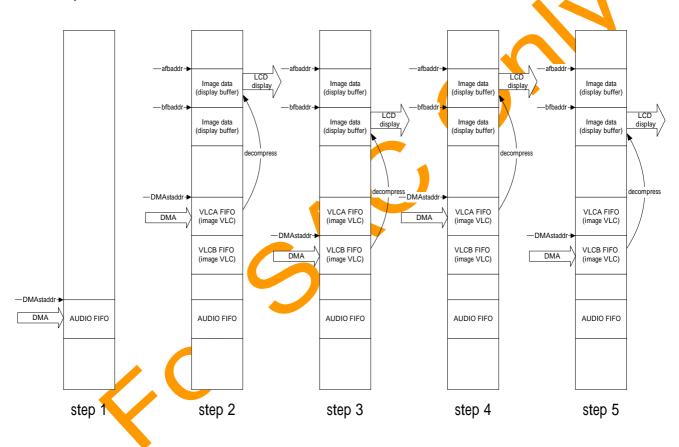

The video capture function operates similar to the preview mode, except that the data in the SDRAM is sent to the JPEG engine for compression and tehn stored in the storage media. The bandwidth requirement in the videoclip is the highest among all the operations of the SPCA533. To construct a video file of the AVI format, the firmware must maintain the header of the AVI. The following diagram shows the data flow of the videoclip.

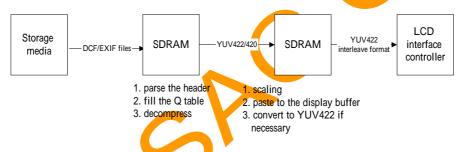

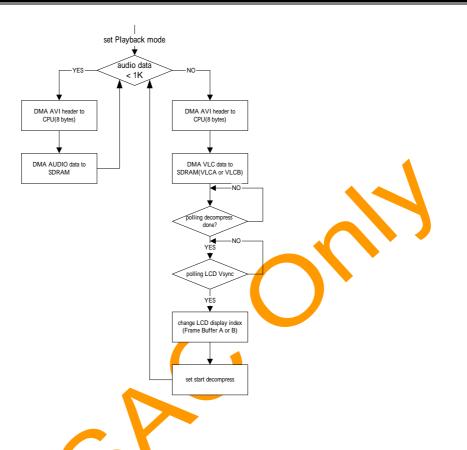

#### 1.1.5 Playback

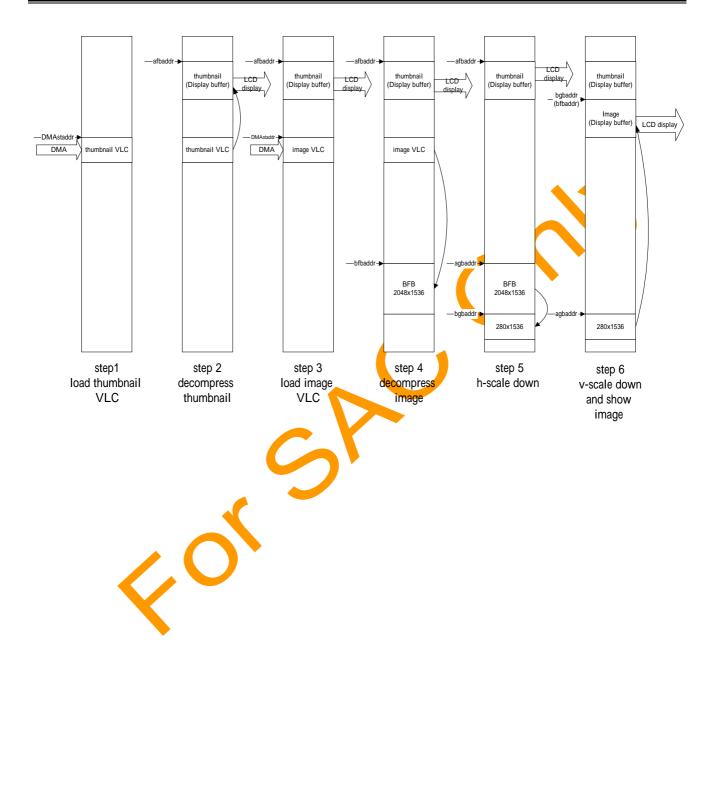

In the playback mode, the SPCA533A fetches the compressed image in the storage media. The headers of the image files are parsed by the firmware. The JPEG quantization table must be programmed before decompression starts. The decomressed image is written into the display buffer for viewing. For mega-pixel sensors, the image normally needs to be scaled dwon before sending to the display devices because the resolution of the display device is smaller than the resolution of the images. The SPCA533A can display multiple images at the same time, too. When this feature is to be implemented, thumbnail images can be used to speedup the playback. Aslo the *copy&past* engine in the DRAM controller can help the firmware to construct the image in the display buffer. The LCD/TV interface controller can only display YUV422 image. If the original file is in YUV420 format, it must be converted to YUV422 format beore viewing. The following diagram is the data flow in the playback mode.

Decompressing a full-size image may take some time, depending on the image resolution. The bottoleneck is often located in the access speed of the storage media. Another approach in the playback mode is to decompress and display the thumbnail image first (resolution 160 by 120). The decompression of the full-size image can be done in the background while the users are viewing the thumbnails. Displaying the thumbnail image requires the LCD/TV interface to scale up the image. This can be done by adjusting the scale factors of the LCD/TV interface controller. Once the full size image is decompressed and scaled to the appropriate size, the firmware may switch the display buffer to display the image of better quality.

#### 1.2 Global

#### 1.2.1 Clocks

The SPCA533A connects to three external crystals. The first one (RTC crystal) is 32.768KHz, which is used in the built-in RTC module. This crystal could be spared when the RTC module is not used. The second crystal (TV crystal) is 27 MHz. This crystal is necessary when the SPCA533's built-in video CODEC is used. The third crystal (USB crystal) is to provide the main operating frequency of the SPCA533. The main operating frequency is generated by the main phase lock loop (MPLL). The input clock frequency of the MPLL could be 6MHz, 12MHz, or 24 MHz, depending on the IO-trap values. To reduce the counts of the external components, the SPCA533's MPLL can also take the 27MHz clock as its input source. This configuration is selected by a dedicated input pin. The following table lists the main clock settings.

| Onextal<br>Pin-B13(280), pin-134(216) | IO-trap{4:3} | USB crystal | TV crystal |

|---------------------------------------|--------------|-------------|------------|

| 0                                     | 0            | 6MHz        | NC         |

| 0                                     | 1            | 12MHz       | NC         |

| 0                                     | 2            | 24MHz       | NC         |

| 0                                     | 3            | 48MHz       | NC         |

| 1                                     | Don't care   | NC          | 27MHz      |

Note when 48MHz USB crystal is used, the main internal phase lock loop will be disabled to reference the external clock directly.

### **User Guide**

### SPCA533A

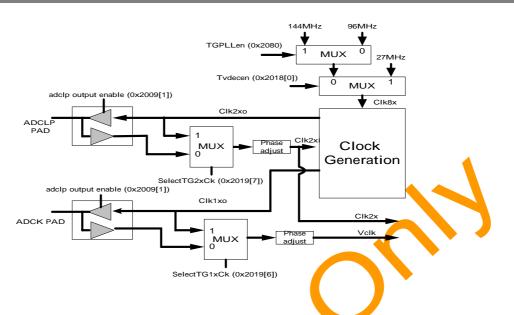

The clock supply to the CMOS sensors and to the internal timing generator (for the CCD systems) is a critical factor in the determination the frame rate and exposure time. The SPCA533A can supply this clock by the main phase lock loop (MPLL). Alternatively, the SPCA533A can supply this clock by a dedicated phase lock loop(TGPLL). The clock source is chosen based on the pixel clock of the sensors. If the pixel clock is 12MHz, choice the MPLL and disable the TGPLL to conserve power. If the pixel clock of the sensors is 18MHz, choose the TGPLL to supply the clock. The TGPLL can also outputs other frequencies such as 21MHz, it is controlled by the input parameters of the TGPLL.

The output clock frequency of the TGPLL is 3MHz\*(TGPLLNS1+1)\*(TGPLLNS2+1)/(TGPLLS+1)\*2

| Т | GPLLS | TGPLLNS1 | TGPLLNS2 | TGPLL   |

|---|-------|----------|----------|---------|

| 0 |       | 3        | 5        | 144 MHz |

| 0 |       | 3        | 6        | 168 MHz |

The 8XCK (8X pixel clock) is the input clock of the timing generator, which could be selected by the following setting

| TVDecMode (register 0X2018[0]) | TGPIIEn (register 0X2080[0]) | 8XCK    |      |   |  |

|--------------------------------|------------------------------|---------|------|---|--|

| 1                              | Don't care                   | 27 MHz  |      |   |  |

| 0                              | 0                            | 96 MHz  |      |   |  |

| 0                              | 1                            | TGPLL o | utpu | t |  |

The 2XCK (2X pixel clock) is selected by the following setting.

| Extclk2xdiv (register 0X2A82[7:0]) | 2XCK       |

|------------------------------------|------------|

| 0                                  | 8XCK / 1   |

| 1                                  | 8XCK / 2   |

| 2                                  | 8XCK/3     |

|                                    |            |

| 254                                | 8XCK / 255 |

| 255                                | 8XCK / 256 |

|                                    |            |

The 1XCK (pixel clock) is selected by the following setting.

| Extclk1xdiv (register 0X2A81[3:0]) | 1XCK (pixel clock) |

|------------------------------------|--------------------|

| 0                                  | 2XCK / 1           |

| 1                                  | 2XCK / 2           |

| 2                                  | 2XCK / 3           |

| 🥖                                  |                    |

| 15                                 | 2XCK / 15          |

| 16                                 | 2XCK / 16          |

The following diagram summarize the clock selection of pixel clock.

**User Guide**

### SPCA533A

The operation clocks of the TV/LCD interface controller can be programmed by the following settings. The detail information is described in section 5.13.

| SelectTVEnc2xCk (reg 0X201C bit 1) | TVEnc2XCK     |

|------------------------------------|---------------|

| 0                                  | 27 MHz        |

| 1                                  | 24 MHz        |

|                                    |               |

| SelectTVEnc1xCk (reg 0X201C bit 0) | TVEnc1XCK     |

| 0                                  | TVEnc2XCK / 2 |

| 1                                  | TVEnc2XCK     |

|                                    | <u> </u>      |

The operating clock of the embedded CPU can be programmed dynamically via cpufreq[2:0] register. The default frequency is 12MHz and the highest frequency is 32 MHz. The register design allows the frequency to be changed at run time. The base clock is 96MHz.

| Cpufreq[2:0] | CPU clock |

|--------------|-----------|

| 0            | 32Mz      |

| 1            | 24MHz     |

| 2            | 12MHz     |

| 3            | 6MHz      |

| 4            | 3MHz      |

| 5            | 1.5MHz    |

| 6            | 750KHz    |

| 7            | 375KHz    |

The SPCA533A can also output a clock for AC97 CODEC or Sunplus's MP3 decoder(SPCA751). The AC97 CODEC takes 24 MHz clock as its input and the SPCA751 usually operated at 13.5MHz. The Audio clock output is an multiplex pin (with GPIO[41]). To select the audio clock output function, set register 0X2019[3]. The audio clock frequency can be programmed by the following register.

| AUDCKfreq (register 0X2021[1:0] | AUDCK    |

|---------------------------------|----------|

| 0                               | 12 MHz   |

| 1                               | 13.5 MHz |

| 2                               | 24 MHz   |

| 3                               | 27 MHz   |

### **User Guide**

### SPCA533A

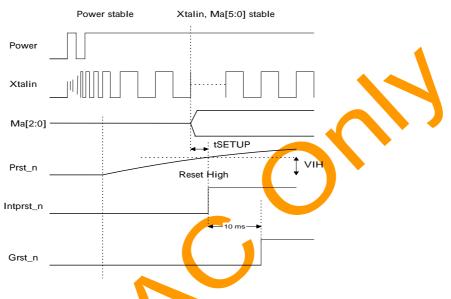

#### 1.2.2 Power On Sequence

The power-on reset to the SPCA533A can be designed by a simple RC-delay circuit. The SPCA533's reset pin connects to an internal Schmitt-triggered buffer, which provides about 1 volt hysteresis to the reset pin. The SPCA533's internal reset circuitry delayed the external reset for 10 ms, allowing the stabilization of the phase lock loops. During this delay period, the IO-trap values are latched. The pull-up circuitry attached to the MA pins must be ready before the internal reset terminates.

The SPCA533A must be properly initialized before any camera operation is possible. The following initialization tasks are performed (once) after the SPCA533A is powered on.

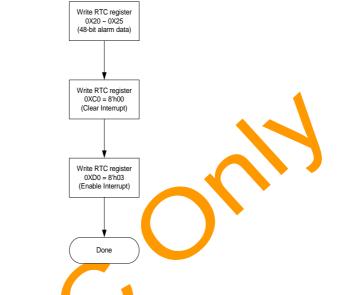

#### 1. RTC initialization

- a) Enable RTC (RTC register 0X00 = 8'h05)

- b) Check the RTC reliability (RTC register 0X02)

- c) Load RTC timer (RTC register 0X10 ~ 0X15, 0Xb0 bit 0)

- d) Load RTC alarm if necessary (RTC register 0X20 ~ 0X25)

- e) Clear RTC interrupt event (RTC register 0XC0)

- f) Enable RTC interrupt if necessary (RTC register 0XD0)

#### 2. GPIO initialization:

- a) Select alternative functions of the GPIO if necessary (register 0X2019 ~ 0X201c)

- b) Select the GPIO direction (input or output) (register 0X2038 ~ 0X203d)

- c) Clear interrupts (register 0X2048 ~ 0X204d, 0X2058 ~ 0X205d)

- d) Set interrupt enable if necessary (register 0X2051 ~ 0X2055, 0X2058 ~ 0X205d)

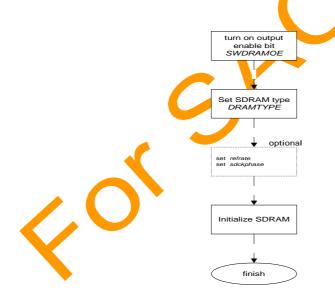

#### 3. SDRAM initialization:

- a) Turn on the output enable bit of the SDRAM bus (register 0X2006).

- b) Select the sdram type(16M, 64M, 128M or 256M)(register 0X2707).

- c) Adjust the sdram clock phase(register 0X2709).

- d) Initialize SDRAM (register 0X27A0[2]). The SPCA533A accesses the SDRAM via a 48MHz clock and the CAS latency is 2.

- e) Set the refresh rate(register 0X270a)

4. Sensor interface initialization: reference to the CMOS sensor and CCD sensor sections for details.

- 5. Storage media interface initialization:

- a) Storage media type (0x2400[2:0])

- b) FMgpio setting (0x2405 ~ 0x2408, 0x2410 ~0x241F)

Note that the media type can be programmed dynamically during camera operation so that switching memory media is possible.

Jun. 14, 2001 Preliminary Version: 0.2.0

#### **User Guide**

#### SPCA533A

#### 6. Audio initialization:

- a) Set the audio buffer mode (register 0x2605)

- b) Set the audio data format (register 0x2606)

- c) Enable the AC'97 codec or the embedded codec

#### 7. CPU initialization

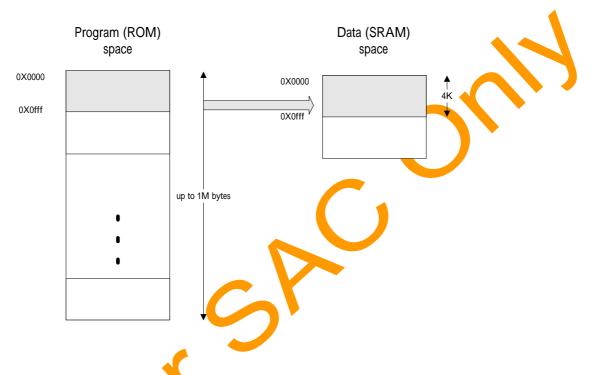

- a) enable 0x0000 0x0fff 4K SRAM (register 0x2C00[0])

- b) enable 0x1000 0x1fff 4K SRAM (register 0x2C00[1])

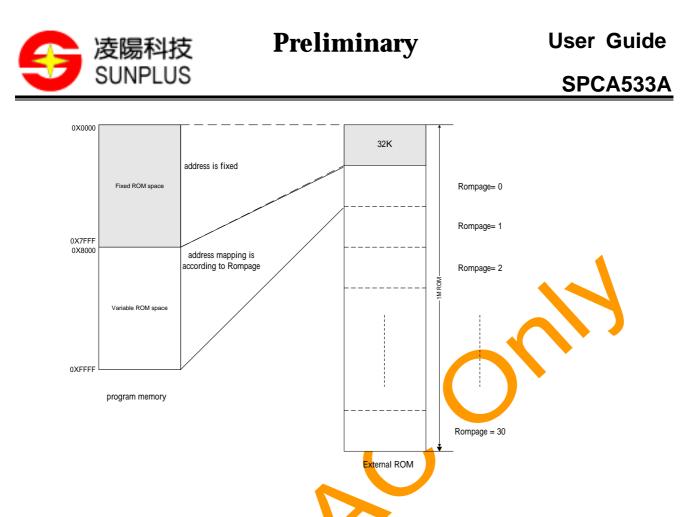

- c) enable banking of the ROM space RompageEn (register 0x2C00[3])

- d) enable RAM space to ROM space mapping via RampageEn (register 0x2C00[2])

- e) Port 1 output enable mode selection via P1oesel[7:0] (register 0x2C02), SFR 8'h90 and 0x201A[4]

- f) Port 3 output enable mode selection via P3oesel[5:0] (register 0x2C03) and SFR 8'hB0

#### 8. TV/LCD interface initialization:

- a) Set the display mode (register 0X2D00)

- b) Set vertical line count per frame (register 0X2D02~0X2D03)

- c) Set horizontal pixel count per line (register 0X2D04~0X2D05)

- d) Set vertical sync width (register 0X2D06)

- e) Set horizontal sync width (register 0X2D07)

- f) Set active region for display (register 0X2D08~0X2D08)

- g) Turn on the TV/LCD encoder function (register 0X2001)

#### 9. Other initialization tasks:

- a) The font-base OSD must be upload to the SDRAM

- b) The graphic-based OSD must be upload to the SDRAM and decompressed

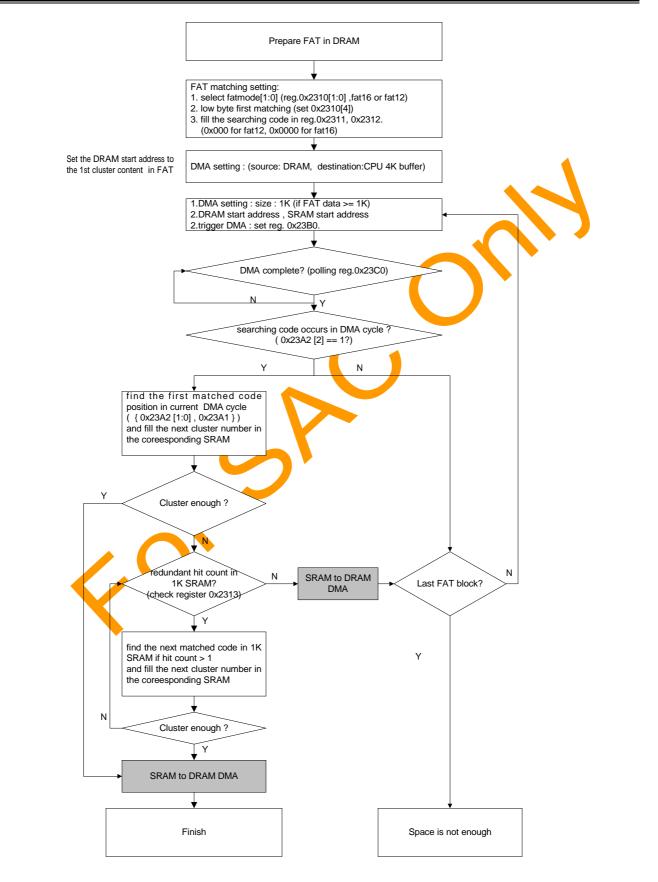

- c) The FAT of the storage media must be uploaded to the SDRAM. It is much faster to operate the FAT in the SDRAM(with the DMA to SRAM function) than from the storage media directly.

- d) The audio sound library (if any) must be uploaded to the SDRAM.

- e) The EXIF file header (if any) must be uploaded to the SDRAM for later use.

#### 1.2.3 Suspend/resume control

To put the system into suspend state, the CPU must set the "*swsuspend*" control bit in the global control register section. When the camera is connected to the PC, the CPU should program the "*swsuspend*" bit after it received an USB suspend interrupt. When the camera is not connected to the PC, the CPU itself should setup a timer to put the system into suspend state within a reasonable period of time. Both the timer in the built-in 8032 and the timer in the global module can be used to perform the time counting.

In the suspend state, the crystal pads of the SPCA533A is disabled. All the internal clocks are stopped. The firmware should put all the IO pins into low (or high) state to prevent current leakage causing by interfacing to the external modules. The following table shows the ideal state of each pin in typical applications.

| CPU interface ( | (note 1)                                          |                                                          |

|-----------------|---------------------------------------------------|----------------------------------------------------------|

| Psen            | HW driving low                                    |                                                          |

| Ale             | HW driving high                                   |                                                          |

| P0[7:0]         | Next instruction address                          |                                                          |

| P1[7:0]         | FW programmable                                   |                                                          |

| P2[7:0]         | Next instruction address                          |                                                          |

| P3[7:0]         | FW programmable                                   |                                                          |

| Storage media   | Interface (Note 3)                                |                                                          |

| Fmgpio[29:0]    | Driving Low/Driving high/Floating                 |                                                          |

| SDRAM interfa   | ce (Note 2)                                       |                                                          |

|                 | SDRAM power cut-off (Set register 0x2708 to high) | SDRAM is used as storage media and in self-refresh state |

Jun. 14, 2001 Preliminary Version: 0.2.0

### SPCA533A

| rasnn                                                                                                                                         | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

|-----------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|-------------------------------------------|------------------------------------|

| casnn                                                                                                                                         | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| mwenn                                                                                                                                         | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| md[15:0]                                                                                                                                      | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| sdclk                                                                                                                                         | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| ldqm                                                                                                                                          | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| udqm                                                                                                                                          | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| cke                                                                                                                                           | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| ma[13:0]                                                                                                                                      | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| trap                                                                                                                                          | HW driving low                                                                                                                                                                                                                                                   |                            | HW driving low                            |                                    |

| System                                                                                                                                        |                                                                                                                                                                                                                                                                  |                            |                                           |                                    |

| prstnn                                                                                                                                        | External pull-high                                                                                                                                                                                                                                               |                            |                                           |                                    |

| xtalusbi                                                                                                                                      | NA                                                                                                                                                                                                                                                               |                            |                                           |                                    |

| xtalusbo                                                                                                                                      | HW driving high                                                                                                                                                                                                                                                  |                            | •                                         |                                    |

| Xtal27i                                                                                                                                       | NA                                                                                                                                                                                                                                                               |                            |                                           |                                    |

| Xtal27o                                                                                                                                       | HW driving high                                                                                                                                                                                                                                                  |                            |                                           | •                                  |

|                                                                                                                                               | ose IO pins (Note 3)                                                                                                                                                                                                                                             |                            |                                           |                                    |

| Gpio[41:0]                                                                                                                                    | Driving Low/Driving high/                                                                                                                                                                                                                                        | /Floating                  |                                           |                                    |

| Sensor inter                                                                                                                                  |                                                                                                                                                                                                                                                                  | ~                          |                                           |                                    |

| rgb[9:0]                                                                                                                                      | Internal pull-low                                                                                                                                                                                                                                                |                            |                                           |                                    |

| <u> </u>                                                                                                                                      | iterface (note 3)                                                                                                                                                                                                                                                |                            |                                           |                                    |

| digtv[21:0]                                                                                                                                   | Driving Low/Driving hi                                                                                                                                                                                                                                           | igh/Floating               |                                           |                                    |

| Timing genera                                                                                                                                 |                                                                                                                                                                                                                                                                  | .g                         |                                           |                                    |

| v1                                                                                                                                            |                                                                                                                                                                                                                                                                  | t turn off the TG output e | enable register to make the TG signals fl | oating. Also, all the Bi-direction |

|                                                                                                                                               |                                                                                                                                                                                                                                                                  |                            | fed into the core of SPCA533. This will   |                                    |

|                                                                                                                                               | SPCA533.                                                                                                                                                                                                                                                         | Ŭ                          |                                           |                                    |

| v2                                                                                                                                            | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| v3                                                                                                                                            | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| V4                                                                                                                                            | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| sg1a                                                                                                                                          | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| sg3a                                                                                                                                          | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| sg1b                                                                                                                                          | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| sg3b                                                                                                                                          |                                                                                                                                                                                                                                                                  |                            |                                           |                                    |

|                                                                                                                                               |                                                                                                                                                                                                                                                                  |                            |                                           |                                    |

| ISUD                                                                                                                                          | Floating                                                                                                                                                                                                                                                         |                            |                                           |                                    |

| sub<br>fr                                                                                                                                     | Floating<br>Floating                                                                                                                                                                                                                                             |                            |                                           |                                    |

| fr                                                                                                                                            | Floating<br>Floating<br>Floating                                                                                                                                                                                                                                 |                            |                                           |                                    |

| fr<br>fh1                                                                                                                                     | Floating<br>Floating<br>Floating<br>Floating                                                                                                                                                                                                                     |                            |                                           |                                    |

| fr<br>fh1<br>fh2                                                                                                                              | Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                                                                                         |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter                                                                                                                  | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                                                                             |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl                                                                                                      | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                                                     |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk                                                                                              | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                                         |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs                                                                                        | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                             |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds                                                                                | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                                                 |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp                                                                       | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                                         |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp                                                              | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                                                             |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck                                                      | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                         |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen                                               | Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating<br>Floating                                                         |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen<br>sck                                        | FloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloating                                 |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen<br>sck<br>sdo                                 | FloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloating |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen<br>sck<br>sdo<br><b>Analog TV sig</b>         | FloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloating |                            |                                           |                                    |

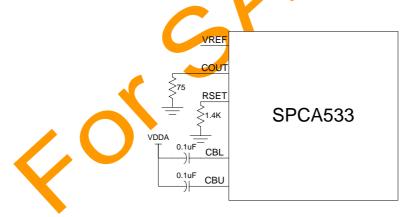

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen<br>sck<br>sdo<br><b>Analog TV sig</b><br>rset | FloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloating |                            |                                           |                                    |

| fr<br>fh1<br>fh2<br>mshutter<br>vsubctrl<br>pblk<br>fs<br>fcds<br>adclp<br>obclp<br>adck<br>sen<br>sck<br>sdo<br><b>Analog TV sig</b>         | FloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloatingFloating |                            |                                           |                                    |

**User Guide**

### SPCA533A

| vref        |                                |                                                               |

|-------------|--------------------------------|---------------------------------------------------------------|

| cout        |                                |                                                               |

| Audio Codeo | 2                              |                                                               |

| micp        |                                |                                                               |

| micn        |                                |                                                               |

| орі         |                                |                                                               |

| оро         |                                |                                                               |

| agc         |                                |                                                               |

| agcout      |                                |                                                               |

| daca        |                                |                                                               |

| audvref     |                                |                                                               |

| RTC         |                                |                                                               |

| xtalrtci    |                                |                                                               |

| xtalrtco    |                                |                                                               |

| USB interfa | ice                            |                                                               |

|             | Connecting to PC               | Stand-alone                                                   |

| dp          | Pull-up externally (by camera) | Pull-up exter <mark>na</mark> lly                             |

| dm          | Pull-down externally (by host) | Floating (the FW must disable the built-in USB transceiver to |

|             |                                | prevent current leak)                                         |

| suspend     | HW driving high                |                                                               |

|             |                                |                                                               |

**Note 1.** 8032 port 1 and port 3 can be programmed to drive-low, drive-high or tri-state by the firmware before the systems enters suspend state. The port 0 and port 2 will be driven the address of the next instruction after the one that sets the "SWsuspend" bit. The power of address latch TTL and external ROM must be supplied in the resume period.

**Note 2.** There are two possible states regarding to the DRAM interface signals. If the DRAM's power is cut off during the suspend state, then the firmware should set the "srefresh" bit to high before entering the suspend state. By doing this, all the DRAM interface signals are driven low by the SPCA533. This will consumes the least power. The other case is when DRAM is used as the storage media and the power is not cut-off during the suspend state. In this case, the SDRAM must be put into the self-refresh state by setting the "srefresh" to high to conserve power. The standard synchronous DRAM power consumption in self-refresh is 1.5 mA for 128M SDRAM and 4 mA for 256M SDRAM.

**Note 3.** All the "fmgpio" bus, "gpio" bus and "digtv" bus can be used as GPIO function. So it is easy to programmed this pins to "driving high", "driving low", or "floating" state before the system entering the suspend state. Just which state will consume the least power depends on the application because the application may pull-up or pull-low these pins externally. If the pin is pulled-up externally, then the application, in the suspend state, should let it floating or driving it high. If the pin is pulled-low externally, then the application should let it floating or driving it low in the suspend state. If the pin is neither pulled-high nor pulled-low externally, then the firmware must the set the appropriate registers to make SPCA533A driving it low. Do not let it floating in this case, otherwise, the floating input will cause current leakage inside the SPCA533.

**Note 4.** In a typically application, the sensors and CDS/AGC must be powered-off in the suspend state. The TG interface can be set to floating by turning off the corresponding output-enable registers. Even though some of the TG control pins have alternative function as input pins, the SPCA533A will gate the internal signal to prevent from internal nodes floating.

Once the camera is into the suspend state, it returns to the normal operation state in the following conditions.

- A. When the camera is not connected to the PC (stand alone application)

- 1. SPCA533A has detected a status change on the GPIO pins. The "uirsmen" must be turned on before entering suspend state.

- 2. The camera is plug into the USB port. Note that the internal USB transceiver might be turned off when the camera is not connected to the PC. In this case, the first thing for the CPU to do is to turn on the internal USB transceiver again. This approach is the same as previous one except the GPIO pin is connected to the USB connector power.

- B. When the camera is connected to the PC (on-line application)

- 1. Host resumes the USB device.

### SPCA533A

- 2. The camera is disconnected from the PC

- 3. SPCA533A has detected a status change on GPIO pins. This is the remote wake up function. The "*uirsmen*" must be turned on to perform remote wakeup. Both approach 2 and 3 need a GPIO pin to be connected to the USB power.

#### 1.2.4 Power Saving Consideration

The clocks supplied to the internal modules are controlled by register 0X2010 ~ 0X2013. To conserve power during camera operation, these clocks can be turned off when the corresponding modules are not in operation. The analog macros, like the video DAC, can also be put into the power saving mode when it is not used. The following table summarizes the operating condition of the internal modules according to the camera operation modes. In this table, 'N' represents the corresponding module is not in operation, 'Y' represents the corresponding module should be in operation, and 'O' represents the operation is optional.

| Camera<br>operation mode | Sensor<br>interface<br>controller | Color<br>DSP | DRAM<br>controller | LCD/TV<br>interface<br>controller | Storage<br>media<br>interface | Audio<br>controller | USB<br>controller | DMA   | JPEG<br>engine | CPU   |

|--------------------------|-----------------------------------|--------------|--------------------|-----------------------------------|-------------------------------|---------------------|-------------------|-------|----------------|-------|

| Idle                     | N                                 | Ν            | N                  | Ν                                 | Ν                             | N                   | N                 | N N   | Ν              | Y (1) |

| Preview                  | Y                                 | Y            | Y                  | Y                                 | O (2)                         | N                   | N                 | O (2) | Ν              | Y     |

| Capture                  | Y                                 | Y            | Y                  | Y                                 | Y                             | O (3)               | N                 | Y     | Y              | Y     |

| Playback                 | Ν                                 | Ν            | Y                  | Y                                 | Y                             | O (3)               | N                 | Y     | Y              | Y     |

| Data transfer (4)        | Ν                                 | Ν            | Y (5)              | Ν                                 | Υ                             | N                   | Y                 | Y     | Ν              | Y     |

- 1) The CPU should operates at the lowest frequency to conserve power. In this mode, all the GPIO events still generate interrupts to the CPU. So the CPU can still receive events of the user interface buttons and the event of a USB plug-in.

- 2) If the data access to the storage media is executed at background while previewing the image, the clock should be supplied to the storage media interface controller.

- 3) If the camera does not support audio function, the audio controller should be put into the power-down mode. Otherwise, it should be turned on when capturing video, recoding an audio annotation and audio playback.

- 4) Here, the data transfer means transferring data between the PC and the camera via the USB bus.

- 5) The DRAM controller is usually in operation when accessing the storage media. The DRAM can be used in constructing and maintaining the FAT. It can be used as the temporary buffer in the data transfer.

The following table summarizes the register settings to power-down individual modules and their corresponding analog macros.

| Module name                 | Power Saving Description                            | Register Setting   |

|-----------------------------|-----------------------------------------------------|--------------------|

| Sensor interface controller | Stop timing generator input clocks                  | 0X2013[2:0] = 3'h0 |

|                             | Power down TG PLL                                   | 0X2080 = 8'h00     |

| Color DSP                   | Stop the 48 MHz clock input of this module          | 0X2010[0] = 0      |

|                             | Stop the pixel clock                                | 0X2012[1] = 0      |

| DRAM controller             | Stop the 48MHz clock input to this module           | 0x2010[5]=0        |

| LCD/TV controller           | Stop the 48 MHz clock input to this module          | 0X2010[7] = 1'b0   |

|                             | Stop the TV/LCD pixel clocks                        | 0X2013[4:3] = 2'b0 |

|                             | Power down TV encoder DAC                           | 0X2001 = 8'h0C     |

| Storage media interface     | Stop the clock input to this module                 | 0X2010[2]=0        |

| Audio controller            | Stop the 48 MHz clock input of the audio controller | 0X2010[4] = 1'b0   |

|                             | Stop the 12MHz clock input of the audio controller  | 0X2011[1] = 1'b0   |

|                             | Gate the AC-link input clock                        | 0X2013[7] = 1'b0   |

|                             | Power down Audio CODEC                              | 0X2670[0] = 1      |

| USB controller              | Stop the 48 MHz clock input of the USB controller   | 0X2010[3] = 0      |

|                             | Stop the 12 MHz clock input of the USB controller   | 0X2011[0] = 0      |

### **User Guide**

### SPCA533A

|      | Power down USB transceiver                          | 0X2005[0] = 1  |

|------|-----------------------------------------------------|----------------|

| DMA  | Stop the clock input to this module                 | 0x2010[1] = 0  |

| JPEG | Stop the 48 MHz clock input to this module          | 0X2010[6] = 0  |

| CPU  | Set the CPU operating clock to the lowest frequency | 0X2024[2]=3'h7 |

#### 1.2.5 User Interface

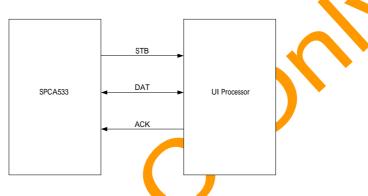

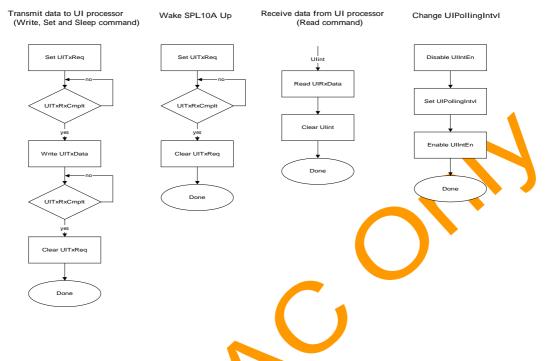

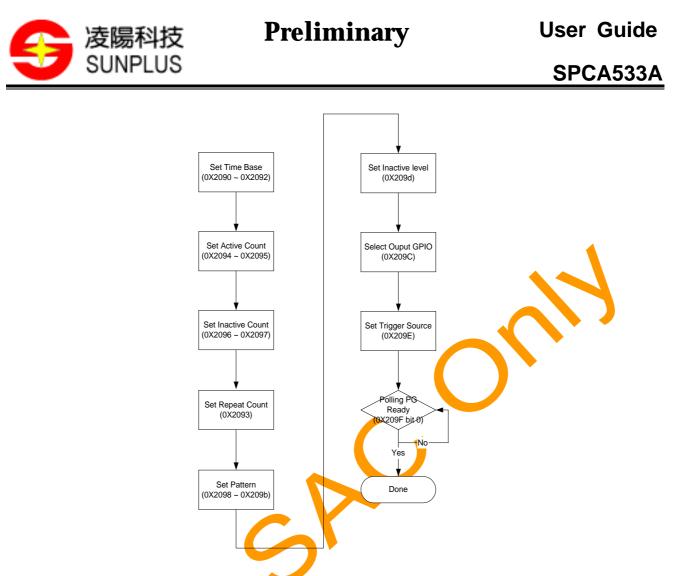

The SPCA533A communicates with the UI module (Sunplus SPL10A) via a 3-pin serial interface. The SPL10A is the Sunplus UI module, which integrates a status LCD and the key-scan function. The SPCA533A may send data to the UI module. For example the picture count can be sent to the UI module and displayed on the status LCD. The SPCA533A can also read the key status from the UI module. The interconnection between the SPCA533A and SPL10A is shown below.

The SPL10A acts as a slave in the camera system. It dos not send data to the SPCA533A spontaneously. The SPCA533A reads the key status on the UI module periodically and interrupts the micro-controller. This polling procedure is done by hardware and the polling interval is programmable. In cases that user inputs be sent to the micro-controller in real time, the GPIO pins of the SPCA533A should be connected to the user input instead. Because the user input via the UI module is read by the SPCA533A periodically and does not guarantee to be delivered in real time. Also, if the user input is used to wake up the SPCA533A from the suspend state, it should also be connected to the SPCA533A GPIO pins, too. Because the SPCA533A stops the polling procedure in the suspend state.

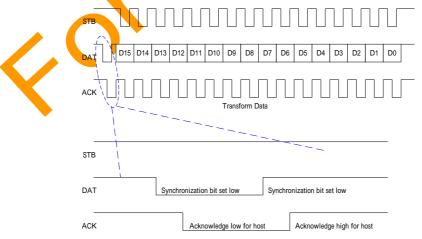

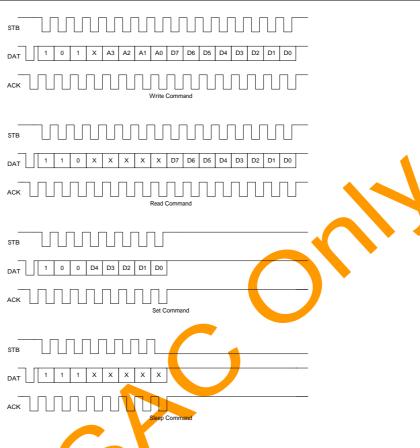

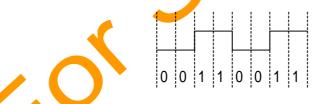

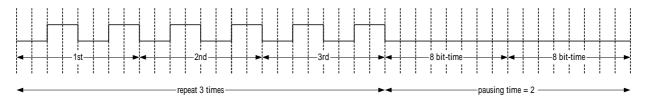

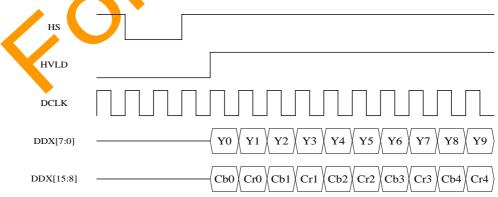

The following timing diagram shows the communication protocol between the SPCA533A and SPL10A.

**User Guide**

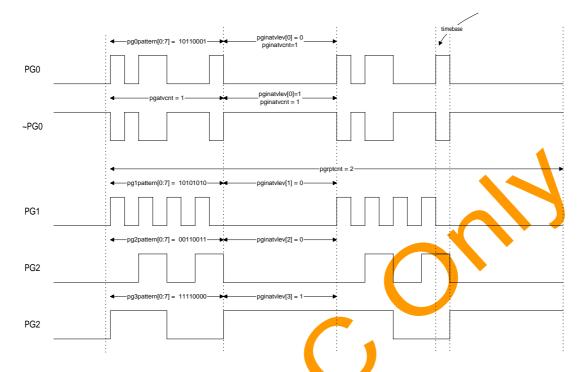

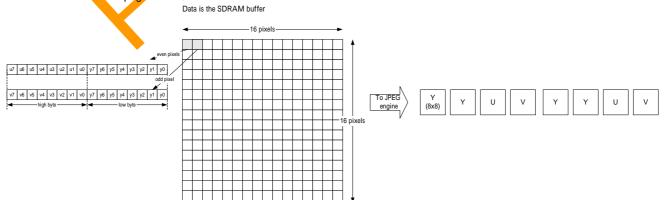

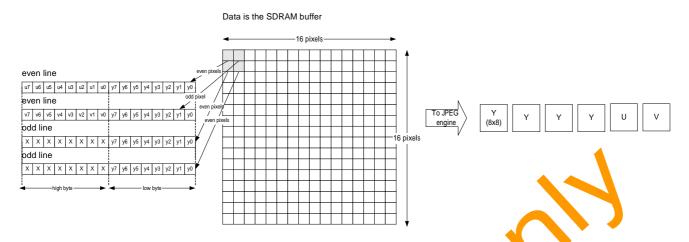

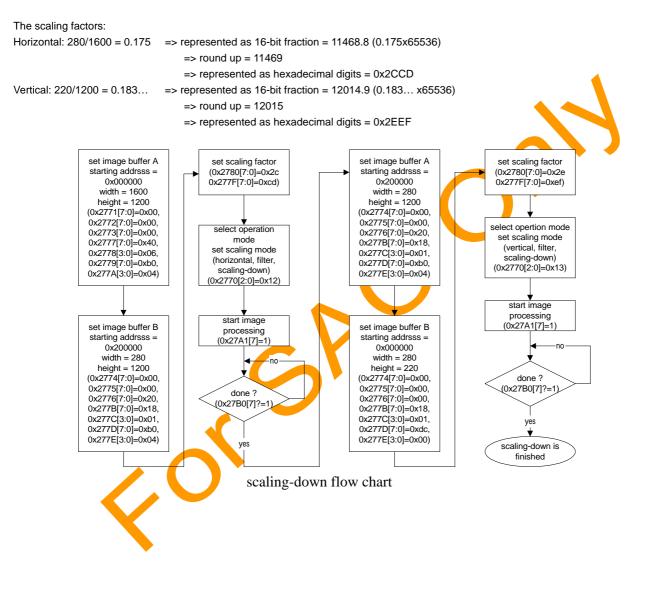

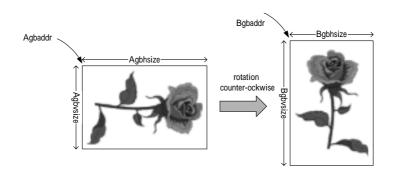

### SPCA533A