### **DESCRIPTION**

The SPE0544 are designed by TVS array that is to protect sensitive electronics from damage or latch-up due to ESD. They are designed for use in applications where board space is at a premium. SPE0544 will protect up to three line, and may be used on lines where the signal polarities swing above and below ground.

SPE0544 offer desirable characteristics for board level protection including fast response time, low operating and clamping voltage, and no device degradation.

SPE0544 may be used to meet the immunity requirements of IEC 61000-4-2, level 4. The small SOT-143 package makes them ideal for use in portable electronics such as cell phones, PDA's, notebook computers, and digital cameras.

# APPLICATIONS

- ◆ Cellular Handsets and Accessories

- Cordless Phone

- ◆ PDA

- Notebooks and Handhelds

- ◆ Portable Instrumentation

- ♦ Digital Cameras

- ♦ MP3 Player

#### **FEATURES**

- Transient protection for data lines to IEC 61000-4-2 (ESD) ±15kV (air), ±8kV (contact)

IEC 61000-4-4 (EFT) 40A (5/50ns)

- ◆ Protects four I/O lines

- Working voltage: 5V

- ♦ Low leakage current

- Low operating and clamping voltages

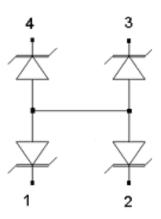

### PIN CONFIGURATION(SOT-143-A)

#### **PART MARKING**

Y: Year Code W: Week Code

# **ORDERING INFORMATION**

| Part Number    | Package   | Part Marking |

|----------------|-----------|--------------|

| SPE0544S14ARGB | SOT-143-A | 44           |

% Week Code : A ~ Z(1 ~ 26); a ~ z(27 ~ 52)

※ SPE0544S14ARGB: Tape Reel; Pb − Free; Halogen − Free

## ABSOULTE MAXIMUM RATINGS

(Ta=25°C Unless otherwise noted)

| Parameter                                 | Symbol | Typical       | Unit |

|-------------------------------------------|--------|---------------|------|

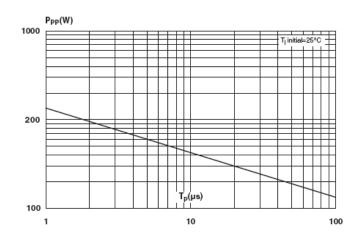

| Peak Pulse Power (tp = 8/20 μs)           | Ppk    | 250           | W    |

| Maximum Peak Pulse Current (tp = 8/20 μs) | Ipp    | 7             | A    |

| ESD per IEC 61000 – 4 – 2 (Air )          | Vpp    | ±15           | KV   |

| ESD per IEC 61000 – 4 – 2 (Contact )      | Vpp    | ±8            | KV   |

| Operating Junction Temperature            | Тл     | -55 ~ 125     | °C   |

| Storage Temperature Range                 | Tstg   | -55 ~ 150     | °C   |

| Lead Soldering Temperature                | TL     | 260 ( 10sec ) | °C   |

# **ELECTRICAL CHARACTERISTICS**

(TA=25°C Unless otherwise noted)

| Parameter                   | Symbol | Conditions                                      | Min. | Тур  | Max. | Unit |

|-----------------------------|--------|-------------------------------------------------|------|------|------|------|

| Reverse Stand – Off Voltage | Vrwm   |                                                 |      |      | 5    | V    |

| Reverse Breakdown Voltage   | VBR    | It = 1 mA                                       | 6    |      |      | V    |

| Reverse Leakage Current     | Ir     | $V_{RWM} = 5V$ , $T=25$ °C                      |      | 0.01 | 1    | μΑ   |

| Reverse Leakage Current     | Ir     | $V_{RWM} = 3V$ , $T=25$ °C                      |      | 0.01 | 0.5  | μΑ   |

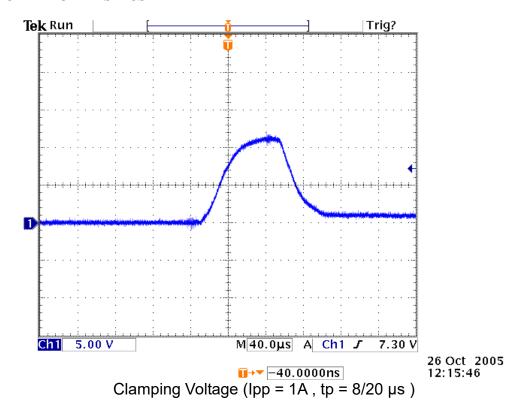

| Clamping Voltage            | Vc     | $Ipp = 1A$ , $tp = 8/20 \mu s$                  |      |      | 11.5 | V    |

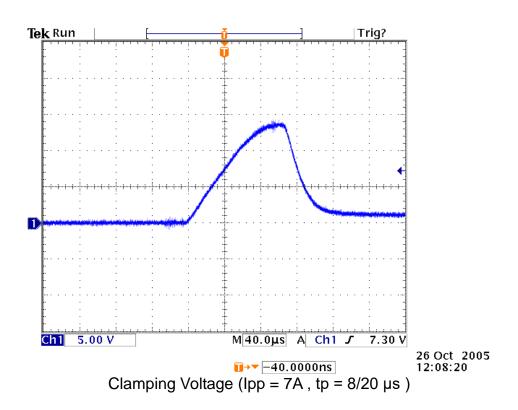

| Clamping Voltage            | Vc     | $Ipp = 7A, tp = 8/20 \mu s$                     |      |      | 15   | V    |

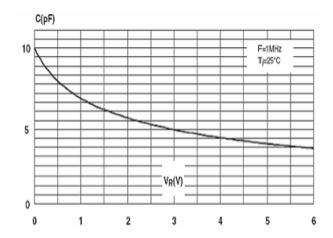

| Junction Capacitance        | Cj     | Between I/O Pin and GND $V_R = 0V$ , $f = 1MHz$ |      | 5    | 10   | pF   |

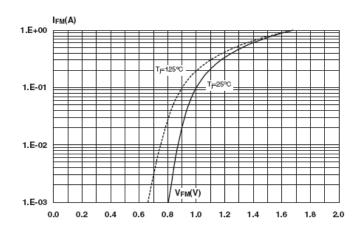

## TYPICAL CHARACTERISTICS

## TYPICAL CHARACTERISTICS

Fig 1 : Junction Capacitance V.S Reverse Voltage Applied

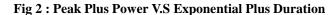

Fig 3 : Relative Variation of Peal Plus Power V.S Initial Junction Temperature

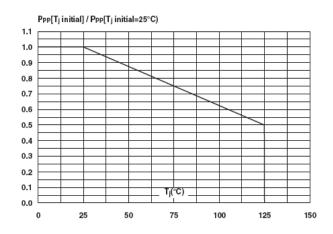

Fig 4: Forward Voltage Drop V.S Peak Forward Current

### APPLICATION NOTE

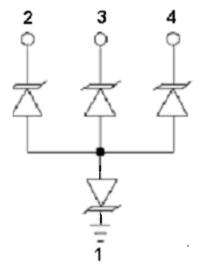

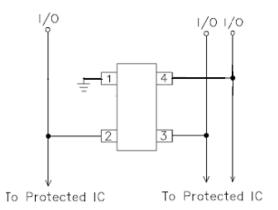

#### **Device Connection for Protection of Four Data Lines**

SPE0544 is designed to protect up to three data lines. The device is connected as follows:

1. The TVS protection of four I/O lines is achieved by connecting pins 1, 2, 4. Pin 3 are connected to ground. The ground connection should be made directly to the ground plane for best results. The path length is kept as short as possible to reduce the effects of parasitic inductance.

## Circuit Board Layout Recommendations for Suppression of ESD

Good circuit board layout is critical for the suppression of ESD induced transients. The following guidelines are recommended:

- 1. Place the TVS near the input terminals or connectors to restrict transient coupling.

- 2. Minimize the path length between the TVS and the protected line.

- 3. Minimize all conductive loops including power and ground loops.

- 4. The ESD transient return path to ground should be kept as short as possible.

- 5. Never run critical signals near board edges.

- 6. Use ground planes whenever possible.

Information provided is alleged to be exact and consistent. SYNC Power Corporation presumes no responsibility for the penalties of use of such information or for any violation of patents or other rights of third parties which may result from its use. No license is granted by allegation or otherwise under any patent or patent rights of SYNC Power Corporation. Conditions mentioned in this publication are subject to change without notice. This publication surpasses and replaces all information previously supplied. SYNC Power Corporation products are not authorized for use as critical components in life support devices or systems without express written approval of SYNC Power Corporation.

© The SYNC Power logo is a registered trademark of SYNC Power Corporation

© 2020 SYNC Power Corporation – Printed in Taiwan – All Rights Reserved

SYNC Power Corporation

7F-2, No.3-1, Park Street

NanKang District (NKSP), Taipei, Taiwan, 115, R.O.C

Phone: 886-2-2655-8178

Fax: 886-2-2655-8468

© http://www.syncpower.com