# SPEAR-07-NC03

# Ethernet Communication Controller with USB-Host

# Features

- Based on ARM720T (8K Caches and MMU included)

- Support a 10/100 Mbits/s Ethernet connection (IEEE802.3)

- Full-Speed USB Host Controller, supports 12Mbit/s Full Speed Devices

- UART Interface: 115KBaud

- I<sup>2</sup>C interface: Fast and Slow.

- IEEE1284 Host Controller

- Real Time Clock

- Timers and Watchdog peripherals

- Integrated PLL (25MHz Input, 48MHz Output)

- Up to 12 GPIOs (including IEEE1284 port)

- 8K SRAM shared with an External Microprocessor

- Static Memory Controller (up to 2 Banks, Max 16M each)

- DRAM Controller SDRAM/EDO (up to 4 Banks, Max 32M each)

- External I/O Banks: 2 x 16KB.

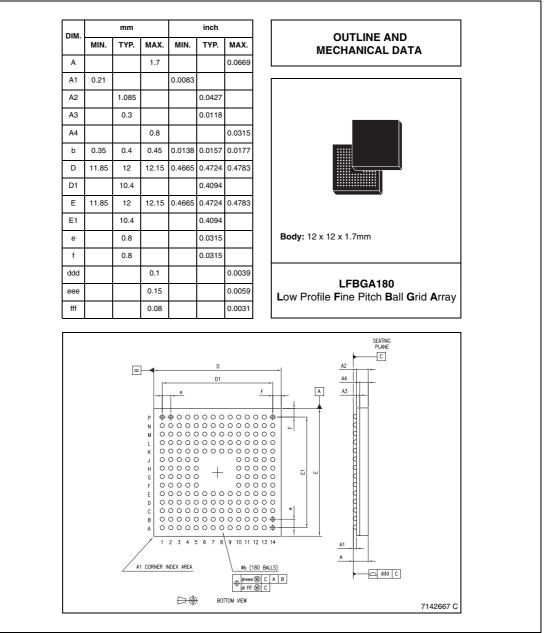

- Package LFBGA 180 (12x12mm x1.7mm)

# Description

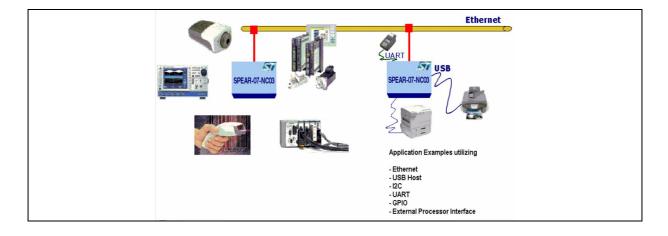

SPEAR-07-NC03 is a smart Communication Controller for USB and Ethernet Communication.

SPEAR-07-NC03 allows the sharing of a Full-Speed USB or IEEE1284 or a UART Peripherals inside an Ethernet System.

SPEAR-07-NC03 is supported by several Operation Systems such as eCOS.

# Order codes

| Part number   | Op. Temp. range, °C | Package  | Packing |

|---------------|---------------------|----------|---------|

| SPEAR-07-NC03 | -40 to +105         | LFBGA180 | Tray    |

# **Table of Contents**

| 1 | Prod  | Product overview            |  |  |  |

|---|-------|-----------------------------|--|--|--|

|   | 1.1   | Overview                    |  |  |  |

| 2 | Feat  | ures                        |  |  |  |

|   | 2.1   | Architecture                |  |  |  |

|   | 2.2   | ARM720T RISC Processor 9    |  |  |  |

|   | 2.3   | External Memory Interface 9 |  |  |  |

|   | 2.4   | IEEE802.3/Ethernet MAC      |  |  |  |

|   | 2.5   | DMA Controller              |  |  |  |

|   | 2.6   | UART                        |  |  |  |

|   | 2.7   | Timers                      |  |  |  |

|   | 2.8   | Watchdog Timer              |  |  |  |

|   | 2.9   | GPIO (Programmable I/O) 10  |  |  |  |

|   | 2.10  | Interrupt Controller        |  |  |  |

|   | 2.11  | IEEE1284 Host Controller 10 |  |  |  |

|   | 2.12  | USB Host Controller 11      |  |  |  |

|   | 2.13  | Shared SRAM                 |  |  |  |

|   | 2.14  | Real Time Clock             |  |  |  |

|   | 2.15  | Frequency Synthesizer       |  |  |  |

| 3 | Top-l | level Block Diagram         |  |  |  |

| 4 | Pin D | Descriptions                |  |  |  |

|   | 4.1   | Functional Pin Groups       |  |  |  |

|   | 4.2   | PAD Types                   |  |  |  |

| 5 | Mem   | ory Map                     |  |  |  |

|   | 5.1   | Global MAP (AHB)            |  |  |  |

|   | 5.2   | I/O MAP (APB)               |  |  |  |

| 6 | Bloc  | ks description              |  |  |  |

|   | 6.1   | CPU SUBSYSTEM & AMBA BUS 22 |  |  |  |

|     | 6.1.1   | ARM720 Processor                    | 22    |

|-----|---------|-------------------------------------|-------|

|     | 6.1.2   | MMU Overview                        | 22    |

|     | 6.1.3   | Instruction and Data Cache overview | 23    |

|     | 6.1.4   | Write Buffer Overview               | 23    |

|     | 6.1.5   | Configuration                       | 23    |

|     | 6.1.6   | Coprocessor Registers Programming   | 24    |

| 6.2 | MAC E   | Ethernet Controller                 | . 26  |

|     | 6.2.1   | Overview                            | 26    |

|     | 6.2.2   | Transfer Logic                      | 27    |

|     | 6.2.3   | Ethernet register map               | 31    |

|     | 6.2.4   | Register description                | 37    |

|     | 6.2.5   | Programming the DMA MAC             | 63    |

| 6.3 | Full-Sp | peed USB Host Controller            | . 68  |

|     | 6.3.1   | Overview                            | 68    |

|     | 6.3.2   | Host Controller Management          | 69    |

|     | 6.3.3   | Initialization of the HCI           | 70    |

|     | 6.3.4   | Operational States                  | 70    |

|     | 6.3.5   | Operational Registers Mapping       | 72    |

|     | 6.3.6   | Register description                | 73    |

| 6.4 | IEEE1   | 284 Host Controller                 | . 96  |

|     | 6.4.1   | Overview                            | 96    |

|     | 6.4.2   | Communication modes                 | 97    |

|     | 6.4.3   | Matrix of Protocol Signal Names     | 98    |

|     | 6.4.4   | Register MAP                        | 98    |

|     | 6.4.5   | IEEE1284 Configuration              | 99    |

|     | 6.4.6   | DMA Registers                       | . 102 |

|     | 6.4.7   | Parallel Port register              | . 114 |

| 6.5 | UART    | Controller                          | 121   |

|     | 6.5.1   | Overview                            | . 121 |

|     | 6.5.2   | Registers Map                       | . 122 |

|     | 6.5.3   | Register description                | . 122 |

| 6.6 | I2C Co  | ontroller                           | 126   |

|     | 6.6.1   | Overview                            | . 126 |

|     | 6.6.2   | Register Map                        | . 128 |

|     | 6.6.3   | Register Description                | . 128 |

|     | 6.6.4   | I2C Functional description          | . 134 |

|     |         |                                     |       |

| 6.7  | Dynam   | nic Memory Controller         | 138 |

|------|---------|-------------------------------|-----|

|      | 6.7.1   | Overview                      | 138 |

|      | 6.7.2   | Memory Access                 | 138 |

|      | 6.7.3   | Address Mapping Table         | 140 |

|      | 6.7.4   | External Bus Interface        | 140 |

|      | 6.7.5   | Register MAP                  | 141 |

|      | 6.7.6   | Register Description          | 141 |

| 6.8  | Static  | Memory Controller             | 145 |

|      | 6.8.1   | SRAMC description             | 145 |

|      | 6.8.2   | Registers Map and description | 145 |

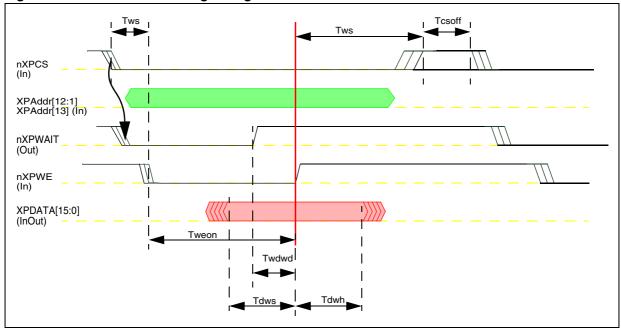

| 6.9  | Shared  | d SRAM Controller             | 147 |

|      | 6.9.1   | Overview                      | 147 |

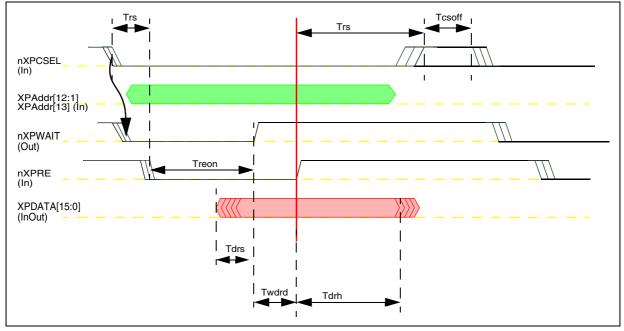

|      | 6.9.2   | External Processor Timings    | 149 |

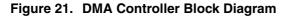

| 6.10 | DMA C   | Controller                    | 150 |

|      | 6.10.1  | Overview                      | 150 |

|      | 6.10.2  | Register Map                  | 151 |

|      | 6.10.3  | Registers Description         | 152 |

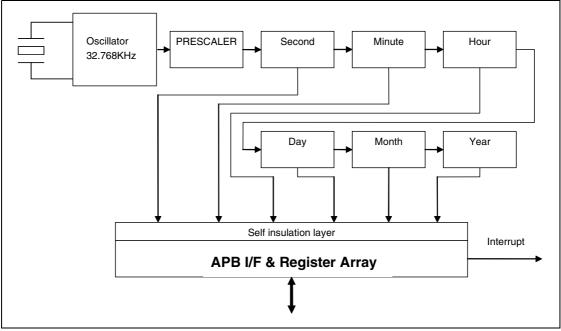

| 6.11 | RTC .   |                               | 157 |

|      | 6.11.1  | Overview                      | 157 |

|      | 6.11.2  | Register Map                  | 157 |

|      | 6.11.3  | Register Description          | 158 |

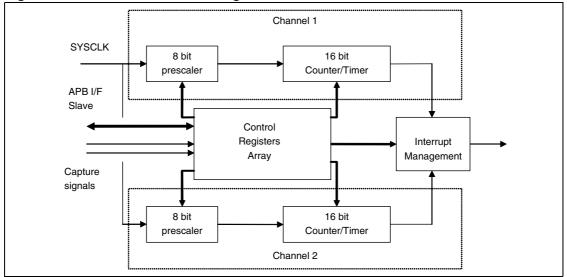

| 6.12 | Timer/  | /Counter                      | 162 |

|      | 6.12.1  | Overview                      | 162 |

|      | 6.12.2  | Registers Map                 | 163 |

|      | 6.12.3  | Registers Description         | 163 |

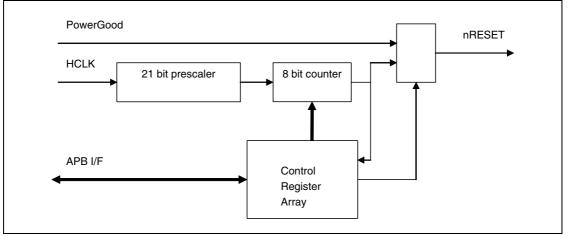

| 6.13 | Watch   | -Dog Timer                    | 166 |

|      | 6.13.1  | Overview                      | 166 |

|      | 6.13.2  | Register map                  | 166 |

|      | 6.13.3  | Register Description          | 166 |

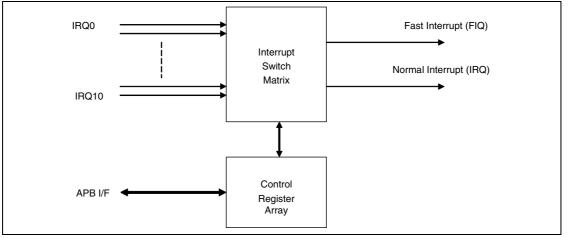

| 6.14 | Interru | ıpt Controller                | 168 |

|      | 6.14.1  | Overview                      | 168 |

|      | 6.14.2  | Register Map                  | 169 |

|      | 6.14.3  | Register Description          | 169 |

|      | 6.14.4  | Interrupt Table               | 176 |

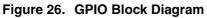

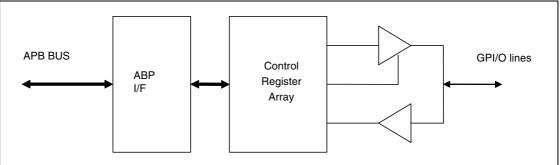

| 6.15 | GPIO    |                               | 176 |

|      | 6.15.1  | Overview                      | 176 |

|    |        | 6.15.2 Register Map                           |

|----|--------|-----------------------------------------------|

|    |        | 6.15.3 Registers Description                  |

|    | 6.16   | RESET and Clock Controller 179                |

|    |        | 6.16.1 Overview                               |

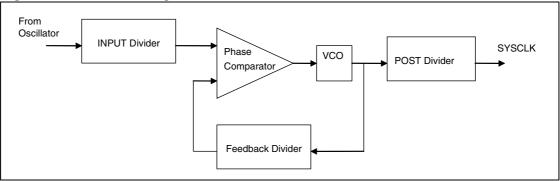

|    | 6.17   | PLL (Frequency synthesizer) 179               |

|    |        | 6.17.1 Overview                               |

|    |        | 6.17.2 Global Configuration Block             |

|    |        | 6.17.3 Register Map                           |

|    |        | 6.17.4 Registers Description                  |

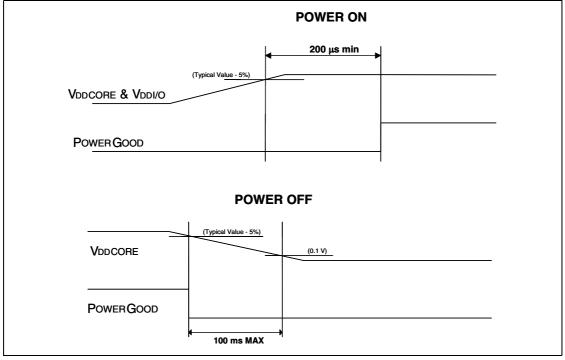

| 7  | Electr | ical Characteristics                          |

|    | 7.1    | Absolute Maximum Rating                       |

|    | 7.2    | Recommended Operating Conditions              |

|    | 7.3    | DC Electrical Characteristics                 |

|    |        | 7.3.1 POWERGOOD timing requirement            |

|    | 7.4    | AC Electrical characteristics                 |

|    | 7.5    | External Memory Bus Timing 189                |

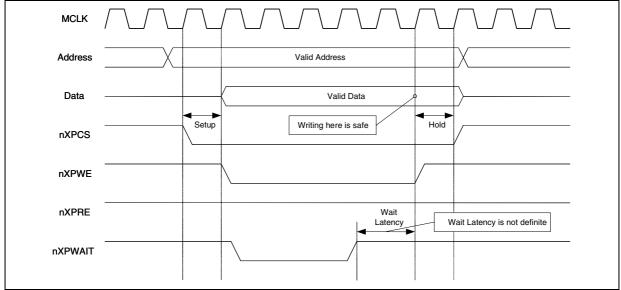

|    |        | 7.5.1 Timings for External CPU writing access |

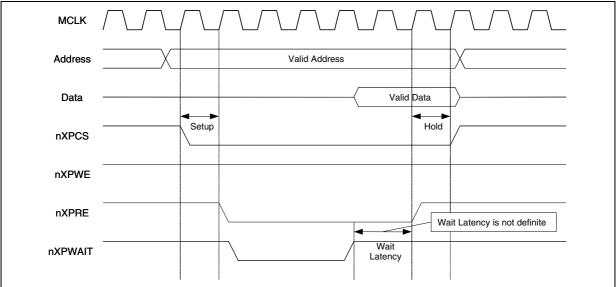

|    |        | 7.5.2 Timings for External CPU reading access |

| 8  | Refer  | ence Document                                 |

| 9  | Packa  | ge Information                                |

| 10 | Revis  | ion history                                   |

# List of tables

| Table 1.  | Pin Descriptions by Functional Groups                   |

|-----------|---------------------------------------------------------|

| Table 2.  | Pin Description by PAD Types (*LH)                      |

| Table 3.  | PAD Description                                         |

| Table 4.  | AHB Memory Map                                          |

| Table 5.  | APB Memory Map                                          |

| Table 6.  | MRC and MCR (CP15) bit pattern24                        |

| Table 7.  | Control Register                                        |

| Table 8.  | TTB Register                                            |

| Table 9.  | DAC Register                                            |

| Table 10. | TLB Operation                                           |

| Table 11. | Ethernet register map                                   |

| Table 12. | USB Host Controller Operational Register Map72          |

| Table 13. | IEEE1284 Register Map                                   |

| Table 14. | DRAM Address Bus                                        |

| Table 15. | Memory Bank Size Register 144                           |

| Table 16. | Bank size field and its corresponding actual size 144   |

| Table 17. | Register MAP and Description 148                        |

| Table 18. | Pin mapping for IEEE1284 Interface                      |

| Table 19. | Pin mapping for JTAG Interface                          |

| Table 20. | Pin mapping for nUSB_ENABLE 183                         |

| Table 21. | Pin mapping for nI2C_ENABLE 184                         |

| Table 22. | Absolute Maximum Ratings 186                            |

| Table 23. | Recommended Operating Conditions                        |

| Table 24. | DC Electrical Characteristics                           |

| Table 25. | Core power consumption ( $V_{DD}$ = 1.8V, $T_A$ = 25°C) |

| Table 26. | Expected timings for external CPU writing access        |

| Table 27. | Expected timings for external CPU reading access        |

# List of figures

| Figure 1.  | SPEAr Net Top level Bock Diagram 1            | 2  |

|------------|-----------------------------------------------|----|

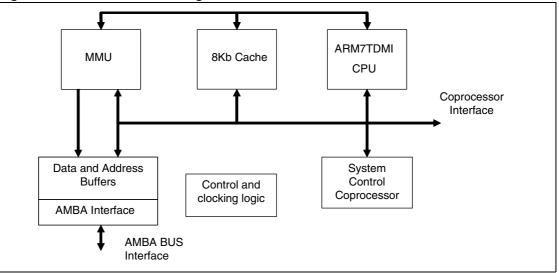

| Figure 2.  | ARM720T Block Diagram                         | 22 |

| Figure 3.  | Ethernet Controller Block Diagram 2           | 26 |

| Figure 4.  | Ethernet Frame Format                         | ;3 |

| Figure 5.  | IEEE802.3 Frame Format                        | 53 |

| Figure 6.  | DMA Descriptor chain                          | ;4 |

| Figure 7.  | USB Host Controller Block Diagram 6           | 6  |

| Figure 8.  | USB Focus Areas                               |    |

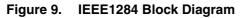

| Figure 9.  | IEEE1284 Block Diagram                        | 16 |

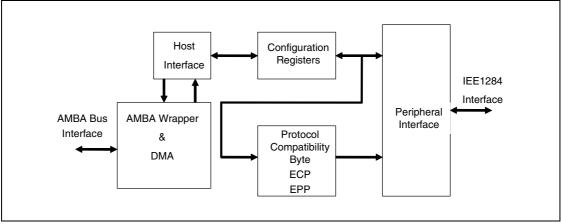

| Figure 10. | IEEE1284 - DMA Block Diagram                  |    |

| Figure 11. | UART Block Diagram                            |    |

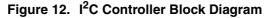

| Figure 12. | I2C Controller Block Diagram                  |    |

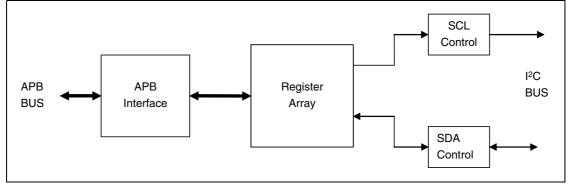

| Figure 13. | I2C Bus Protocol                              |    |

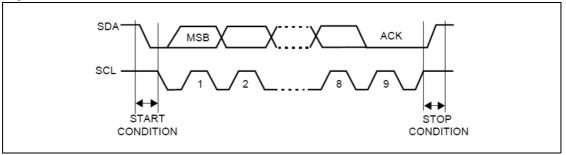

| Figure 14. | Transfer sequencing                           |    |

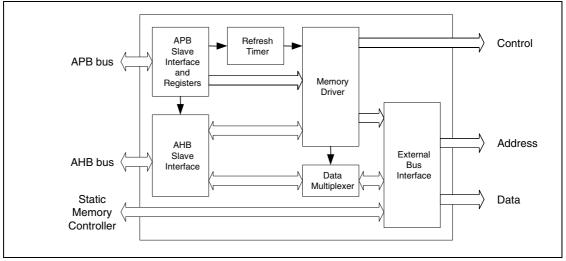

| Figure 15. | SDRAM Controller Block Diagram                |    |

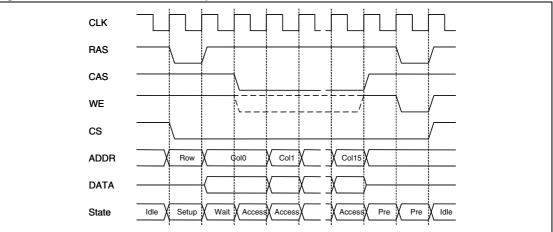

| Figure 16. | SDRAM Access Example                          |    |

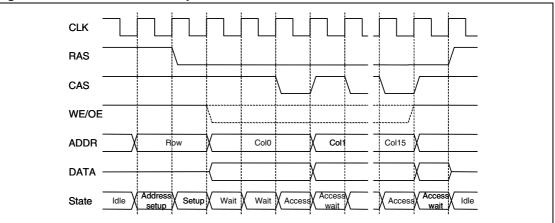

| Figure 17. | EDO Access Example                            |    |

| Figure 18. | Shared SRAM Controller Block Diagram 14       |    |

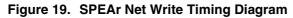

| Figure 19. | SPEAr Net Write Timing Diagram                |    |

| Figure 20. | SPEAr Net Read Timing Diagram14               |    |

| Figure 21. | DMA Controller Block Diagram                  | 60 |

| Figure 22. | RTC Block Diagram                             |    |

| Figure 23. | Timer/Counter Block Diagram                   |    |

| Figure 24. | Watch-Dog Timer Block Diagram                 |    |

| Figure 25. | Interrupt Controller Block Diagram 16         |    |

| Figure 26. | GPIO Block Diagram                            |    |

| Figure 27. | PLL Block Diagram                             |    |

| Figure 28. | POWERGOOD requirement                         |    |

| Figure 29. | External CPU writing timings                  |    |

| Figure 30. | External CPU reading timingss                 |    |

| Figure 31. | LFBGA180 Mechanical Data & Package Dimensions | 12 |

|            |                                               |    |

# **1 Product overview**

## 1.1 Overview

The SPEAR-07-NC03 is based on ARM720T RISC core, cache and MMU. It provide a bridge between four different I/F :

- 1. IEEE802.3/Ethernet MAC core for network interface. Its base interface with PHY (physical layer) chip is capable of 10/100 Mbps MII (Medium Independent Interface) and 7-wire interface.

- 2. USB host controller with both interrupt-based and DMA-based data handling method.

- 3. IEEE1284 host controller offering Compatibility mode, Nibble mode and ECP mode.

- 4. Shared RAM (Mail box method) for communication with other processors.

- 5. I<sup>2</sup>C master controller.

# 2 Features

## 2.1 Architecture

- Integrated System For Ethernet Application

- 48MHz, 3.3V I/O and 1.8V Internal Core Voltage

- ARM720T RISC Processor Core

- AMBA Rev. 2.0 System Bus Architecture

- IEEE802.3/Ethernet Compliant MAC Core

- USB Interface Solution (Host)

- IEEE1284 Interface Solution (Master)

# 2.2 ARM720T RISC Processor

- ARM7TDMI RISC Core

- 8KB Unified Instruction/Data Cache

- Enlarged Write Buffer (8 words and 4 different addresses)

- Virtual Address Support with MMU

# 2.3 External Memory Interface

- 16bit/8bit Memory Bus Support

- ROM/SRAM/Flash Static Memory Controller

- SDRAM/EDO DRAM Controller

- External I/O Bank Controller

- Independent Configurable Memory and I/O Banks

- Replaceable Memory and I/O Bank Addresses

# 2.4 IEEE802.3/Ethernet MAC

- 10/100 MAC, MAC Host block, Station Management block, Address

- Compliant with IEEE 802.3 and 802.3u specifications

- Supports 10/100 Mb/s data transfer rates

- IEEE 802.3 Media Independent Interface (MII)

- Supports full and half duplex operations

- Check block and the Control Status Register (CSR) block

# 2.5 DMA Controller

- Dedicated Channels for MAC core, USB Host and IEEE1284 interface

- 2 Channels general purpose DMA (Memory To Memory)

- 2 Channels general purpose DMA dedicated to the external requests (I/O to Memory and Memory to I/O)

- Increments/Decrements of Source/Destination Address In 16/8bit(external), 32/16/ 8(internal) Data Transfers

- Burst Transfer Mode

## 2.6 UART

- Support For 8-Bit Serial Data Tx And Rx

- Selectable 2/1 Stop Bits

- Selectable Even, Odd and No Parity

- Parity, Overrun And Framing Error Detection

- Max Transfer rate:115KBaude

## 2.7 Timers

• Channel Programmable 16-Bit Timers with 8 bit pre-scaler

# 2.8 Watchdog Timer

- For Recovery from Unexpected System Hang-up

- One Programmable 16-Bit Watchdog Timer With Reset Output Signal (more than 200 system clock period to initial peripheral devices)

- Programmable period 1 ~ 10 sec

# 2.9 GPIO (Programmable I/O)

- 4 Dedicated Programmable I/O Ports (Pins)

- 2 Multiplexed Pins with I2C Bus Signals

- Pins Individually Configurable To Input, Output Or I/O Mode

# 2.10 Interrupt Controller

- 2 External Interrupt Sources Support

- 9 Internal interrupt sources.

- All channels can be individually rerouted to the Fast (nFIQ) or to the Normal (nIRQ) processor lines

- Level and edge (rise, fall and both) selectable

- Software Controlled Priority

# 2.11 IEEE1284 Host Controller

• Compatibility/Nibble/ECP/EPP Mode Host Support

- DMA-based Data Transfer Capability for ECP

- Fully Software Controllable Operation Mode

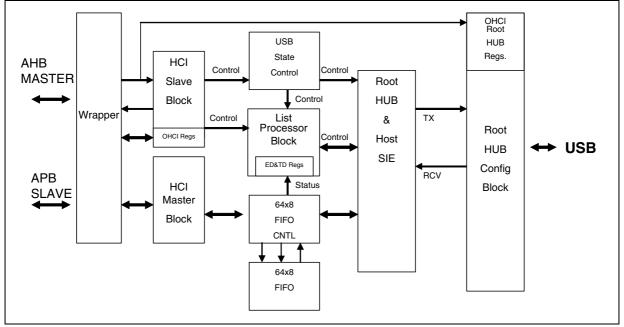

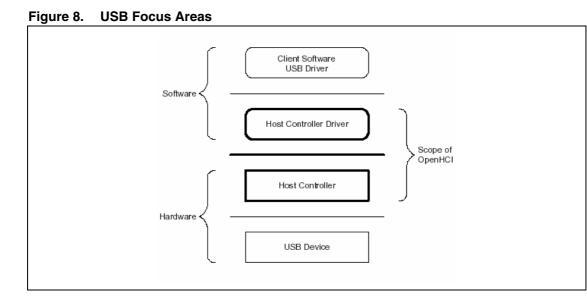

## 2.12 USB Host Controller

- Full-Speed USB compliant

- Supports Low Speed and Full Speed Devices

- Configuration data stored in Port Configurable Block

- Single 48 MHz input clock

- Integrated Digital PLL

## 2.13 Shared SRAM

- External Processor Communication Purpose

- Shared SRAM Bus Arbiter

- Same address can be accessed at the same time

- Separated from AHB Bus for Bus Traffic Reduce

- Interrupt Output Generation for Transfer Notification

## 2.14 Real Time Clock

- Real time clock-calendar (RTC)

- Clocked by 32.768MHz low power clock input

- Separated power supply (1.8 V)

- 14 digits (YYYY MM DD hh mm ss) precision

# 2.15 Frequency Synthesizer

- On-chip Frequency Synthesizer Provided

- Fin: 25 MHz.

- Fout: 48 MHz

# **3** Top-level Block Diagram

# 4 Pin Descriptions

# 4.1 Functional Pin Groups

Note: Note: symbol / means multiplexing modes

Table 1.

Pin Descriptions by Functional Groups

| Group              | Pin Name                               | Function                                                                                                                                                                                       | Remark                                        |

|--------------------|----------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|

|                    | MCLKI                                  | Oscillator Clock Input                                                                                                                                                                         | 25 MHz                                        |

|                    | MCLKO                                  | Oscillator Clock Output                                                                                                                                                                        | 25 MHz                                        |

| Clocks, Reset      | PowerGood                              | System Reset Input                                                                                                                                                                             |                                               |

| and configuration. | nResetOut                              | Peripheral Chips Driving Reset Output                                                                                                                                                          | Synchronous with System<br>Clock              |

|                    | TMODE0                                 | Test Mode Selector                                                                                                                                                                             | "1" $\rightarrow$ Test                        |

|                    | PCLK                                   | Output Clock (25 MHz)                                                                                                                                                                          |                                               |

|                    | Add[22:11],<br>Add[10]/AP,<br>Add[9:0] | Address Bus<br>Add[10]/AP is the auto pre-charge control<br>pin. The auto pre-charge command is<br>issued at the same time as burst read or<br>burst write by asserting high on Add[10]/<br>AP | ROM Banks: 16MB Max.<br>DRAM Banks: 32MB Max. |

|                    | Data[15:0]                             | External, Bi-directional, 16 bit Data Bus                                                                                                                                                      |                                               |

|                    | nRAS[3:0]/<br>nSDCS[3:0]               | Row Address Strobe for EDO DRAM/<br>nSDCS is chip select pin for SDRAM                                                                                                                         |                                               |

|                    | nSDRAS                                 | Row Address Strobe for SDRAM                                                                                                                                                                   |                                               |

| Memory             | nSDCAS                                 | Column Address Strobe for SDRAM                                                                                                                                                                |                                               |

| Interface          | SDCLK                                  | System Clock for SDRAM                                                                                                                                                                         | 48 MHz                                        |

|                    | CKE                                    | Clock enable signal for SDRAM                                                                                                                                                                  |                                               |

|                    | nWE                                    | Write Enable for external devices.                                                                                                                                                             |                                               |

|                    | nECS[1:0]                              | Chip Select for external I/O Bank                                                                                                                                                              | Banks size: 16KB                              |

|                    | nRCS[1:0]                              | Not ROM/SRAM/FLASH Chip Select                                                                                                                                                                 |                                               |

|                    | nOE                                    | Not Output Enable for memory I/O                                                                                                                                                               |                                               |

|                    | nCAS[1:0]/ DQM[1:0]                    | nCAS is the Column Address Strobe for<br>EDO DQM is data mask signal for<br>SDRAM.                                                                                                             |                                               |

| Group                  | Pin Name                          | Function                                                                   | Remark |

|------------------------|-----------------------------------|----------------------------------------------------------------------------|--------|

|                        | MDC                               | Management Data Clock                                                      |        |

|                        | MDIO                              | Management Data I/O                                                        |        |

|                        | COL/<br>COL_10M                   | Collision detected/collision detected for 10Mbps                           |        |

|                        | TX_CLK/<br>TXCLK_10M              | Transmit clock/ transmit clock for 10Mbps                                  |        |

|                        | TXD[3:0]/<br>TXD_10M/<br>LOOP_10M | Transmit data/ transmit data for 10Mbps                                    |        |

| Ethernet<br>Controller | TX_EN/<br>TXEN_10M                | Transmit enable/transmit enable for 10Mbps                                 |        |

|                        | CRS/<br>CRS_10M                   | Carrier sense/carrier sense for 10Mbps                                     |        |

|                        | RX_CLK/<br>RXCLK_10M              | Receive clock/receive clock for 10Mbps                                     |        |

|                        | RXD[3:0]/<br>RXD_10M              | Receive data/receive data for 10Mbps                                       |        |

|                        | RX_DV/<br>LINK_10M                | Receive data valid                                                         |        |

|                        | RX_ERR                            | Receive error                                                              |        |

| Group                  | Pin Name                          | Function                                                                   | Remark |

| UART                   | RXData                            | UART receive data                                                          |        |

| UANI                   | TXData                            | UART transmit data                                                         |        |

|                        | ТСК                               | Test Clock Input                                                           |        |

|                        | TDI                               | Test Data Input                                                            |        |

| JTAG Interface         | TDO                               | Test Data Output                                                           |        |

|                        | TMS                               | Test Mode select Input                                                     |        |

|                        | TRST                              | Test Reset Line                                                            |        |

| GPI/O                  | GPI/O[5:0]                        | General Purpose I/O #5 and #4/<br>I <sup>2</sup> C Bus Controller SDA, SCL |        |

|                        | SCL                               | Serial Clock line                                                          |        |

| I2C Interface          | SDA                               | Serial Data line                                                           |        |

Table 1.

Pin Descriptions by Functional Groups (continued)

| Group                              | Pin Name                | Function                                    | Remark                         |

|------------------------------------|-------------------------|---------------------------------------------|--------------------------------|

|                                    | XPData[15:0]            | External Processor Data Bus High Byte       |                                |

|                                    | XPAddr[12:0]            | External Processor Address Bus              |                                |

|                                    | nXPCS                   | Shared SRAM CS from External<br>Processor   |                                |

| External<br>Processor<br>Interface | nXPWE                   | Shared SRAM Write Strobe from Ext.<br>Proc. |                                |

|                                    | nXPRE                   | Shared SRAM Read Strobe from Ext.<br>Proc.  |                                |

|                                    | nXPWAIT                 | Wait Signal to External Processor           |                                |

|                                    | nXPIRQ                  | Interrupt Request to External Processor     |                                |

| USB                                | UHD+                    | USB Host differential Data signal high side |                                |

| 030                                | UHD-                    | USB Host differential Data signal low side  |                                |

|                                    | PpData[7:0]             | Data Lines to/from peripheral               |                                |

|                                    | nSTROBE                 | Strobe Line to peripheral                   |                                |

|                                    | nACK                    | Ack line from peripheral                    |                                |

|                                    | Busy                    | Busy line from peripheral                   |                                |

|                                    | PError                  | Paper Error line from peripheral            |                                |

| IEEE1284                           | Select                  | Selection feedback from peripheral          |                                |

|                                    | nAutoFD                 | Auto Feed signal to peripheral              |                                |

|                                    | nFault                  | Generic error line from peripheral          |                                |

|                                    | nInit                   | Init (Reset) line to peripheral             |                                |

|                                    | nSelectIn               | Select signal to peripheral                 |                                |

|                                    | PpDataDir               | Direction control for external transceiver  |                                |

| RTC                                | RTCXI                   | RTC Oscillator Input line                   | 32.768 KHz                     |

|                                    | RTCXO                   | RTC Oscillator Output line                  | 32.768 KHz                     |

|                                    | nXIRQ[1:0]              | External Interrupt request lines            |                                |

| MISC.                              | nXDRQ[1:0]              | External request lines for DMA              |                                |

|                                    | nXDACK[1:0]             | External Acknowledge lines from DMA         |                                |

|                                    | Sdram/EDO               | DRAM type selection                         | $Pull\text{-}Up\toSDRAMM$      |

|                                    | USBEnable               | USB Transceiver Enable or Disable           | Pull-up $\rightarrow$ Enabled  |

| Configuration                      | IEEE1284/<br>XProcessor | IEEE1284 or External Processor selection    | Pull-up $\rightarrow$ IEEE1284 |

|                                    | BootRomBusWidth         | Bus Width Selection for Rom 0               | Pull-up $\rightarrow$ 16 bits  |

|                                    | UART/JTAG               | Debug interface selection                   | $Pull-up\toUART$               |

|                                    | GenConf[2:0]            | General purpose Configuration lines         |                                |

|                                    | VDD_Core                | Internal Logic Core VDD (1.8V 5%)           |                                |

| Devee                              | VDD_I/O                 | I/O Pad VDD (3.3V 5%)                       |                                |

| Power                              | VDD_RTC                 | RTC VDD (1.8V 5%)                           |                                |

|                                    | GND                     | Ground                                      |                                |

Table 1.

Pin Descriptions by Functional Groups (continued)

# 4.2 PAD Types

Table 2.

Pin Description by PAD Types (\*LH)

| Ref. | Ball | Name                      | Туре         | Dir. |

|------|------|---------------------------|--------------|------|

| 1    | B1   | MCLKI                     | ANA          | -    |

| 2    | C1   | MCLKO                     | OSCI27B      | I    |

| 3    | F2   | PowerGood                 | SCHMITT_TC   | I    |

| 4    | E4   | nRESETOut                 | B4TR_TC      | 0    |

| 5    | D1   | TMODE0                    | SCHMITT_TC   | I    |

| 6    | E3   | PCLK                      | BD4TARP_TC   | 0    |

| 7    | F5   | Add0                      | B8TR_TC      | 0    |

| 8    | G4   | Add1                      | B8TR_TC      | 0    |

| 9    | G2   | Add2                      | B8TR_TC      | 0    |

| 10   | G1   | Add3                      | B8TR_TC      | 0    |

| 11   | G5   | Add4                      | B8TR_TC      | 0    |

| 12   | H4   | Add5                      | B8TR_TC      | 0    |

| 13   | H5   | Add6                      | B8TR_TC      | 0    |

| 14   | H1   | Add7                      | B8TR_TC      | 0    |

| 15   | НЗ   | Add8                      | B8TR_TC      | 0    |

| 16   | J4   | Add9                      | B8TR_TC      | 0    |

| 17   | J5   | Add10_AP                  | B8TR_TC      | 0    |

| 18   | J2   | Add11                     | B8TR_TC      | 0    |

| 19   | J3   | Add12                     | B8TR_TC      | 0    |

| 20   | K5   | Add13                     | B8TR_TC      | 0    |

| 21   | K2   | Add14                     | B8TR_TC      | 0    |

| 22   | L1   | Add15_GenConf0            | BD8STRP_TC   | I/O  |

| 23   | K4   | Add16_GenConf1            | BD8STRP_TC   | I/O  |

| 24   | L2   | Add17_GenConf2            | BD8STRP_TC   | I/O  |

| 25   | M1   | Add18_UART/JTAG           | BD8STRP_TC   | I/O  |

| 26   | N1   | Add19_BootRomBusWidth     | BD8STRP_TC   | I/O  |

| 27   | М3   | Add20_IEEE1284/XProcessor | BD8STRP_TC   | I/O  |

| 28   | N2   | Add21_USBEnable           | BD8STRP_TC   | I/O  |

| 29   | P1   | Add22_Sdram/EDO           | BD8STRP_TC   | I/O  |

| 30   | P3   | Data0                     | BD8STRUQP_TC | I/O  |

| 31   | N4   | Data1                     | BD8STRUQP_TC | I/O  |

| 32   | P4   | Data2                     | BD8STRUQP_TC | I/O  |

| 33   | N5   | Data3                     | BD8STRUQP_TC | I/O  |

| Ref. | Ball | Name               | Туре         | Dir. |

|------|------|--------------------|--------------|------|

| 34   | P5   | Data4              | BD8STRUQP_TC | I/O  |

| 35   | M6   | Data5              | BD8STRUQP_TC | I/O  |

| 36   | N6   | Data6              | BD8STRUQP_TC | I/O  |

| 37   | P6   | Data7              | BD8STRUQP_TC | I/O  |

| 38   | L6   | Data8              | BD8STRUQP_TC | I/O  |

| 39   | M7   | Data9              | BD8STRUQP_TC | I/O  |

| 40   | N7   | Data10             | BD8STRUQP_TC | I/O  |

| 41   | K7   | Data11             | BD8STRUQP_TC | I/O  |

| 42   | L7   | Data12             | BD8STRUQP_TC | I/O  |

| Ref. | Ball | Name               | Туре         | Dir. |

| 43   | M8   | Data13             | BD8STRUQP_TC | I/O  |

| 44   | K8   | Data14             | BD8STRUQP_TC | I/O  |

| 45   | P8   | Data15             | BD8STRUQP_TC | I/O  |

| 46   | N8   | nRAS0_nSDCS0       | B4TR_TC      | 0    |

| 47   | M9   | nRAS1_nSDCS1_TDI   | BD4STRUQP_TC | I/O  |

| 48   | К9   | nRAS2_nSDCS2_TDO   | B4TR_TC      | 0    |

| 49   | P9   | nRAS3_nSDCS3_nTRST | BD4STRUQP_TC | I/O  |

| 50   | N9   | nSDRAS             | B4TR_TC      | 0    |

| 51   | M10  | nSDCAS             | B4TR_TC      | 0    |

| 52   | P2   | SDCLK              | BD4TARP_TC   | 0    |

| 53   | N10  | CKE                | B2TR_TC      | 0    |

| Ref. | Ball | Name               | Туре         | Dir. |

| 54   | P11  | nWE                | B8TR_TC      | 0    |

| 55   | L10  | nECS0              | B4TR_TC      | 0    |

| 56   | P12  | nECS1              | B4TR_TC      | 0    |

| 57   | N11  | nRCS0              | B2TR_TC      | 0    |

| 58   | P14  | nRCS1              | B2TR_TC      | 0    |

| 59   | N12  | nOE                | B8TR_TC      | 0    |

| 60   | N13  | nCAS0_DQM0         | B4TR_TC      | 0    |

| 61   | M12  | nCAS1_DQM1         | B4TR_TC      | 0    |

| 62   | M13  | MDC                | B4TR_TC      | 0    |

| 63   | N14  | MDIO               | BD4STRUQP_TC | I/O  |

| 64   | M14  | COL/COL10M         | SCHMITT_TC   |      |

| 65   | K12  | TXClk/TXClk10M     | SCHMITT_TC   |      |

| 66   | L14  | TXD0/TXD010M       | B4TR_TC      | 0    |

Table 2.

Pin Description by PAD Types (\*LH) (continued)

| Ref. | Ball | Name            | Туре         | Dir. |

|------|------|-----------------|--------------|------|

| 67   | K13  | TXD1/TXD110M    | B4TR_TC      | 0    |

| 68   | K14  | TXD2/TXD210M    | B4TR_TC      | 0    |

| 69   | J12  | TXD3/TXD310M    | B4TR_TC      | 0    |

| 70   | K10  | TXEN/TXEN10M    | B4TR_TC      | 0    |

| 71   | J13  | CRS/CRS10M      | SCHMITT_TC   | I    |

| 72   | J14  | RXClk/RXClk10M  | SCHMITT_TC   | I    |

| 73   | J10  | RXD0/RXD010M    | SCHMITT_TC   | I    |

| 74   | H13  | RXD1/RXD110M    | SCHMITT_TC   | I    |

| 75   | H11  | RXD2/RXD210M    | SCHMITT_TC   | I    |

| 76   | H14  | RXD3/RXD310M    | SCHMITT_TC   | I    |

| 77   | H10  | RxDV/LINK10M    | SCHMITT_TC   | I    |

| 78   | G11  | RXERR           | SCHMITT_TC   | I    |

| 79   | G10  | RXData_TCK      | SCHMITT_TC   | I    |

| 80   | G14  | TXData_TMS      | BD4STRUQP_TC | I/O  |

| 81   | A3   | GPIO0           | BD4STRUQP_TC | I/O  |

| 82   | B4   | GPIO1           | BD4STRUQP_TC | I/O  |

| 83   | A2   | GPIO2           | BD4STRUQP_TC | I/O  |

| 84   | A1   | GPIO3           | BD4STRUQP_TC | I/O  |

| Ref. | Ball | Name            | Туре         | Dir. |

| 85   | B3   | GPIO4_SCL       | BD4STRUQP_TC | I/O  |

| 86   | C3   | GPIO5_SDA       | BD4STRUQP_TC | I/O  |

| 87   | F10  | nXIRQ0          | SCHMITT_TC   | I    |

| 88   | F14  | nXIRQ1          | SCHMITT_TC   | I    |

| 89   | E10  | nXDRQ0          | SCHMITT_TC   | I    |

| 90   | F12  | nXDRQ1          | SCHMITT_TC   | I    |

| 91   | E14  | nXDACK0         | B4TR_TC      | 0    |

| 92   | E13  | nXDACK1         | B4TR_TC      | 0    |

| 93   | E1   | RTCXO           | ANA          | -    |

| 94   | E2   | RTCXI           | OSCI32B      | 1    |

| 95   | D14  | XPData0_PpData0 | BD8STRUQP_TC | I/O  |

| 96   | E11  | XPData1_PpData1 | BD8STRUQP_TC | I/O  |

| 97   | D13  | XPData2_PpData2 | BD8STRUQP_TC | I/O  |

| 98   | B14  | XPData3_PpData3 | BD8STRUQP_TC | I/O  |

| 99   | C13  | XPData4_PpData4 | BD8STRUQP_TC | I/O  |

| 100  | C12  | XPData5_PpData5 | BD8STRUQP_TC | I/O  |

| Table 2. | Pin Description by PAD Types (*LH) (continued) |

|----------|------------------------------------------------|

|          |                                                |

| Ref. | Ball                                                          | Name              | Туре         | Dir. |

|------|---------------------------------------------------------------|-------------------|--------------|------|

| 101  | B13                                                           | XPData6_PpData6   | BD8STRUQP_TC | I/O  |

| 102  | B12                                                           | XPData7_PpData7   | BD8STRUQP_TC | I/O  |

| 103  | A13                                                           | XPData8           | BD8STRUQP_TC | I/O  |

| 104  | B11                                                           | XPData9           | BD8STRUQP_TC | I/O  |

| 105  | C10                                                           | XPData10          | BD8STRUQP_TC | I/O  |

| 106  | A11                                                           | XPData11          | BD8STRUQP_TC | I/O  |

| 107  | B10                                                           | XPData12          | BD8STRUQP_TC | I/O  |

| 108  | D10                                                           | XPData13          | BD8STRUQP_TC | I/O  |

| 109  | B9                                                            | XPData14          | BD8STRUQP_TC | I/O  |

| 110  | A9                                                            | XPData15          | BD8STRUQP_TC | I/O  |

| 111  | D9                                                            | XPAddr0_nSTROBE   | BD2STRUQP_TC | I/O  |

| 112  | C9                                                            | XPAddr1_nACK      | SCHMITT_TC   | I    |

| 113  | A8                                                            | XPAddr2_Busy      | SCHMITT_TC   | I    |

| 114  | E8                                                            | XPAddr3_PError    | SCHMITT_TC   | I    |

| 115  | D8                                                            | XPAddr4_Select    | SCHMITT_TC   | I    |

| 116  | C8                                                            | XPAddr5_nAutoFd   | BD2STRUQP_TC | I/O  |

| 117  | E7                                                            | XPAddr6_nFault    | SCHMITT_TC   | I    |

| 118  | D7                                                            | XPAddr7_nInit     | BD2STRUQP_TC | I/O  |

| 119  | B7                                                            | XPAddr8_SelectIn  | BD2STRUQP_TC | I/O  |

| 120  | C7                                                            | XPAddr9_PpDataDir | BD2STRUQP_TC | I/O  |

| 121  | A6                                                            | XPAddr10          | SCHMITT_TC   | I    |

| 122  | B6                                                            | XPAddr11          | SCHMITT_TC   | I    |

| 123  | D6                                                            | XPAddr12          | SCHMITT_TC   | I    |

| 124  | C6                                                            | nXPCS             | SCHMITT_TC   | I    |

| 125  | D5                                                            | nXPWE             | SCHMITT_TC   | I    |

| 126  | A5                                                            | nXPRE             | SCHMITT_TC   | I    |

| 127  | A4                                                            | nXPWAIT           | B4TR_TC      | 0    |

| Ref. | Ball                                                          | Name              | Туре         | Dir. |

| 128  | C5                                                            | nXPIRQ            | B4TR_TC      | 0    |

| 129  | F11                                                           | UHD+              | USB_PAD      | I/O  |

| 130  | G13                                                           | UHD-              | USB_PAD      | I/O  |

| 131  | E6, A12, E12, G12,<br>L13, P10, L8, K6, M5,<br>M2, K1, H2, F4 | VDD3I/O           | Power        | -    |

Table 2.

Pin Description by PAD Types (\*LH) (continued)

| Ref. | Ball                                                                       | Name    | Туре          | Dir. |

|------|----------------------------------------------------------------------------|---------|---------------|------|

| 144  | D2, G3, J1, K3, N3,<br>L5, P7, L9, P13, K11,<br>H12, C14, F13, A14,<br>A10 | VSS     | Power         | -    |

| 459  | F3                                                                         | VDDRTC  | Power         | -    |

| 160  | E5                                                                         | VSSRTC  | Power         |      |

| 161  | B2                                                                         | VDD3PLL | Power         | -    |

| 162  | C2                                                                         | VSSPLL  | Power         |      |

| 163  | F1, J11, E9                                                                | VDD     | Power         | -    |

| 166  | B8, A7, B5                                                                 | VSS     | Power         | -    |

| 169  | C4, C11, D3, D4, D11,<br>D12, L3, L4, L11, L12,<br>M4, M11                 | NC      | Not Connected | -    |

Table 2.

Pin Description by PAD Types (\*LH) (continued)

## Table 3. PAD Description

| PAD Name              | Description                                                                                   |

|-----------------------|-----------------------------------------------------------------------------------------------|

| ANA                   | Analog PAD Buffer                                                                             |

| B2TR_TC               | TTL Output Pad Buffer, 3 V capable, 2mA drive capability                                      |

| B4TR_TC               | TTL Output Pad Buffer, 3 V capable, 4mA drive capability                                      |

| B8TR_TC               | TTL Output Pad Buffer, 3 V capable, 8mA drive capability                                      |

| BD2STRUQP_TC          | TTL Schmitt Trigger Bidirectional Pad Buffer, 2mA drive capability, 3 V Capable, with Pull-Up |

| BD4STRUQP_TC          | TTL Schmitt Trigger Bidirectional Pad Buffer, 4mA drive capability, 3 V Capable with Pull-Up  |

| BD4TARP_TC            | TTL Bidirectional Pad Buffer, 3 V capable, 4mA drive capability, Active Slew Rate             |

| BD8STRP_TC            | TTL Schmitt Trigger Bidirectional Pad Buffer, 8mA drive capability, 3 V Capable               |

| BD8STRUQP_TC          | TTL Schmitt Trigger Bidirectional Pad Buffer, 8mA drive capability, 3 V Capable with Pull-Up  |

| OSCI27B               | Oscillator (Max Frequency 27 MHz)                                                             |

| OSCI32B               | Oscillator (32 KHz)                                                                           |

| SCHMITT_TC            | TTL Schmitt Trigger Input Pad Buffer 3 V tolerant                                             |

| USB_PAD               | USB Transceiver                                                                               |

| V <sub>DD3</sub> IOCO | Power Pad - Internal supply for 3.3 V level                                                   |

| V <sub>DD</sub> CO    | Power Pad - Internal supply for 1.8 V level                                                   |

| V <sub>SS</sub> CO    | Power Pad - Internal ground, for Core only                                                    |

| V <sub>SS</sub> IOCO  | Power Pad - Internal ground                                                                   |

# 5 Memory Map

# 5.1 Global MAP (AHB)

### Table 4.AHB Memory Map

| Starting Address | End Address | Description                                      |

|------------------|-------------|--------------------------------------------------|

|                  |             | Two ROM/FLASH/SRAM Banks.                        |

| 0x000.0000       | 0x01FE.FFFF | – Bank size granularity: 64 KB                   |

| 0,000.0000       | 0,0111.1111 | – Max Bank size: 16 MB                           |

|                  |             | <ul> <li>The two banks are adjacent.</li> </ul>  |

|                  |             | Four SDRAM/EDO Banks.                            |

| 0x1000.0000      | 0x17FF.FFFF | – Max Bank size: 32 MB                           |

| 0x1000.0000      | VXI/FE.FFFF | – Bank size granularity: 64 KB                   |

|                  |             | <ul> <li>The four banks are adjacent.</li> </ul> |

| 0x2000.0000      | 0x2000.7FFF | Two External I/O Banks                           |

| 0x2000.0000      | 0.2000.7FFF | Bank size: 16 KB                                 |

| 0x2100.0000      | 0x2100.1FFF | 8 KB Shared SRAM                                 |

| 0x2200.0000      | 0x2200.0BFF | IEEE1284 Interface & FIFOs                       |

| 0x2300.0000      | 0x2300.03FF | ARM Slave Test Interface                         |

| 0x3000.0000      | 0x3000.37FF | APB Bridge                                       |

Note: The decoder will ignore the ADD31 lines. In this way will be possible to access all the devices trough cache in range 0x000.0000 - 0x7FFF.FFFF and without cache in range 0x8000.0000 - 0xFFFF.FFFF

# 5.2 I/O MAP (APB)

| Starting Address | End Address | Description                    |

|------------------|-------------|--------------------------------|

| 0x3000.0000      | 0x3000.03FF | Interrupt Controller           |

| 0x3000.0400      | 0x3000.07FF | General Purpose Timers         |

| 0x3000.0800      | 0x3000.0BFF | Watch Dog Timer                |

| 0x3000.0C00      | 0x3000.0FFF | Real Time Clock                |

| 0x3000.1000      | 0x3000.13FF | General Purpose I/O            |

| 0x3000.1400      | 0x3000.17FF | I <sup>2</sup> C Interface     |

| 0x3000.1800      | 0x3000.1BFF | UART                           |

| 0x3000.1C00      | 0x3000.1FFF | Configuration Registers        |

| 0x3000.2000      | 0x3000.23FF | DMA Controller General Purpose |

| 0x3000.2400      | 0x3000.27FF | Static Memory Controller       |

| 0x3000.2800      | 0x3000.2BFF | Dynamic Memory Controller      |

| 0x3000.2C00      | 0x3000.2FFF | USB Host Controller            |

| 0x3000.3000      | 0x3000.33FF | DMA MAC                        |

| 0x3000.3400      | 0x3000.37FF | MAC Ethernet Controller        |

### Table 5. APB Memory Map

# 6 Blocks description

# 6.1 CPU SUBSYSTEM & AMBA BUS

### Figure 2. ARM720T Block Diagram

## 6.1.1 ARM720 Processor

The ARM720T is a general purpose 32-bit RISC microprocessor with 8KB cache, enlarged write buffer and Memory Management Unit (MMU) combined in a single chip.

The CPU within ARM720T is the ARM7TDMI.

The on-chip mixed data and instruction cache, together with the write buffer, substantially raise the average execution speed and reduce the average amount of memory bandwidth required by the processor.

The MMU supports a conventional two-level, page-table structure and the memory interface has been designed to allow the performance potential to be realized without incurring high costs in the memory system.

## 6.1.2 MMU Overview

The Memory Management MMU performs two primary functions. It:

- translates virtual addresses into physical addresses

- controls memory access permissions

The MMU hardware required to perform these functions consists of:

- a Translation Look-aside Buffer (TLB)

- access control logic

- translation-table-walking logic

When the MMU is turned off (as happens on reset), the virtual address is output directly onto the physical address bus.

## 6.1.3 Instruction and Data Cache overview

ARM720T contains an 8KB mixed instruction and data cache (IDC).

The cache only operates on a write-through basis with a read-miss allocation policy and a random replacement algorithm.

The IDC has 512 lines of 16 bytes (four words), arranged as a 4-way set-associative cache, and uses the virtual addresses generated by the processor core after relocation by the Process Identifier as appropriate.

The IDC is always reloaded a line at a time (4 words). It may be enabled or disabled via the ARM720T Control Register and is disabled immediately after the Power-On Reset.

The operation of the cache is further controlled by the Cacheable (C bit) stored in the Memory Management Page Table.

For this reason, the MMU must be enabled in order to use the IDC.

However, the two functions may be enabled simultaneously, with a single write to the Control Register.

## 6.1.4 Write Buffer Overview

The ARM720T write buffer is provided to improve system performance.

It can buffer up to eight words of data, and four independent addresses and may be enabled or disabled via the W bit (bit 3) in the ARM720T Control Register.

The buffer is disabled and flushed on reset.

The write buffer operation is further controlled by the Bufferable (B) bit, which is stored in the Memory Management Page Tables. For this reason, the MMU must be enabled so you can use the write buffer. The two functions may however be enabled simultaneously, with a single write to the Control Register.

## 6.1.5 Configuration

The operation and configuration of ARM720T is controlled:

- directly via coprocessor instructions

- indirectly via the Memory Management Page tables

The coprocessor instructions manipulate a number of on-chip registers which control the configuration of the following:

- Cache

- Write buffer

- MMU

- A number of other configuration options

## 6.1.6 Coprocessor Registers Programming

The ARM720T instruction set allows specialized additional instruction to be implemented using coprocessor.

The Memory Unit in the ARM720T core is referred as Coprocessor 15 (CP15).

**Important:** CP15 registers can only be accessed with **MRC** and **MCR** instructions in a **Privileged mode**. CDP, LDC and STC instructions, as well as unprivileged MRC and MCR instructions to CP15 cause the undefined instruction trap to be taken.

The bit fields of the instruction are shown in the following table:

#### Table 6. MRC and MCR (CP15) bit pattern

| 31 | 30    | 29 | 28 | 27 | 26 | 25 | 24 | 23   | 22  | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6   | 5 | 4 | 3  | 2 | 1 | 0 |

|----|-------|----|----|----|----|----|----|------|-----|----|----|----|----|----|----|----|----|----|----|----|----|---|----|-----|-----|---|---|----|---|---|---|

|    | Cond. |    | 1  | 1  | 1  | 0  | Ор | code | e_1 | L  |    | CI | Rn |    |    | R  | d  |    | 1  | 1  | 1  | 1 | Ор | cod | e_2 | 1 |   | CR | m |   |   |

#### Symbol Description

Cond: Condition Code Field

L: Direction

0 Store to Coprocessor (MCR)

1 Load from Coprocessor (MRC)

Rd: ARM register

CRn: Coprocessor Register

CRm: Should be zero except when accessing register 7, 8 and 13.

opcode\_1: Should be zero

opcode\_2: Should be zero except when accessing register 7, 8 and 13.

Note that the CPID field, bit 11:8, is set to 15 (MMU Coprocessor).

The assembler syntax is:

<MCRIMRC>{cond} p15, opcode\_1, Rd, CRn, CRm, opcode\_2

### 6.1.6.1 Registers

#### Register 0, ID (RO)

It is a read-only register. CRm and opcode\_2 should be zero.

Reading from this register return always 0x41807203. Last nibble is the revision number.

#### Register 1, Control (R/W)

CRm and opcode\_2 should be zero.

The control bits pattern is shown in

#### Table 7. Control Register

| 31 | 30      | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16  | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|---------|----|----|----|----|----|----|----|----|----|----|----|----|----|-----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

|    | UNP/SBZ |    |    |    |    |    |    |    |    |    |    |    | V  | UN | P/S | ΒZ | R  | S  | В  | L  | D  | Ρ | W | С | Α | М |   |   |   |   |   |

| М       | MMU enable/disable bit ( 0= disable, 1 = enable)             |

|---------|--------------------------------------------------------------|

| Α       | Alignment fault Enable/disable bit (0 = disable, 1 = enable) |

| С       | Cache enable/disable bit (0 = disable, 1 = enable)           |

| W       | Write Buffer enable/disable bit (0 = disable, 1 = enable)    |

| Р       | When read return always 1. When written is ignored.          |

| D       | When read return always 1. When written is ignored.          |

| L       | When read return always 1. When written is ignored.          |

| В       | Endianess bit ( 0 = Little Endian, 1 = Big Endian)           |

| S       | System Protection (See Access Permission AP Bits)            |

| R       | ROM Protection (See Access Permission Bits)                  |

| V       | Location of exception vectors (Windows CE)                   |

| UNP/SBZ | Unpredictable when read, Should Be Zero when written.        |

Example:

ldr r0, =0x0F

; Enable MMU with cache, write buffer and

MCR p15, 0, r0, 1, 0, 0 ; alignment fault

### Register 2, Translation Table Base (R/W)

CRm and opcode\_2 should be zero.

This is the currently active first-level translation table.

Only bit 31:14 are valid. The others are unpredictable when read, should be zero if written.

### Table 8. TTB Register

| 31 30 29 28 27 | 26 25            | 24 23 | 22 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8  | 7   | 6  | 5 | 4 | 3 | 2 | 1 | 0 |

|----------------|------------------|-------|-------|----|----|----|----|----|----|----|----|----|----|----|---|----|-----|----|---|---|---|---|---|---|

|                | TranslationTaBle |       |       |    |    |    |    |    |    |    |    |    |    |    | ļ | UN | P/S | BZ | - |   |   |   |   |   |

#### Register 3, Domain Access Control (R/W)

CRm and opcode\_2 should be zero.

The Domain Access Control Register consists of 16 2-bit fields, each of which defines the access permissions for one of the 16 Domains (D15-D0).

The meaning of this bit is described in the MMU translation mechanism.

#### Table 9. DAC Register

| 31 | 30 | 29 | 28 | 27 | 26 | 25 | 24 | 23 | 22 | 21 | 20 | 19 | 18 | 17 | 16 | 15 | 14 | 13 | 12 | 11 | 10 | 9 | 8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|----|---|---|---|---|---|---|---|---|---|---|

| D  | 15 | D  | 14 | D  | 13 | D  | 12 | D  | 11 | D  | 10 | D  | 9  | D  | 8  | D  | 7  | D  | 6  | D  | 5  | D | 4 | D | 3 | D | 2 | D | 1 | D | 0 |

### **Register 4 (Reserved)**

Register 5, Fault Status Register (FSR)

Register 6, Fault Address Register (FAR)

Register 7, Cache Operations (WO)

For this operation opcode\_2 must be 0x0b000 and CRm must be 0x0b0111.

This operation invalidates all cache data. Use with caution. Reading from it is undefined. Example:

MCR p15, 0, r0, c7, c7, 0 ; invalidate all the data inside cache

### **Register 8, TLB Operations**

Two operation are defined as showed on the following table:

#### Table 10. TLB Operation

| Function                      | Opcode_2 | CRm    | (Rd)            | Assembler Syntax          |

|-------------------------------|----------|--------|-----------------|---------------------------|

| Invalidate entire TLB         | 0b000    | 0b0111 | 0               | MCR p15, 0, Rd, C8, C7, 0 |

| Invalidate TLB (Single entry) | 0b001    | 0b0111 | Virtual Address | MCR p15, 0, Rd, C8, C7, 1 |

The Invalidate TLB invalidates all of the unlocked entries in the TLB.

The invalidate TLB single entry invalidates any TLB entry corresponding to the Virtual Address in Rd.

**Register 9 to 12 are Reserved**

**Register 13, Oricess Identifier**

Not Used

Register 14 to 15 are Reserved

# 6.2 MAC Ethernet Controller

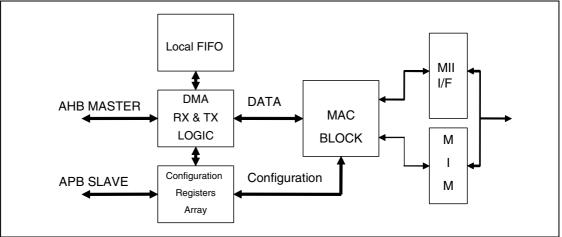

### Figure 3. Ethernet Controller Block Diagram

### 6.2.1 Overview

The Ethernet Media Access Controller (MAC110) core incorporates the essential protocol requirements for operation of an Ethernet/IEEE 802.3 compliant node, and provides interface between the host subsystem and the Media Independent Interface (MII). The MAC110 core can

operate either in 100Mbps mode or the 10Mbps mode based on the clock provided on the MII interface (25/2.5 MHz).

The MAC110 core operates both in half-duplex mode and full-duplex modes. When operating in the half- duplex mode, the MAC110 core is fully compliant to Section 4 of ISO/IEC 8802-3 (ANSI/IEEE Standard) and ANSI/IEEE 802.3. When operating in the full-duplex mode, the MAC110 core is compliant to the IEEE 802.3x standard for full-duplex operations. It is also compatible with Home PNA 1.1.

The MAC110 core provides programmable enhanced features designed to minimize host supervision, bus utilization, and pre- or post-message processing. These features include ability to disable retires after a collision, dynamic FCS generation on a frame-by-frame basis, automatic pad field insertion and deletion to enforce minimum frame size attributes, automatic retransmission and detection of collision frames.

The MAC110 core can sustain transmission or reception of minimal-sized back -to-back packets at full line speed with an inter-packet gap (IPG) of 90.6 us for 10-Mb/s and 0.96 us for 100-Mb/s.

The five primary attributes of the MAC block are:

- 1. Transmit and receive message data encapsulation

- Framing (frame boundary delimitation, frame synchronization)

- Error detection (physical medium transmission errors)

- 2. Media access management

- Medium allocation (collision detection, except in full-duplex operation)

- Contention resolution (collision handling, except in full-duplex operation)

- 3. Flow Control during Full Duplex mode

- Decoding of Control frames (PAUSE Command) and disabling the transmitter

- Generation of Control Frames

- 4. Interface to the PHY

- Support of MII protocol to interface with a MII based PHY.

- 5. Management Interface support on MII

- Generation of PHY Management frames on the MDC/MDI/MDO.

To minimize the CPU load during the data transfer is available a local DMA with FIFO capable to fetch itself the descriptors for the data blocks and to manage the data according to the instruction included on the descriptor.

## 6.2.2 Transfer Logic

### 6.2.2.1 RX LOGIC

The receive (RX) DMA block includes all the logic required to manage data transfers from the RX port of the MAC110 wrapper to an external AHB memory mapped device.

It includes:

- RX wrapper interface

- RX FIFO

- RX DMA master SM

- DMA descriptor SM

## 6.2.2.2 RX WRAPPER INTERFACE

The wrapper interface is a simple synchronous interface with RX\_nREQ, RX\_nACK, RX\_DATA signals for data handshake, plus some sideband signals for the MAC protocol support (see later). The data path (RX\_DATA) is 32 bit wide.

When the RX DMA logic has been enabled, after a valid descriptor fetch, the RX interface control logic starts driving the RX\_nACK signal, de-asserting it when

- the internal FIFO becomes full or

- the DMA transfer completes.

The wrapper logic will drive the RX\_nREQ signal when it has data valid to be transferred: the transfer is done, and the data can be updated, if RX\_nREQ and RX\_nACK are both asserted on the same clock.

#### **RX FIFO**

The FIFO depth can be 2/4/8/16/32 entries, 32 bit each.

The RX FIFO is loaded by the RX wrapper interface logic and read by the RX DMA master SM.

The FIFO download is done with 32 bits operations (possibly burst type to optimize the bus bandwidth).

If there are some incomplete words coming from the MAC core (this con occurs only at the end of the frame) the DMA adds some dummy bytes in order to complete the word and increase the performance. Added bytes have an undefined value.

#### RX DMA MASTER SM

The RX DMA block has a State Machine (SM) dedicated to the DMA master operation. When enabled via the RX configuration registers, it's able to manage the RX data transfer without further processor intervention.

The DMA transfer can be:

- DMA continuous/fixed size: the DMA can be required to run indefinitely or to stop after a configured number of data bytes has been transferred

- fixed/incrementing address: the DMA address can be fixed (i.e. all the data are transferred to the same AHB word aligned address) or it can be updated after each data transfer

- linear incrementing or wrapping address: when the address is defined as incrementing, it can be required that, once reached a programmed value, the address counter wraps back to the initial address value (the address location, pointed by the wrapping address, is not modified)

- with FIFO entry threshold: the DMA SM starts transferring data on the AHB bus when a programmable number of 32 bit RX FIFO entries is valid

When the DMA is enabled, as soon as data appears in the FIFO, the DMA may either initiate an AHB transfer immediately, or be delayed until X data bytes are available in the FIFO (FIFO entry threshold).

The DMA can be configured to wrap-round the AHB address at some point to implement a circular buffer in CPU memory.

The DMA can be configured to run indefinitely or to stop after DMA\_XFERCOUNT data have been transferred.

When the DMA completes, the master DMA SM can be required to assert an interrupt request to the processor and wait for new instruction, or to wake up the DMA descriptor SM to require a new DMA descriptor fetch.

To save gates, the implementation limits the maximum DMA transfer count to 4 Kbytes, hence the XFER\_COUNT field in the DMA control registers is limited to 12 bits.

The DMA start address (DMA\_ADDRESS) must be 32 bit word aligned.

The DMA wrapping address point must be 32 bit word aligned.

If an AHB error condition occurs, while the DMA is running, the SM activity is suspended, until the error interrupt bit (MERR\_INT) is reset. When the error condition is removed the DMA makes the same request previously interrupted by the error response.

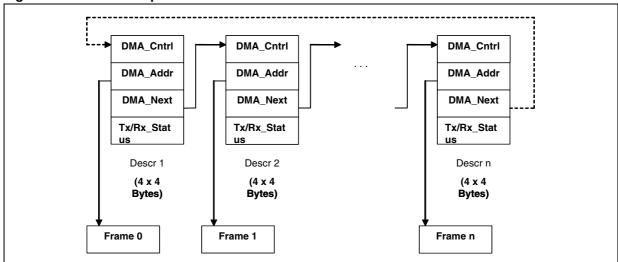

#### **DMA descriptor SM**

A dedicated SM has been implemented that, when required by the DMA master logic, starts some AHB master read operations to load from the external memory all the information (DMA descriptors) required to start the new DMA data transfer.

The DMA descriptor consists of a VALID bit plus 3 registers: the DMA control (DMA\_CTL), the DMA base address (DMA\_ADDR) and the DMA next descriptor address register (DMA\_NXT).

The Host Processor must ensure that the descriptors are up to date in memory when the DMA descriptor SM loads them. The fetch order is: DMA\_CTL, DMA\_ADDR, DMA\_NXT and VALID bit.

If a fetched descriptor is not valid (VALID=0), then the DMA engine can be programmed to stop the operation (reset the DMA\_EN bit in RX\_DMA\_START) and raise an interrupt (RX\_DONE), or to repeat the descriptor fetch operation, until a valid descriptors is found.

The interrupt register bit named RX\_NEXT is always set when a not valid descriptor is loaded.

In the first case, the DMA will then wait for the Host Processor to re-enable the DMA operation (START\_FETCH bit in the

RX\_DMA\_START register set to 1) before attempting anew descriptor fetch.

While, when in polling mode, the DMA will keep reloading the descriptor, with an access frequency determined by the DFETCH\_DLY field in the RX\_DMA\_START register.

An AHB ERROR response suspends the descriptor SM activity and reset the DMA\_EN bit in RX\_DMA\_START register. To help the error source understanding, the RX\_DMA\_CADDR register value is the address at which the error occurred.

After clearing the error bit, the SW needs to reprogram the DMA registers, to start again a new descriptor fetch.

## 6.2.2.3 TX LOGIC

The transmit (TX) DMA block includes all the logic required to manage data transfers from an external AHB memory mapped device to the TX port of the MAC110 wrapper.

It includes:

- TX wrapper interface

- TX FIFO

- TX DMA master SM

- DMA descriptor SM

#### **TX WRAPPER INTERFACE**

The wrapper interface is a simple synchronous interface with TX\_nREQ, TX\_nACK, TX\_DATA signals for data handshake, plus some sideband signals for the MAC protocol support (see later). The data path (TX\_DATA) is 32 bit wide.

When the TX DMA logic has been enabled, as soon as the internal FIFO is no more empty the TX interface control logic starts driving the TX\_nACK signal, de-asserting it when the internal FIFO becomes empty again or the DMA transfer completes.

The wrapper has to drive the TX\_nREQ signal when it accept valid data to be transferred: the transfer is done and the data can be updated if TX\_nREQ and TX\_nACK are both asserted on the same clock.

#### **TX FIFO**

The FIFO depth can be 2/4/8/16/32 entries, 32 bit each. The TX FIFO is loaded by the TX DMA master SM and read by the TX wrapper interface. The FIFO load is usually done with 32 bits operations (possibly burst type to optimize the bus bandwidth), unless the DMA end has been reached and the DMA buffer size is not a multiple of 32 bits.

#### **TX DMA MASTER SM**

The TX DMA block has a State Machine (SM) dedicated to the DMA master operation. When enabled via the TX configuration registers, it's able to manage the TX data transfers without further processor intervention.

The DMA transfer can be:

DMA continuous/fixed size: the DMA can be required to run indefinitely or to stop after a configured number of data bytes has been transferred

fixed/incrementing address: the DMA address can be fixed (i.e. all the data are transferred from the same AHB, word aligned, address) or it can be updated after each data transfer

linear incrementing or wrapping address: when the address is defined as incrementing, it can be required that, once reached a programmed value, the address counter wraps back to the initial address value (the address location, pointed by the wrapping address, is not accessed)

with FIFO entry threshold: the DMA SM starts transferring data on the AHB bus when a programmable number of 32 bit TX FIFO entries is empty

When the DMA is enabled, as soon as one free entry is available in the FIFO, the DMA may initiate AHB transfers immediately, or can be delayed. The DMA may be delayed until X data entries are available in the FIFO (FIFO entry threshold).

The DMA can be configured to wrap-round the AHB address at some point to implement a circular buffer in CPU memory.

The DMA can be configured to run indefinitely or to stop after DMA\_XFERCOUNT data have been transferred.

When the DMA completes, the master DMA SM can be required to assert an interrupt request to the processor and wait for new instruction, or to wake up the DMA descriptor SM, to require a new DMA descriptor fetch.

To save gates, the implementation limits the maximum DMA transfer count to 4Kbytes, hence the XFER\_COUNT field in the DMA control registers is limited to 12 bits.

The DMA start address (DMA\_ADDRESS) must be 32 bit word aligned and the DMA wrapping address point must be 32 bit word aligned.

If an AHB error condition occurs, while the DMA is running, the SM activity is suspended, until the error interrupt bit (MERR\_INT) is reset. When the error condition is removed the DMA makes the same request previously interrupted by the error response.

Special care must be taken when the FIFO entry to be read has 3 valid bytes: in this case, because the AHB protocol doesn't allow to 3 byte transfers, the AHB master splits the transfer in two single transfers (byte + half or half + byte) and sends an acknowledge signal to the FIFO only when the second one has been read. If the second read receives an error response then, when the error condition is removed, the DMA repeats even the first one (because the FIFO has not yet see the acknowledge).

#### DMA DESCRIPTOR SM

A dedicated SM has been implemented that, when required by the DMA master logic, starts some AHB master read operations to load from the external memory all the information (DMA descriptors) required to start the DMA data transfer.

The DMA descriptor consists of a VALID bit plus 3 registers: the DMA control (DMA\_CTL), the DMA base address (DMA\_ADDR) and the DMA next descriptor address register (DMA\_NXT).

The Host Processor must ensure that the descriptors are up to date in memory when the DMA descriptor SM loads them. The fetch order is: DMA\_CTL, DMA\_ADDR, DMA\_NXT and VALID bit.

If a fetched descriptor is not valid (VALID=0), then the DMA engine can be programmed to stop the operation (reset the DMA\_EN bit in TX\_DMA\_START) and raise an interrupt (TX\_DONE), or to repeat the descriptor fetch operation, until a valid descriptors is found. The interrupt register bit named TX\_NEXT is always set when a not valid descriptor is loaded.

In the first case, the DMA will then wait for the HP to re-enable the DMA operation (START\_FETCH bit in the TX\_DMA\_START register set to 1) before attempting a new descriptor fetch.

While, when in polling mode, the DMA will keep reloading the descriptor, with an access frequency determined by the DFETCH\_DLY field in the TX\_DMA\_START register.

An AHB ERROR response suspends the descriptor SM activity and reset the DMA\_EN bit in TX\_DMA\_START register. To help the error source understanding, the TX\_DMA\_CADDR register value is the address at which the error occurred.

After clearing the error bit, the SW needs to reprogram the DMA registers, to start again a new descriptor fetch.

### 6.2.3 Ethernet register map

#### Table 11. Ethernet register map

| Address     | Register Name | Description                                     |

|-------------|---------------|-------------------------------------------------|

| 0x3000_3000 | DMA_STS_CNTL  | Ethernet DMA, status and control register       |

| 0x3000_3004 | DMA_INT_EN    | Ethernet DMA, Interrupt sources enable register |

| 0x3000_3008 | DMA_INT_STS   | Ethernet DMA, Interrupt status register         |

| 0x3000_300C | Reserved      | -                                               |

| 0x3000_3010 | RX_DMA_START  | Ethernet DMA, RX start register                 |

| Address                      | Register Name | Description                                       |

|------------------------------|---------------|---------------------------------------------------|

| 0x3000_3014                  | RX_DMA_CNTL   | Ethernet DMA, RX control register                 |

| 0x3000_3018                  | RX_DMA_ADDR   | Ethernet DMA, RX base address register            |

| 0x3000_301C                  | RX_DMA_NXT    | Ethernet DMA, RX next descriptor address register |

| 0x3000_3020                  | RX_DMA_CADDR  | Ethernet DMA, RX current address register         |

| 0x3000_3024                  | RX_DMA_CXFER  | Ethernet DMA, RX current transfer count register  |

| 0x3000_3028                  | RX_DMA_TO     | Ethernet DMA, RX time out register                |

| 0x3000_302C                  | RX_DMA_FIFO   | Ethernet DMA, RX FIFO status register             |

| 0x3000_3030                  | TX_DMA_START  | Ethernet DMA, TX start register                   |

| 0x3000_3034                  | TX_DMA_CNTL   | Ethernet DMA, TX control register                 |

| 0x3000_3038                  | TX_DMA_ADDR   | Ethernet DMA, TX base address register            |

| 0x3000_303C                  | TX_DMA_NXT    | Ethernet DMA, TX next descriptor address register |

| 0x3000_3040                  | TX_DMA_CADDR  | Ethernet DMA, TX current address register         |

| 0x3000_3044                  | TX_DMA_CXFER  | Ethernet DMA, TX current transfer count register  |

| 0x3000_3048                  | TX_DMA_TO     | Ethernet DMA, TX time out register                |

| 0x300_304C                   | TX_DMA_FIFO   | Ethernet DMA, TX FIFO status register             |

| 0x3000_3050 -<br>0x3000_30FC | reserved      | -                                                 |

| 0x3000_3100 -<br>0x3000_317C | RX_FIFO       | RX local FIFO (32 double word = 128 byte)         |

| 0x3000_3180 -<br>0x3000_31FC | Reserved      | -                                                 |