Silicon Storage Technology, Inc.

# FlashFlex51 MCU SST89F54 / SST89F58

8051 Compatible Multi-Purpose 8-bit Microcontroller Unit with Embedded SuperFlash Memory for Flexibility

## **User's Manual**

Preliminary

Preliminary

### **Table of Contents**

| Introduction                                  | 5   |

|-----------------------------------------------|-----|

| Functional Block Diagram                      | 6   |

| Features                                      | 7   |

| Product Description                           | 8   |

| New Product Features (SST Uniqueness)         | .10 |

| SuperFlash Technology                         | 10  |

| SuperFlash Organization                       | 10  |

| SuperFlash Programmability                    |     |

| Security Lock                                 |     |

| SST89F54/58 Unique Special Function Registers | 10  |

| MCU Timing                                    | .11 |

| Machine Cycle                                 |     |

| Timing Parameters                             | 11  |

| Reset                                         | .12 |

| Power-On Reset                                | 12  |

| Architecture                                  | .13 |

| ALU                                           | 13  |

| Timing and Control                            | 13  |

| Registers                                     | 13  |

| Memory Organization                           | .14 |

| Program Memory                                |     |

| Data Memory                                   |     |

| External Memory Interface                     | .19 |

| Accessing External Memory                     | 19  |

| Reset Operation of the External Memory        |     |

### Preliminary

| Special Function Registers                                      | 21 |

|-----------------------------------------------------------------|----|

| Accumulator (ACC)                                               | 21 |

| B Register (B)                                                  | 22 |

| Program Status Word (PSW)                                       | 22 |

| RS0 and RS1                                                     | 22 |

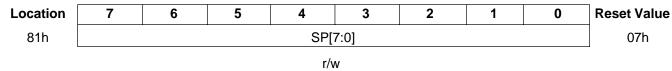

| Stack Pointer (SP)                                              | 23 |

| Data Pointer (DPTR)                                             | 23 |

| Interrupt Enable Register (IE)                                  | 24 |

| Interrupt Priority Register (IP)                                | 24 |

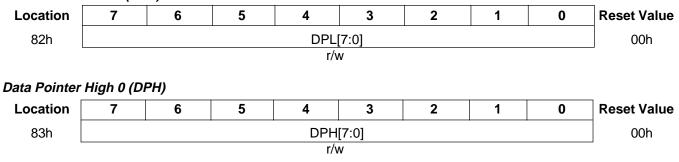

| Port Latches (P0, P1, P2, P3)                                   | 25 |

| Power Control Register (PCON)                                   | 26 |

| Serial Data Buffer (SBUF)                                       | 27 |

| Serial Port Control Register (SCON)                             | 27 |

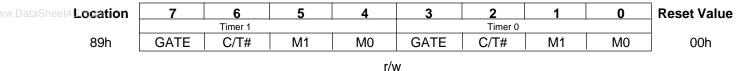

| Timer and Timer/Counter Control Registers                       | 28 |

| Timer/Counter Mode Control Register (TMOD)                      | 28 |

| Timer/Counter Control Register (TCON)                           | 29 |

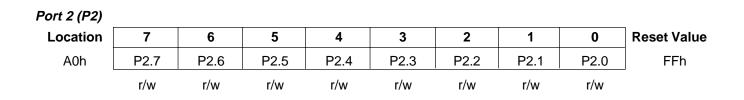

| Timer/Counter 2 Control Register (T2CON)                        | 30 |

| Watchdog Registers                                              |    |

| Watchdog Timer Control Register (WDTC)                          | 31 |

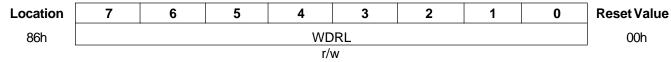

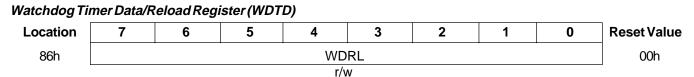

| Watchdog Timer Data/Reload Register (WDTD)                      | 32 |

| SST89F54/58 Unique Special Function Registers                   | 32 |

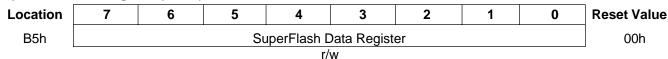

| SuperFlash Data Register (SFDT)                                 | 32 |

| SuperFlash Address Registers (SFAL, SFAH)                       |    |

| SuperFlash Command Register (SFCM)                              |    |

| SuperFlash Configuration/Status Register (SFCF)                 | 34 |

| Flash Memory Programming                                        | 35 |

| External Host Mode                                              |    |

| External Host Mode Commands                                     |    |

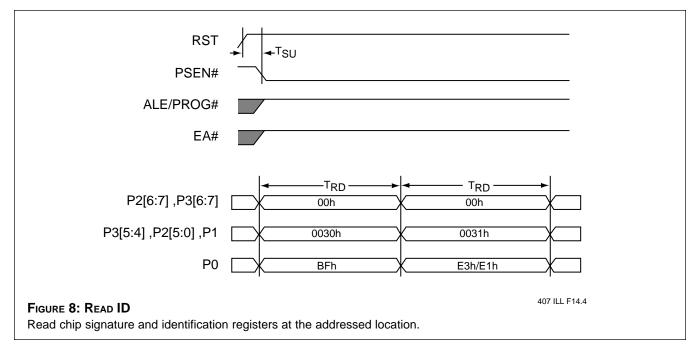

| Product Identification                                          |    |

| Programming a SST89F54/58                                       |    |

| Flash Operation Status Detection (External Host Mode Handshake) |    |

| In-Application Programming Mode                                 |    |

| In-Application Mode Commands                                    |    |

| Polling                                                         | 47 |

| Power Mode Management                                           | 10 |

|                                                                 |    |

| Power Down Mode<br>Standby (Stop Clock) Mode                    |    |

| Stanuby (Stop Clock) wode                                       | 48 |

| On-Chip Peripheral Components                                   | 49 |

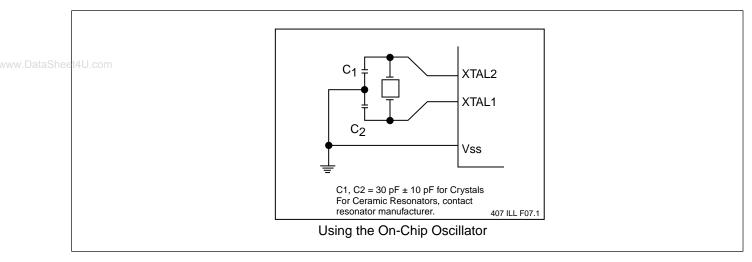

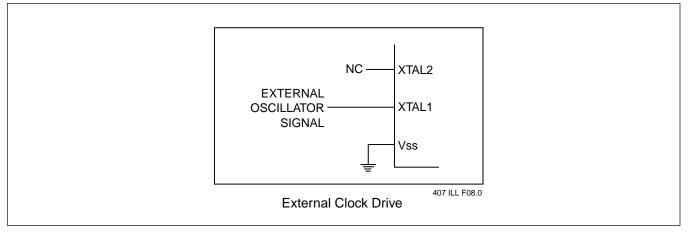

| Clock Input Options                                             | 49 |

| Timers/Counters                                                 |    |

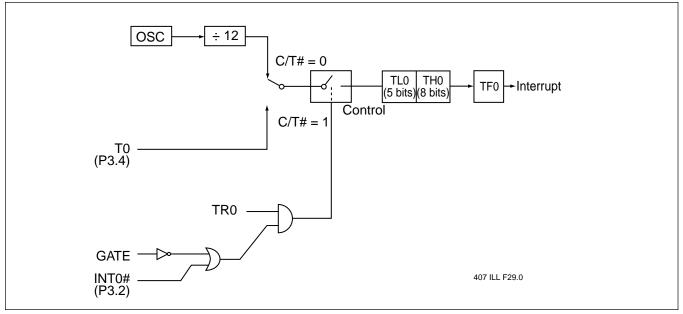

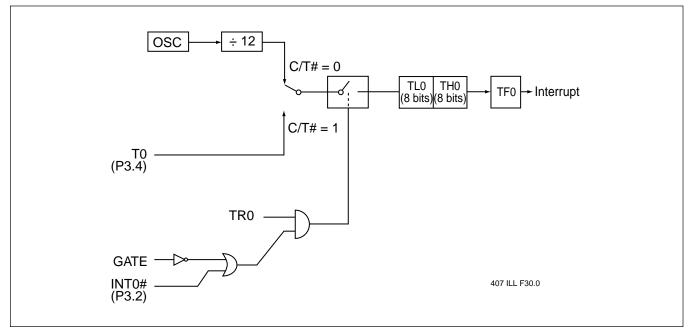

| Timer 0                                                         |    |

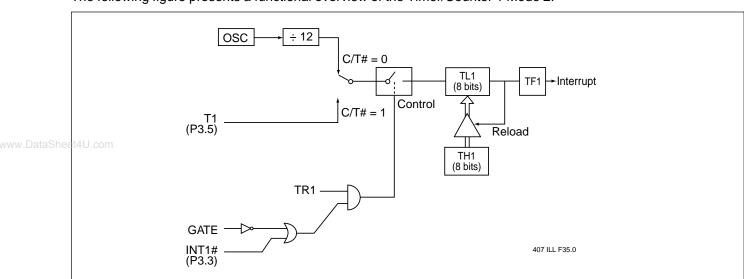

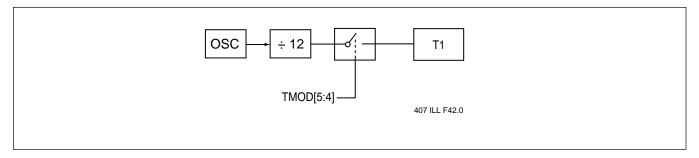

| Timer 1                                                         |    |

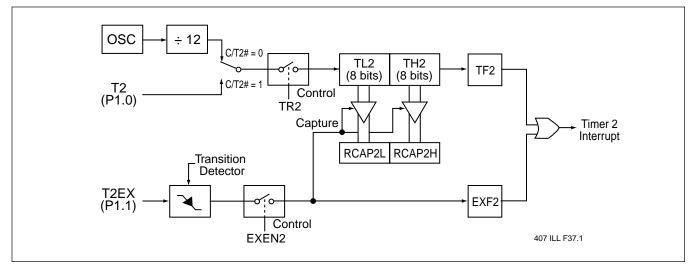

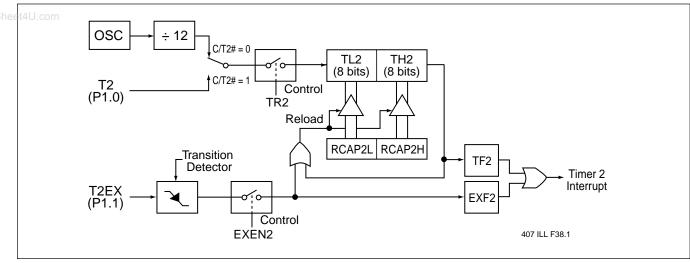

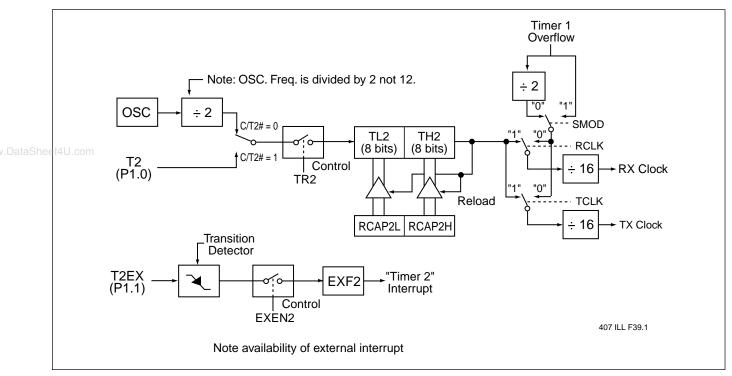

| Timer 2                                                         | 57 |

### Preliminary

| Port 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 59                                                                                                                               |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------|

| Ροπ υ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 60                                                                                                                               |

| Port 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 60                                                                                                                               |

| Port 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| Port 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| Reading and Writing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| Serial I/O (UART)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| Selecting the Mode                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |                                                                                                                                  |

| Baud Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                                                                                                                                  |

| Mode 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| et4U. Mode 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| Mode 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |                                                                                                                                  |

| Mode 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 68                                                                                                                               |

| Interrupt System                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

| Interrupt Priority Levels                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |                                                                                                                                  |

| Interrupt Execution                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |                                                                                                                                  |

| •                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |                                                                                                                                  |

| Security Lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |                                                                                                                                  |

| Activation and deactivation of the security lock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 73                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 75                                                                                                                               |

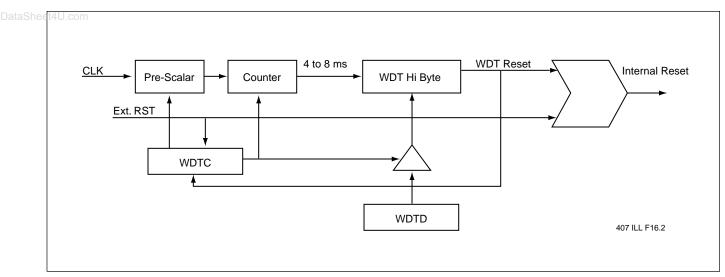

| Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

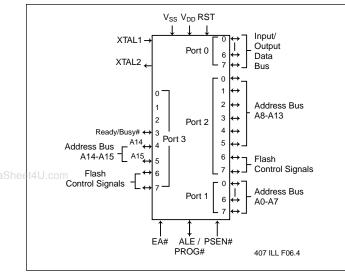

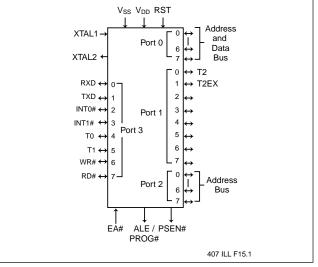

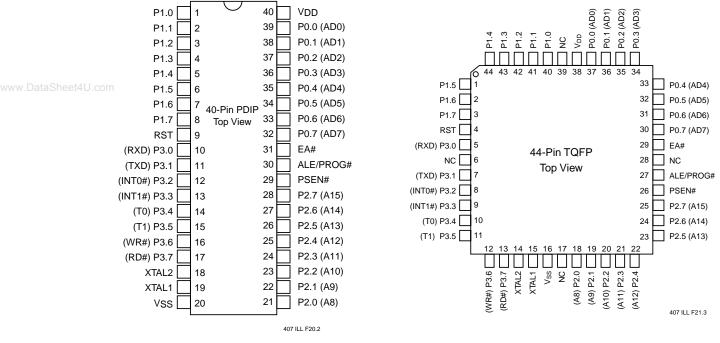

| SST89F54/58 Pin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 90                                                                                                                               |

| 55169F54/56 Fin Descriptions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |                                                                                                                                  |

| Appendix A- Programming Examples                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                                                                                                                                  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |                                                                                                                                  |

| Example 1: Using the 4K Flash Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83                                                                                                                               |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 83                                                                                                                               |

| Example 1: Using the 4K Flash Block<br>Example 2: Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83<br>86                                                                                                                         |

| Example 1: Using the 4K Flash Block<br>Example 2: Watchdog Timer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 83<br>86<br>                                                                                                                     |

| Example 1: Using the 4K Flash Block<br>Example 2: Watchdog Timer<br>Appendix B- Instruction Set<br>Arithmetic Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |                                                                                                                                  |

| Example 1: Using the 4K Flash Block<br>Example 2: Watchdog Timer<br>Appendix B- Instruction Set<br>Arithmetic Operations<br>Logical Operations                                                                                                                                                                                                                                                                                                                                                                                                                                            |                                                                                                                                  |

| Example 1: Using the 4K Flash Block         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations                                                                                                                                                                                                                                                                                                                                                                                       | 83<br>86<br>                                                                                                                     |

| Example 1: Using the 4K Flash Block<br>Example 2: Watchdog Timer<br>Appendix B- Instruction Set<br>Arithmetic Operations<br>Logical Operations                                                                                                                                                                                                                                                                                                                                                                                                                                            | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91                                                                                     |

| Example 1: Using the 4K Flash Block         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching                                                                                                                                                                                                                                                                                                                       | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>91<br>92                                                                         |

| Example 1: Using the 4K Flash Block         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching                                                                                                                                                                                                                                                                                                                       | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>91<br>92                                                                         |

| Example 1: Using the 4K Flash Block         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation                                                                                                                                                                                                                                                                                                                                                 | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>92<br>92<br>93                                                                   |

| Example 1: Using the 4K Flash Block.         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching                                                                                                                                                                                                                                                                                                                      | 83<br>86<br>89<br>                                                                                                               |

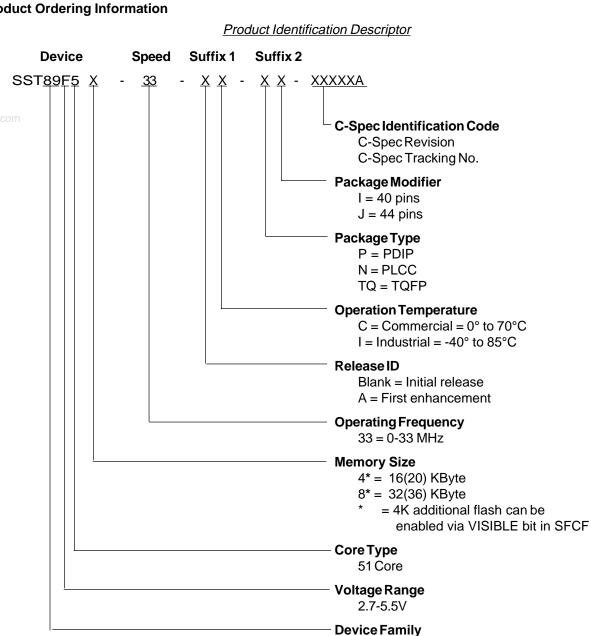

| Example 1: Using the 4K Flash Block.         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching         Appendix C- Ordering Information         Product Ordering Information                                                                                                                                                                                                                                        | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>91<br>92<br>93<br>93<br>93<br>94                                                 |

| Example 1: Using the 4K Flash Block.         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching         Appendix C- Ordering Information         Product Ordering Information         Part Number Valid Combinations         Part Number Cross-Reference Guide                                                                                                                                                       | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>92<br>92<br>93<br>93<br>93<br>93<br>95                                           |

| Example 1: Using the 4K Flash Block         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching         Appendix C- Ordering Information         Product Ordering Information         Part Number Valid Combinations         Part Number Cross-Reference Guide         Appendix D- Third Party Development Tools                                                                                                      | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>92<br>92<br>93<br>93<br>93<br>93<br>94<br>95<br>96                               |

| Example 1: Using the 4K Flash Block.<br>Example 2: Watchdog Timer<br>Appendix B- Instruction Set<br>Arithmetic Operations<br>Logical Operations<br>Data Transfer Operations<br>Boolean Variable Manipulation<br>Program Branching<br>Appendix C- Ordering Information<br>Product Ordering Information<br>Part Number Valid Combinations<br>Part Number Cross-Reference Guide<br>Appendix D- Third Party Development Tools<br>Programmers                                                                                                                                                  | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>92<br>92<br>93<br>93<br>93<br>93<br>94<br>95<br>96<br>96<br>96                   |

| Example 1: Using the 4K Flash Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83<br>86<br>89<br>89<br>90<br>90<br>90<br>91<br>92<br>93<br>93<br>93<br>93<br>93<br>94<br>95<br>96<br>98                         |

| Example 1: Using the 4K Flash Block.         Example 2: Watchdog Timer         Appendix B- Instruction Set         Arithmetic Operations         Logical Operations         Data Transfer Operations         Boolean Variable Manipulation         Program Branching         Appendix C- Ordering Information         Product Ordering Information         Part Number Valid Combinations         Part Number Cross-Reference Guide         Appendix D- Third Party Development Tools         Programmers         Programmer Adapters         Software: Compilers, Assemblers, Simulators | 83<br>86<br>89<br>90<br>90<br>90<br>90<br>91<br>92<br>93<br>93<br>93<br>93<br>93<br>94<br>95<br>96<br>96<br>98<br>98<br>98       |

| Example 1: Using the 4K Flash Block                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 83<br>86<br>89<br>89<br>90<br>90<br>91<br>92<br>92<br>93<br>93<br>93<br>93<br>93<br>94<br>95<br>96<br>96<br>98<br>98<br>99<br>99 |

### Introduction

Silicon Storage Technology, Inc. (SST) designs, manufactures and sells a variety of Electrically Erasable Programmable Read Only Memory (EEPROMs) products manufactured with SST's proprietary SuperFlash EEPROM technology. These programmable, nonvolatile memory products retain data without applied power and are much more flexible to use than other competing nonvolatile memory solutions.

When compared with alternate solutions, SST's patented processes and designs allow for the creation of high performance, high reliability and high density EEPROMs at competitive prices. Founded in 1989, SST serves the manufacturers of personal computers, notebook computers, palm computers, PC peripherals, PCMCIA cards, cellular phones, video games, electronic organizers, digital cameras, and other commercial applications requiring low power and rugged reprogrammable nonvolatile memory.

The growing use and popularity of SST's SuperFlash EEPROM technology in the flash embedded controller market has prompted the development of the SST89F54/58, the first members of the FlashFlex51 family of 8-bit, 8xC5x compatible microcontrollers. The FlashFlex51 family is a family of multi-purpose microcontroller products designed and manufactured with state-of-the-art SuperFlash CMOS semiconductor process technology. As members of the FlashFlex51 family, the SST89F54/58 use the same powerful instruction set, have the same architecture, and are pin-for-pin compatible with standard 8xC5x microcontroller devices.

The highly reliable, patented SuperFlash technology and memory cell have a number of important advantages for designing and manufacturing flash EEPROMs in the application of embedded controllers, when compared with other approaches. These advantages translate into significant cost and reliability benefits for our customers

SST has developed extensive partnerships with several major IC manufacturers. These partnerships provide SST with a guaranteed source of high quality, state-of-the-art wafers. SST agreements with large users provide the information and demand for SST to maintain a leadership position in the cost and performance driven embedded controller market.

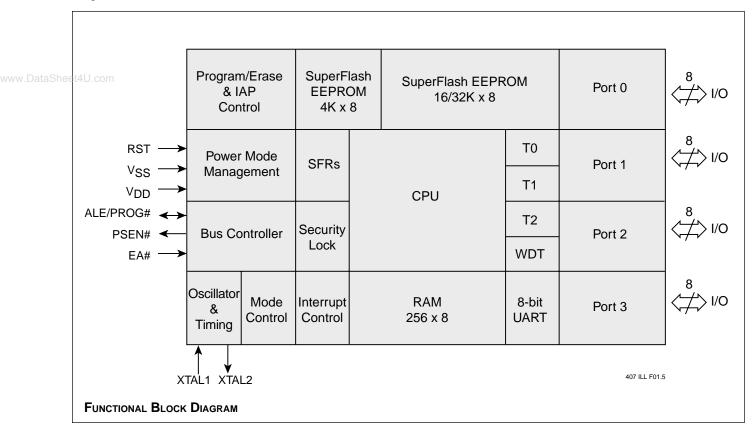

## Functional Block Diagram

The SST89F54/58 are fully compatible with the 8xC5x family of microcontrollers and may be used in applications that support the 8xC5x architecture. The functional block diagram for the SST89F54/58 is presented in the figure below. The following sections will provide a comprehensive overview of the hardware features presented in the functional block diagram.

### Features

The FlashFlex51 family is a family of embedded controllers which are comprised of the same core features, including an 8-bit MCU (ALU and register set), three Counter/Timer peripherals, and parallel and serial I/O peripherals. The SST89F54/58 support all of the standard features of 8xC5x compatible microcontrollers along with new features. A short overview of the new (non-8xC5x standard) features that the SST89F54/58 support are presented in the New Product Features section. Below is a summary of the features that the SST89F54/58 support.

- 8051 Family Compatible Multi-Purpose 8-bit Microcontroller Unit (MCU) with Embedded SuperFlash Memory for Flexibility

- ww.DataShered/UFully software and development toolset compatibility as well as pin-for-pin compatibile with standard 8xC5x microcontrollers.

- 256 Bytes register/data RAM

- 20/36 KByte Embedded High Performance Flexible SuperFlash EEPROM

- One 16/32 KByte block (128-Byte sector size)

- One 4 KByte block (64-Byte sector size)

- Individual Block Security Lock

- 87C5x Programmer Compatible

- Concurrent Operation during In-Application Programming (IAP)

- Supports External Address Range up to 64 KByte of Program and Data Memory

- High Current Drive on Port 1 (5,6,7) pins

- Three 16-bit Timer/Counters

- Programmable Serial Port (UART)

- Six Interrupt Sources at 2 Priority Levels

- Selectable Watchdog Timer (WDT)

- Four 8-bit I/O Ports (32 I/O Pins)

- TTL-and CMOS-Compatible Logic Levels

- 0 to 33 MHz Operation at 5V ± 10% Supply

- 0 to 12 MHz Operation at 3V ± 10% Supply

- Low Voltage (3V) Operation (0 to 12 MHz)

- PDIP-40, PLCC-44 and TQFP-44 Packages

- Temperature Ranges:

- Commercial (0°C to +70°C)

- Industrial (-40°C to +85°C)

Preliminary

## **Product Description**

The FlashFlex51 family is a family of embedded microcontroller products designed and manufactured on the state-ofthe-art SuperFlash CMOS semiconductor process technology. As a member of the FlashFlex51 controller family, the SST89F54/58 use the same powerful instruction set, has the same architecture, and is pin-for-pin compatible with standard 8xC5x microcontroller devices.

### MCU

The SST89F54/58 feature an enhanced 8-bit FlashFlex51 MCU, which is fully software and development toolset compatible. The MCU may operate at a frequency between 0 to 33 MHz with a 5 Volts supply.

### **Memory Organization**

The SST89F54/58 memory architecture is organized around two separate address spaces, which include one area for program memory and one area for data memory (RAM). The SST89F54/58 support up to 64 KByte of program memory with a maximum of 20/36 KByte located on-chip and the remaining memory located externally. The SST89F54/58 support up to 64 KByte of external data memory, in addition to 256 Bytes of on-chip RAM. The SST89F54/58 have 256 x 8 bits of on-chip RAM.

The SST89F54/58 internal program memory consists of Silicon Storage Technology's highly reliable, high density SuperFlash EEPROMs. SST's patented programmable, nonvolatile memory products retain data without applied power and are much more flexible to use than other competing nonvolatile memory solutions. The SST89F54/58 internal program memory consists of two SuperFlash memory blocks, Block 1 and Block 0. Block 1 is the secondary 4 KByte SuperFlash EEPROM.

### Watchdog Timer

The SST89F54/58 provide an enhanced programmable watchdog timer for fail safe protection against software hang. When a software hang or a hardware based software error occurs, the Watchdog Timer (WDT) unit provides an automatic recovery of the system by means of an internally generated watchdog reset.

### Serial I/O

The SST89F54/58 provide a full duplex Serial I/O Port that allows data to be transmitted and received simultaneously in hardware by the transmit and receive registers, respectively, while the software is performing other tasks. The Serial I/O port may operate in four different modes and perform the function of an UART (Universal Asynchronous Receiver/Transmitter) chip.

### **Power-Saving Modes**

The SST89F54/58 provide two power-saving modes of operation for applications where power consumption is critical. The two power-saving modes are Power Down and Standby (Stop Clock) modes. In the Power Down mode, the oscillator is frozen and the current draw is reduced to approximately 15% of the current drawn when the device is fully active while the supply voltage for the SST89F54/58 can be reduced to a V<sub>DD</sub> of 2V. Standby mode, like Power Down mode, reduces device current drain to approximately 15 microamperes. It is controlled by hardware (gating on/off the system clock).

### **Parallel Ports**

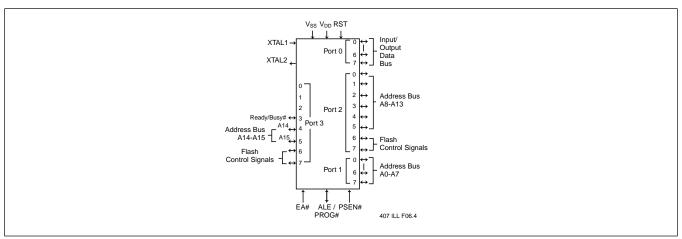

The SST89F54/58 provide four 8-bit parallel ports, which are accessed by the Port 0 (P0), Port 1 (P1), Port 2 (P2) and Port 3 (P3) special function registers. Each port consists of an output driver, an input buffer and an 8-bit latch, which is located in the port's special function register. The four parallel ports are bi-directional ports and may be used for either input or output. Port 1, Port 2 and Port 3 are multifunctional and can be used for general I/O or for alternate functions. A port pin serving in its alternate function cannot be used for normal I/O, however the alternate functions can be activated, only if the corresponding bit latch in the port special function register contains a "1". The function of the port pins also depends upon whether the system is in the External Host Mode or the In-Application Mode.

### Preliminary

### **Timers/Counters**

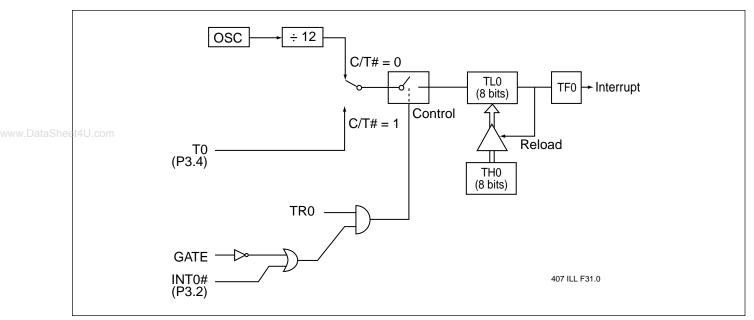

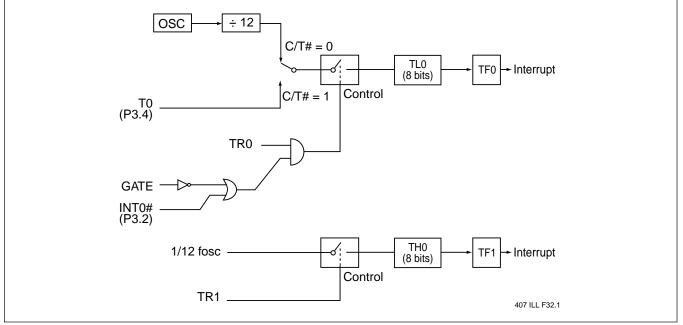

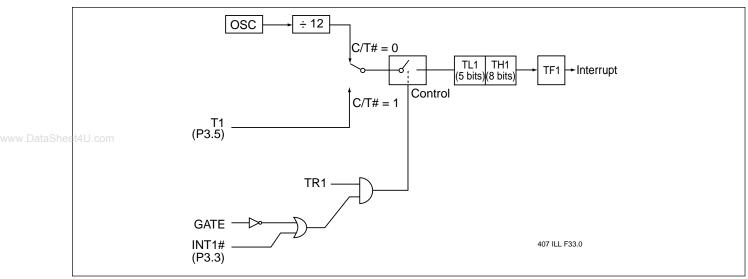

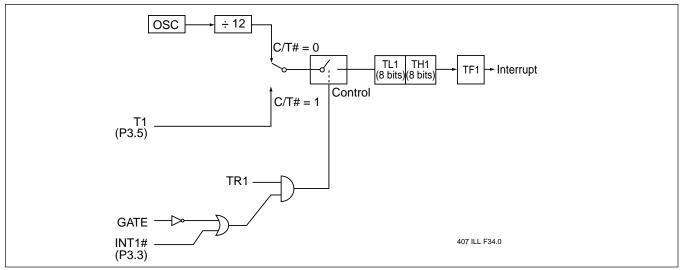

The SST89F54/58 provide three 16-bit registers that can be used as either timers or event counters. The three Timers/ Counters are the Timer 0 (T0), Timer 1 (T1) and Timer 2 (T2) registers. These three registers are located in the SFR as pairs of 8-bit registers. The low byte of the T0 register is stored in the Timer 0 LSB (TL0) special function register and the high byte of the T0 register is stored in the Timer 0 MSB (TH0) special function register. The low byte of the T1 register is stored in the Timer 1 LSB (TL1) special function register and the high byte of the T1 register is stored in the Timer 1 MSB (TH1) special function register. The low byte of the T2 register is stored in the Timer 2 LSB (TL2) special function register and the high byte of the T2 register is stored in the Timer 2 MSB (TH2) special function register. The T0, T1 and T2 registers are alternate functions of port pins.

### Interrupts

The SST89F54/58 provide 6 interrupt sources, which include two external interrupts (INT0# and INT1#), three Timer/ Counter interrupts (TF0, TF1 and TF2), and one from the serial port (SI or TI). The Interrupt Enable (IE) special function register is the source of the interrupts. Each of the bits that generate the interrupts may be set or cleared by software with the same result as setting or clearing the bits through hardware. Therefore, interrupts may be generated or canceled by software. Individual interrupts can be enabled or disabled by setting or clearing individual bits of the IE register. The SST89F54/58 also contain a global enable bit which allows all of the interrupts to be enabled or disabled by setting or clearing the EA bit of the IE register.

### New Product Features (SST Uniqueness)

### SuperFlash Technology

The SST89F54/58 are members of the FlashFlex51 family of embedded 8-bit microcontrollers. The FlashFlex51 family is a family of embedded microcontroller products designed and manufactured on the state-of-the-art SuperFlash CMOS semiconductor process technology. As a member of the FlashFlex51 controller family, the SST89F54/58 use the same powerful instruction set, have the same architecture, and are pin-for-pin compatible with standard 8xC5x microcontroller devices.

### SuperFlash Organization

SST89F54/58 come with 20/36 KByte of integrated on-chip flash EEPROM program memory, using the patented and proprietary SST CMOS SuperFlash EEPROM technology and the SST field enhancing tunneling injector split-gate memory cells. The Super Flash memory is partitioned into 2 independent program memory blocks. The primary 16/32 KByte SuperFlash memory occupies the standard 8xC5x's 16/32 KByte of internal ROM space and the secondary 4 KByte SuperFlash block occupies the upper most of the 64 KByte address space for the 8xC5x architecture.

### SuperFlash Programmability

Typical 8xC5x microcontrollers, while referencing program storage, can only read instructions, even though the physical device used for external program storage can read/program, it is effectively read-only memory. This is due to the fact that the ROM is masked at the factory and once the ROM chips are masked, the program cannot be changed. However, SST solves this user restriction by implementing flash memory blocks that can be programmed via a standard 87C5x EPROM programmer or a standard flash EEPROM memory programmer fitted with a special adapter and firmware for SST89F54/58 devices. During power-on reset, the SST89F54/58 can be configured as a master for In-Application Programming (IAP) operation or as a slave to an external host. The SST89F54/58 are designed to be programmed "in-place" and "in-operation" on the printed circuit board assembly for maximum flexibility.

### Security Lock

The SST89F54/58 provide a security lock mechanism, that prevents program code corruption resulting from accidental sector or block erasing/programming erroneous program code to the internal flash memory blocks. The security lock also prevents software piracy by disabling the read access of the internal flash memory contents. When the security lock is activated, the MOVC instructions executed from external program memory or flash memory are disabled from fetching code bytes from unlocked memory blocks.

### SST89F54/58 Unique Special Function Registers

The SST89F54/58 not only provide the standard 8xC5x SFRs, but it also implements seven new registers, which include the SFDT, SFAL, SFAH, SFCM, SFCF, WDTD and WDTC registers. The SFDT, SFAL, SFAH, SFCM and SFCF support the SuperFlash EEPROM memory and the WDTC and WDTD registers support the Watchdog Timer.

### **MCU** Timing

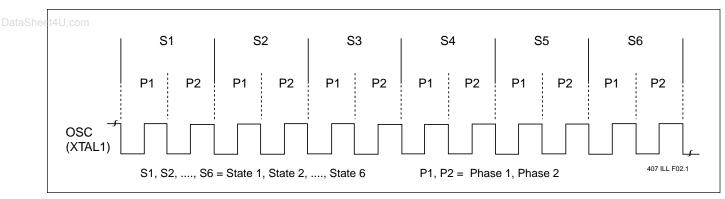

### Machine Cycle

The SST89F54/58 machine cycle consists of six states, which are divided into two phases that are one clock period for each phase. Therefore, the SST89F54/58 machine cycle is 12 clock periods. Operating the SST89F54/58 with a low voltage, (3 Volts supply) limits the MCU to a frequency between 0 to 12 MHz and a machine cycle limited to a maximum of 1 ms.

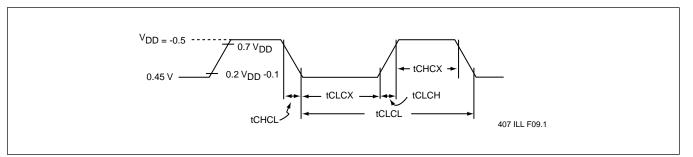

FIGURE 1: MACHINE CYCLE WAVEFORM

### **Timing Parameters**

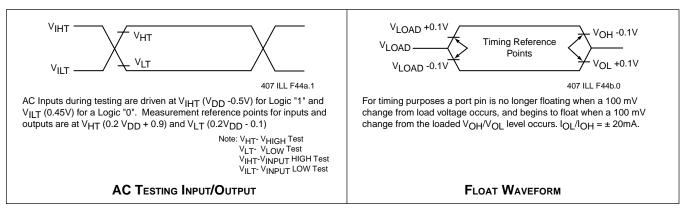

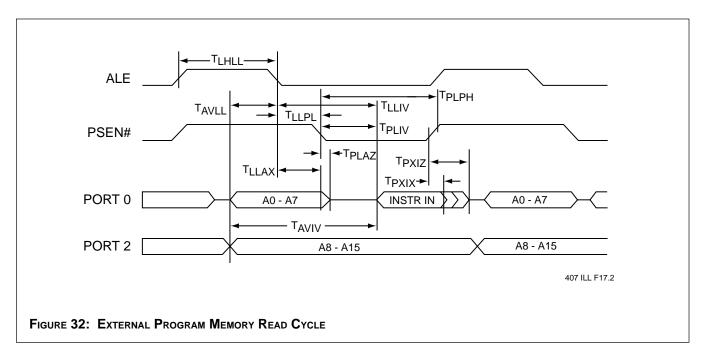

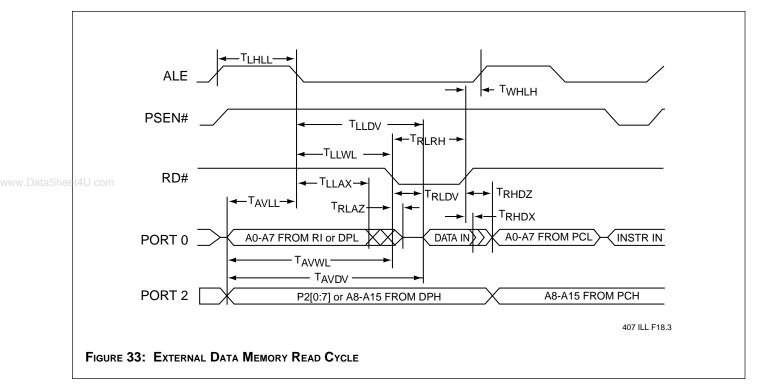

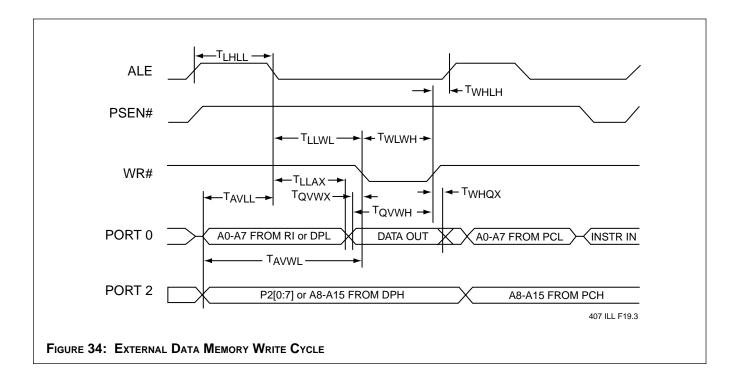

The timing characteristics for the PSEN#, ALE, RD# and WR# signals are presented in the AC Characteristics Table in the Appendix section. External Program Memory Read, External Data Memory Read, and External Data Memory Write Cycle Waveforms are also presented in the Appendix section.

Note that the timings published in the AC Characteristics Table of the Appendix section includes the propagation delays for the given testing specifications. The parameter values are subject to change without notice.

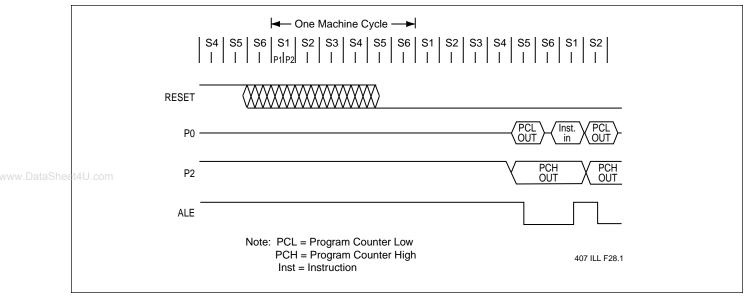

FIGURE 2: RESET WAVEFORM

### Reset

A system reset initializes the MCU and begins program execution at program memory location 0000h. The reset input for the SST89F54/58 is the RST pin. In order to reset the SST89F54/58, a logic level high must be applied to the RST pin for at least two machine cycles (24 clocks), after the oscillator becomes stable. ALE, PSEN# are weakly pulled high during reset. During reset, ALE and PSEN output a high level in order to perform correct reset. This level must not be affected by external element. A system reset will not affect the 256 Bytes of on-chip RAM while the SST89F54/58 is running, however, the contents of the on-chip RAM during power up are indeterminate. All Special Function Registers (SFR) return to their reset values, which are outlined in the Special Function Registers section. The Machine Cycle Waveform figure below presents the reset timing waveform

After a successful reset is completed, if the PSEN# pin is driven by an input force with a high-to-low transition while the RST input pin is continually held high, the device will enter the External Host mode for the internal flash memory programming operation. Otherwise the device will enter the IAP mode.

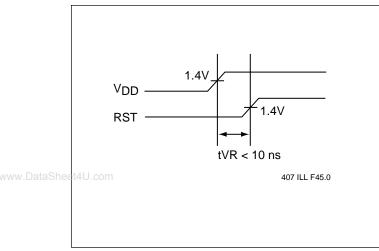

### **Power-On Reset**

At initial power up, the port pins will be in a random state until the oscillator has started and the internal reset algorithm has written one's to all the pins. Powering up the device without a valid reset could cause the CPU to start executing instructions from an indeterminate location. Such undefined states may inadvertently corrupt the code in the flash.

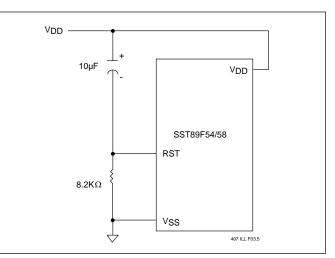

To ensure a good power-on reset, it is required that the V<sub>DD</sub> rise time does not exceed 1 ms and the oscillator start up time does not exceed 10 ms. The Minimum V<sub>DD</sub> to RST for Power-On Reset figure below shows the maximum delay time allowed between initial power up and reset. RST should lag no more than 10 ns behind V<sub>DD</sub> at voltages above 1.4 V. A common method to extend the RST signal is to implement a RC circuit by connecting the RST pin to V<sub>CC</sub> through a 10  $\mu$ F capacitor and to V<sub>SS</sub> through an 8.2K resistor as shown in the Power-On Reset circuit in Figure 4. This method maintains the necessary relationship between V<sub>DD</sub> and RST to avoid programming at an indeterminate location which may cause code corruption in the flash.

### Preliminary

### Architecture

The MCU in the SST89F54/58 family is an enhanced 8-bit FlashFlex51 MCU, which is fully software and development toolset compatible as well as pin-for-pin compatible to standard 8xC5x microcontrollers. The MCU is composed of three sections, which consist of an arithmetic logic unit (ALU), a timing and a Timing and Control section, and Registers section.

### ALU

Data byte manipulation is controlled by the ALU. The ALU performs all addition, subtraction, multiplication, division and logic operations such as logical AND and OR. The ALU section is internal to the microcontroller MCU and is not under the programmer's direct control.

### **Timing and Control**

The Timing and Control section is responsible for synchronizing the flow of data into and out of the MCU. It coordinates the movement of data on the buses both internal and external to the microcontroller. The PSEN#, RD# and WR# signals are generated by the Timing and Control section. This section is internal to the microcontroller MCU and is not under the programmer's direct control. However, the operating frequency of the MCU may be changed by using an external oscillator.

### Registers

The Registers section is composed of 8-bit latches which are used to hold and manipulate data. The register section of the SST89F54/58 are made up of two register groups, which include the 8-bit special function registers and the eight general-purpose 8-bit register banks. The only section of the MCU that is directly controllable by the programmer is the Registers section.

The Special Function Registers (SFR) are standard components of 8xC5x compatible microcontrollers, which perform specific, required tasks. Every normal processor register, except the eight general-purpose register banks, and special function corresponds to a special function register. Processor registers such as the accumulator (ACC), the program status word register (PSW), the data pointer to external memory (DPL and DPH) and the stack pointer (SP) are controlled by special function registers. Also, all internal features such as the Watchdog Timer, Power Mode Management, Timers/Counters, Parallel Ports, Serial Port, Security Lock and SuperFlash memory functions, are controlled by special function registers. The special function registers function much like accumulators, and programming them is simple and convenient.

The 8 general-purpose 8-bit register banks are called R0 through R7 and are grouped into four banks of eight bytes each. The general-purpose registers provide scratchpad RAM for temporary values.

Preliminary

## **Memory Organization**

The SST89F54/58 memory architecture is organized around two separate address spaces, which include one area for program memory (ROM) and one area for data memory (RAM). The SST89F54/58 support up to 64 KByte of program memory with a maximum of 20/36 KByte located on-chip and the remaining memory located externally. The SST89F54/58 support up to 64 KByte of external data memory. The SST89F54/58 have 256 x 8 bits of on-chip RAM.

The Timing and Control (T/C) bus is used in order to distinguish between the overlapping program and data memory spaces. The control lines used to access external data memory are the RD# and WR# lines. The RD# line is active for an external data memory write. The control line used to read program memory is the Program Store Enable (PSEN#) line. Note that there is no equivalent WR# line for program memory since there are no instructions that permit programming to program memory. Internal data memory is accessed through indirect addressing techniques.

### Program Memory

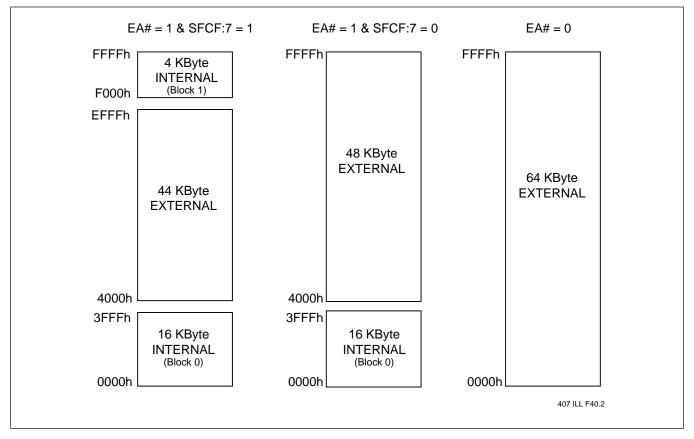

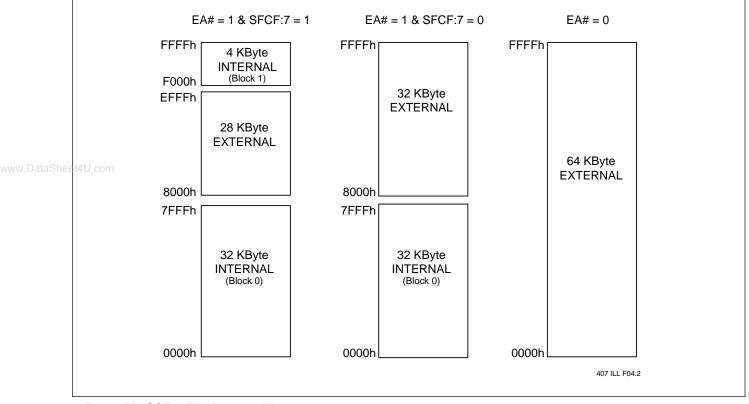

The SST89F54/58 program memory structure is unique in that it provides two different options for memory organization. The figures below present the two options for program memory organization for the SST89F54 and SST89F58.

#### FIGURE 5A: SST89F54 PROGRAM MEMORY ORGANIZATION

#### Preliminary

FIGURE 5B: SST89F58 PROGRAM MEMORY ORGANIZATION

As demonstrated in the figure, the Secondary Flash Block Visibility (VIS) bit of the SuperFlash Configuration (SFCF) register and the External Access (EA#) signal produced by the EA# pin of the bus controller determine the program memory organization. The EA# pin must be strapped to Vss in order to enable the SST89F54/58 to fetch code from External Program Memory locations starting at 0000h to FFFFh. Note, however, that if either of the Lock bits (SFCF[6:5]) of the SFCF register are read, the logic level at the EA# pin will be internally latched during reset. The various combinations of the Lock bits and the results are presented in the table below.

| SFCF.6    | SFCF.5 | Security Lock Decoding                                                      |

|-----------|--------|-----------------------------------------------------------------------------|

| 1         | 1      | Flash Block 0 and Block 1 are locked                                        |

| t4U.com 1 | 0      | Both locked but they are accessible only through In-Application Programming |

| 0         | 1      | Flash Block 1 is locked                                                     |

| 0         | 0      | No Flash Blocks are locked                                                  |

The EA# pin must be strapped to  $V_{DD}$  in order to enable the SST89F54/58 to fetch code from internal program memory. The VIS bit serves as an Secondary Flash Block Visibility selector for the 4KByte block of internal flash program memory. The VIS bit must be set in order for the 4 KByte block of internal flash program memory to be visible at the top of the secondary 64 KByte address range. The VIS bit must be cleared in order for the 4KByte block of internal flash memory to not be visible.

When the EA# line is inactive, the program memory for the SST89F54 is composed of two memory blocks. The primary memory block is 16 KByte of flash memory and occupies the address space 0000h to 3FFFh. The 48 KByte of external memory occupies the address space 4000h to FFFFh. When the 4 KByte flash memory is visible, it resides in the secondary memory block and occupies the address space F000h to FFFFh. The 16KByte primary SuperFlash block are organized as 128 sectors with sector address from A15 to A7. Each sector contains 2 rows with row address from A15 to A6. Each row has 64 Bytes with byte address from A5 to A0.

When the EA# line is inactive, the program memory for the SST89F58 is composed of two memory blocks. The primary memory block is 32 KByte of flash memory and occupies the address space 0000h to 7FFFh. The 32 KByte of external memory occupies the address space 8000h to FFFFh. When the 4 KByte flash memory is visible, it resides in the secondary 4KByte memory block and occupies the address space F000h to FFFFh. The 32 KByte primary SuperFlash block are organized as 256 sectors with sector address from A15 to A7. Each sector contains 2 rows with row address from A15 to A6. Each row has 64 bytes with byte address from A5 to A0.

When internal code operation is enabled (EA# = 1), the secondary 4 KByte flash memory block is selectively visible for code fetching. The secondary block is always accessible through the SuperFlash mailbox registers: SFCM, SFCF, SFAL, SFAH and SFDT. When bit 7 of the SuperFlash Configuration/Status mailbox register (SFCF:7), SFR address location F7h, is set, the secondary 4 KByte block will be visible by program counter. The 4K x 8 secondary SuperFlash block are organized as 64 sectors with sector address from A15 to A6. Each sector contains 2 rows with row address from A15 to A5. Each row contains 32 bytes with byte address from A4 to A0.

Note that after reset, the MCU begins fetching instructions starting at address 0000h. The physical location of address 0000h is either on-chip or external, depending on the value of the EA# line. If the EA# line is a logic low, address 0000h and all other program storage addresses will reference external program memory. If the EA# line is a logic high, address 0000h will reference on-chip program memory. Also note that each interrupt service routine is associated with an interrupt vector address located in the interrupt vector table, which starts at 0003h. The physical location of address 0003h will depend on the logic level of the EA# line as well.

### **Data Memory**

The SST89F54/58 data memory structure consists of 256 Bytes of on-chip RAM and can address up to 64 KByte of external data memory. Note that the 256 Bytes of on-chip RAM is not affected by a system reset while the SST89F54/58 is running, however, the contents of the on-chip RAM during power up is indeterminate.

The 4 KByte of small sectors (64 Bytes per sector) on chip flash memory to be mapped either as program memory or data memory. When the 4KByte flash is mapped as data memory (SFCF:7=0) it is accessible via the mailbox registers.

ww.DataSheet4U.com

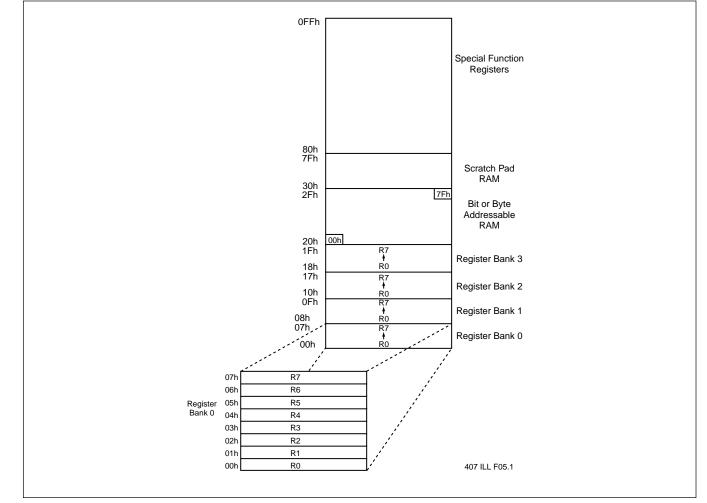

FIGURE 6: INTERNAL DATA MEMORY (256 BYTES RAM)

The secondary 128 Bytes of the 256 Bytes of on-chip RAM contain the Special Function Registers. The Special Function Registers reside at memory locations 80h through FFh in the on-chip RAM. More information about the Special Function Registers is presented in the Special Function Registers section.

The lowest 32 Bytes of the lower 128 Bytes are grouped into four banks of eight one-byte registers. The four banks reside at memory locations 00h through 1Fh in the on-chip RAM. The four banks are simply groups of eight bytes that may be used for general-purpose storage, however, only one bank is activated at a time. The active bank is selected by a combination of the RS1 and RS0 bits in the PSW register as outlined in the table below. Note that RS1 and RS0 can be set by program instructions.

### REGISTER BANK SELECT TABLE

| eet4U.com <b>RS1</b> | RS0 | REGISTER BANK | ADDRESS |

|----------------------|-----|---------------|---------|

| 0                    | 0   | 0             | 00h-07h |

| 0                    | 1   | 1             | 08h-0Fh |

| 1                    | 0   | 2             | 10h-17h |

| 1                    | 1   | 3             | 18h-1Fh |

The eight registers in the active bank are byte addressable. They can be read or written to by the program and may be referred to as R0 through R7. **Note:** after reset, the stack pointer (SP) is pointing to the top register of the lowest bank (address 07h), causing the stack to start at 8h. In order to avoid writing stack data into the registers, it is required that a new address is loaded into the SP before any CALL or PUSH instructions are used.

The next 16 Bytes of the lower 128 Bytes form a block that can be addressed as either bytes or as 128 individual bits. The block of bit or byte addressable RAM resides at memory locations 20h through 2Fh in the on-chip RAM. The byte addresses are 20h to 2Fh. The bit addresses are 00h to 7Fh. The format of the instruction determines whether the reference is to a byte or a bit.

The remaining 80 bytes of the lower 128 Bytes form a block that can be used as scratch pad RAM. The scratch pad RAM resides at memory locations 30h through 7Fh in the on-chip RAM.

The external data memory consists of up to 64 KByte of memory and resides at memory locations 0000h through FFFFh. The external data memory can be accessed by using indirect addressing techniques. The 16-bit Data Pointer (DPTR) register is used to store the address of the external memory location. The low byte of the DPTR register is stored in the Data Pointer High (DPH) register.

### **External Memory Interface**

The main function of the external bus interface is to connect the external memory to the MCU. The external bus also facilitates the expansion of the external data memory. The SST89F54/58 memory architecture supports up to 64 Kbyte of external data memory. The external data memory resides at memory locations 0000h through FFFFh can be accessed by using indirect addressing techniques. The 16-bit Data Pointer (DPTR) register is used to store the address of the external memory location. The low byte of the DPTR register is stored in the Data Pointer Low (DPL) register and the high byte of the DPTR register is stored in the Data Pointer High (DPH) register.

### **Accessing External Memory**

The SST89F54/58 memory architecture is organized around two separate address spaces, which include one area for program memory (ROM) and one area for data memory (RAM). The SST89F54/58 support up to 64 KByte of program memory with a maximum of 20/36 KByte located on-chip and the remaining memory located externally. The SST89F54/58 support up to 64 KByte of external data memory, in addition to 256 Bytes of on-chip RAM.

The Timing and Control (T/C) bus is used in order to distinguish between the overlapping program and data memory spaces. External Program Memory is accessed when the EA# signal is active or the program counter (PC) contains an address that is larger than FFFFh. The control lines used to access external data memory are the RD# and WR# lines. The RD# line is an alternate function of the Port 3 bit P3.7 and the WR# line is an alternate function of the Port 3 bit P3.6. The RD# line is active for an external data memory read and the WR# line is active for an external data memory write. The control line used to read program memory is the Program Store Enable (PSEN#) line. Note that there is no equivalent WR# line for program memory since there are no instructions that permit programming to program memory. Internal data memory is accessed through indirect addressing techniques.

Instructions which access external program memory always use a 16-bit address. Instructions which access external data memory may use either an 8-bit (MOVX@RI) or a 16-bit (MOVX@DPTR) address, depending on the instruction being executed. An instruction that uses a 16-bit address outputs the high byte of the address to Port 2, where it is held for the duration of the read or write cycle. During this time the Port 2 latch (P2) does not have to contain 1's and the contents of Port 2 are not lost. If the external memory cycle is not immediately followed by another external memory read or write cycle, the prior contents of the Port 2 latches are restored after the memory access cycle. Note that if an 8-bit address is being used, the contents of the Port 2 latches are unchanged and remain at the Port 2 pins throughout the external memory cycle.

Instructions which access external program or data memory output the low byte of the address to Port 0. During this time, the Port 0 pins are connected to an internal active pull-up and they do not float. The ALE signal is used to capture the address byte into an external latch. The address byte is valid at the negative transition of the ALE signal. For a write instruction, the data byte to be written is sent to Port 0 just before the WR# signal is activated and remains there until after the WR# signal is deactivated. For a read instruction, the data byte to be read is read from Port 0 just before the read strobe is deactivated. During any access to external memory, the MCU writes 0FFh to Port 0, therefore, the prior contents of the Port 0 latches are lost.

### Preliminary

### **Reset Operation of the External Memory**

A system reset initializes the MCU and begins program execution at program memory location 0000h. The physical location of address 0000h is either on-chip or external, depending on the value of the EA# line. If the EA# line is a logic low, address 0000h and all other program storage addresses will reference external program memory. If the EA# line is a logic high, address 0000h will reference on-chip program memory.

The reset input for the SST89F54/58 is the RST pin. In order to reset the SST89F54/58, a logic level high must by applied to the RST pin for at least two machine cycles, while the oscillator is running. The reset signal is asynchronous to the system clock, however, the RST pin is sampled during the second phase of the fifth state of every machine cycle. A power-on reset also requires a logic level high to by applied to the RST pin for at least two machine cycles, providing that the V<sub>DD</sub> rise time does not exceed a millisecond and the oscillator start up time does not exceed 10 milliseconds.

After a successful reset is completed, if the PSEN# pin is driven by an input force with a high-to-low transition while the RST input pin is continually held high, the device will enter the External Host mode for the internal flash memory programming operation, otherwise the device will enter normal operation. In normal operation, the content of the external RAM is not affected by a reset, as long as the power supply is not turned off. However, after a power-on reset, the content of the external RAM is undefined. If the reset occurs during a write instruction to the external RAM, the content of the external RAM memory location depends on the machine cycle in which the active reset signal is detected. In the case of the 2-cycle MOVX instruction, the external RAM will not be affected if the instruction is in its first cycle, however it is overwritten if the instruction is in its second cycle. Note that a system reset will not affect the on-chip RAM while the SST89F54/58 are running, however, the contents of the on-chip RAM during power up are indeterminate.

### **Special Function Registers**

The Special Function Registers (SFRs) are standard components of 8xC5x compatible microcontrollers which perform specific, required tasks. The registers are eight bits each and are located in internal data memory at memory locations 80h - FFh in the secondary 128 Bytes of the on-chip 256 Bytes of RAM and may be addressed by program instructions. Some of the SFR locations are bit addressable as well as byte addressable. The addresses in the SFR map which are not occupied are reserved for use in future versions of the SST89F54/58 and should not be used in programs for the current version. The result of reading or writing to these registers is indeterminate. User programs should not write 1's to these addresses, since they may be used in future products to invoke new features.

The SST89F54/58 not only provide the standard 8xC5x SFRs, but it also implement seven new registers, which include the SFDT, SFAL, SFAH, SFCM, SFCF, WDTC and WDTD registers. Most of the unique features of the SST89F54/58 microcontroller family, such as the SuperFlash EEPROM memory are controlled by bits in these additional SFRs.

The SFRs for the SST89F54/58 are organized in the memory map shown below. Individual descriptions of each SFR and its eight bits are presented in the following sections, including the contents of each register after reset. Note that the individual bits of each register may be accessed individually by designating the name of the register followed by a decimal point followed by the number of the bit position within the register.

|    |                                             |         |        |        |     |     |      |      | _  |  |

|----|---------------------------------------------|---------|--------|--------|-----|-----|------|------|----|--|

| F8 | SFDT                                        | SFAL    | SFAH   | SFCM   |     |     |      |      | FF |  |

| F0 | B*                                          |         |        |        |     |     |      | SFCF | F7 |  |

| E8 |                                             |         |        |        |     |     |      |      | EF |  |

| E0 | ACC*                                        |         |        |        |     |     |      |      | E7 |  |

| D8 |                                             |         |        |        |     |     |      |      | DF |  |

| D0 | PSW*                                        |         |        |        |     |     |      |      | D7 |  |

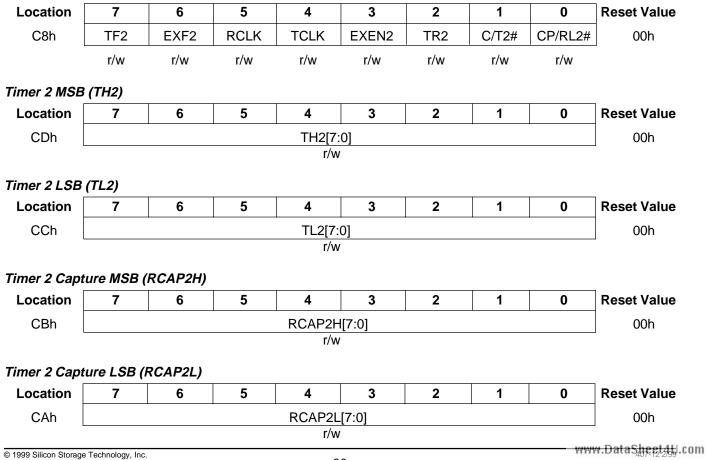

| C8 | T2CON*                                      |         | RCAP2L | RCAP2H | TL2 | TH2 |      |      | CF |  |

| C0 | WDTC                                        |         |        |        |     |     |      |      | C7 |  |

| B8 | IP*                                         |         |        | BF     |     |     |      |      |    |  |

| B0 | P3*                                         |         |        | B7     |     |     |      |      |    |  |

| A8 | IE*                                         |         |        |        |     |     |      |      | AF |  |

| A0 | P2*                                         |         |        |        |     |     |      |      | A7 |  |

| 98 | SCON*                                       | SBUF    |        |        |     |     |      |      | 9F |  |

| 90 | P1*                                         |         |        |        |     |     |      |      | 97 |  |

| 88 | TCON*                                       | TMOD    | TL0    | TL1    | TH0 | TH1 |      |      | 8F |  |

| 80 | P0*                                         | SP      | DPL    | DPH    |     |     | WDTD | PCON | 87 |  |

|    | FlashFlex51 SFR Memory Map                  |         |        |        |     |     |      |      |    |  |

|    | * = BIT AI                                  | DDRESSA | ABLE   |        |     |     |      |      |    |  |

|    | All addresses are hexadecimal 407 ILL F43.4 |         |        |        |     |     |      |      |    |  |

8 BYTES

For the following SFR descriptions, "r/w" under the corresponding bit means read or write, while "r" means read only, "r/c" means read or clear, "r/s" means read or set.

### Accumulator (ACC)

The Accumulator register serves as the accumulator for arithmetic operations. The accumulator is also used in some instructions as an index register. When referring to the accumulator as a location in the SFR, the mnemonic ACC is used, however accumulator-specific instructions refer to the accumulator as A. The following table provides a bit description of the Accumulator register.

### Accumulator (ACC)

| Location | 7     | 6     | 5     | 4     | 3     | 2     | 1     | 0     | Reset Value |

|----------|-------|-------|-------|-------|-------|-------|-------|-------|-------------|

| E0h      | ACC.7 | ACC.6 | ACC.5 | ACC.4 | ACC.3 | ACC.2 | ACC.1 | ACC.0 | 00h         |

|          | r/w   |             |

### B Register (B)

The B register serves as a second accumulator for certain arithmetic operations. Specifically, the B register functions as a divisor in the DIV AB instruction and as a multiplicand in the MUL AB instruction. B register-specific instructions refer to the B register as B. The B register is also used in some instructions as a general-purpose scratchpad register. The following table provides a bit description of the B register.

### B Register (B)

| Location | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0   | Reset Value |

|----------|-----|-----|-----|-----|-----|-----|-----|-----|-------------|

| F0h      | B.7 | B.6 | B.5 | B.4 | B.3 | B.2 | B.1 | B.0 | 00h         |

| et4U.com | r/w |             |

### Program Status Word (PSW)

The Program Status Word register serves as a status flag. The following table provides a bit description of the PSW register.

### Program Status Word (PSW)

| Location | 7   | 6   | 5   | 4   | 3   | 2   | 1   | 0      | Reset Value |

|----------|-----|-----|-----|-----|-----|-----|-----|--------|-------------|

| D0h      | CY  | AC  | F0  | RS1 | RS0 | OV  | F1  | PARITY | 00h         |

|          | r/w    |             |

The PSW contains the common status flags such as the CY, AC, OV and PARITY flags.

**Carry Flag** bit (CY) is set to 1 if the last arithmetic operation resulted in a carry into (during addition) or a borrow (during subtraction) from the high order byte. All other arithmetic operations clear the CY flag to 0

**Auxiliary Carry** Flag bit (AC) is set to 1 if the last arithmetic operation resulted in a carry into (during addition), or a borrow (during subtraction) from the high order nibble. All other arithmetic operations clear the AC flag to 0.

**Overflow Flag** bit (OV) is set to 1 if the last arithmetic operation resulted in a carry (during addition), borrow (during subtraction), or overflow (during multiply or divide). All other arithmetic operations clear the OV flag to 0.

**Parity Flag** bit (PARITY) is set to 1 if the modulo-2 sum of the eight bits of the ACC register is 1 (odd-parity). If the modulo-2 sum of the eight bits of the ACC register is 0 (even-parity) then the PARITY flag is cleared to 0.

In addition to the usual status flags, the SST89F54/58 implement four control flags, which include the F0, F1, RS0 and RS1 flags and are not associated with any specific MCU state or function.