# ST2226B

: A.002 Version

Issue Date: 2005/02/23

File Name : SP-ST2226B-A.002.doc

Total Pages: 20

# PWM-Controlled Constant Current Driver for LED **Displays**

ST2226B

### **PWM-Controlled Constant Current Driver**

# for LED Displays

# **General Description**

The ST2226B is a LED driver incorporating shift registers, data latches, 16-channel constant current circuitry with current value set by an external resistor, 1024 gray level PWM (Pulse Width Modulation) functional unit and time division capability. Each channel can provide a maximum current of 60 mA. Time division operation allows driving up to 1 or 2 LEDs with a single output channel (mode-1 and mode-2 respectively).

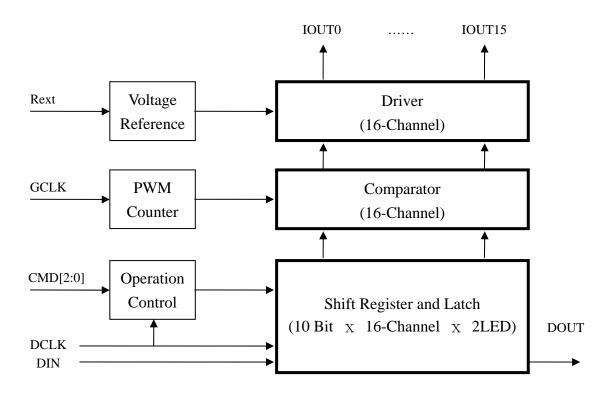

# **Block Diagram.**

Figure 1. Functional block diagram

#### **Features**

- Constant current outputs with current value settings by an external resistor

- Maximum output current: 60 mA

- Time division output allows the driving of 1 or 2 LEDs with a single output

- Maximum / minimum output voltage: 17V / 1.25V

- 10 bits luminance data with PWM current outputs

- Serial shift-in architecture for luminance data in time division Mode 1 and Mode 2

# **Absolute Maximum Ratings**

| Supply Voltage (AV <sub>DD</sub> , DV <sub>DD</sub> ) | -0.3 to 6                     | V                      |

|-------------------------------------------------------|-------------------------------|------------------------|

| Input Voltage Range (V <sub>IN</sub> )                | -0.3 to DV <sub>DD</sub> +0.3 | V                      |

| Driver Output Voltage Range (V <sub>OUT</sub> )       | -0.3 to 17                    | V                      |

| Driver Output Current (I <sub>OUT</sub> )             | 0 to 60                       | mA                     |

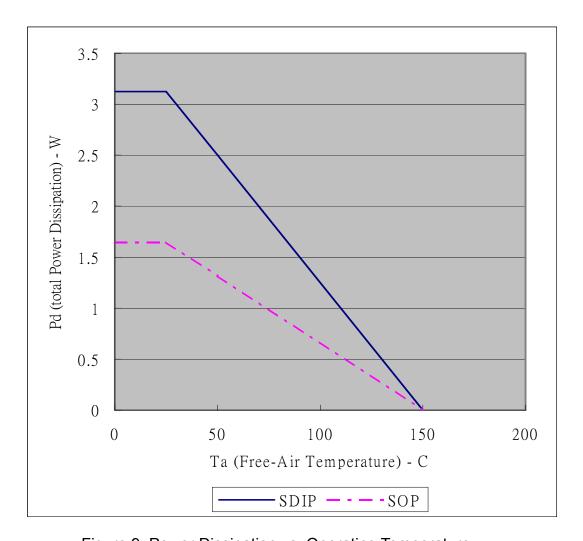

| Power Dissipation (T <sub>a</sub> = 50 °C or less)    | 2.50, SDIP28                  | W                      |

|                                                       | 1.32, SOP28                   |                        |

| Thermal Resistance (Θ <sub>ia</sub> )                 | 40.0, SDIP28                  | °C / W                 |

|                                                       | 75.9, SOP28                   |                        |

| Operating temperature range (T <sub>op</sub> )        | -40 to 85                     | $^{\circ}\!\mathbb{C}$ |

| Storage temperature range (T <sub>stg</sub> )         | -55 to 150                    | $^{\circ}\!\mathbb{C}$ |

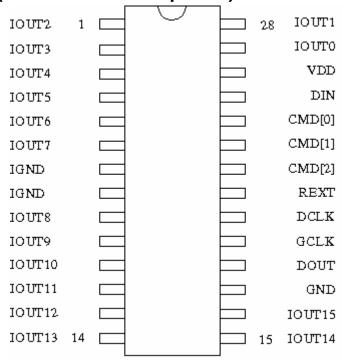

# Pin Connection (SDIP28 / SOP28 Top View)

# Pin Assignment (SDIP28 / SOP28)

| Pin No. | NAME   | Pin No. | NAME   |

|---------|--------|---------|--------|

| 1       | IOUT2  | 15      | IOUT14 |

| 2       | IOUT3  | 16      | IOUT15 |

| 3       | IOUT4  | 17      | GND    |

| 4       | IOUT5  | 18      | DOUT   |

| 5       | IOUT6  | 19      | GCLK   |

| 6       | IOUT7  | 20      | DCLK   |

| 7       | IGND   | 21      | REXT   |

| 8       | IGND   | 22      | CMD[2] |

| 9       | IOUT8  | 23      | CMD[1] |

| 10      | IOUT9  | 24      | CMD[0] |

| 11      | IOUT10 | 25      | DIN    |

| 12      | IOUT11 | 26      | VDD    |

| 13      | IOUT12 | 27      | IOUT0  |

| 14      | IOUT13 | 28      | IOUT1  |

# **Pin Description**

| NAME     | PIN NO.                                                                        | I/O | DESCRIPTION                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

|----------|--------------------------------------------------------------------------------|-----|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| CMD[2:0] | SDIP/SOP:<br>22, 23, 24                                                        | ı   | Encoded commands for data transfer, time division operation and PWM display:  CMD[2:0] Command  [000]: Mode-1 time division operation / No operation for display  [001]: Mode-2 time division operation / No operation for display  [010]: Data transfer enable (Shift-In)  [011]: Data latch strobe (Capture)  [100]: First LED emitting  [101]: Second LED emitting  [110]: LED emitting disable / IOUT disable (Stop)  [111]: Test mode  CMD commands are latched at the rising edges of DCLK.  There is one DCLK latency between Shift-in command latched and data shift-in. |

| DIN      | SDIP/SOP:<br>25                                                                | I   | Serial input for luminance data (time division mode-1/2)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| DOUT     | SDIP/SOP:<br>18                                                                | 0   | Serial output for luminance data (time division mode-1/2).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| DCLK     | SDIP/SOP:<br>20                                                                | I   | Synchronous clock input for command and serial data transfer. The input data of DIN is synchronous to rising edges of DCLK, and transferred to DOUT on falling edges of DCLK.                                                                                                                                                                                                                                                                                                                                                                                                    |

| GCLK     | SDIP/SOP:<br>19                                                                | I   | Clock input for PWM operation.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| IOUT0-15 | SDIP/SOP:<br>27, 28, 1, 2<br>3, 4, 5, 6, 9,<br>10, 11, 12<br>13, 14, 15,<br>16 | 0   | LED driver outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| REXT     | SDIP/SOP:<br>21                                                                | 0   | Driver current setting. LED current is set to a current value by connecting an external resistor between REXT and GND.                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| VDD      | SDIP/SOP:<br>26                                                                | -   | Power supply                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| GND      | SDIP/SOP:<br>17                                                                | -   | Analog and digital ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| IGND     | SDIP/SOP:<br>7, 8                                                              | -   | Two ground-pin for driver outputs.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

# **Recommended Operating Conditions**

### **DC Characteristics**

| PARAMETER                                                             | MIN          | NOM | MAX            | UNIT                   |

|-----------------------------------------------------------------------|--------------|-----|----------------|------------------------|

| Supply voltage, DV <sub>DD</sub> , AV <sub>DD</sub>                   | 4.75         | 5   | 5.25           | V                      |

| Driver output voltage when driver on, V <sub>OUT</sub>                | 1.25         | -   | 5              | V                      |

| Driver output voltage when driver off <sup>1</sup> , V <sub>OUT</sub> | 0            | -   | 17             | V                      |

| Driver output current, I <sub>OUT</sub>                               | 5            | -   | 60             | mA                     |

| High-level input voltage, V <sub>IH</sub>                             | $0.8DV_{DD}$ | ľ   | $DV_DD$        | V                      |

| Low-level input voltage, V <sub>IL</sub>                              | 0            | ľ   | $0.2  DV_{DD}$ | V                      |

| High-level output current, I <sub>OH</sub>                            | -            | ľ   | -1             | mA                     |

| Low-level output current, I <sub>OL</sub>                             | -            | ľ   | 1              | mA                     |

| Operating free-air temperature <sup>2</sup> , T <sub>op</sub>         | -20          | -   | 80             | $^{\circ}\!\mathbb{C}$ |

### **AC Characteristics**

| PARAMETER                                              | TEST              | MIN | NOM | MAX | UNIT |

|--------------------------------------------------------|-------------------|-----|-----|-----|------|

|                                                        | CONDITIONS        |     |     |     |      |

| DCLK clock frequency, f <sub>DCLK</sub>                |                   | -   | -   | 15  | MHz  |

| DCLK pulse duration, t <sub>wh</sub> / t <sub>wl</sub> | High or low level | 20  | -   | -   | ns   |

| DCLK rise/fall time t <sub>r</sub> / t <sub>f</sub>    |                   | 1   | -   | 40  | ns   |

| GCLK clock frequency, f <sub>GCLK</sub>                |                   |     | -   | 20  | MHz  |

| GCLK pulse duration, t <sub>wh</sub> / t <sub>wl</sub> | High or low level | 15  | -   | -   | ns   |

| GCLK rise/fall time t <sub>r</sub> /t <sub>f</sub>     |                   | -   | -   | 20  | ns   |

|                                                        | CMD to DCLK       | 25  |     |     | ns   |

| Setup time, t <sub>su</sub>                            | DIN to DCLK       | 25  | -   | -   |      |

|                                                        | DCLK to CMD       | 25  |     |     |      |

|                                                        | CMD to DCLK       | 25  |     |     | ns   |

| Hold time, t <sub>h</sub> / t <sub>wh</sub>            | DIN to DCLK       | 25  | -   | -   |      |

|                                                        | DCLK to CMD       | 25  |     |     |      |

<sup>1.</sup> The driver output voltage including any overshoot stress has to be compliant with the maximum voltage (17V).

<sup>2.</sup> Recommended junction temperature range is from -20 to 150 °C.

# **Electrical Characteristics**

| PARAMETER                               | TEST                       | MIN         | NOM  | MAX  | UNIT |

|-----------------------------------------|----------------------------|-------------|------|------|------|

|                                         | CONDITIONS                 |             |      |      |      |

| High-level digital output voltage,      |                            | $DV_{DD}$ - | -    | -    | V    |

| V <sub>OH</sub>                         |                            | 0.5         |      |      |      |

| Low-level digital output voltage,       |                            | -           |      | 0.5  | V    |

| $V_{OL}$                                |                            |             |      |      |      |

| Input current, I <sub>I</sub>           |                            | ı           | ı    | ±1   | μΑ   |

| Supply current (Digital)                | DCLK = 10MHz,              |             | 0.5  |      | mA   |

|                                         | GCLK = 10MHz               |             |      |      |      |

| Supply current (Analog)                 | REXT = 2K                  |             | 14   |      | mA   |

| Voltage reference, V <sub>BG</sub>      | Rext = $2K\Omega$          | 1.24        | 1.26 | 1.28 | V    |

| Driver output current, I <sub>OUT</sub> | Rext = $2K\Omega$ ,        |             | 32.2 |      | mA   |

|                                         | $V_{OUT} = 2.0V$           |             |      |      |      |

| Driver output leakage current, IoL      |                            | -           | -    | 1    | μA   |

| Driver current skew between             | V <sub>OUT</sub> = 2V, I = | -           | ±3   | ±6   | %    |

| channels, I <sub>OL1</sub>              | 40mA                       |             |      |      |      |

| Driver current skew between             | V <sub>OUT</sub> = 2V, I = | -           | ±6   | ±12  | %    |

| chips, I <sub>OL2</sub>                 | 40mA                       |             |      |      |      |

# Switching Characteristics, $C_L = 15pF$ , IOUT = 20mA

| PARAMETER                         | TEST CONDITIONS | MIN | NOM | MAX | UNIT |

|-----------------------------------|-----------------|-----|-----|-----|------|

| Rise time, t <sub>r</sub>         | DOUT            |     | 10  | 20  | ns   |

|                                   | IOUT            | -   | 25  | 40  |      |

| Fall time, t <sub>f</sub>         | DOUT            | -   | 10  | 20  | ns   |

|                                   | IOUT            | -   | 25  | 40  |      |

| Propagation delay, t <sub>d</sub> | GCLK to IOUT    | -   | 5   | 10  | ns   |

# **Typical Control Method**

## 1) Command Sequence

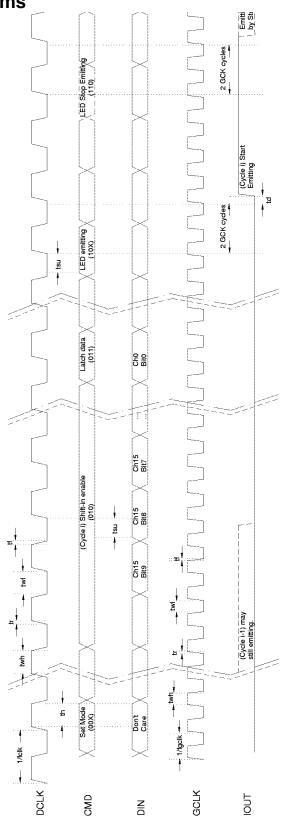

To manipulate ST2226B, we should properly control the CMD, DIN, DCLK, and GCLK as following steps:

- 1. Issue command "Shift-in", and then enter luminance data DIN. Note that ST2226B starts to shift-in data at the DCLK rising edge next to the edge which latched Shift-in command.

- 2. After data are completely entered, send command "Capture" to save data in registers.

- 3. Send command "*Disable*". This step is needed before the "Emitting" command to keep the chip synchronized.

- 4. Issue command "Emitting" or "Disable". Note that:

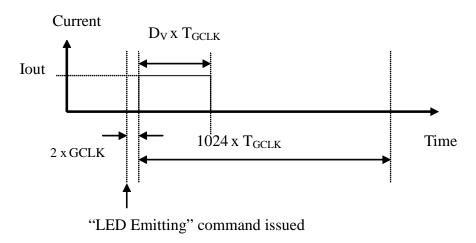

- A. ST2226B generates its output in one-shot fashion, i.e. the output after (1024) x T<sub>GCLK</sub> is always zero.

- B. There are 2 GCLK latencies between the latched *LED Emitting/Disable* command and PWM start/stop. This is shown in Figure 2.

- 5. Repeat step 1~4. In the same frame, the luminance data doesn't have to change, just repeat step 3~4. Note that the second command "*Emitting*" will be omitted if (1024) x T<sub>GCLK</sub> PWM has not finished, unless the "*Disable*" command is sent in advance.

The process discussed above could be summarized in the following table and timing diagram. At the same time, DCLK and GCLK remain free running.

Frame Frame Frame N-1 Ν N+1 Emitting / Disable Emitting / Disable Emitting / Disable Disable Shift-In Shift-In Sapture Disable Shift-In Disable Sapture NOP NOP : : Shift-in Data Shift-in Data. Shift-in Data Shift-in Data Don't care. Jon't care.

Table 1. Example of Command Sequence

<sup>&</sup>lt;sup>3</sup> We used the NOPs (No operation) to wait for the next frame data (at 60Hz) ready.

#### 2) LED Emitting Time and Current

ST2226B adjusts the LED luminance using PWM (pulse width modulation) technique. The luminance data ( $D_V$ ) has a resolution of 10 bits (1024steps) and can be set independently for each LED. The relationship between lout, luminance data, and emitting time is shown in Figure 2.

Figure 2. PWM Current Output

#### 3) Phase Relationship of DCLK and GCLK

Matching ST2226B's GCLK and DCLK is an important step in the system design. If there is a certain length of delay between the rising edge of DCLK and of GCLK, the command "LED Emitting" & "LED Disable" will not be correctly recognized, which will then cause the display data loss. It is safe to keep both of GCLK and DCLK rising at the same time, so that the frequencies of DCLK and GCLK have an integer multiple relationship.

For the design which has a fixed, corresponding clock phase relationship between GCLK & DCLK, e.g. the display controller is built by FPGAs, this clock phase problem is unlikely to happen. However, if it dose happen, try to control the clock phase, e.g. invert GCLK, to solve this problem. On the contrary, for the design which can not control the clock phase, e.g. the display controller is built by microprocessors, the following sequential modification on "Emitting" & "Disable" commands is preferred to be employed in the design:

- 1. Gate GCLK.

- 2. Issue "Emitting" or "Disable" command.

- 3. Let go of GCLK.

**Timing Diagrams**

Figure 3. Timing Diagram

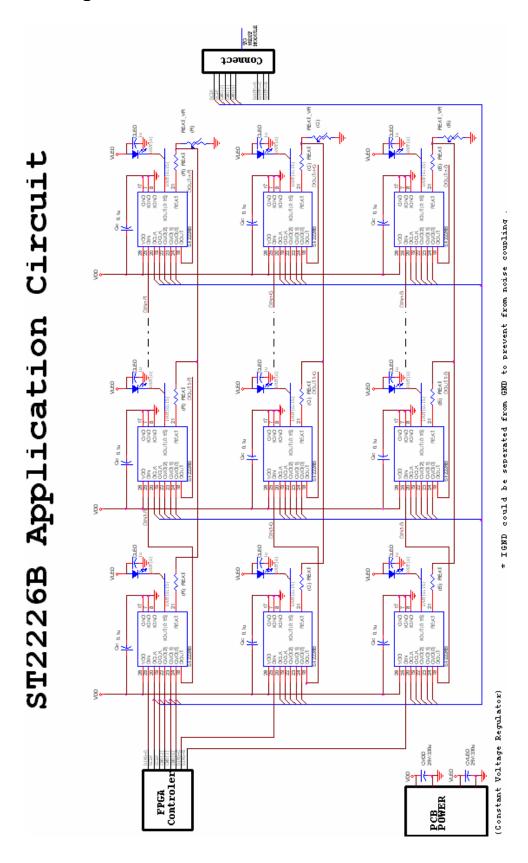

# **Application Diagrams**

# **Detailed Description**

#### 1) Time Division Operation

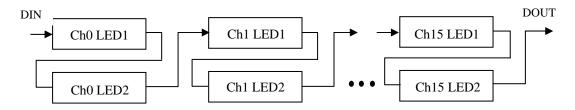

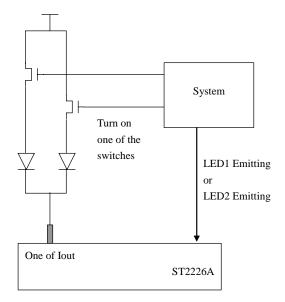

Since ST2226B can drive 1 LED or 2 LEDs, the user can choose either MODE1 luminance data or MODE2 luminance data. After the luminance data is given, a command should be issued so that the driver can operate in MODE1 or in MODE2. Figure 4 shows the route of data shift-in in MODE2. Later we will explain the data structure of MODE1 and MODE2 in more details.

Figure 4. Block Diagram for Primary Bus.

Figure 5. shows how to switch between 2 LEDs. When "LED1 Emitting" command is sent, LED1 PWM output will start 2 GCLK later. At the same time, the switch of LED1 should be turned on. On the other hand, LED2 switch should be turned on when LED2 PWM output starts. Again, "Disable" command must be sent before "LED1/LED2 Emitting". By periodically switching the emitting commands and LED switches, we could drive 2 LEDs per channel.

Figure 5. System Configuration for MODE 2 Operation

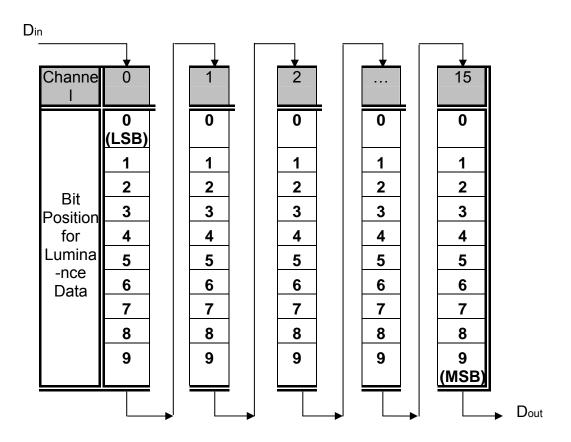

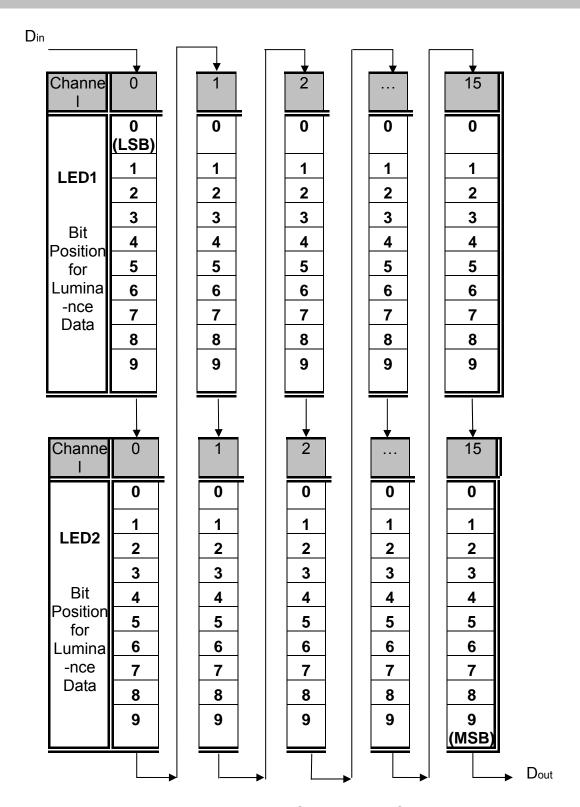

#### 2) Serial Shift-In Luminance Data

In the MODE1 operation, the data for shift registers and latches is set as  $\{16(\text{channel}) \times 10 \text{ bit (luminance)} \times 1(\text{led})\}$  whereas in MODE2 operation, the data is set as  $\{16(\text{channel}) \times 10 \text{ bit (luminance)} \times 2(\text{led})\}$  configuration. The driver IC can remember both 2 sets of luminance data.

The serial shift architecture assumes a FIFO (first-in firs-out) discipline, hence in the MODE1 operation, the most significant bit (MSB, Bit 9, Channel 15) luminance data is the first data shifted in, whereas the least significant bit (LSB, Bit 0, Channel 0) is the last data bit in a data set. The data structure for the MODE1 and MODE2 is shown in the Figure 6. and Figure 7. respectively.

Figure 6. Luminance Data Structure in MODE 1

Figure 7. Luminance Data Structure in MODE 2

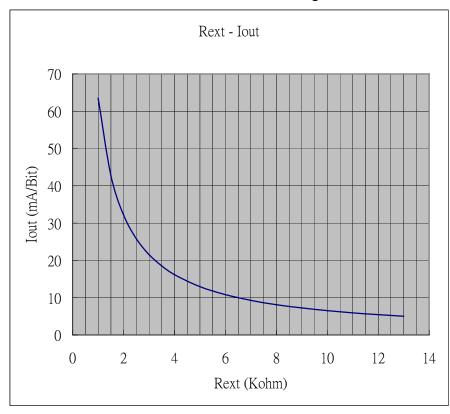

#### 3) Driver Current Output

The drive current is set by an external resistor, Rext, connected between the REXT pin and GND. Varying the resistor value can adjust the current scale ranging from 5mA to the maximum 60 mA. Note that the REXT pin voltage is designed to be independent of supply voltage, temperature, and process variation, and is approximately 1.26V.

The output current could be calculated roughly by the following equation: lout =  $(1.26 / \text{Rext}) \times 51$

The full-scale current IOUT vs. Rext is shown in Figure 8.

Figure 8. Driver current as a function of R<sub>EXT</sub>

#### 4) Power Rating

For the relationship between power dissipation and operating temperature, please refer to the following Figure 9.

Figure 9. Power Dissipation vs. Operating Temperature

#### 5) Advantages for application

To understand what the advantages over ON-OFF type drivers, we assume that in MODE 1 operation, the frame rate is 60Hz, DCLK & GCLK both run at 10MHz. We can shift in (1/60Hz)/(1/10MHz)=167K bits per frame. One channel takes 10 bits, thus 167K/10=16.7K channels (single color pixels). For two dimension display, we take the square root of 16.7K pixels, which equals 129. The resolution, in this case is 129\*129. We can round the data a little bit, and we can construct a 128\*128 image by connecting 1024 driver ICs. (1,024 EA drivers\*16 channels = 16,384 bit).

Within a frame, there are 1024\*16\*10=163K DCLK & GCLK cycles, and we know that the PWM takes 1024 GCLK cycles and is one-shot. So we can issue up to 163K/1024=160 PWM cycles within a frame. This can be used as an 160-level total brightness control in addition to the 1024-level pixel-dependent luminance control. These 160- "LED1 Emitting" shall be issued periodically within a frame. Each time when issuing the "LED1 Emitting" command, the shift-in process will be pended for a few cycles; however, we can resume feeding the data right after the "LED1 Emitting" command is issued.

To make the total brightness at full scale, all 160 "LED1 Emitting" commands should be issued. To make the total brightness half of the full scale, we can issue 80-"LED1 Emitting" commands in companion with 80-"LED Disable" commands, so that all the 128\*128 LEDs are half of their brightness.

A comparison table for PWM LED driver vs. ON-OFF type is provided for reference.

Table 2. Comparison between PWM and ON-OFF Free Running

|                          | PWM       | ON-OFF    |

|--------------------------|-----------|-----------|

| Frame rate               | 60        | 60        |

| No. shift-in pixels      | 128 x 128 | 128 x 128 |

| Grayscale for each pixel | 1024      | 1024      |

| Grayscale for overall    | 160       | 1         |

| panel                    |           |           |

| Clocks needed per frame  | 167k      | 16.8Meg   |

| Clock rate               | 10 MHz    | 1.0 GHz⁴  |

\_

<sup>&</sup>lt;sup>4</sup> Surely out of spec. Can't realize in this configuration. System designs for ON-OFF type drivers thus need to reduce frame rate or the no. shift-in pixels or grayscale level for each pixel.

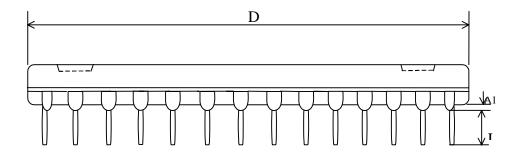

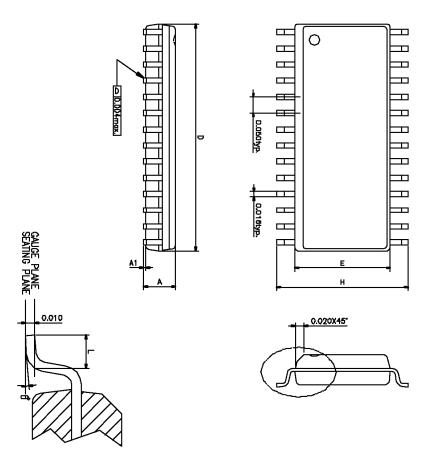

# **Package Outline Dimension**

# SDIP28

| SYMBOL | INCH(BASE)  | MM(REF)      |

|--------|-------------|--------------|

| Α      | 0.130±0.005 | 3.302±0.127  |

| A1     | 0.01(MIN)   | 0.254(MIN)   |

| В      | 0.018±0.005 | 0.457±0.127  |

| B1     | 0.060±0.004 | 1.524±0.102  |

| С      | 0.010±0.004 | 0.254±0.102  |

| D      | 1.388±0.002 | 35.255±0.051 |

| E      | 0.310±0.010 | 7.874±0.254  |

| E1     | 0.288±0.004 | 7.315±0.102  |

| е      | 0.100(TYP)  | 2.540(TYP)   |

| eB     | 0.350±0.020 | 8.890±0.508  |

| L      | 0.130±0.010 | 3.302±0.254  |

| S      | 0.044±0.005 | 1.118±0.127  |

| Q1     | 0.060±0.005 | 1.524±0.127  |

| θ      | 0°~10°      | 0°~10°       |

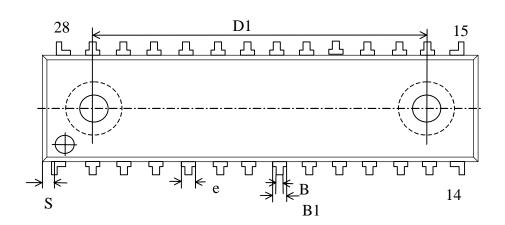

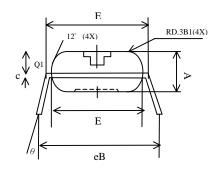

# SOP28

PER SIDE.

3.DIMENSIONS "E" DGES NOT INCLUDE INTER-LEAD FLASH,

OR PROTRUSIONS, INTER-LEAD FLASH AND PROTRUSIONS

SHALL NOT EXCEED .25mm (.010in) PER SIDE

| NOTES: 1.JEDEC OUTLINE : MS-013 AE 2.DIMENSIONS "b" DOES NOT INCLUDE MOLD FL |

|------------------------------------------------------------------------------|

| Ÿ                                                                            |

|                                                                              |

|                                                                              |

|             | ď  | L     | Н     | Ε     | D     | A1    | Α     | MBOLS |

|-------------|----|-------|-------|-------|-------|-------|-------|-------|

|             | 0  | 0.016 | 0.394 | 0.291 | 0.697 | 0.004 | 0.093 | MIN.  |

| UNIT : INCH | 00 | 0.050 | 0.419 | 0.299 | 0.713 | 0.012 | 0.104 | MAX.  |

|             |    |       |       |       |       |       |       |       |

SY

Version: A.002 ST2226B Page: 18

The products listed herein are designed for ordinary electronic applications, such as electrical appliances, audio-visual equipment, communications devices and so on. Hence, it is advisable that the devices should not be used in medical instruments, surgical implants, aerospace machinery, nuclear power control systems, disaster/crime-prevention equipment and the like. Misusing those products may directly or indirectly endanger human life, or cause injury and property loss.

Silicon Touch Technology, Inc. will not take any responsibilities regarding the misusage of the products mentioned above. Anyone who purchases any products described herein with the above-mentioned intention or with such misused applications should accept full responsibility and indemnify. Silicon Touch Technology, Inc. and its distributors and all their officers and employees shall defend jointly and severally against any and all claims and litigation and all damages, cost and expenses associated with such intention and manipulation.