### Dual electronic fuse (eFuse) for 5 V and 12 V rails

QFN10 (2 x 3 mm)

#### **Maturity status link**

STEF512PUR

#### **Features**

- 5 V and 12 V channels into one chip

- Output over voltage clamp

- Fixed current limit: 3 A on 5 V, 4 A on 12 V

- · Latched-off thermal protection

- Input undervoltage lockout

- Adjustable output voltage slew rate for each channel

- Integrated 40 mΩ Power FETs

- SAS disable pin

- Current monitor output

- QFN10-2x3 package

#### **Applications**

- HD and SSD drives

- Set-top boxes

- DVD and Blu-ray disc drivers

#### **Description**

The STEF512PUR is an integrated dual electronic eFuse, designed to protect circuitry on the output from overcurrent and overvoltage events, in those applications requiring hot swap operation and in-rush current control.

The device embeds two independent electronic fuses, one for the 5 V rails and one for the 12 V rails. Thanks to the very low ON-resistance of the integrated power FETs, the voltage drop from the main supply to the load is very low during normal operation.

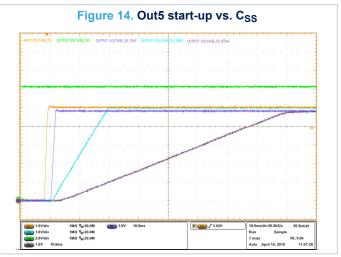

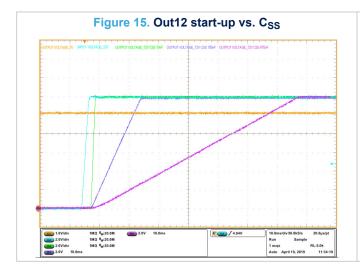

The startup time can be adjusted by the user for each eFuse, via two small soft-start capacitors, connected to the relevant pins.

In this way the inrush current at startup can be kept under control.

The maximum load current is precisely limited, by utilizing a sense FET topology, to factory-defined values (3 A for 5 V output and 4 A for 12 V output).

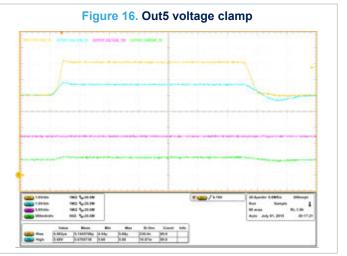

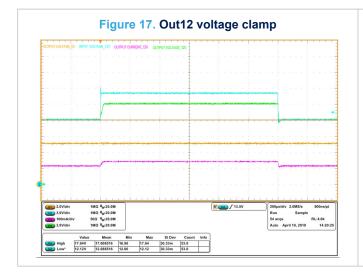

The device also provides precise overvoltage clamp for each channel, preventing the load being damaged from power supply failures, and undervoltage lockout (UVLO), assuring that the input voltage is above the minimum operating threshold, before the power device is turned on.

When an overload condition occurs, the STEF512PUR limits the output current to the predefined safe value. If the anomalous overload condition persists, the device goes into thermal shutdown, the internal switch is opened and the load disconnected from the power supply.

In the QFN10 package two current monitor pins are available, providing continuous information on the load current for each channel.

## 1 Diagram

$V_{CC\_X}$  $\bigvee_{t=1}^{t} V_{OUT\_X}$ CHARGE PUMP  $\overline{\mathsf{EN}}$ ENABLE UVLO AND GATE DRIVER CURRENT Thermal dV /dt Voltage SS\_x 📥 MONITOR Protection control Control and LIMIT GND  $I_{MON}\_x$

Figure 1. Block diagram (one channel)

DS13182 - Rev 5 page 2/23

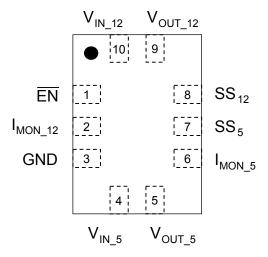

# Pin configuration

Figure 2. Pin connection (top view)

Table 1. Pin description

| Symbol              | Pin n° | Description                                                                                                                                                         |

|---------------------|--------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| V <sub>IN_12</sub>  | 10     | 12 V rail supply voltage                                                                                                                                            |

| V <sub>IN_5</sub>   | 4      | 5 V rail supply voltage                                                                                                                                             |

| V <sub>OUT_12</sub> | 9      | 12 V rail output voltage                                                                                                                                            |

| V <sub>OUT_5</sub>  | 5      | 5 V rail output voltage                                                                                                                                             |

| GND                 | 3      | Ground                                                                                                                                                              |

| EN                  | 1      | SAS disable input: set this pin logic-low to turn on the device, high to turn off the device. This pin is internally pulled down via 1 $\mbox{M}\Omega$ resistor.   |

| SS <sub>5</sub>     | 7      | Soft Start adjustment pin for the 5 V rail. A capacitor must be connected between this pin and GND to program the output voltage slew-rate. Do not leave floating.  |

| SS <sub>12</sub>    | 8      | Soft-start adjustment pin for the 12 V rail. A capacitor must be connected between this pin and GND to program the output voltage slew-rate. Do not leave floating. |

| I <sub>MON_5</sub>  | 6      | 5 V rail current monitor. Connect a resistor between this pin and GND.                                                                                              |

| I <sub>MON_12</sub> | 2      | 12 V rail current monitor. Connect a resistor between this pin and GND.                                                                                             |

DS13182 - Rev 5 page 3/23

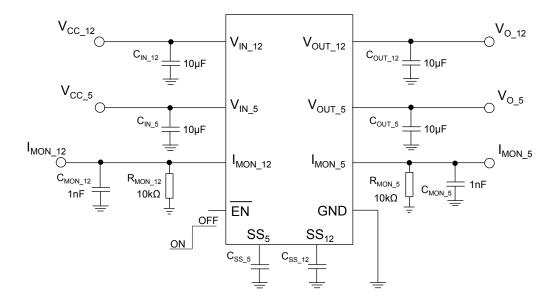

# 3 Typical application

Figure 3. Typical application diagram

DS13182 - Rev 5 page 4/23

## 4 Maximum ratings

Table 2. Absolute maximum ratings

| Symbol                                 | Parameter                         | Value       | Unit |

|----------------------------------------|-----------------------------------|-------------|------|

| V <sub>IN_5</sub> , V <sub>IN_12</sub> | Input supply voltage (max 100 ms) | - 0.3 to 25 | V    |

| V <sub>IN_5</sub> , V <sub>IN_12</sub> | Input supply voltage              | - 0.3 to 20 | V    |

| V <sub>OUT_5</sub>                     | Output voltage (1)                | 10          | V    |

| V <sub>OUT_12</sub>                    | Output voltage (1)                | 18          | V    |

| V <sub>EN</sub>                        | Enable pin voltage                | - 0.3 to 7  | V    |

| SS <sub>x</sub>                        | Soft-start pin voltage            | - 0.3 to 7  | V    |

| I <sub>MON_x</sub>                     | Monitor pin voltage               | - 0.3 to 7  | V    |

| ESD                                    | Charge device model               | ± 500       | V    |

| ESD                                    | Human body model                  | ± 2000      | V    |

| T <sub>J-OP</sub>                      | Operating junction temperature    | - 40 to 125 | °C   |

| T <sub>J-MAX</sub>                     | Maximum junction temperature      | 150         | °C   |

| T <sub>STG</sub>                       | Storage temperature               | - 55 to 150 | °C   |

<sup>1.</sup> Refer to Section 6.5.

Note:

Absolute maximum ratings are those values beyond which damage to the device may occur. Functional operation under these conditions is not implied. Exposure to absolute-maximum-rated conditions for extended periods may affect device reliability.

Table 3. Thermal data

| Symbol            | Parameter                           | Value | Unit |

|-------------------|-------------------------------------|-------|------|

| R <sub>thJA</sub> | Thermal resistance junction-ambient | 105   | °C/W |

| R <sub>thJC</sub> | Thermal resistance junction to case | 16    | °C/W |

DS13182 - Rev 5 page 5/23

## 5 Electrical characteristics

$T_{J} = 25~^{\circ}C,~V_{IN\_5} = 5~V,~V_{IN\_12} = 12~V,~\overline{EN} = 0~V;~C_{IN} = 10~\mu\text{F};~C_{OUT} = 10~\mu\text{F};~unless~otherwise~specified.}$

**Table 4. Electrical characteristics**

| Symbol                | Parameter                                                                      | Test conditions                                                   | Min. | Тур. | Max. | Unit  |

|-----------------------|--------------------------------------------------------------------------------|-------------------------------------------------------------------|------|------|------|-------|

| 5 V eFuse             |                                                                                |                                                                   |      |      |      |       |

| V <sub>Clamp_5</sub>  | Output clamping voltage                                                        | V <sub>IN_5</sub> = 8 V, I <sub>OUT</sub> = 5 mA                  | 5.5  | 5.7  | 5.9  | V     |

| V <sub>UVLO_5</sub>   | Undervoltage lockout                                                           | Turn-on, voltage rising                                           | 4.25 | 4.35 | 4.45 | V     |

| V <sub>Hyst_5</sub>   | UVLO hysteresis                                                                | Turn-off, voltage falling                                         |      | 1.78 |      | V     |

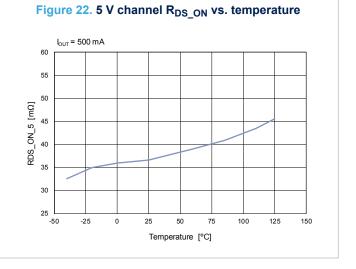

| В                     | 0                                                                              | T <sub>J</sub> = 25 °C                                            |      | 36   |      | 0     |

| R <sub>DSon_5</sub>   | On-resistance                                                                  | T <sub>J</sub> = 125 °C                                           |      |      | 50   | mΩ    |

| I <sub>L_5</sub>      | Off state leakage current                                                      | $V_{EN} = 5 \text{ V}, V_{OUT\_5} = GND$                          |      | 1    | 5    | μA    |

| I <sub>D5</sub>       | Maximum continuous current                                                     | T <sub>A</sub> = 25 °C                                            |      | 2.5  |      | Α     |

| I <sub>Short_5</sub>  | Short-circuit current limit                                                    |                                                                   | 0.6  | 1    | 1.4  | Α     |

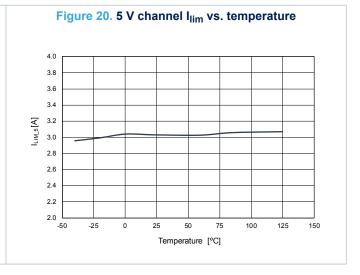

| I <sub>Lim_5</sub>    | Overload current limit                                                         |                                                                   | 2.5  | 3    | 3.3  | Α     |

| dV/dt_5               | Output voltage ramp time                                                       | From 10 % to 90 % of V <sub>OUT</sub> C <sub>dv/dt</sub> = 100 nF | 11   | 13   | 15   | ms    |

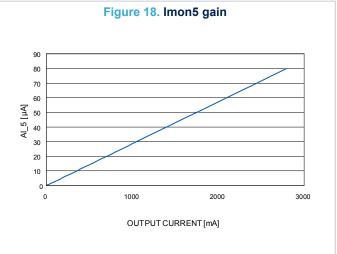

| A <sub>I_5</sub>      | Current monitor output current gain, I <sub>MON_5</sub> / I <sub>OUT_5</sub>   | I <sub>OUT_5</sub> > = 200 mA                                     | 27   | 30   | 33   | μA/A  |

| 12 V eFuse            | <u>'</u>                                                                       |                                                                   |      |      |      |       |

| V <sub>Clamp_12</sub> | Output clamping voltage                                                        | V <sub>IN_12</sub> = 17 V, I <sub>OUT</sub> = 5 mA                | 14.5 | 15   | 15.5 | V     |

| V <sub>UVLO_12</sub>  | Undervoltage lockout                                                           | Turn-on, voltage rising                                           | 9.4  | 9.7  | 10   | V     |

| V <sub>Hyst_12</sub>  | UVLO hysteresis (12 V rail)                                                    | Turn-off, voltage falling                                         |      | 2    |      | V     |

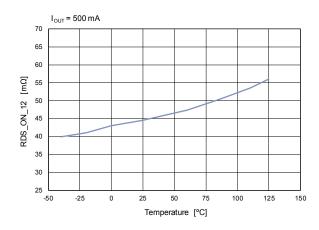

| В                     | On marietanes (40 V mail)                                                      | T <sub>J</sub> = 25 °C                                            |      | 40   |      | mΩ    |

| R <sub>DSon_12</sub>  | On-resistance (12 V rail)                                                      | T <sub>J</sub> = 125 °C                                           |      |      | 70   | 11122 |

| I <sub>L_12</sub>     | Off state leakage current                                                      | $V_{EN} = 5 \text{ V}, V_{OUT\_12} = GND$                         |      | 1    | 5    | μA    |

| I <sub>D12</sub>      | Continuous current (1)(2)                                                      | T <sub>A</sub> = 25 °C                                            |      | 3.5  |      | Α     |

| I <sub>Short_12</sub> | Short-circuit current limit                                                    |                                                                   |      | 1.8  |      | Α     |

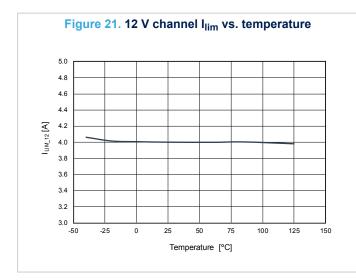

| I <sub>Lim_12</sub>   | Overload current limit                                                         |                                                                   | 3.6  | 4    | 4.5  | Α     |

| dV/dt_ <sub>12</sub>  | Output voltage ramp time                                                       | From 10 % to 90 % of $V_{OUT}$ , $C_{dv/dt} = 100 \text{ nF}$     | 10   | 12   | 14   | ms    |

| A <sub>I_12</sub>     | Current monitor output current gain, I <sub>MON_12</sub> / I <sub>OUT_12</sub> | I <sub>OUT_12</sub> ≥ 200 mA                                      | 27   | 30   | 33   | μA/A  |

| Common fe             | atures                                                                         |                                                                   |      |      |      |       |

| V <sub>IL</sub>       | Low level input voltage                                                        | Output enabled                                                    |      |      | 0.7  | V     |

| $V_{IH}$              | High level input voltage                                                       | Output disabled                                                   | 2.1  |      |      | V     |

| R <sub>P</sub>        | Pull-down resistor                                                             |                                                                   |      | 1000 |      | kΩ    |

| 1                     | Quiescent current (excluding                                                   | Device operating                                                  |      | 250  | 1000 | μA    |

| I <sub>q</sub>        | EN current)                                                                    | Off-state, = 5 V                                                  |      | 40   | 80   | μA    |

| IEN                   | Enable pin current                                                             | V <sub>EN</sub> = 5 V                                             |      | 5    | 10   | μA    |

DS13182 - Rev 5 page 6/23

| Symbol      | Parameter                | Test conditions | Min. | Тур. | Max. | Unit |

|-------------|--------------------------|-----------------|------|------|------|------|

| Thermalprot | ection                   |                 |      |      |      |      |

| TSD         | Shutdown temperature (1) |                 |      | 165  |      | °C   |

|             | Hysteresis               |                 |      | 20   |      | C    |

<sup>1.</sup> Guaranteedby design, but not tested in production.

Table 5. Recommended operating condition

| Symbol           | Parameter          | Test Conditions | Min. | Тур. | Max. | Unit |

|------------------|--------------------|-----------------|------|------|------|------|

| C <sub>IN</sub>  | Input capacitance  | Stability       | 1    | 47   |      | uF   |

| C <sub>OUT</sub> | Output capacitance | Stability       | 10   | 47   |      | μι   |

DS13182 - Rev 5 page 7/23

<sup>2.</sup> The maximum continuous current is the current level above which the control loop starts increasing the ON resistance of the pass element.

### 6 Device functional description

The STEF512PUR embeds a 5 V and a 12 V electronic fuses (eFuses). Each eFuse is an intelligent load switch, able limit the voltage or the current during fault events, such as input overvoltage or output overload respectively. For this purpose it contains 2 analogue control loops, one limiting the output voltage and one limiting the input current.

The current limiting loop is also used during the start-up phase of the eFuse to limit the inrush current into the output capacitor.

During normal operation the eFuse behaves as a low-resistance Power FET, therefore the output voltage follows the input one. In case of overvoltage or overcurrent event, the eFuse limits the  $V_{GS}$  of the internal FET, in order to clamp the output voltage or current respectively. During such events the die temperature increases due to the power dissipation and so, if the fault persists and the overtemperature threshold is overcome, the device goes into thermal shutdown, the internal FET is turned-off and the load disconnected from the power supply.

Once the eFuse is in thermal shutdown, it does not restart automatically. The eFuse can be restarted manually by toggling the  $\overline{\text{EN}}$  pin or performing a power-up cycle, (this will be effective as soon as the die temperature drops by at least the overtemperature hysteresis).

Each eFuse provides factory-trimmed undervoltage lockout feature and user-adjustable output voltage rise time.

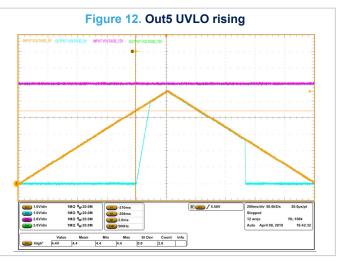

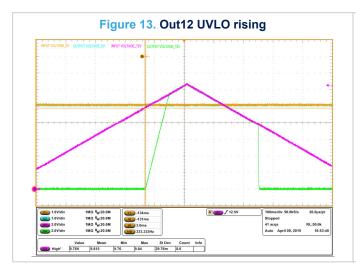

#### 6.1 Undervoltage lockout

Undervoltage lockout circuit prevents each eFuse to turn-on if the supply voltage is below the UVLO rising threshold. During operation, if the input voltage falls below  $(V_{UVLO_x} - V_{Hyst_x})$ , the output of the relevant channel is turned off

If the supply voltage comes back into the operative range, the relevant channel restarts with soft-start cycle.

#### 6.2 Startup sequence and voltage clamp

The typical start-up sequence of each eFuse is as follows:

- The power supply is connected to the V<sub>IN x</sub> pin and higher than the undervoltage lockout threshold

- The disable pin EN is asserted by the user to low logic level (or left floating), enabling the device

- Typically, 1.2 ms after the eFuse starts ramping up the output voltage

- Each channel will ramp up with a rate set by the relevant C<sub>SSx</sub>

- If the input voltage continues rising, above the overvoltage threshold (V<sub>Clamp\_x</sub>), as a consequence of a failure in the power supply, the eFuse limits the output voltage to V<sub>Clamp\_x</sub>. The eFuse keeps operating in this state until it hits its overtemperature threshold and shuts down

#### 6.3 Current limit function

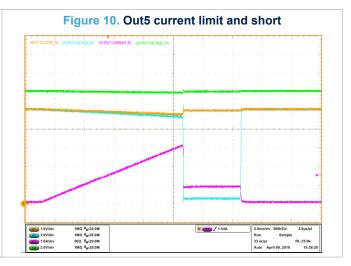

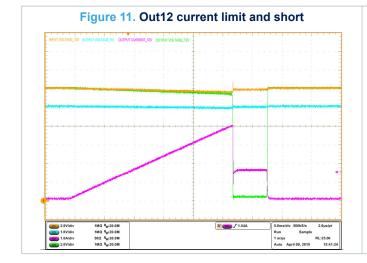

Each eFuse provides 2 kinds of current limit protection mechanisms:

- In case of overload, the device starts increasing the power MOS resistance. The overload current limit (I<sub>Lim x</sub>) is 3 A typ. for the 5 V fuse and 4 A (typ.) for the 12 V

- In the case of strong overload or short circuit, the short-circuit current limit is activated and the current is clamped to I<sub>Short x</sub>: 1 A typ. on 5 V channel and 1.8 A typ. on 12 V channel

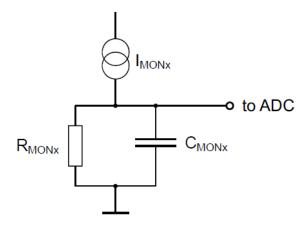

#### 6.4 eFuse current monitor

The eFuse is equipped with current monitoring capability that allows the host processor to read the current flowing through each channel. An  $I_{MON_x}$  (x = 5, 12) current proportional to the load current flowing through the eFuse is imposed on an external  $R_{MON_x}$ , converting the sensing current into voltage for further processing by the ADC. An external RC filter is used to provide a stable signal (see figure below).

The current monitoring amplifier gain  $(A_{l\_x} = I_{MON\_x} / I_{OUT\_x})$  is typically 30  $\mu$ A/A, as defined in the electrical characteristic Table 4. Electrical characteristics.

DS13182 - Rev 5 page 8/23

Figure 4. Current monitor simplified circuit

### 6.5 Application guidelines

Output capacitors are mandatory to guarantee device control loop stability. Input capacitors are recommended to reduce the transient effects of stray inductances which may be present on the input power paths. In fact, when the STEF512PUR interrupts the current flow, input inductance generates a positive voltage spike on the input, and output inductance generates a negative voltage spike on the output.

Input and output bypass capacitors must be placed as close as possible to the device.

When the device is powered by a power line made up of very long wires, the input inductance is higher than few  $\mu$ H, so the input capacitor should be increased in order to guarantee the proper operation of the device.

It is suggested to provide for additional protections and methods for addressing these transients, such as:

- Minimizing inductance of the input and output tracks

- TVS diodes on the input to absorb inductive spikes

- Schottky diode on the output to absorb negative spikes

- · Combination of ceramic and electrolytic capacitors on the input and output

The device is not designed for continuous (DC) operation in reverse biasing conditions ( $V_{OUT} > V_{IN} + 0.3 \text{ V}$  for more than 100 µs).

In fact the parasitic body diodes of the pass elements cannot withstand high current levels in DC biasing conditions that might lead to destruction or malfunction.

If this condition exists in the final application, we recommend placing a reverse current protection diode in series to the current path or selecting a device embedding reverse current protection MOSFET.

DS13182 - Rev 5 page 9/23

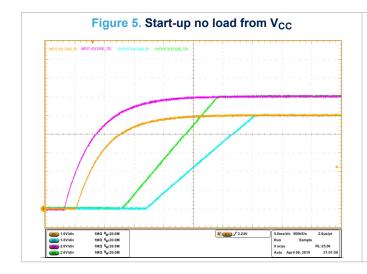

## 7 Typical characteristics

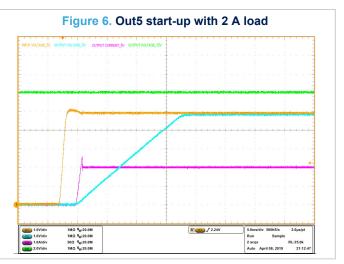

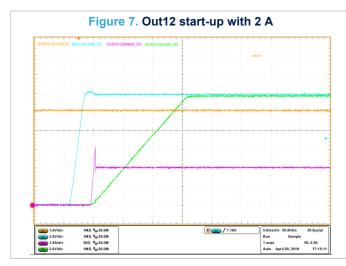

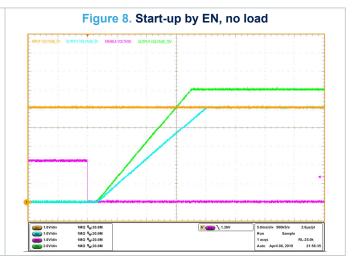

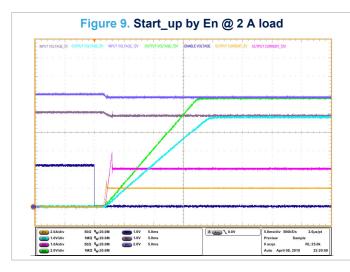

The following plots are referred to the typical application circuit and, unless otherwise noted, at  $T_A$  = 25 °C.

DS13182 - Rev 5 page 10/23

DS13182 - Rev 5 page 11/23

Figure 19. Imon12 Gain

140

120

100

200

1000 2000 3000 4000 5000

OUTPUT CURRENT [mA]

DS13182 - Rev 5 page 12/23

DS13182 - Rev 5 page 13/23

### 8 Package information

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK packages, depending on their level of environmental compliance. ECOPACK specifications, grade definitions and product status are available at: www.st.com. ECOPACK is an ST trademark.

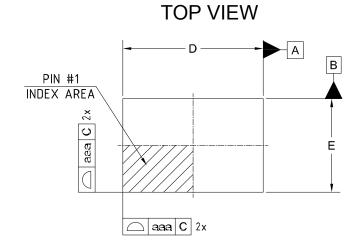

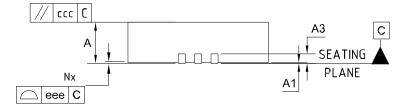

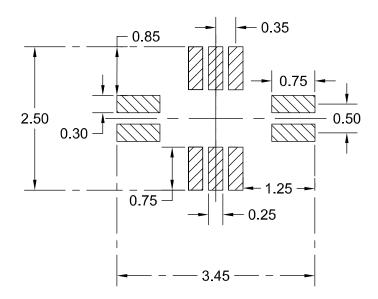

#### 8.1 QFN10 (2 x 3 mm) package information

Figure 24. QFN10 (2 x 3 mm) package outline

### SIDE VIEW

### **BOTTOM VIEW**

DS13182 - Rev 5 page 14/23

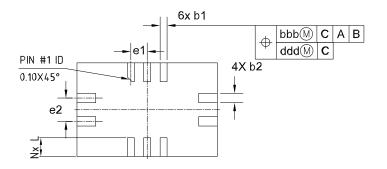

Table 6. QFN10 (2 x 3 mm) mechanical data

| Dim. | mm       |            |      |  |  |  |

|------|----------|------------|------|--|--|--|

| Dim. | Min.     | Тур.       | Max. |  |  |  |

| Α    | 0.70     | 0.75       | 0.80 |  |  |  |

| A1   | 0        | 0.02       | 0.05 |  |  |  |

| A3   |          | 0.203 ref. |      |  |  |  |

| b1   | 0.10     | 0.15       | 0.20 |  |  |  |

| b2   | 0.15     | 0.20       | 0.25 |  |  |  |

| D    | 3.00 BSC |            |      |  |  |  |

| Е    |          | 2.00 BSC   |      |  |  |  |

| e1   |          | 0.35 BSC   |      |  |  |  |

| e2   |          | 0.50 BSC   |      |  |  |  |

| L    | 0.30     | 0.40       | 0.50 |  |  |  |

| aaa  |          | 0.05       |      |  |  |  |

| bbb  | 0.10     |            |      |  |  |  |

| ccc  | 0.10     |            |      |  |  |  |

| ddd  |          | 0.05       |      |  |  |  |

| eee  |          | 0.08       |      |  |  |  |

Figure 25. QFN10 (2 x 3 mm) recommended footprint

DS13182 - Rev 5 page 15/23

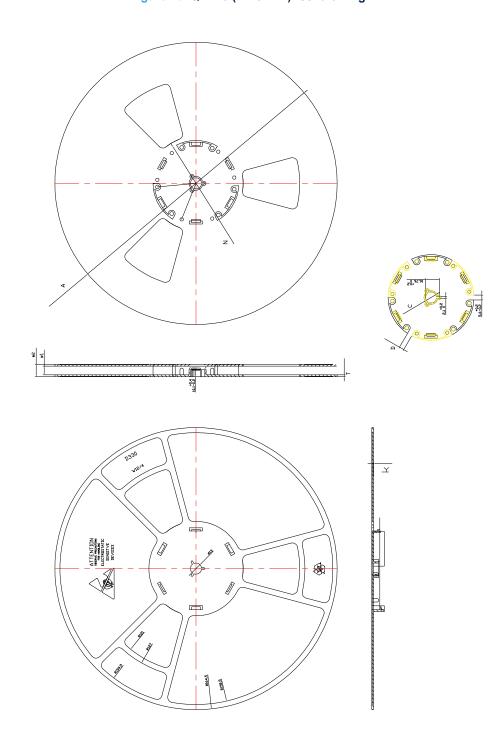

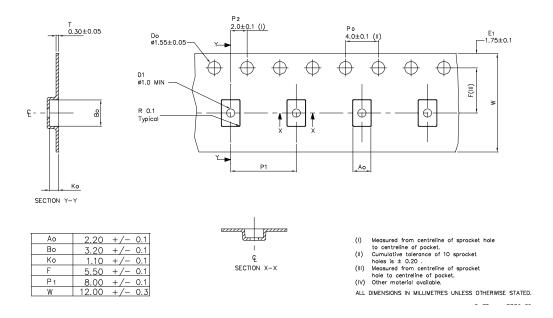

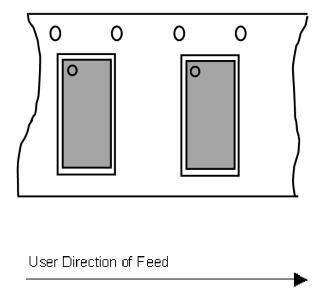

## 8.2 QFN10 (2 x 3 mm) packing information

Figure 26. QFN10 (2 x 3 mm) reel drawing

| TYPE | Α      | N            | С                  | D               | w1                 | w2                 | Т        | K                 |

|------|--------|--------------|--------------------|-----------------|--------------------|--------------------|----------|-------------------|

| 12MM | ø330-2 | +2<br>ø100-2 | +0,2<br>\$13,1-0,2 | +0,5<br>5,6-0,5 | 12,4 <sup>+2</sup> | 16,6 <sup>+2</sup> | 2,1±0,15 | +0,15<br>1.4 -0,1 |

DS13182 - Rev 5 page 16/23

Figure 27. QFN10 (2 x 3 mm) reel drawing

Figure 28. QFN10 (2 x 3 mm) tape oriented

DS13182 - Rev 5 page 17/23

# 9 Ordering information

Table 7. Order codes

| Order code | Package | Current limit configuration | Marking |

|------------|---------|-----------------------------|---------|

| STEF512PUR | QFN10   | 3 A on 5 V , 4 A on 12 V    | W51     |

DS13182 - Rev 5 page 18/23

### **Revision history**

Table 8. Document revision history

| Date        | Revision | Changes                                                                                       |

|-------------|----------|-----------------------------------------------------------------------------------------------|

| 07-Jan-2020 | 1        | Initial release.                                                                              |

| 13-Jan-2020 | 2        | Added $A_{l\_5}$ and $A_{l\_12}$ Min. and Max. values in Table 4. Electrical characteristics. |

| 21-Sep-2020 | 3        | Updated ILIM_5 Min. value in Table 4. Electrical characteristics.  Minor text changes.        |

| 04-Apr-2023 | 4        | Added Section 8.2 QFN10 (2 x 3 mm) packing information.                                       |

| 04-Apr-2024 | 5        | Updated footnote in Table 2. Added Section 6.5: Application guidelines.                       |

DS13182 - Rev 5 page 19/23

### **Contents**

| 1  | Diag                | gram                                 |    |  |  |  |  |  |

|----|---------------------|--------------------------------------|----|--|--|--|--|--|

| 2  |                     | configuration                        |    |  |  |  |  |  |

| 3  |                     | ical application                     |    |  |  |  |  |  |

| 4  | Max                 | kimum ratings                        | 5  |  |  |  |  |  |

| 5  | Elec                | Electrical characteristics           |    |  |  |  |  |  |

| 6  | Dev                 | Device functional description        |    |  |  |  |  |  |

|    | 6.1                 | Undervoltage lockout                 |    |  |  |  |  |  |

|    | 6.2                 | Startup sequence and voltage clamp   | 8  |  |  |  |  |  |

|    | 6.3                 | Current limit function               | 8  |  |  |  |  |  |

|    | 6.4                 | eFuse current monitor                | 8  |  |  |  |  |  |

|    | 6.5                 | Application guidelines               |    |  |  |  |  |  |

| 7  |                     | ical characteristics                 |    |  |  |  |  |  |

| 8  | Package information |                                      |    |  |  |  |  |  |

|    | 8.1                 | QFN10 (2 x 3 mm) package information |    |  |  |  |  |  |

|    | 8.2                 | QFN10 (2 x 3 mm) packing information |    |  |  |  |  |  |

| 9  | Ord                 | ering information                    | 18 |  |  |  |  |  |

| Re | vision              | history                              |    |  |  |  |  |  |

### **List of tables**

| Table 1. | Pin description                  | . 3 |

|----------|----------------------------------|-----|

| Table 2. | Absolute maximum ratings         | . 5 |

| Table 3. | Thermal data                     | . 5 |

| Table 4. | Electrical characteristics       | . 6 |

| Table 5. | Recommended operating condition  | . 7 |

| Table 6. | QFN10 (2 x 3 mm) mechanical data | 15  |

| Table 7. | Order codes                      | 18  |

| Table 8. | Document revision history        | 19  |

DS13182 - Rev 5 page 21/23

# **List of figures**

| Figure 1.  | Block diagram (one channel)                     | . 2 |

|------------|-------------------------------------------------|-----|

| Figure 2.  | Pin connection (top view)                       | 3   |

| Figure 3.  | Typical application diagram                     | 4   |

| Figure 4.  | Current monitor simplified circuit              | 9   |

| Figure 5.  | Start-up no load from V <sub>CC</sub>           | 10  |

| Figure 6.  | Out5 start-up with 2 A load                     | 10  |

| Figure 7.  | Out12 start-up with 2 A                         | 10  |

| Figure 8.  | Start-up by EN, no load                         | 10  |

| Figure 9.  | Start_up by En @ 2 A load                       | 10  |

| Figure 10. | Out5 current limit and short                    | 10  |

| Figure 11. | Out12 current limit and short                   | 11  |

| Figure 12. | Out5 UVLO rising                                | 11  |

| Figure 13. | Out12 UVLO rising                               | 11  |

| Figure 14. | Out5 start-up vs. C <sub>SS</sub>               | 11  |

| Figure 15. | Out12 start-up vs. C <sub>SS</sub>              | 11  |

| Figure 16. | Out5 voltage clamp                              | 11  |

| Figure 17. | Out12 voltage clamp                             | 12  |

| Figure 18. | Imon5 gain                                      | 12  |

| Figure 19. | Imon12 Gain                                     | 12  |

| Figure 20. | 5 V channel I <sub>lim</sub> vs. temperature    | 12  |

| Figure 21. | 12 V channel I <sub>lim</sub> vs. temperature   | 12  |

| Figure 22. | 5 V channel R <sub>DS_ON</sub> vs. temperature  | 12  |

| Figure 23. | 12 V channel R <sub>DS_ON</sub> vs. temperature | 13  |

| Figure 24. | QFN10 (2 x 3 mm) package outline                | 14  |

| Figure 25. | QFN10 (2 x 3 mm) recommended footprint.         | 15  |

| Figure 26. | QFN10 (2 x 3 mm) reel drawing                   | 16  |

| Figure 27. | QFN10 (2 x 3 mm) reel drawing                   | 17  |

| Figure 28. | QFN10 (2 x 3 mm) tape oriented                  | 17  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to www.st.com/trademarks. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2024 STMicroelectronics – All rights reserved

DS13182 - Rev 5 page 23/23