### Trench gate field-stop 1700 V, 50 A low loss M series IGBT die in D7 packing

#### **Features**

- Low V<sub>CE(sat)</sub> = 2 V (typ.) @ I<sub>C</sub> = 50 A

- 10 µs of short-circuit withstand time

- · Minimized tail current

- · Tight parameter distribution

- Positive V<sub>CE(sat)</sub> temperature coefficient

#### **Applications**

- Industrial motor control

- Industrial drives

#### **Description**

EGCD

This device is an IGBT developed using an advanced proprietary trench gate field-stop structure. The device is part of the M series IGBTs, which represent an optimal balance between inverter system performance and efficiency where the low-loss and the short-circuit functionality is essential. Furthermore, the positive  $V_{\text{CE(sat)}}$  temperature coefficient and the tight parameter distribution result in safer paralleling operation.

#### Product status link

STG50M170F3D7

| Product summary                |               |  |  |

|--------------------------------|---------------|--|--|

| Order code                     | STG50M170F3D7 |  |  |

| V <sub>CE</sub>                | 1700 V        |  |  |

| I <sub>CN</sub>                | 50 A          |  |  |

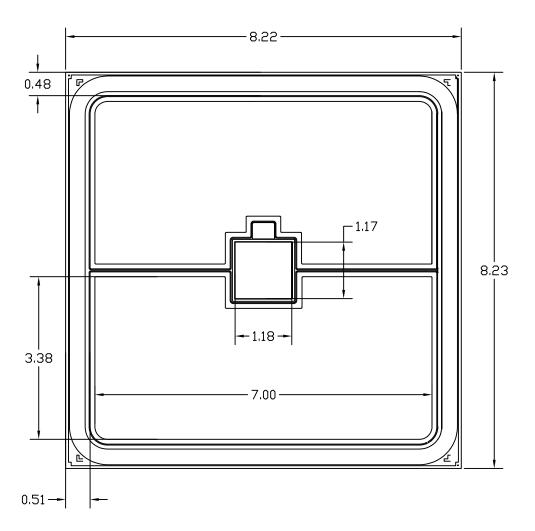

| <b>Die size</b> 8.22 x 8.23 mm |               |  |  |

| Packing                        | D7            |  |  |

## 1 Mechanical parameters

**Table 1. Mechanical parameters**

| Symbol                       | Symbol                                   |              | Unit             |

|------------------------------|------------------------------------------|--------------|------------------|

| Die size including scril     | Die size including scribe line           |              | mm               |

| Wafer size                   |                                          | 200          | mm               |

| Maximum possible dice p      | oer wafer                                | 384          | dice             |

| Die thickness                |                                          | 175          | μm               |

| Front side passivat          | Front side passivation                   |              | e                |

| Emitter pad size including g | Emitter pad size including gate pad (x2) |              | mm               |

| Gate pad size                | Gate pad size                            |              | mm               |

| Front side metallization     | composition                              | AlCu         |                  |

| Front side metalization      | thickness                                | 4.5          | μm               |

| Back side metallization      | composition                              | Al/Ti/NiV/Aç | 9                |

| back side metalization       | thickness                                | 0.65         | μm               |

| Die bond                     | Die bond                                 |              | e or soft solder |

| Recommended wire be          | Recommended wire bonding                 |              | μm               |

DS13689 - Rev 3 page 2/10

## 2 Electrical ratings

$T_J$  = 25 °C unless otherwise specified.

Table 2. Absolute maximum ratings

| Symbol                         | Parameter                                                                                                            | Value      | Unit |

|--------------------------------|----------------------------------------------------------------------------------------------------------------------|------------|------|

| V <sub>CES</sub>               | Collector-emitter voltage (V <sub>GE</sub> = 0 V)                                                                    | 1700       | V    |

| $V_{GE}$                       | Gate-emitter voltage                                                                                                 | ±20        | V    |

| I <sub>CN</sub> <sup>(1)</sup> | Continuous collector current at T = 100 °C                                                                           | 50         | Α    |

| I <sub>CP</sub> <sup>(2)</sup> | Pulsed collector current                                                                                             | 150        | Α    |

| t <sub>SC</sub> <sup>(3)</sup> | Short circuit withstand time ( $V_{CC}$ = 1000 V, $V_{GE}$ = ±15 V, $V_{CE}$ (peak) ≤ 1700 V, $T_{Jstart}$ = 125 °C) | 10         | μs   |

| TJ                             | Operating junction temperature range                                                                                 | -55 to 150 | °C   |

<sup>1.</sup> Nominal collector current for die packaged in ST discrete solution. Current level depends on the assembly thermal properties and is limited by maximum junction temperature.

DS13689 - Rev 3 page 3/10

<sup>2.</sup> Pulse width is limited by maximum junction temperature. Specified by design, not tested in production.

<sup>3.</sup> Evaluated by characterization, not tested in production.

### **Electrical characteristics**

Table 3. Static characteristics (tested on wafer unless otherwise specified)

| Symbol               | Parameter                            | Test conditions                                           | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|-----------------------------------------------------------|------|------|------|------|

| V <sub>(BR)CES</sub> | Collector-emitter breakdown voltage  | I <sub>C</sub> = 1 mA, V <sub>GE</sub> = 0 V              | 1700 |      |      | V    |

| V <sub>CE(sat)</sub> | Collector-emitter saturation voltage | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 15 A             |      |      | 1.9  | V    |

| V <sub>GE(th)</sub>  | Gate threshold voltage               | V <sub>CE</sub> = V <sub>GE</sub> , I <sub>C</sub> = 1 mA | 5    | 6    | 7    | V    |

| I <sub>CES</sub>     | Collector cut-off current            | V <sub>GE</sub> = 0 V, V <sub>CE</sub> = 1700 V           |      |      | 25   | μA   |

| I <sub>GES</sub>     | Gate-emitter leakage current         | V <sub>CE</sub> = 0 V, V <sub>GE</sub> = ±20 V            |      |      | ±250 | nA   |

Table 4. Electrical characteristics (evaluated by characterization, not tested in production)

| Symbol               | Parameter                            | Test conditions                                                        | Min. | Тур. | Max. | Unit |

|----------------------|--------------------------------------|------------------------------------------------------------------------|------|------|------|------|

| V <sub>CE(sat)</sub> | Collector-emitter saturation voltage | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 50 A                          | -    | 2    | 2.6  | V    |

|                      |                                      | V <sub>GE</sub> = 15 V, I <sub>C</sub> = 50 A, T <sub>J</sub> = 150 °C | -    | 2.4  |      | V    |

| C <sub>ies</sub>     | Input capacitance                    |                                                                        | -    | 4100 |      | pF   |

| C <sub>oes</sub>     | Output capacitance                   | $V_{CE} = 25 \text{ V}, f = 1 \text{ MHz}, V_{GE} = 0 \text{ V}$       | -    | 252  |      | pF   |

| C <sub>res</sub>     | Reverse transfer capacitance         |                                                                        | -    | 130  |      | pF   |

| R <sub>G</sub>       | Integrated gate resistance           | f = 1 MHz                                                              | -    | 11.5 |      | Ω    |

| Qg                   | Total gate charge                    | $V_{CC}$ = 1360 V, $I_{C}$ = 50 A, $V_{GE}$ = 0 to 15 V                | -    | 225  |      | nC   |

Table 5. Switching characteristics on inductive load (evaluated by characterization, not tested in production)

| Symbol               | Parameter                 | Test conditions                                                                               | Min. | Тур.  | Max. | Unit |

|----------------------|---------------------------|-----------------------------------------------------------------------------------------------|------|-------|------|------|

| t <sub>d(on)</sub>   | Turn-on delay time        | $V_{CC}$ = 900 V, $I_{C}$ = 50 A, $V_{GE}$ = ±15 V, $R_{G}$ = 8.2 $\Omega$                    | -    | 140   | -    | ns   |

| t <sub>r</sub>       | Current rise time         |                                                                                               | -    | 25    | -    | ns   |

| t <sub>d(off)</sub>  | Turn-off delay time       |                                                                                               | -    | 248   | -    | ns   |

| t <sub>f</sub>       | Current fall time         |                                                                                               | -    | 463   | -    | ns   |

| E <sub>off</sub> (1) | Turn-off switching energy |                                                                                               | -    | 10    | -    | mJ   |

| t <sub>d(on)</sub>   | Turn-on delay time        |                                                                                               | -    | 141.5 | -    | ns   |

| t <sub>r</sub>       | Current rise time         | $V_{CC}$ = 900 V, $I_{C}$ = 50 A, $V_{GE}$ = ±15 V, $R_{G}$ = 8.2 $\Omega$ , $T_{J}$ = 150 °C | -    | 27    | -    | ns   |

| t <sub>d(off)</sub>  | Turn-off delay time       |                                                                                               | -    | 263   | -    | ns   |

| t <sub>f</sub>       | Current fall time         |                                                                                               | -    | 618   | -    | ns   |

| E <sub>off</sub> (1) | Turn-off switching energy |                                                                                               | -    | 12.4  | -    | mJ   |

<sup>1.</sup> Including the tail of the collector current.

Note:

The aforementioned values are not tested at chip level and are strongly dependent on the package/module design and the mounting technology.

DS13689 - Rev 3 page 4/10

# 4 Die layout

Figure 1. Die drawing (dimensions are in mm)

Table 6. Die delivery

| Packing | Description                                                                                                               | <b>Details</b>                                                                                                                                                                                                  |

|---------|---------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| D7      | Wafer tested, inked or inkless, cut on sticky foil on 10.8" (276 mm) ring (see Figure 2. D7 drawing and die orientation). | Wafer is held by ring and placed in a proper box, containing a maximum of 25 wafers, sealed under vacuum inside a plastic envelope. The latter is protected by two foam shells and then sealed in a carton box. |

DS13689 - Rev 3 page 5/10

Metallic ring

Wafer

Demonstrating picture, not in scale

Figure 2. D7 drawing and die orientation

GADG220320211732MT

DS13689 - Rev 3 page 6/10

#### 5 Additional information

#### 5.1 Additional testing and screening

For customers requiring product supplied as known good die (KGD) or requiring specific die level testing (that is for dynamic and switching characterization), please contact the local ST sales office.

If KGD is requested, the shipping delivery is D8.

#### 5.2 Shipping

Several shipping options are offered. Consult the local ST sales office for availability:

- Die on film-sticky foil suffix on sales type D7

- Carrier tape suffix on sales type D8

#### 5.3 Handling

- Products must be handled only at ESD safe workstations. Standard ESD precautions and safe work environments are as defined in MIL-HDBK-263.

- Products must be handled only in a class 1000 or better-designated clean room environment.

- Singular die is not to be handled with tweezers. A vacuum wand with a nonmetallic ESD protected tip should be used.

### 5.4 Wafer/die storage

Once the packaging is opened, the wafer must be stored in a dry, inert atmosphere, such as nitrogen. Optimum temperature for storage is 18  $^{\circ}$ C  $\pm 2$   $^{\circ}$ C with as few variations as possible to avoid parasitic polymerization of the adhesive. Sawn wafers must be processed within 12 weeks after receipt by the customer. After the customer opens the package, the customer is responsible for the products.

DS13689 - Rev 3 page 7/10

## **Revision history**

Table 7. Document revision history

| Date        | Revision | Changes                                                                         |

|-------------|----------|---------------------------------------------------------------------------------|

| 22-Mar-2021 | 1        | First release.                                                                  |

| 29-Oct-2021 | 2        | Updated notes in <i>Table 2. Absolute maximum ratings</i> . Minor text changes. |

| 17-Aug-2022 | 3        | Updated Applications on cover page. Updated Table 6. Die delivery.              |

DS13689 - Rev 3 page 8/10

### **Contents**

| 1                        | Mech    | nanical parameters               | 2 |  |  |

|--------------------------|---------|----------------------------------|---|--|--|

| 2                        | Elect   | rical ratings                    | 3 |  |  |

| 3                        | Elect   | rical characteristics            | 4 |  |  |

| 4                        | Die la  | ayout                            | 5 |  |  |

| 5 Additional information |         |                                  |   |  |  |

|                          | 5.1     | Additional testing and screening | 7 |  |  |

|                          | 5.2     | Shipping                         | 7 |  |  |

|                          | 5.3     | Handling                         | 7 |  |  |

|                          | 5.4     | Wafer/die storage                | 7 |  |  |

| Rev                      | ision l | nistory                          | 8 |  |  |

#### **IMPORTANT NOTICE - READ CAREFULLY**

STMicroelectronics NV and its subsidiaries ("ST") reserve the right to make changes, corrections, enhancements, modifications, and improvements to ST products and/or to this document at any time without notice. Purchasers should obtain the latest relevant information on ST products before placing orders. ST products are sold pursuant to ST's terms and conditions of sale in place at the time of order acknowledgment.

Purchasers are solely responsible for the choice, selection, and use of ST products and ST assumes no liability for application assistance or the design of purchasers' products.

No license, express or implied, to any intellectual property right is granted by ST herein.

Resale of ST products with provisions different from the information set forth herein shall void any warranty granted by ST for such product.

ST and the ST logo are trademarks of ST. For additional information about ST trademarks, refer to <a href="https://www.st.com/trademarks">www.st.com/trademarks</a>. All other product or service names are the property of their respective owners.

Information in this document supersedes and replaces information previously supplied in any prior versions of this document.

© 2022 STMicroelectronics – All rights reserved

DS13689 - Rev 3 page 10/10