# **Data Sheet**

# by

# **SYNTEK<sup>®</sup>**

# ======STK1160========

# USB2.0 TV Tuner/Video Capture Controller

# Version 1.2

DESIGN CENTER 10F, No.1, Alley 30, Lane 358, Rueiguang Rd., Neihu District, Taipei City 114, Taiwan (R.O.C.) TEL: 886-2-26590055 FAX: 886-2-26590077

HEADQUARTERS 3F, No. 24-2, Industry E.Rd. IV, Science-Based Industrial Park, Hsinchu, Taiwan (R.O.C.) TEL: 886-3-5773181 FAX: 886-3-5778010

# **Caution!**

The information in this document is subject to change without notice and does not represent a commitment on part of the vendor, who assumes no liability or responsibility for any errors that may appear in this data sheet.

No warranty or representation, either expressed or implied, is made with respect to the quality, accuracy, or fitness for any particular part of this document. In no event DCNT the manufacturer be liable for direct, indirect, special, incidental or consequential damages arising from any defect or error in this data sheet or product. Product names appearing in this data sheet are for identification purpose only, and trademarks and product names or brand names appearing in this document are property of their respective owners.

This data sheet contains materials protected under *International Copyright Laws*. All rights reserved. No part of this data sheet may be reproduced, transmitted, or transcribed without the expressed written permission of the manufacturer and authors of this data sheet.

# **1 Product Overview**

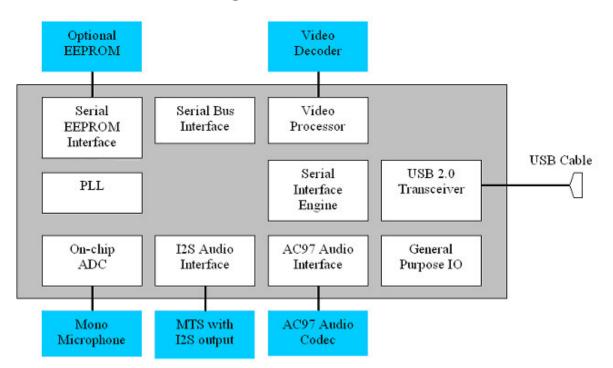

STK1160 is a highly integrated, single chip high-speed USB 2.0 compliant digital video imaging controller. Utilizing a high-speed, high-bandwidth isochronous pipe, it is able to transfer ITU-R 656 or ITU-R 601 format NTSC/PAL/SECAM video. It also provides 16-bit stereo audio stream through another USB 2.0 isochronous pipe.

STK1160 supports a wide range of video decoders, TV tuners, and demodulators. The device also provides AC97 and I2S interfaces for external stereo audio codec or uses an integrated low-cost 8-bit mono ADC.

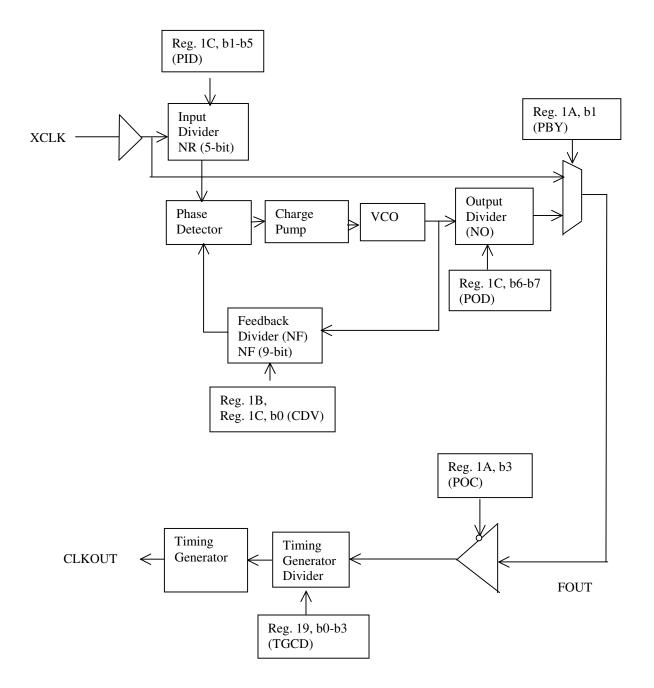

# 2 Functional Block Diagram

# **3** Product Features

### 3.1 Video Stream Interface

- Support 8-bit ITU-R 656 interface standard, and compliance with 10-bit video inputs.

- Support 8-bit ITU-R 601 interface standard, and compliance with 10-bit video inputs.

- Support hardware windowing and decimation.

# 3.2 Serial Bus Interfaces

- Support a serial communication to video decoders, demodulators, and TV tuners.

- Support a serial communication to optional remote controller.

- Support a serial communication to optional serial EEPROM.

- Support 2-wire or 3-wire serial communications.

# 3.3 Integrated Hi-Speed USB 2.0 Transceiver

- High-speed USB 2.0 and USB 1.1 full-speed functionality

- USB composite device with video and audio interfaces

- USB 2.0 isochronous video pipe can transfer up to 24 MB/sec

- USB 2.0 isochronous audio pipe can transfer up to 192 KB/sec

- Vendor ID, product IDs and string descriptors can be stored in an external serial EEPROM

# 3.4 Audio Interface

- Integrated on-chip ADC supports 8-bit mono audio recording at 8 KHz sampling rate.

- AC97 interface supports 16-bit stereo audio recording at 48/32 KHz sampling rate.

- I2S interface supports 16-bit stereo audio recording at 48/32 KHz sampling rate.

- Audio data is in PCM audio format

- Audio device is USB audio class compliant

## 3.5 General Purpose Input/Output Interface

• 10 general purpose input/output pins

## 3.6 Power Management

- 1.8V power supply voltage for chip core.

- 1.8V and 3.3V power supply voltage for on-chip USB transceiver.

- 1.8V power supply voltage for on-chip PLL.

- 3.3V power supply voltage for IO.

- 3.3V power supply voltage for on-chip ADC.

- Supports advance power down mechanism.

## 3.7 Other Features

- Supports all test modes defined in the USB 2.0 specification

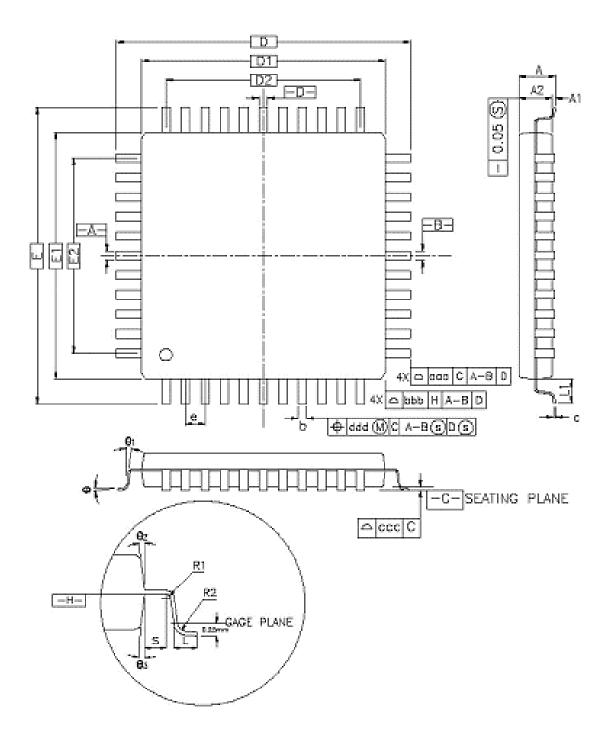

- 80-pin LQFP package

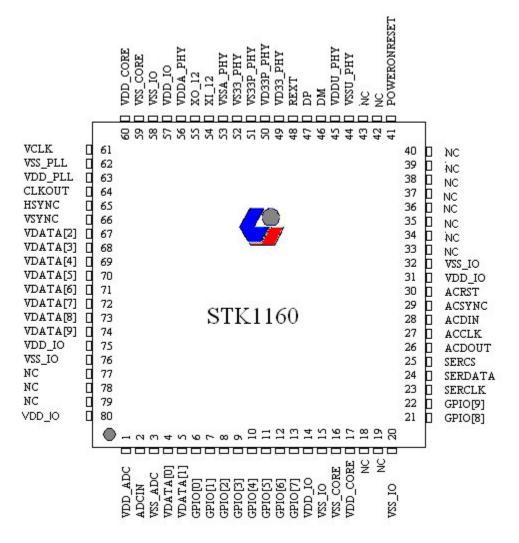

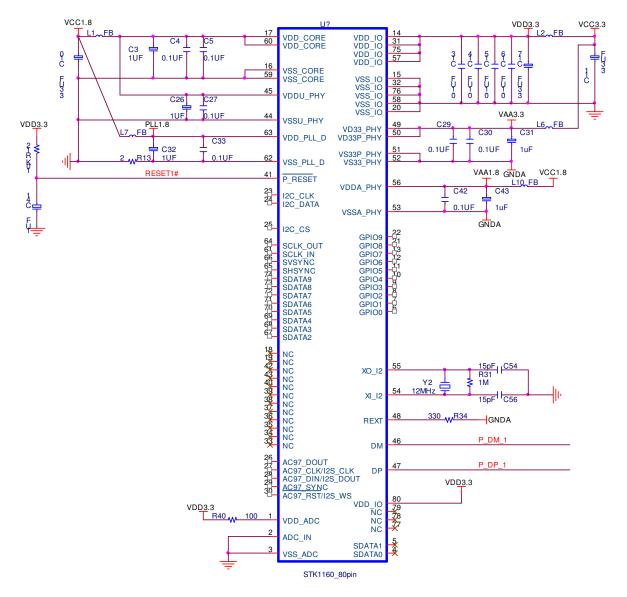

# 4 Pin Diagram

**STK1160**

# 4.1 Pin Descriptions

| Pin#           | Name            | Dir | Pull | Active | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------|-----------------|-----|------|--------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 4-5            | VDATA[0]-[1]    | Ι   | PD   |        | Video Decoder data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 67-74          | VDATA[2]-[9]    | Ι   | PD   |        | Video Decoder data input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|                |                 |     |      |        | For 8-bit video data interface, use VDATA [2]-[9].                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 61             | VCLK            | Ι   | PD   |        | Video Decoder clock input                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 64             | CLKOUT          | 0   | PD   |        | Video Decoder clock output                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 65             | HSYNC           | I/O | PD   |        | Horizontal Sync signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 66             | VSYNC           | I/O | PD   |        | Vertical Sync signal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 23             | SERCLK          | 0   |      |        | Serial bus clock                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 24             | SERDATA         | I/O |      |        | Serial bus data                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 25             | SERCS           | 0   | PD   | Н      | Serial bus chip select                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 6              | GPIO[0]         | I/O | PD   |        | General purpose I/O 0                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                 |     |      |        | If 93C46 serial ROM is present, this pin is used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |                 |     |      |        | Clock (SK) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 7              | GPIO[1]         | I/O | PD   |        | General purpose I/O 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                 |     |      |        | If 93C46 serial ROM is present, this pin is used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |                 |     |      |        | Data (DIO) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 8              | GPIO[2]         | I/O | PD   |        | General purpose I/O 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                 |     |      |        | If 93C46 serial ROM is present, this pin is used for                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|                |                 |     |      |        | Chip Select (CS) signal.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 9              | GPIO[3]         | I/O | PD   |        | General purpose I/O 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 10             | GPIO[4]         | I/O | PD   |        | General purpose I/O 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 11             | GPIO[5]         | I/O | PD   |        | General purpose I/O 5                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 12             | GPIO[6]         | I/O | PU   |        | General purpose I/O 6                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 13             | GPIO[7]         | I/O | PD   |        | General purpose I/O 7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                |                 |     |      |        | If video source does not always output valid data, this                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                 |     |      |        | pin can be used as data valid signal when VVLD                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

|                |                 |     |      |        | register is enabled. "High" indicates the data is valid                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|                |                 |     |      |        | and "Low" indicates the data is invalid.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 21-22          | GPIO[8]-GPIO[9] | I/O |      |        | General purpose I/O 8-9                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 2              | ADCIN           | Ι   |      |        | Audio analog input from microphone                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 26             | ACDOUT          | 0   | PD   |        | AC97 serial data out                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 27             | ACCLK           | Ι   | PD   |        | AC97 clock in / I2S clock in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 28             | ACDIN           | Ι   | PD   |        | AC97 serial data in / I2S data in                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |