STK7560 Series

# Chopper Type Parallel 2-Output Voltage Regulators

### Applications

- Voltage regulator for printers, electronic typewriters, XY plotters.

- Voltage regulator for MSX per sonal computer s, flopp y disk drive, computer terminals, por table VTRs.

### Features

- ICs having 2 outputs for microcomputer power supply (5V) and motor drive power supply (12, 15, 24, 36V) and being capable of deli vering 2 regulated outputs from 1 rectifier.

- Good efficiency due to chopper type and no beat trouble due to fixed oscillation type oscillator common to 2 outputs.

- Independent o vercurrent protectors f or 2 outputs (F oldback characteristics).

- Output 2 (drive power supply) can be turned ON/OFF by external signal. Two outputs can be also turned ON/OFF simultaneously by an e xternal cir cuit connected (Refer to Sample Application Circuit).

- High-precision setting of output v oltage, elminating the need to use a variable resistor for adjustment.

- Input/output Gnd lines are united into one, f acilatating combination with other nagative power supply.

- A negative voltage regulator (-5V, -12V, etc.) can be connected externally (Refer to Sample Application Circuit).

- Output voltage/output current are provided in series.

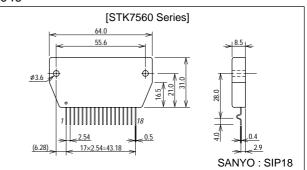

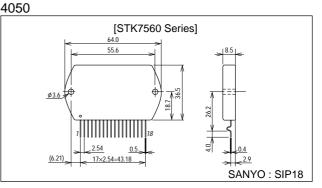

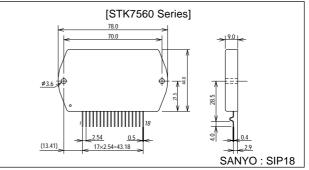

## **Package Dimensions**

#### unit:mm

#### 4049

## unit:mm

#### 4051A

- Any and all SANYO products described or contained herein do not have specifications that can handle applications that require extremely high levels of reliability, such as life-support systems, aircraft's control systems, or other applications whose failure can be reasonably expected to result in serious physical and/or material damage. Consult with your SANYO representative nearest you before using any SANYO products described or contained herein in such applications.

- SANYO assumes no responsibility for equipment failures that result from using products at values that exceed, even momentarily, rated values (such as maximum ratings, parameters) listed in products specifications of any and all SANYO products described or contained herein.

SANYO Electric Co., Ltd. Semiconductor Company TOKYO OFFICE Tokyo Bldg., 1-10, 1 Chome, Ueno, Taito-ku, TOKYO, 110-8534 JAPAN

## **Case Outline**

| Type No. | Case<br>Outline | Type No. | Case<br>Outline | Type No. | Case<br>Outline | Type No.  | Case<br>Outline |

|----------|-----------------|----------|-----------------|----------|-----------------|-----------|-----------------|

| STK7561A | No.4049         | STK7562A | No.4049         | STK7563A | No.4049         | *STK7565A | No.4049         |

| STK7561F | No.4050         | STK7562F | No.4050         | STK7563F | No.4050         | *STK7565F | No.4050         |

| STK7561G | No.4050         | STK7562G | No.4050         | STK7563G | No.4050         |           |                 |

| STK7561J | No.4050         | STK7562J | No.4050         | STK7563J | No.4050         |           |                 |

| STK7561L | No.4051         | STK7562L | No.4051         | STK7563L | No.4051         |           |                 |

\* New product

## **Specifications**

#### Main Maximum Ratings and Operating Characteistics at $Ta = 25^{\circ}C$

|          | Limits             |       |                | OUTPUT  |      |     | OUTPUT   |      |     |

|----------|--------------------|-------|----------------|---------|------|-----|----------|------|-----|

| Type No. | Vin max            | Tg ma | Tst            | Vøa     | lløa | lop | Vv       | lløa | lop |

|          | ()vdc)             | (°C)  | (°C)           | ()/     | A()  | A() | ()/      | A()  | (A  |

| STK7561A |                    | 105   | –30 to<br>+105 | 5V±0.1V | 2    | 2.4 | 12V±0.2V | 2    | 4   |

| STK7561F | 50<br>(05 setiers) |       |                |         | 3    | 3.6 |          | 3    | 6   |

| STK7561G |                    |       |                |         | 3    | 3.6 |          | 5    | 10  |

| STK7561J | (25 rating)        |       |                |         | 5    | 6.0 |          | 2    | 4   |

| STK7561L |                    |       |                |         | 5    | 6.0 |          | 5    | 10  |

| STK7562A |                    |       |                |         | 2    | 2.4 |          | 2    | 4   |

| STK7562F | 50                 |       | 20.40          |         | 3    | 3.6 |          | 3    | 6   |

| STK7562G | 50<br>(30 rating)  | 105   | -30 to<br>+105 | 5V±0.1V | 3    | 3.6 | 15V±0.3V | 5    | 10  |

| STK7562J |                    |       |                |         | 5    | 6.0 |          | 2    | 4   |

| STK7562L |                    |       |                |         | 5    | 6.0 |          | 5    | 10  |

| STK7563A |                    |       |                |         | 2    | 2.4 |          | 2    | 4   |

| STK7563F | 50                 |       | 20.40          |         | 3    | 3.6 |          | 3    | 6   |

| STK7563G |                    | 105   | -30 to         | 5V±0.1V | 3    | 3.6 | 24V±0.4V | 5    | 10  |

| STK7563J | (35 rating)        |       | +105           |         | 5    | 6.0 |          | 2    | 4   |

| STK7563L |                    |       |                |         | 5    | 6.0 |          | 5    | 10  |

| STK7565A | 80                 | 105   | -30 to         | 5V±0.1V | 2    | 2.4 | 36V±0.6V | 2    | 4   |

| STK7565F | (45 rating)        | 105   | +105           | 5V±0.1V | 3    | 3.6 | 30V±0.0V | 3    | 6   |

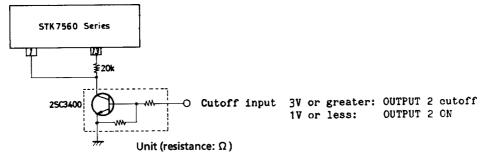

(Note) 1 Output 2 cutoff (pin 1 input ) : OUTPUT 2 cutoff at 1V or less, OUTPUT 2 ON at 3V or greater.

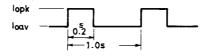

2 The peak current value of OUTPUT 1 (5V) is set to 120% of the rating.

3 The peak current value of OUTPUT 2 (12V, 15V, 24V, 36V) is set to 200% of the rating considering the motor driving mode.

4 The secondary winding provided in the 5V choke coil makes OUTPUT 3 (-5V, 12V, -15V, 0.3A) available.

5 Peak current setting time.

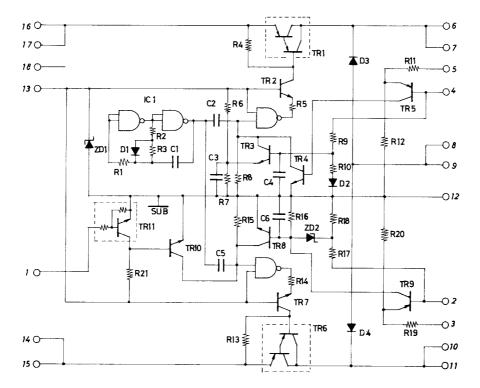

## **Equivalent Circuit**

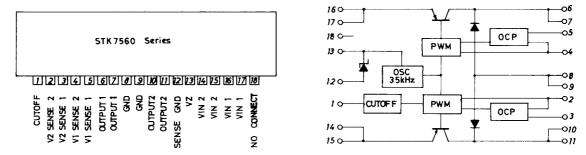

## **Equivalent Circuit Block Diagram and Pin Assignment**

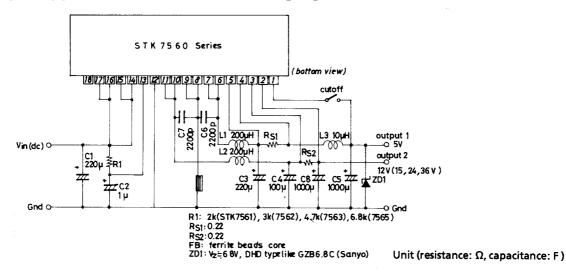

Sample Application Circuit 1 : Standard peripheral circuit

Note 1 The N. C pin (pin 18) must not be used as a relay pin for other line, pin.

2 Pins connected inside the IC (6-7, 8-9, 10-11, 14-15, 16-17) must be also connected on the printed circuit board.

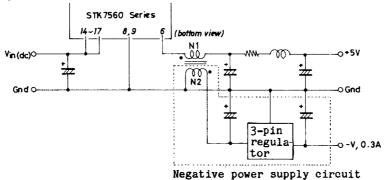

## Sample Application Circuit 2: 3 Outpus including a nagative output

The secondary winding provided in the 5V choke coil provides 2 functions of choke coil and transformer, eliminating the need to use a center tap on the input transformer to make a negative power supply available. The 5V output needs a load of approximately 0.5A.

Sample 5V choke coil (for -12V output)

| <u> </u>  |      |              |                 |          |  |

|-----------|------|--------------|-----------------|----------|--|

| <u>eo</u> |      |              | A, F, or G type | J type   |  |

| 00 N2     | Fer  | rite core    | EI-26           | EI-30    |  |

|           |      | Gap          | 0.5mm           | 0.5mmt×2 |  |

| -         | N1   | No. of turns | 40              | 35       |  |

|           | INI  | Wøre dia     | 0ø6mm           | 0.8mm    |  |

|           | N2 - | No. of turns | 120             | 105      |  |

|           |      | Wiøde dia    | 0ømm            | 0.3mm    |  |

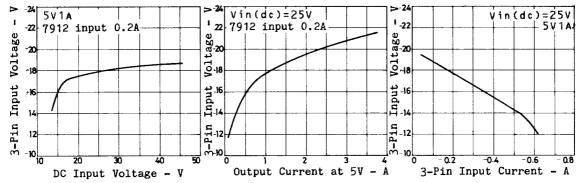

Sample data of 3-pin regulator input voltage (coil output voltage)/A, F, or G type

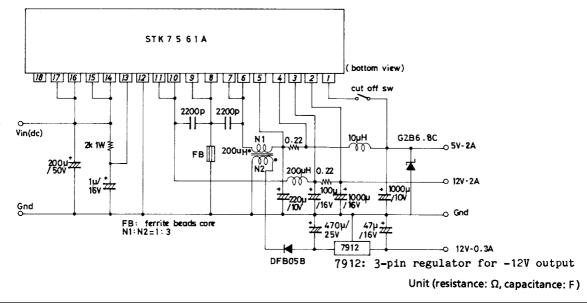

Sample Application Circuit 3 : STK7561A : 3 outputs of 5V, 12V, -12V

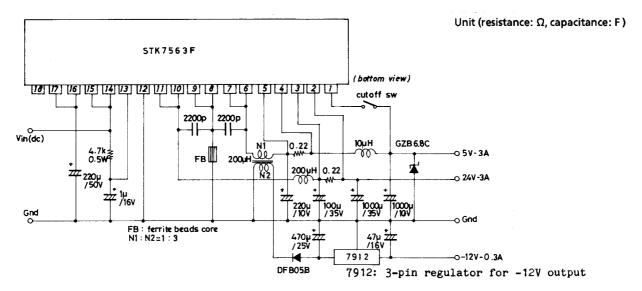

### Sample Application Circuit 4 : STK7563F : 3 outputs of 5V, 24V, -12V

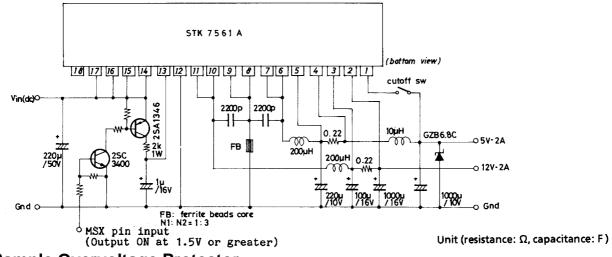

Sample Application Circuit 5 : STK7561A : Power supply for MSX personal computer, 2-output simultaneous ON/OFF

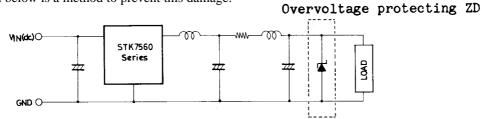

#### Sample Overvoltage Protector

Overcurrent may cause great damege. Particulary, the circuit connected to microcomputer power supply (5V) may be damaged.

Shown below is a method to prevent this damage.

Connect a zener diode in parallel with the load. Use a DHD (double heat sink) type zener diode whose zener voltage is 1 to 2V higher than supply voltage (5V).

Overvoltage exceeding the zener voltage is limited by the zener diode.

With no current limiting rersistor connected, overcurrent flows in the zener diode.

Then, zener diode is shorted, thus protecting the load.

## 'High active' setting of cutoff input

'Low active' setting of cutoff input can be changed to 'High active' setting as shown below.

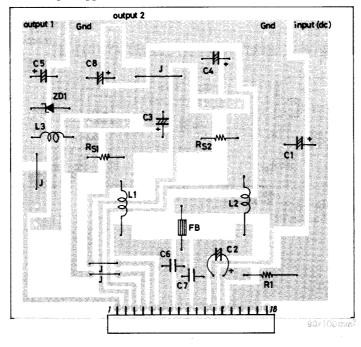

### **Sample Printed Circuit Pattern**

Standard peripheral circuit for Sample Application Circuit 1 (Cu-foiled area)

#### Precautions

- $\cdot$  Make the large current-carrying lines thicker and shorter.

- $\cdot$  Please high input capacitor C1 close to the input pin of the IC.

- Place switching spike-reducing C6, C7 close to the IC pins.

- Connect GND of ferrite bead core to GND of input capacitor C1 to minimize the core, C1-related pattern loop area.

- Connect V SENSE GND (pin 12) to GND of current line near the load.

- Connect GND of output capacitors C3, C4, C5, C8 near the load not to oppose current flow.

- $\cdot$  Connect pins connected inside the IC (pins 6, 7, etc.) also on the printed circuit board.

- $\cdot$  Do not use NC (pin 18) as a relay pin for otherline, pin.

#### Resons

- $\rightarrow$  To minimize voltage loss on the pattern

- $\rightarrow$  To minimize input ripple.

- $\rightarrow$  To reduce switching spike more effectively.

- $\rightarrow$  To reduce switching spike more effectively.

- → To improve load r egulation c haracteristic of output voltage.

- $\rightarrow$  To improve ripple characteristic.

- $\rightarrow$  To provent current from concentrating on pin.

Input Voltage - Vdc

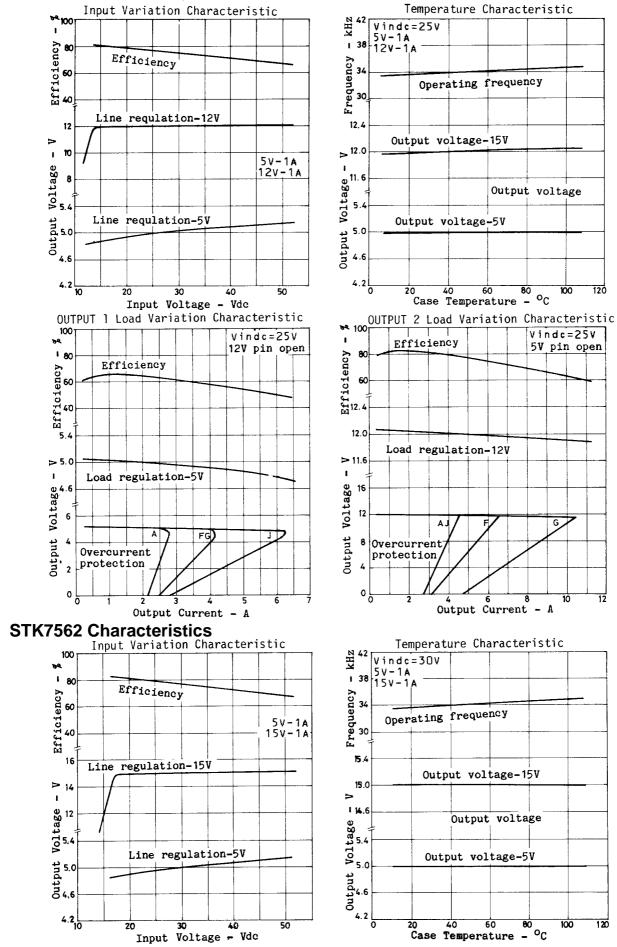

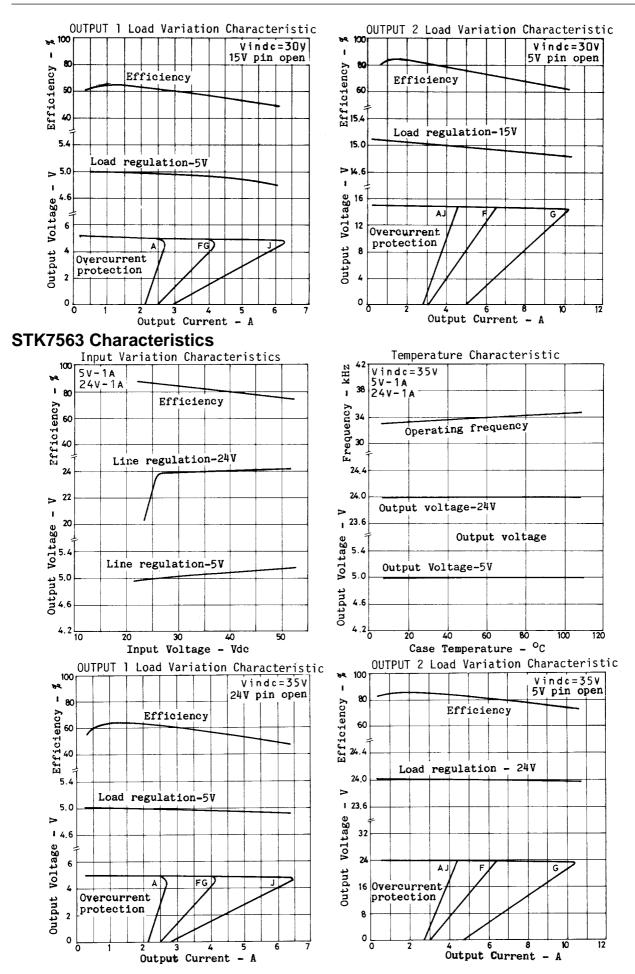

### **STK7561 Characteristics**

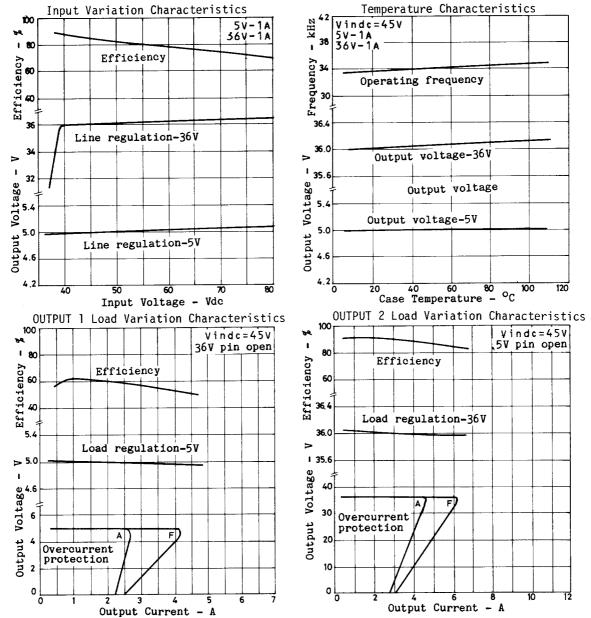

## STK7565 Characteristics

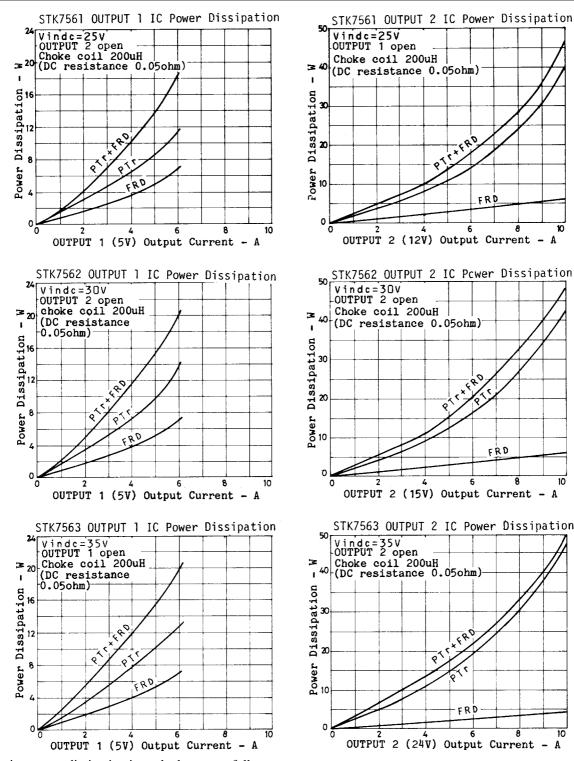

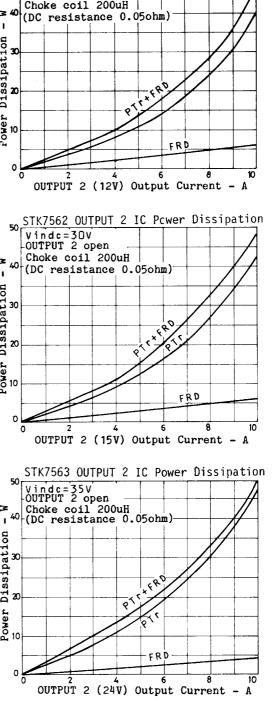

## **Termal Design**

Most power dissipation of STK7560 series-applied volage regulators is caused by power transistor PTr, flywheel diode FRD, choke coil, current detect resistor.

Power detect parts are PTr FRD for the IC system, and TR1, D3 for OUTPUT 1, and TR6, D4 for OUTPUT 2. The relation between output current and power dissipation is shown below.

Assuming power dissipation in each element as follows : P<sub>T</sub>1 for power transistor of OUTPUT 1

- PF1 for FRD of OUTPUT 1

- PT<sub>2</sub> for power transistor of OUTPUT 2

- PF2 for FRD of OUTPUT 2

Total power dissipation Pd in the IC and heat sink thermal resistance  $\theta$ ca are :

$$Pd=(PT + PF1) + (PT2 + PF2)$$

[W]

$$\theta ca = \frac{Tc - Ta}{Pd} \quad [^{\circ}C/W]$$

where Tc : Case temperature=105°C, Ta=Ambient temperature Junction temperature in each element is :

$T_j = Pd \times \theta_j c + Tc [^{\circ}C]$

| Type No.             | Teble of Thermal Resistanc θjc            |                                                                                                                    |                                                                                                                                            |                                                                                                                                                                                        |  |  |  |

|----------------------|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|                      | ODTR                                      | PUT 1                                                                                                              | OUTPUT                                                                                                                                     |                                                                                                                                                                                        |  |  |  |

|                      | T <b>R</b> 1                              | D6                                                                                                                 | TAR                                                                                                                                        | D                                                                                                                                                                                      |  |  |  |

| S97K7560A            | 45                                        | 19.                                                                                                                | 45                                                                                                                                         | 12.                                                                                                                                                                                    |  |  |  |

| STK7560F<br>STK7560G | 457                                       | 1 <b>2</b> .                                                                                                       | 25                                                                                                                                         | 5.                                                                                                                                                                                     |  |  |  |

| S <b>7</b> K7560J    | 25                                        | 57                                                                                                                 | 45                                                                                                                                         | 12.                                                                                                                                                                                    |  |  |  |

|                      | S <b>3</b> K7560A<br>STK7560F<br>STK7560G | Type No.         O២TF           T&1         S\$\$K7560A         45           STK7560F         STK7560G         457 | Type No.         OUTPUT 1           T&1         D6           S\$\$K7560A         45         19.           STK7560F         457         12. | Type No.         O型TPUT 1         OUTF           T81         D6         TR           S\$K7560A         45         19.         45           STK7560F         457         12.         25 |  |  |  |

where Tj max=150°C, Pd : Power dissipation P<sub>T</sub>1, P<sub>F</sub>1, P<sub>T</sub>2, P<sub>F</sub>2 in each element,  $\theta$  jc=Junction-case thermal resistance in each element.

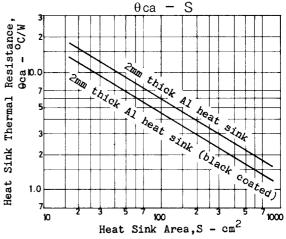

To dessipate heat satisfactorily, use a heat sink with thermal resistance  $\theta$ ca meeting two temperature conditions of Tc max=105°C, Tj max=105°C.

Since the actual thermal resistance of the heat sink greatly depends on various conditions such as equipment layout or ventilation, allow an ample margin in thermal design. Shown right is the relation between Al heat sink area and thermal resistance. The Al surface coated with black improves thermal characteristic, lowering thermal resistance approximately 20% as compared with the Al heat sink of the same area.

## **Description of Operation of Internal Blocks**

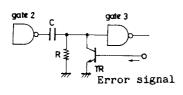

[PWM]

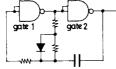

External excitation type OSC circuit where the CMOS NAND gate-used ring OSC is formed by the 2-stage NAND circuit, delivering basic pulses. This circuit provides pulse width modulation where the frequency is constant and the duty only varies.

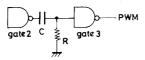

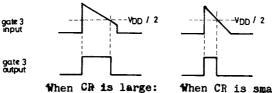

Pulse width modulation (PWM) is provided by differentiating the output of NAND gate 2 using the differentiating circuit of time constant CR as shown left and by applying the result to the input of NAND gate 3.

The threshold voltage at the input of NAND gate 3 is approximately 1/2 of supply voltage V<sub>DD</sub> applied to the gate and the PWM output as shown below is obtained.

In the actual circuit transistor TR is connected in parallel with resistor R as shown left. The error signal from the constant-voltage output side is used to control the base current of TR so that the resistor value is varied equivalently to make the output voltage constant.

When the error signal is large, the base bias of TR is deepend and the equivalent resistance gets small, narrowing the pulse width to control the output voltage.

When the error signal is small, the base bias of TR is shallowed, widening the pulse width to control the output voltage.

```

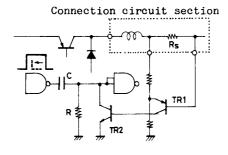

[OCP]

```

Overcurrent protection (OSC) is provided as follows : The voltage drop across current detect resistor Rs of the external connection circuit is detected to turn ON transistor TR1. Then, the collector current is applied to the base of TR2 to make time constant CR small, forcing the pulse width to be narrow.

The "fold-back" overcurrent characteristic occurs in which the pulse width is narrowd to drop the output voltage and also to decrease the output current.

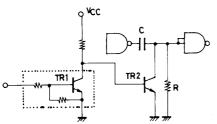

#### [Cutoff]

The cutoff circuit (remote ON/OFF control) is so designed that the output is turned ON at 'H' level of cutoff input. In the circuit shown below, when the input is at 'H' level, TR1 is turned ON to drop the base voltage of TR2 and TR2 is turned OFF. Since TR2 is independent of the differentiating circuit composed of C and R, the output is turned ON.

When the input is at 'L' level, TR1 is turned OFF to increase the base voltage of TR2 and TR2 is turned ON. Since TR2 is connected in parallel with R of the differentiating circuit, R is short-circuited to make R of time constant CR O equivalently and the output is turned OFF.

### New products = Development of 5V-1A rated small-sized STK7570 series

| Series   | Maximum Ratings / Ta=25°C |            |                       | OUTPUT 1               |          |              | OUTPUT 2 |      |      |

|----------|---------------------------|------------|-----------------------|------------------------|----------|--------------|----------|------|------|

| Lineup   | Vin max                   | Tg ma      | Tet                   | Vv                     | lko a    | lo p         | Vv       | lksa | lo p |

| Type No. | ()vdc)                    | (°C)       | (°C)                  | ()/                    | A()      | A()          | ()/      | A()  | (A   |

| STK7571A |                           | 105        | -30 to                | -30 to<br>+105 5V±0.1V | 1        | 1.2          | 12V±0.2V | 2    | 4    |

| STK7571B |                           |            | +105                  |                        | 1        | 1.2          |          | 3    | 6    |

| STK7572A |                           | -30 to     | -30 to                | 5V±0.1V                | 1        | 1.2          | 15V±0.3V | 2    | 4    |

| STK7572B |                           | 105        | +105                  |                        | 1        | 1.2          |          | 3    | 6    |

| STK7573A | 60                        | 105        | -30 to                | 5V±0.1V                | 1        | 1.2          | 24V±0.4V | 2    | 4    |

| STK7573B | [35]                      | 105        | +105                  | 5v±0.1v                | 1        | 1.2          | 240±0.40 | 3    | 6    |

| STK7575B | 70                        | 105 -3     | 105 -30 to<br>+105 5V | 5V±0.1V                | 1        | 1.2          | 36V±0.6V | 2    | 4    |

| STK7575B | [45]                      | 105        |                       |                        | 1        | 1.2          | 307±0.07 | 3    | 6    |

|          |                           | 59.2<br>52 |                       | 8.5<br>13<br>12<br>12  | <b>*</b> | OSC<br>35kHz |          | OCP  |      |

- Specifications of any and all SANYO products described or contained herein stipulate the performance, characteristics, and functions of the described products in the independent state, and are not guarantees of the performance, characteristics, and functions of the described products as mounted in the customer's products or equipment. To verify symptoms and states that cannot be evaluated in an independent device, the customer should always evaluate and test devices mounted in the customer's products or equipment.

- SANYO Electric Co., Ltd. strives to supply high-quality high-reliability products. However, any and all semiconductor products fail with some probability. It is possible that these probabilistic failures could give rise to accidents or events that could endanger human lives, that could give rise to smoke or fire, or that could cause damage to other property. When designing equipment, adopt safety measures so that these kinds of accidents or events cannot occur. Such measures include but are not limited to protective circuits and error prevention circuits for safe design, redundant design, and structural design.

- In the event that any or all SANYO products(including technical data, services) described or contained herein are controlled under any of applicable local export control laws and regulations, such products must not be exported without obtaining the export license from the authorities concerned in accordance with the above law.

- No part of this publication may be reproduced or transmitted in any form or by any means, electronic or mechanical, including photocopying and recording, or any information storage or retrieval system, or otherwise, without the prior written permission of SANYO Electric Co., Ltd.

- Any and all information described or contained herein are subject to change without notice due to product/technology improvement, etc. When designing equipment, refer to the "Delivery Specification" for the SANYO product that you intend to use.

- Information (including circuit diagrams and circuit parameters) herein is for example only ; it is not guaranteed for volume production. SANYO believes information herein is accurate and reliable, but no guarantees are made or implied regarding its use or any infringements of intellectual property rights or other rights of third parties.

This catalog provides information as of November, 1999. Specifications and information herein are subject to change without notice.