# **STR720**

# ARM720T<sup>™</sup> 16/32-BIT MCU WITH 16K RAM, USB, CAN, 3 TIMERS, ADC, 6 COMMUNICATIONS INTERFACES

#### PRELIMINARY DATA

#### ARM720T MCU

- 32-bit RISC MCU with 3-stage pipeline.

- Max. CPU frequency 70 MHz

- Fully instructions compatible with the ARM7 family of processors

- 8 KByte Instruction + Data cache, 4-way set-associative

- Write buffer de-coupling CPU from system memory during write operations

- MMU for virtual to physical address mapping and memory protection

#### Memories

- 16 KBytes Program RAM Memory

- External SDRAM Interface for up to 128 Mbytes SDRAM

- External Memory Interface (EMI) for up to 8 Mbytes SRAM, Flash, ROM.

- ATAPI interface supporting PIO4 mode

#### Nested interrupt controller

- Fast interrupt handling with multiple vectors

- 32 vectors with 16 IRQ priority levels

- 2 maskable FIQ sources

#### Clock, Reset and Supply Management

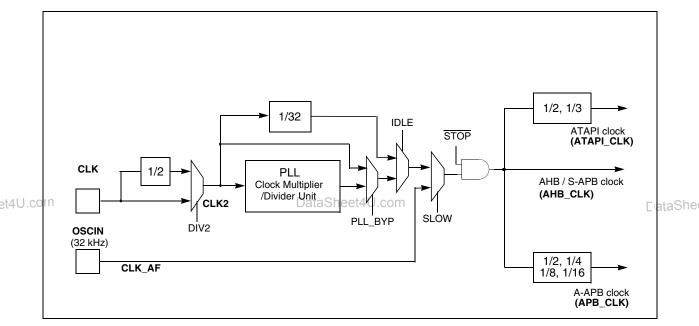

- Internal system clocks generated by fully internal PLL

- Power management providing different operating modes: RUN, SLOW, STOP, STANDBY.

#### 34 I/O ports

- 34 multifunctional bidirectional I/O lines

- 5 ports with interrupt capability

Table 1. Device Summary

- 3 Timers

- Two 16-bit programmable Timer modules with prescaler (f<sub>APB</sub> divided by 1 to 256)

driven from internal selectable clock (oscillator or CPU clock), output compare and input capture functions.

16-bit Watchdog Timer with 8-bit prescaler

#### 6 Communications Interfaces

USB v 2.0 Full Speed (12Mbit/s) Device Function with Suspend and Resume support

de – CAN module compliant with the CAN DataSheet4U.comspecification V2.0 part B (active).

- Two High-Speed Universal Asynchronous Receiver Transmitter (UART) for full-duplex asynchronous communication.

- Two Buffered Serial Peripheral Interfaces (BSPI) for full-duplex, synchronous, communications with external devices, master or slave operation.

#### A/D Converter

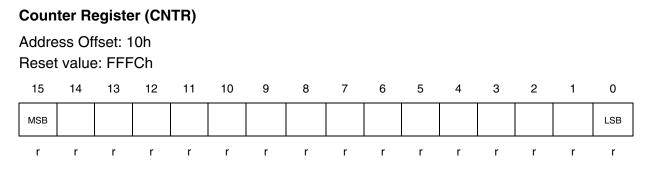

Sigma Delta Analog/Digital Converter with 11.5-bit ENOB resolution supporting 4 multiplexed inputs at up to 950 Hz sampling rate.

#### Development Tools Support

- 5-pin JTAG port (IEEE 1149.1 Standard)

| Features              | STR720RBQ6                      | STR720RXH6                          |

|-----------------------|---------------------------------|-------------------------------------|

| Boot ROM - bytes      | 4                               | K                                   |

| Program RAM - bytes   | 16                              | бК                                  |

| Operating Voltage     | 3.0 to 3.6V for I/Os and A/D, 1 | .8V for core and backup block       |

| Operating Temperature | -40 to                          | +85°C                               |

| Package               | PQFP208 28x28x3.4               | BGA (contact marketing for details) |

DataSheet4U.com

www.DataSheet4U.com Bev. 4.0

#### December 2004

1/401

| 11        | NTR   |                                                  | 10          |

|-----------|-------|--------------------------------------------------|-------------|

| 2 A       | ACRO  | ONYMS                                            | 11          |

| 3 5       | SYST  | TEM BLOCK DIAGRAM                                | 13          |

| 4 F       | PIN C | DATA                                             | 14          |

|           | 4.1   | Power Supply pins                                | 14          |

|           | 4.2   | Global Pins                                      |             |

|           | 4.3   | JTAG pins                                        | 15          |

|           | 4.4   | Port 1 pins                                      |             |

|           | 4.5   | Port 2 pins                                      | 16          |

|           | 4.6   | Port 3 pins                                      | 17          |

|           | 4.7   | Port 4 pins                                      | 18          |

|           | 4.8   | Main Clock input pins                            | 19          |

|           | 4.9   | Port 6 pins                                      | 19          |

|           | 4.10  | Port 7 pins                                      | 21          |

|           | 4.11  |                                                  |             |

| 5 A       | ARCI  |                                                  | 27          |

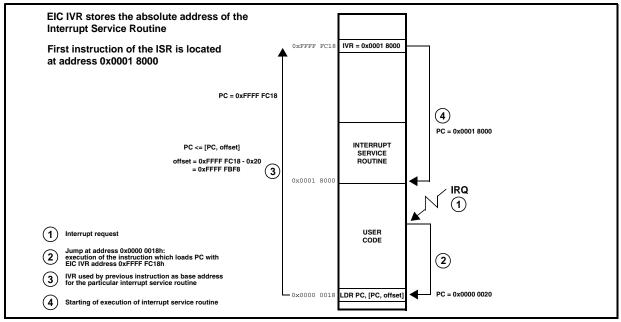

| :         | 5.1   | Enhanced Interrupt Controller (EIC)              | 27          |

|           | 5     | 5.1.1 IRQ Interrupt Vector Table                 | 28          |

|           | 5     | 5.1.2 FIQ Interrupt Vector Table                 | 32          |

| et4U.co   | 5     | 5.1.3 IRQ Interrupt Vectoring                    | 33 ataShe   |

|           | 5.2   | Wake-up/Interrupt management Unit (WIU)          | 34          |

|           | 5.3   | DMA Controller (DMAC)                            |             |

|           | 5.4   | DRAM controller (DRAMC)                          |             |

|           | 5.5   | External Memory Interface                        |             |

|           | 5.6   | ATAPI IDE interface                              |             |

|           | 5.7   | Reset and Clock Control Unit (RCCU)              |             |

|           |       | 5.7.1 Clock management                           |             |

|           | -     | 5.7.2 RESET management                           |             |

|           |       | Real Time Clock (RTC)                            |             |

|           | 5.9   | AHB-APB bridges       Clock Gating Control (CGC) |             |

|           | 5.10  |                                                  |             |

|           | -     | Buffered Serial Peripheral Interface (BSPI)      |             |

|           |       | Controller Area Network Interface (CAN)          |             |

|           |       | Universal Serial Bus Interface (USB)             |             |

|           |       | WatchDoG timer (WDG)                             |             |

|           |       | Extended Function Timer (EFT)                    |             |

|           |       | S S-D Analog to Digital Converter (ADC)          |             |

|           |       | General Purpose I/O Ports                        |             |

|           |       | Dedicated Pins                                   |             |

| DataSheet |       | Del-                                             | Sheet4U.com |

| 5.2          | 20 Miscellanea Registers                                   | 46                  |

|--------------|------------------------------------------------------------|---------------------|

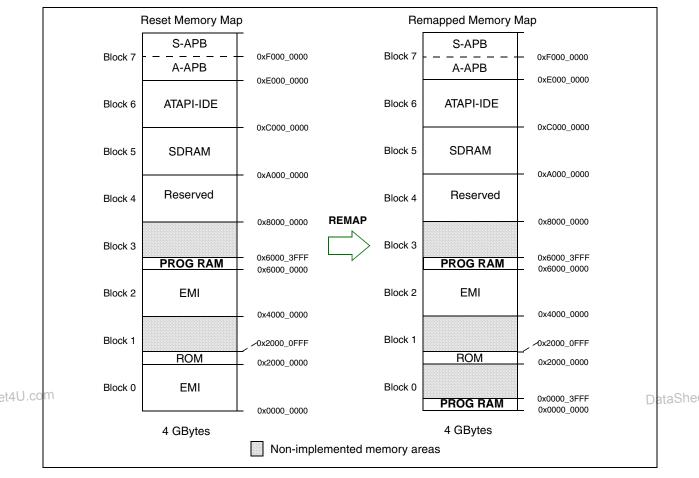

| 6 MEI        | MORY ORGANIZATION                                          | 47                  |

| 6.1          | Program memory                                             | 47                  |

| 6.2          | Memory map                                                 | 48                  |

| 6.3          | APB Bridges Mapping                                        | 48                  |

|              | 6.3.1 Asynchronous APB sub-system (A-APB)                  | 48                  |

|              | 6.3.2 Synchronous APB sub-system (S-APB)                   | 50                  |

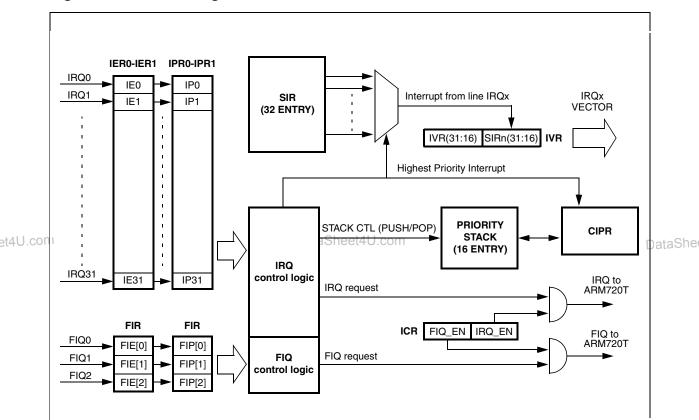

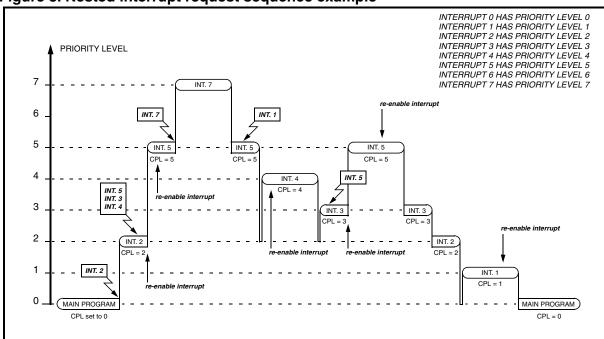

| 7 ENI        | HANCED INTERRUPT CONTROLLER (EIC)                          | 51                  |

| 7.1          | Introduction                                               | 51                  |

| 7.2          | 2 Main Features                                            | 51                  |

| 7.3          | Functional Description                                     | 52                  |

|              | 7.3.1 Priority Level Arbitration                           | 53                  |

| 7.4          | Register Description                                       | 56                  |

|              | 7.4.1 Register map                                         | 66                  |

| 7.5          | Programming considerations                                 | 67                  |

| 7.6          | 6 Application note                                         | 67                  |

|              | 7.6.1 Avoiding LR_sys and r5 registers content loss        |                     |

|              | 7.6.2 Hints about subroutines used inside ISRs             | 69                  |

| 7.7          | ' Interrupt latency                                        | 69                  |

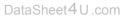

|              | KE-UP INTERRUPT UNIT (WIU)                                 |                     |

| et4U.co 8.1  | Introduction                                               | 70 ataShe           |

| 8.2          | 2 Main Features                                            | 70                  |

| 8.3          | Functional Description                                     | 71                  |

|              | 8.3.1 Interrupt Mode Selection                             | 72                  |

|              | 8.3.2 Wake-up Mode Selection                               | 72                  |

|              | 8.3.3 STOP Mode Entering Conditions                        |                     |

| 8.4          |                                                            |                     |

| 8.5          |                                                            |                     |

| 8.6          | 5 5                                                        |                     |

|              | 8.6.1 Procedure for Entering/Exiting STOP mode             |                     |

|              | 8.6.2 Simultaneous Setting of Pending Bits                 |                     |

|              | 8.6.3 Dealing with level-active signals as interrupt lines |                     |

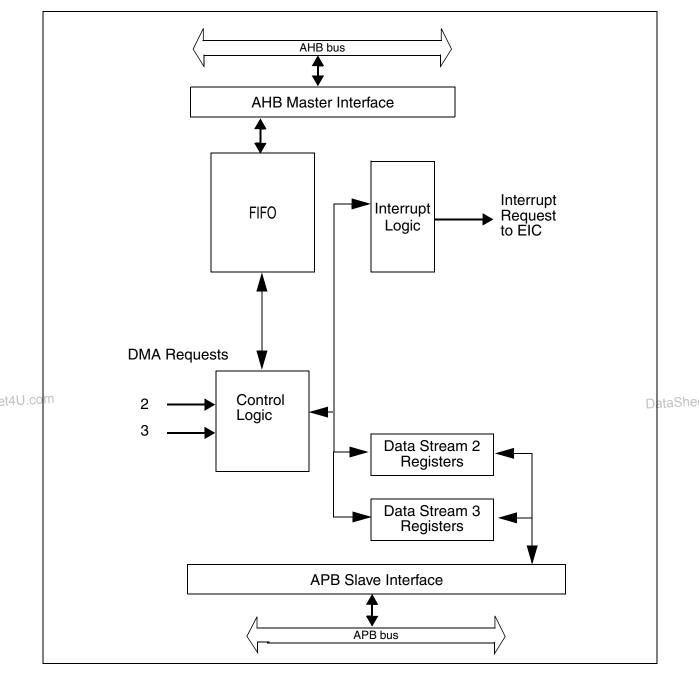

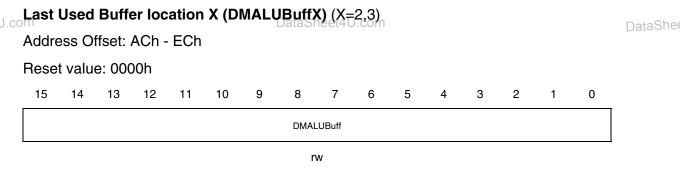

| 9 DM         | A CONTROLLER (DMAC)                                        | 81                  |

| 9.1          | Introduction                                               | 81                  |

| 9.2          |                                                            |                     |

| 9.3          |                                                            |                     |

|              | 9.3.1 Circular mode operations                             |                     |

| 9.4          |                                                            |                     |

|              | 9.4.1 Register map                                         | 99                  |

| 10 DF        | RAM CONTROLLER (DRAMC)                                     |                     |

| DataSheet4U. | .com                                                       | www.DataSheet4U.com |

\_

| 10.1         | Introduction                          | . 101       |

|--------------|---------------------------------------|-------------|

| 10.2         | Main Features                         | . 101       |

| 10.3         | Functional Description                | . 101       |

|              | 10.3.1 AHB Interface                  | . 101       |

|              | 10.3.2 APB Interface                  | . 103       |

|              | 10.3.3 Refresh Timer                  | . 103       |

| 10.4         | Register description                  | . 104       |

|              | 10.4.1 Register map                   | . 113       |

| 10.5         | Programming considerations            | . 114       |

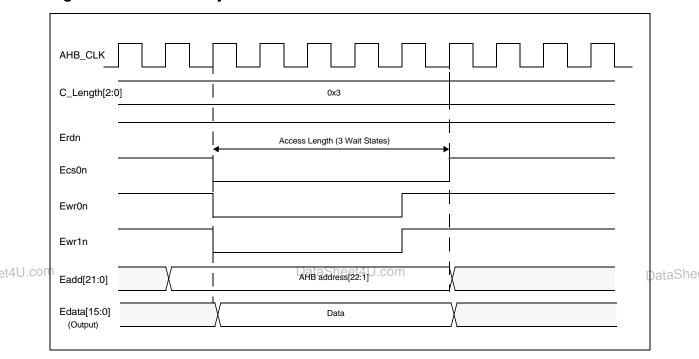

| 11 EX        | <b>FERNAL MEMORY INTERFACE (EMI)</b>  | 115         |

| 11.1         | Introduction                          | . 115       |

| 11.2         | Main Features                         | . 115       |

| 11.3         | Functional Description                | . 116       |

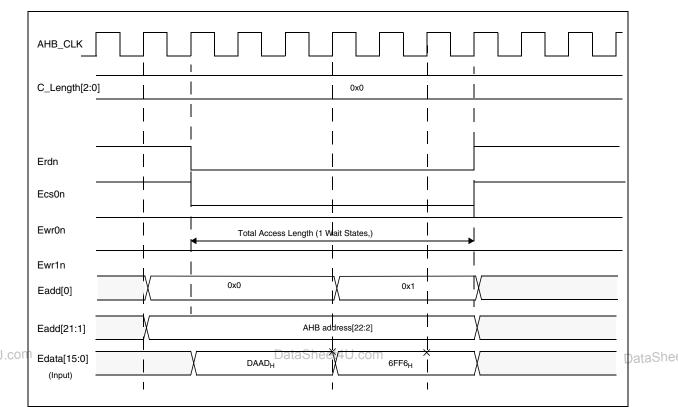

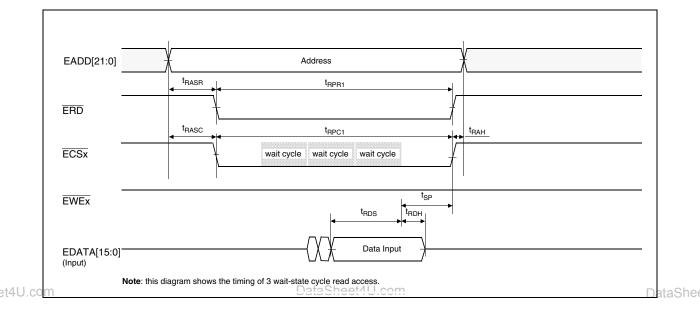

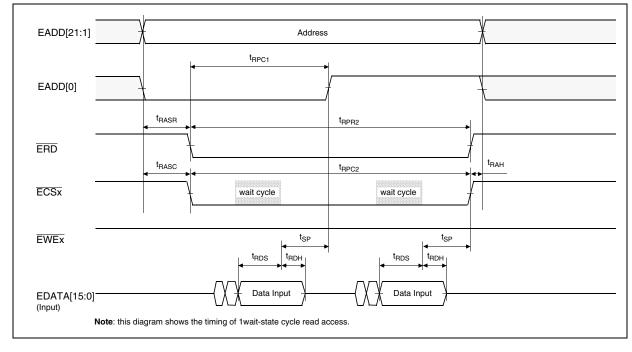

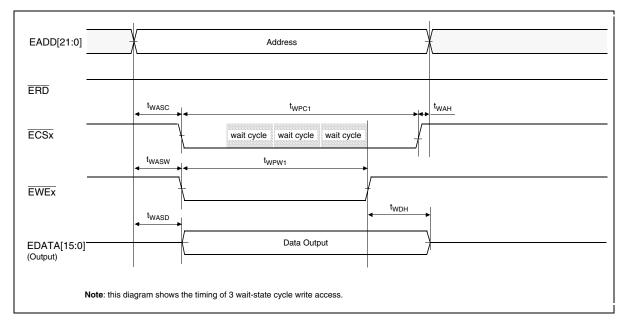

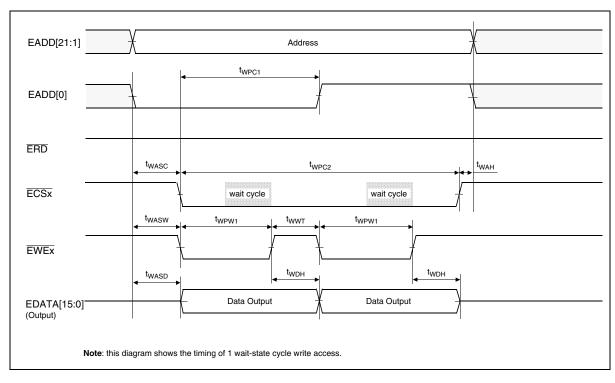

|              | 11.3.1 EMI Programmable Timings       | . 116       |

|              | 11.3.2 Write Access Examples          | . 118       |

|              | 11.3.3 Read Access Examples           |             |

|              | Register description                  |             |

|              | 11.4.1 Register map                   |             |

|              | Programming considerations            |             |

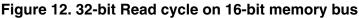

| 12 AT/       | API-IDE INTERFACE                     | 126         |

| et4U.co 12.1 | Introduction                          | .126 ataShe |

| 12.2         |                                       |             |

|              | Functional Description                |             |

|              | Programming Considerations            |             |

|              | 12.4.1 Initialization                 |             |

|              | 12.4.2 Basic Read Transfer            |             |

|              | Register map                          |             |

|              | 12.5.1 IDE Command Block Register Set |             |

|              | 12.5.2 IDE Configuration Register Set |             |

|              |                                       |             |

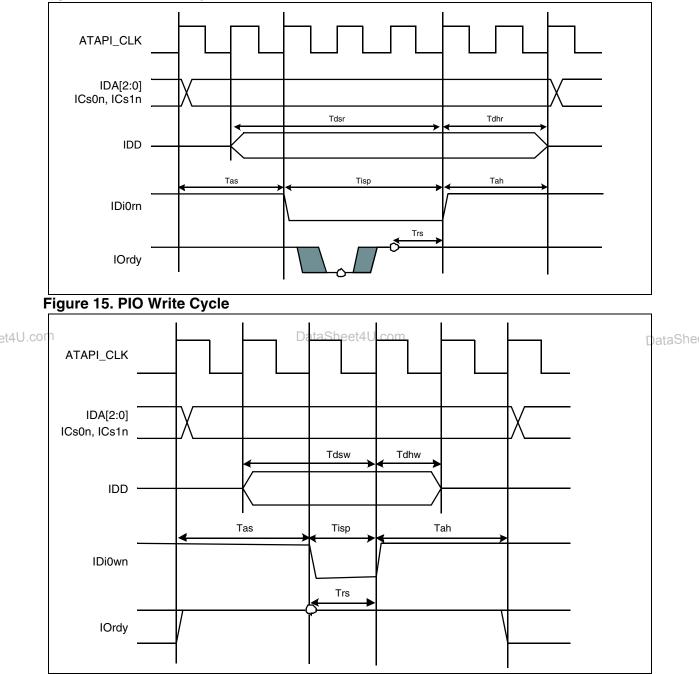

|              | 12.6.1 IDE PIO Read/Write Cycles      |             |

| 13 RE        | SET AND CLOCK CONTROL UNIT (RCCU)     |             |

| 13.1         |                                       |             |

|              | Main Features                         |             |

|              | Functional Description                |             |

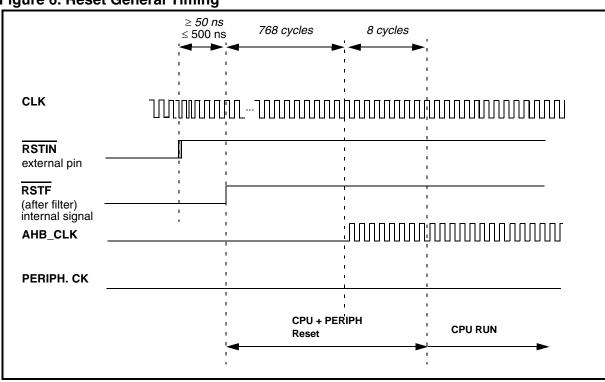

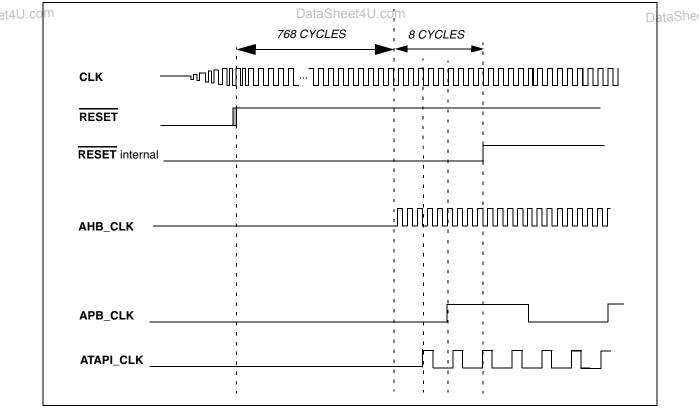

|              | 13.3.1 Reset Management               |             |

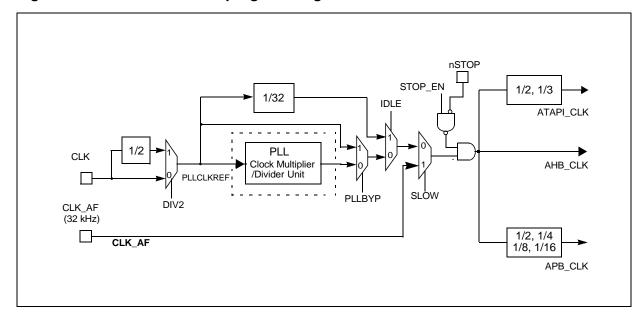

|              | 13.3.2 PLL Management                 |             |

|              | 13.3.3 Mode of Operation              |             |

|              | Register description                  |             |

|              | 13.4.1 Register map                   | . 149       |

|              |                                       | 1 ml 1 ml   |

DataSheet4U.com

www.DataSheet4U.com

4/401

\_

| 14 REAL T          | IME CLOCK (RTC)                                    | 150                     |

|--------------------|----------------------------------------------------|-------------------------|

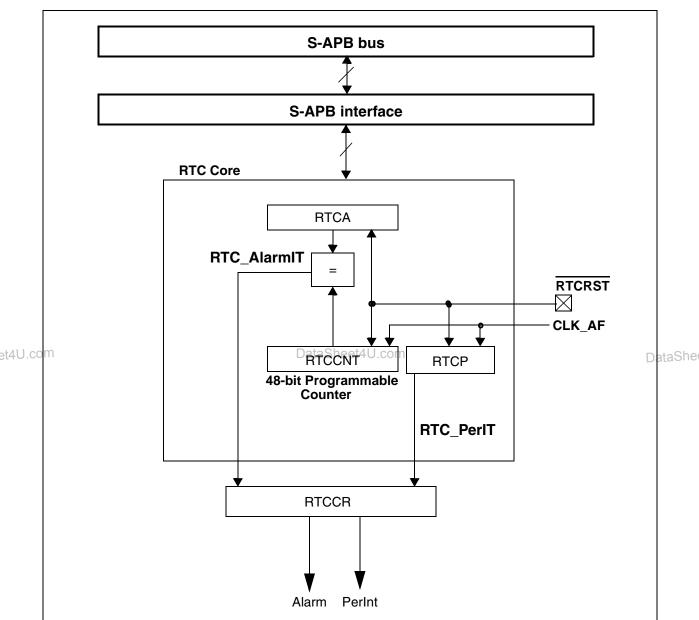

| 14.1 Intr          | oduction                                           | . 150                   |

| 14.2 Mai           | n Features                                         | . 150                   |

| 14.3 Fun           | ctional Description                                | . 150                   |

| 14.3.1             | 1 Overview                                         | . 150                   |

| 14.3.2             | 2 Reset procedure                                  | . 152                   |

| 14.3.3             | 3 Free-running mode                                | . 152                   |

| 14.3.4             | 4 Configuration mode                               | . 152                   |

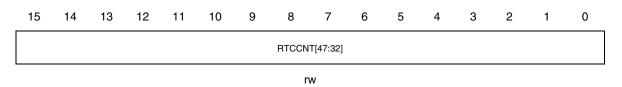

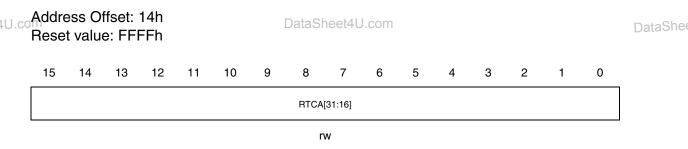

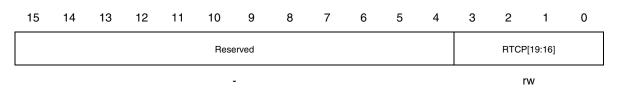

| 14.4 Reg           | jister description                                 | . 152                   |

|                    | 1 Register map                                     |                         |

| 14.5 Pro           | gramming considerations                            | . 158                   |

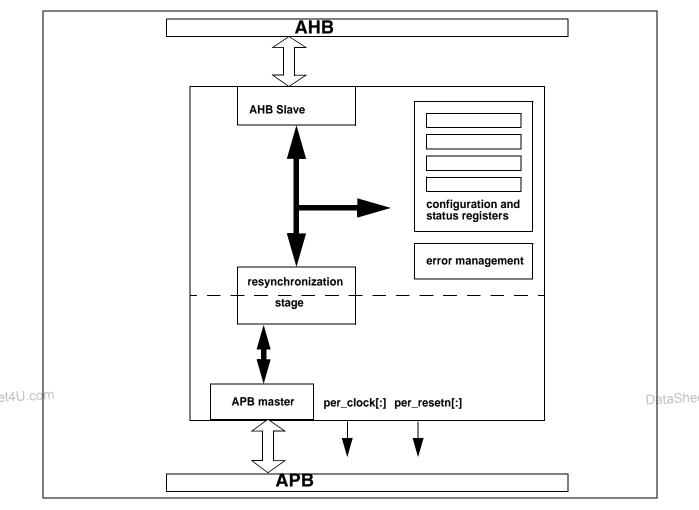

| 15 ASYNC           | HRONOUS AHB-APB BRIDGE (A3BRG)                     | 160                     |

| 15.1 Intr          | oduction                                           | . 160                   |

| 15.2 Mai           | n Features                                         | . 160                   |

| 15.3 Fun           | ctional Description                                | . 160                   |

| 15.3.1             | 1 Peripherals clock gating                         | . 162                   |

| 15.3.2             | 2 Peripherals reset control                        | . 162                   |

| 15.4 Reg           | jister description                                 | . 162                   |

| 15.4.1             | 1 Register map                                     | . 168                   |

|                    |                                                    | 169                     |

| et4U.co 16.1 Intro | oduction                                           | .169 ataShe             |

| 16.2 Mai           | n Features                                         | . 169                   |

| 16.3 Fun           | ctional Description                                | . 169                   |

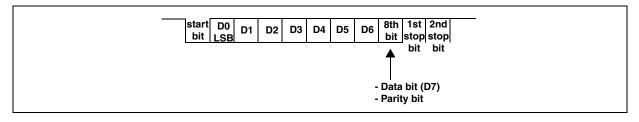

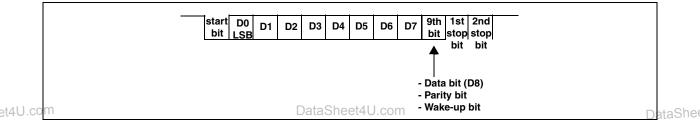

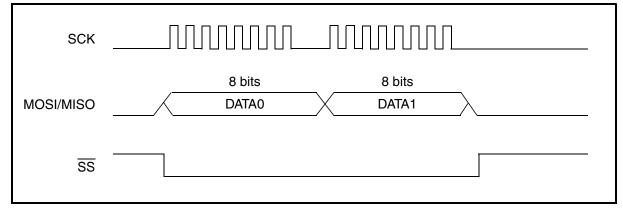

| 16.3.1             | 1 Data frames                                      | . 169                   |

|                    | 2 Transmission                                     |                         |

|                    | 3 Reception                                        |                         |

|                    | 4 Timeout mechanism                                |                         |

|                    | 5 Baud rate generation                             |                         |

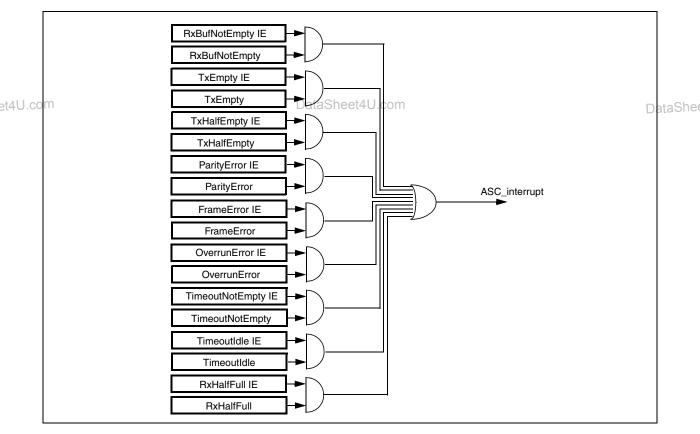

|                    | 6 Interrupt control                                |                         |

|                    | 7 Using the ASC interrupts when fifos are disabled |                         |

|                    | 3 Using the ASC interrupts when fifos are enabled  |                         |

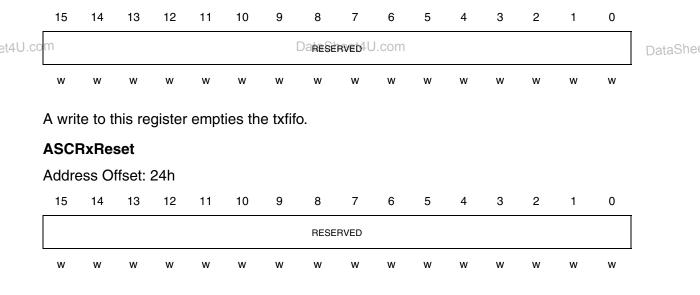

| -                  | Jister description                                 |                         |

|                    | 1 Register map                                     |                         |

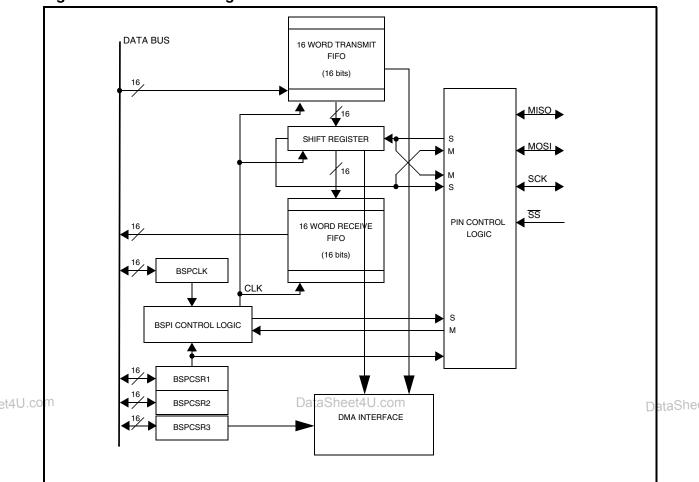

|                    | RED SPI (BSPI)                                     |                         |

|                    | oduction                                           |                         |

|                    | n Features                                         |                         |

|                    |                                                    |                         |

|                    | 1 BSPI Pin Description                             |                         |

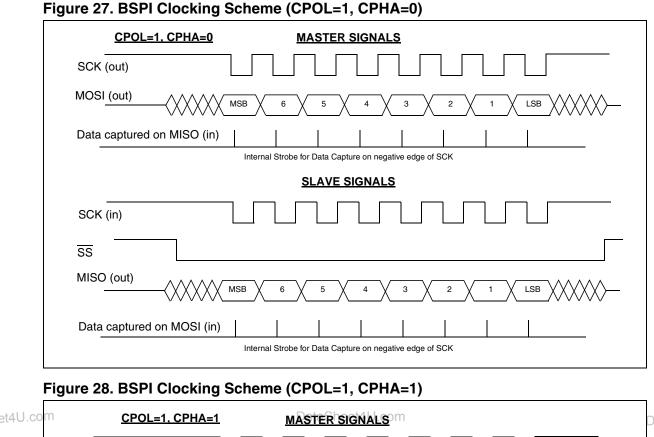

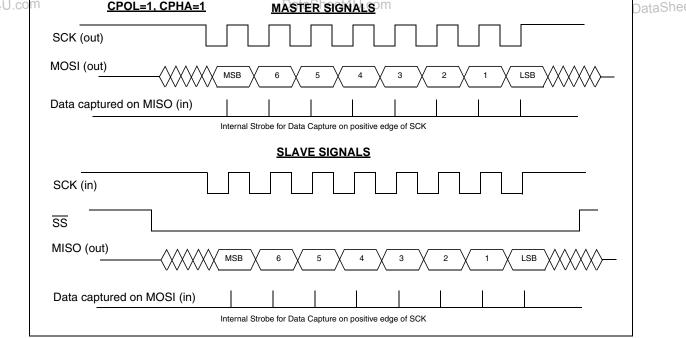

|                    | 2 BSPI Operation                                   |                         |

|                    | 3 Transmit FIFO                                    | . 191<br>ataSheet4U.com |

| DataSheet4U.com    | 141444.D                                           | ata31166140.0011        |

\_

| 17.3.4      | Receive FIFO                                         |

|-------------|------------------------------------------------------|

|             | Start-up Status                                      |

|             | Clocking problems and clearing of the shift-register |

|             | Interrupt control                                    |

| 17.3.8      | DMA Interface                                        |

| 17.4 Regi   | ster description                                     |

|             | Register map                                         |

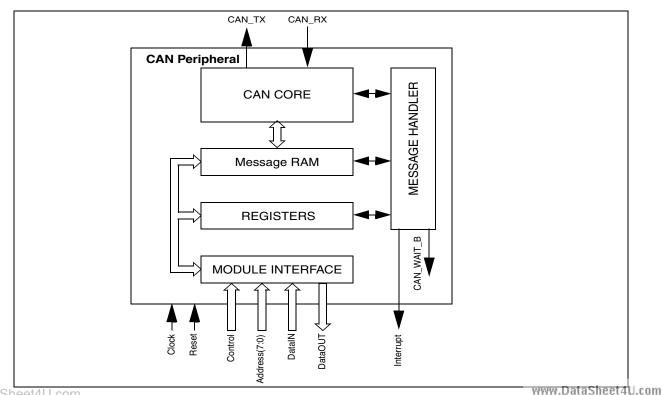

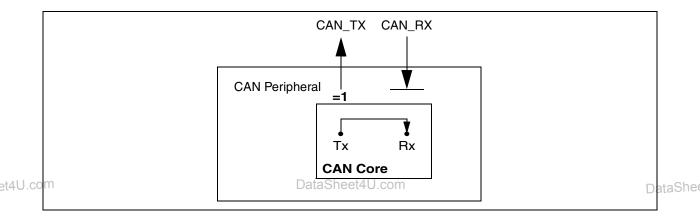

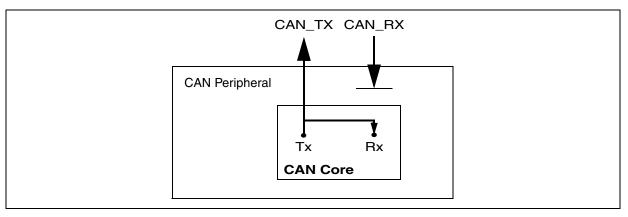

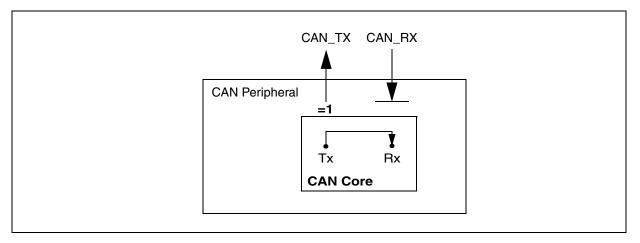

|             | er Area Network (CAN) 202                            |

|             | duction                                              |

| 18.2 Main   | Features                                             |

|             | k Diagram                                            |

| 18.4 Fund   | ctional Description                                  |

|             | Software Initialization                              |

|             | CAN Message Transfer 204                             |

| 18.4.3      | Disabled Automatic Re-Transmission Mode              |

| 18.4.4      | Test Mode                                            |

| 18.4.5      | Silent Mode                                          |

|             | Loop Back Mode                                       |

| 18.4.7      | Loop Back Combined with Silent Mode                  |

| 18.4.8      | Basic Mode                                           |

|             | Software Control of CAN_TX Pin                       |

| 18.5 Regi   | ster Description                                     |

|             | CAN Interface Reset State                            |

| 18.5.2      | CAN Protocol Related Registers                       |

| 18.5.3      | Message Interface Register Sets 219                  |

| 18.5.4      | Message Handler Registers 232                        |

| 18.6 Regi   | ster Map                                             |

| 18.7 CAN    | Communications                                       |

|             | Managing Message Objects 240                         |

| 18.7.2      | Message Handler State Machine 240                    |

| 18.7.3      | Configuring a Transmit Object 244                    |

| 18.7.4      | Updating a Transmit Object 244                       |

| 18.7.5      | Configuring a Receive Object 245                     |

| 18.7.6      | Handling Received Messages                           |

| 18.7.7      | Configuring a FIFO Buffer 246                        |

| 18.7.8      | Receiving Messages with FIFO Buffers                 |

|             | Handling Interrupts                                  |

| 18.7.1      | 0Configuring the Bit Timing 249                      |

| 18.7.1      | 1Register Map                                        |

| 19 USB Slav | ve Interface (USB) 263                               |

DataSheet4U.com

et4U

www.DataSheet4U.com

6/401

ataShe

\_\_\_\_

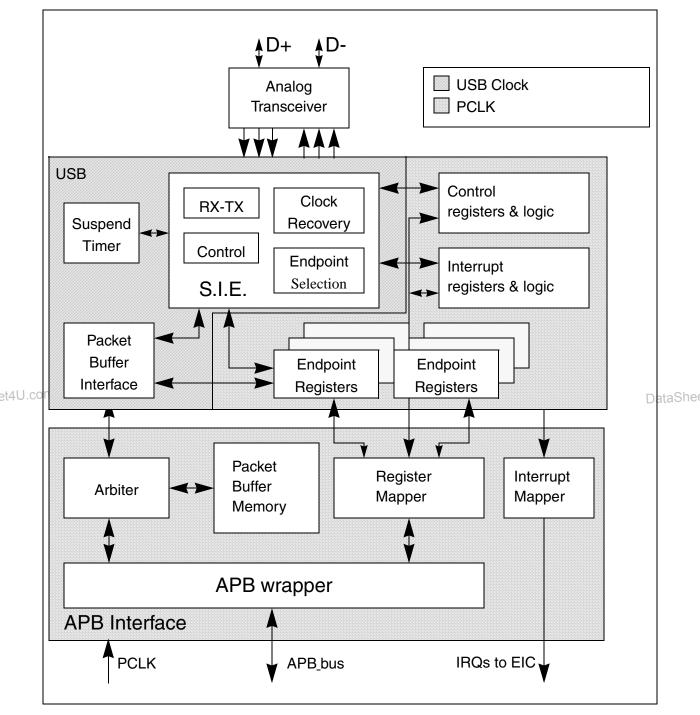

|         | 19.1  | Intro  | duction                        | 263         |           |

|---------|-------|--------|--------------------------------|-------------|-----------|

|         | 19.2  | Main   | Features                       | 263         |           |

|         | 19.3  | Bloc   | k Diagram                      | 263         |           |

|         | 19.4  | Fund   | tional Description             | 265         |           |

|         |       | 19.4.1 | Description of USB Blocks      | 266         |           |

|         | 19.5  | Prog   | ramming Considerations         | 267         |           |

|         |       |        | Generic USB Device Programming |             |           |

|         |       | 19.5.2 | System and Power-On Reset      | 267         |           |

|         |       | 19.5.3 | Double-Buffered Endpoints      | 273         |           |

|         |       | 19.5.4 | Isochronous Transfers          | 276         |           |

|         |       |        | Suspend/Resume Events          |             |           |

|         |       | -      | ster Description               |             |           |

|         |       |        | Common Registers               |             |           |

|         |       |        | Endpoint-Specific Registers    |             |           |

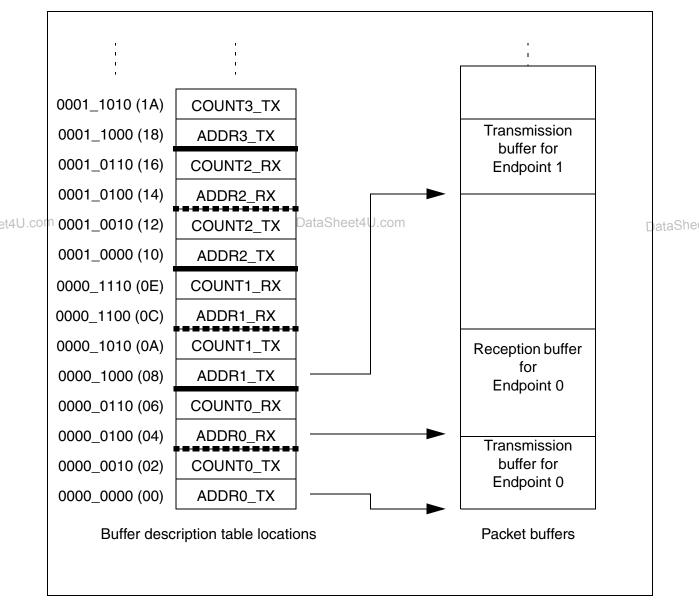

|         |       |        | Buffer Descriptor Table        |             |           |

|         |       |        | Register Map                   |             |           |

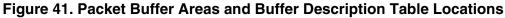

| 2       | 20 WA | TCHE   | DOG TIMER (WDG)                | 303         |           |

|         | 20.1  | Intro  | duction                        | 303         |           |

|         | 20.2  | Main   | Features                       | 303         |           |

|         |       |        | tional Description             |             |           |

| et4U.co |       |        | Free-running Timer mode        |             | ataShe    |

|         |       |        | Watchdog mode                  |             |           |

|         |       | -      | ster description               |             |           |

|         |       | 20.4.1 | Register Map                   | 308         |           |

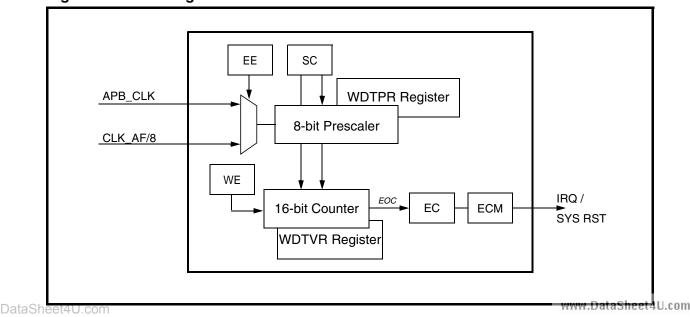

| 2       | 21 EX |        | ED FUNCTION TIMER (EFT)        |             |           |

|         | 21.1  |        | duction                        |             |           |

|         | 21.2  |        | Features                       |             |           |

|         |       |        | tional Description             |             |           |

|         |       |        | Counter                        |             |           |

|         |       |        | External Clock                 |             |           |

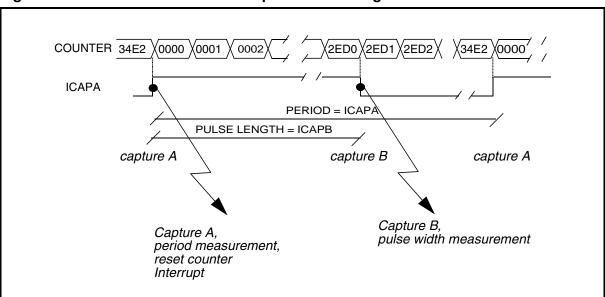

|         |       |        | Input Capture                  |             |           |

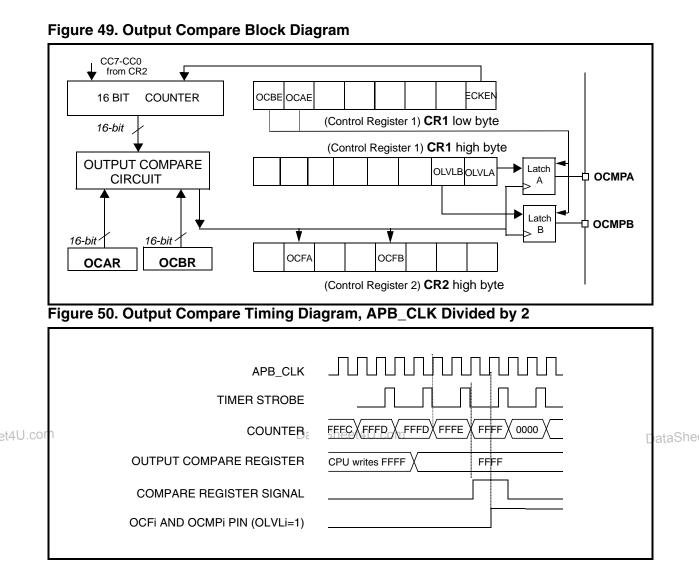

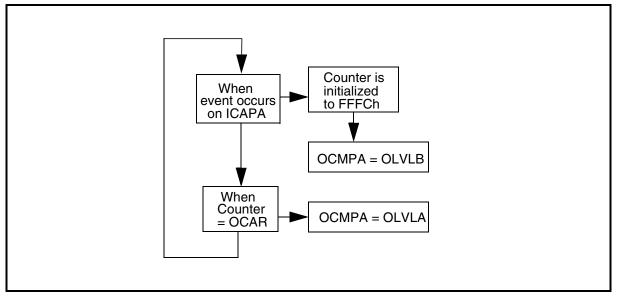

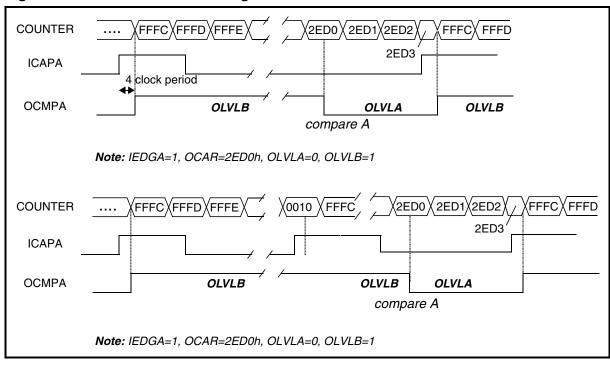

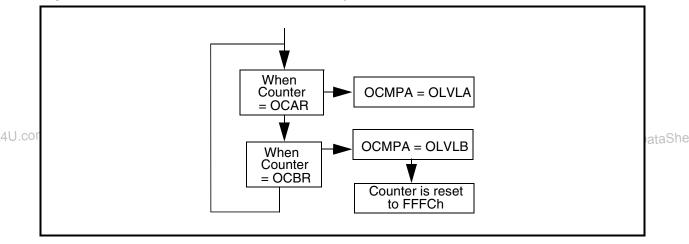

|         |       |        | Output Compare                 |             |           |

|         |       |        | Forced Compare Mode            |             |           |

|         |       |        | One Pulse Mode                 |             |           |

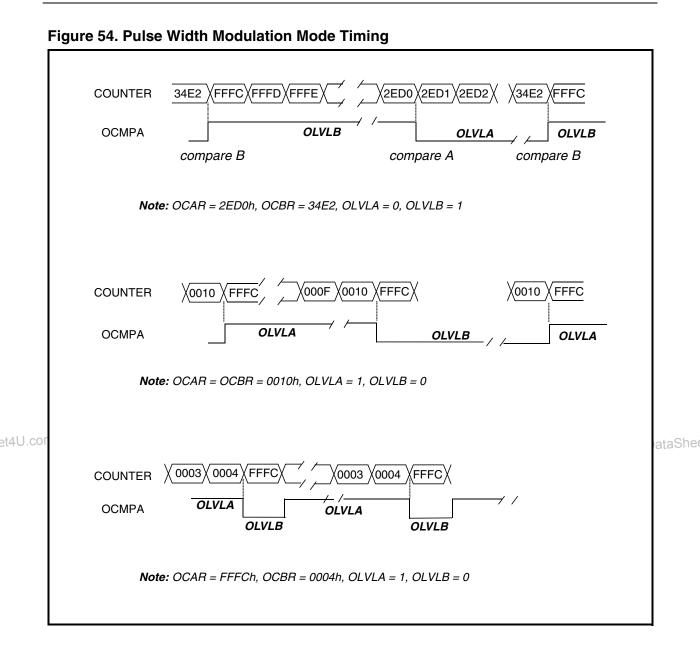

|         |       |        | Pulse Width Modulation Mode    |             |           |

|         |       |        | Pulse Width Modulation Input   |             |           |

|         |       | -      |                                |             |           |

| -       |       |        |                                |             |           |

| 2       |       |        | LOG/DIGITAL CONVERTER (ADC)    |             |           |

|         | 22.1  | Intro  | duction                        | 332         |           |

|         |       |        |                                | w DataChast | 411 a a m |

DataSheet4U.com

\_

| 22.2        | 2 Main Features                              | 332             |     |

|-------------|----------------------------------------------|-----------------|-----|

| 22.3        | 3 Functional Description                     | 332             |     |

|             | 22.3.1 Normal (Round-Robin) Operation of ADC | 333             |     |

|             | 22.3.2 Single-Channel Operation              | 333             |     |

|             | 22.3.3 Low-rate operating mode               | 333             |     |

|             | 22.3.4 Interrupt and DMA Requests            | 333             |     |

|             | 22.3.5 Clock Timing                          |                 |     |

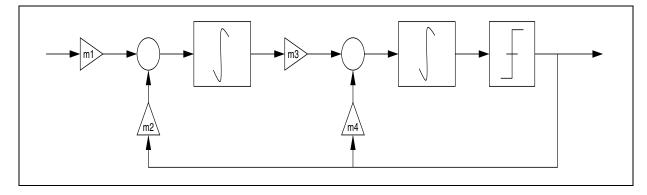

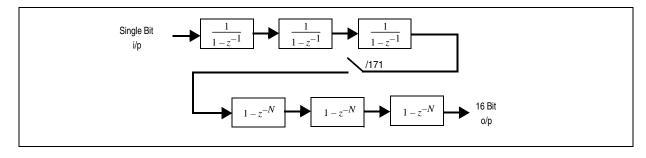

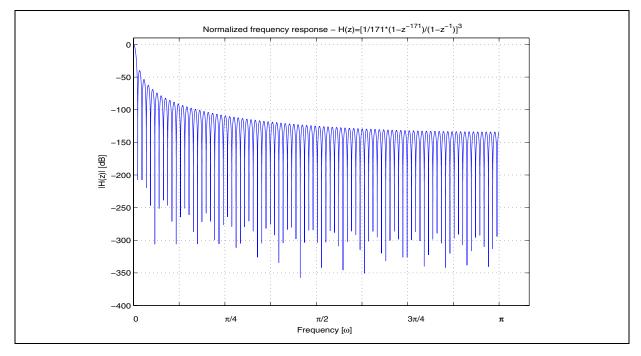

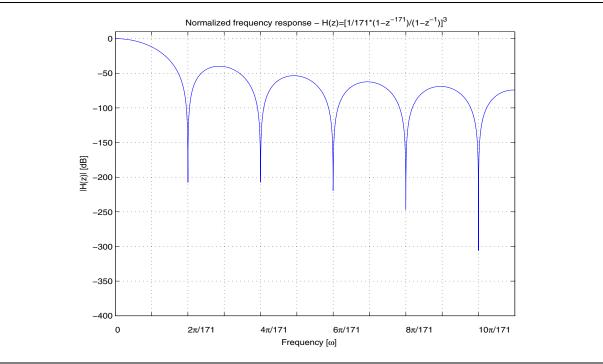

|             | 22.3.6 S-D Modulator                         |                 |     |

|             | 22.3.7 The Sinc3 Decimation Filter           |                 |     |

|             | 22.3.8 Bandgap Reference                     |                 |     |

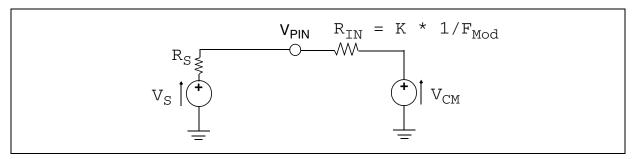

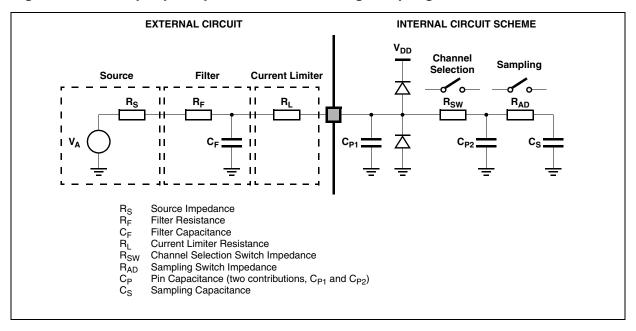

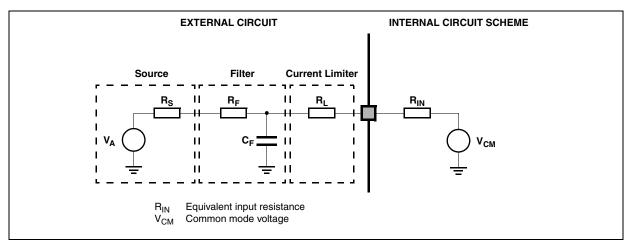

|             | 22.3.9 ADC Input Equivalent Circuit          |                 |     |

|             | 22.3.10ADC Output Coding                     |                 |     |

|             | 22.3.11Power Saving Features                 |                 |     |

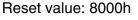

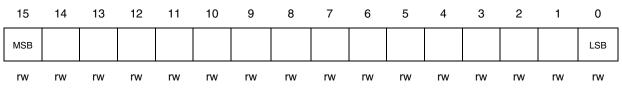

| 22.4        | 4 Register description                       |                 |     |

|             | 22.4.1 Register map                          |                 |     |

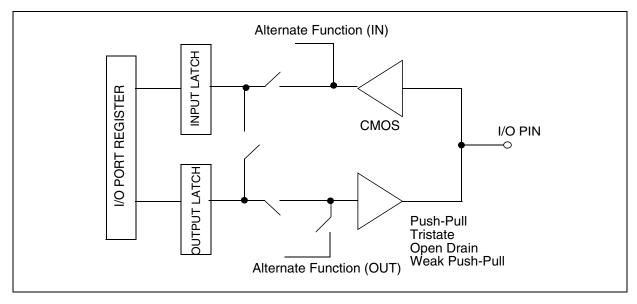

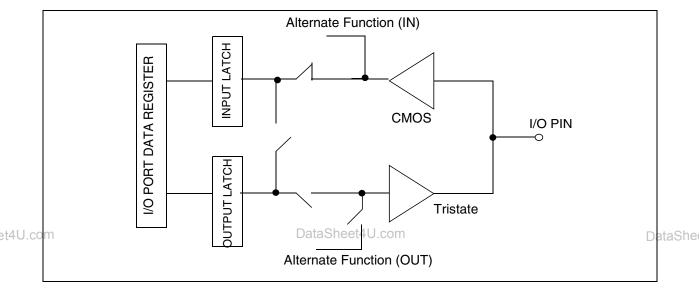

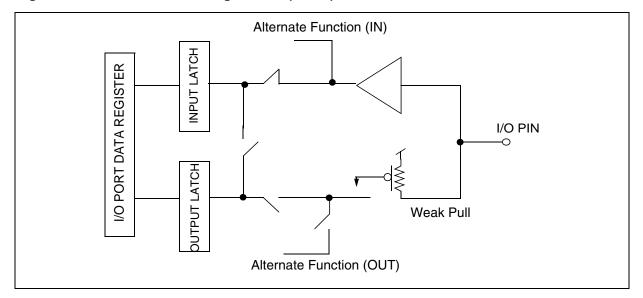

| 23 GE       | ENERAL PURPOSE I/O PORTS                     | 343             |     |

| 23.         | 1 Introduction                               | 343             |     |

| 23.2        | 2 Main Features                              | 343             |     |

| 23.3        | 3 Functional Description                     | 343             |     |

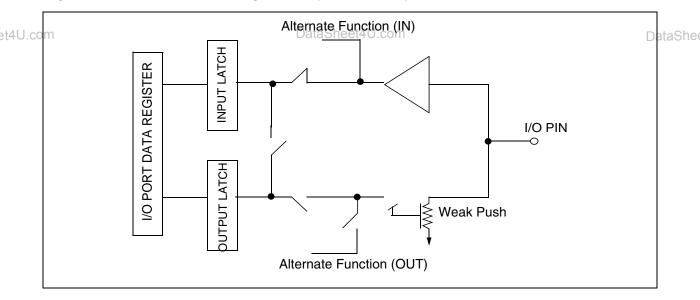

|             | 23.3.1 Input Configuration                   |                 |     |

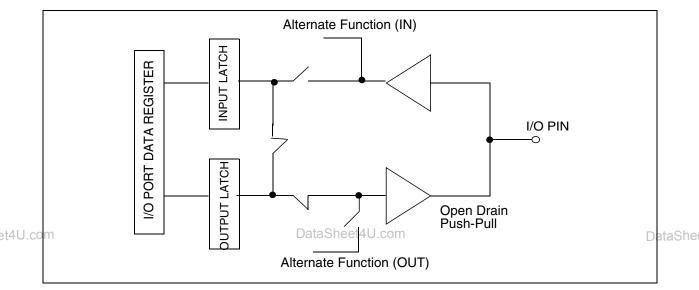

| et4U.co     | 23.3.2 Bidirectional Configuration           | ala             | She |

|             | 23.3.3 Output Configuration                  |                 |     |

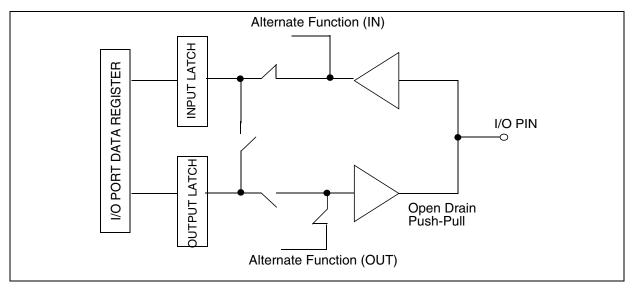

|             | 23.3.4 Alternate Function Configuration      |                 |     |

| 23.4        | 4 Register description                       |                 |     |

|             | 23.4.1 Register map                          |                 |     |

| 24 MI       | SCELLANEA REGISTERS (GCR - CGC - AHB_ERR)    | 351             |     |

| 24.         | 1 Introduction                               | 351             |     |

| 24.2        | 2 A-GCR Block description                    | 351             |     |

|             | 3 S-GCR Block description                    |                 |     |

|             | 4 CGC Block description                      |                 |     |

| 24.         | 5 AHB Error detection block description      |                 |     |

|             | 24.5.1 Register map                          |                 |     |

| 25 PC       | OWER REDUCTION MODES                         | 364             |     |

| 25.         | 1 RUN Mode                                   | 364             |     |

| 25.2        | 2 IDLE Mode                                  | 367             |     |

| 25.3        | 3 SLOW Mode                                  | 367             |     |

| 25.4        | 4 STOP Mode                                  | 368             |     |

| 25.         | 5 STANDBY Mode                               | 369             |     |

| 26 SY       | STEM RESET                                   | 370             |     |

| 26.         | 1 RESET Input Pin                            | 370             |     |

| DataSheet4U | com www                                      | I.DataSheet4U.c | om  |

57

\_\_\_\_

| 26.2 RTCRST Input Pin                                                                                                                                                                                                                    |  |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| 26.3 JTRST Input Pin                                                                                                                                                                                                                     |  |

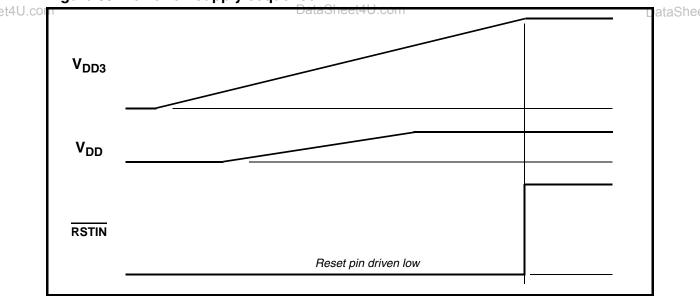

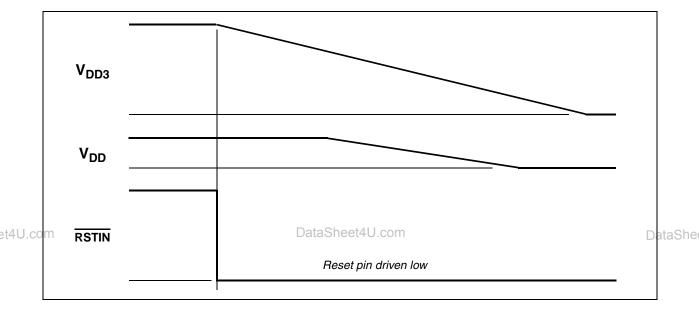

| 26.4 Power-on/off and Stand-by entry/exit                                                                                                                                                                                                |  |

| 27 PACKAGE MECHANICAL DATA                                                                                                                                                                                                               |  |

| 28 ELECTRICAL CHARACTERISTICS                                                                                                                                                                                                            |  |

| 28.1 Parameter Conditions                                                                                                                                                                                                                |  |

| 28.1.1 Minimum and Maximum values                                                                                                                                                                                                        |  |

| 28.1.2 Typical values                                                                                                                                                                                                                    |  |

| 28.1.3 Typical curves                                                                                                                                                                                                                    |  |

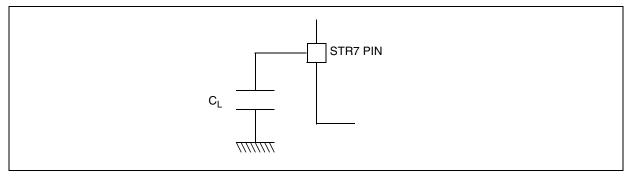

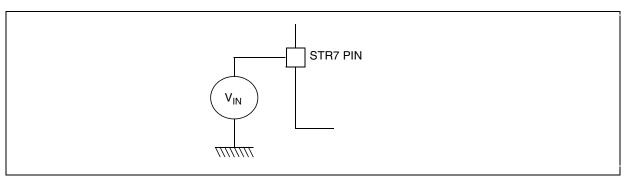

| 28.1.4 Loading capacitor                                                                                                                                                                                                                 |  |

| 28.1.5 Pin input voltage                                                                                                                                                                                                                 |  |

| 28.2 Absolute maximum ratings                                                                                                                                                                                                            |  |

| 28.3 Electrical sensitivity 376                                                                                                                                                                                                          |  |

| 28.3.1 Electro-Static Discharge (ESD)                                                                                                                                                                                                    |  |

| 28.3.2 Static Latch-Up (LU)                                                                                                                                                                                                              |  |

| 28.4 Operating conditions                                                                                                                                                                                                                |  |

| 28.5 Thermal characteristics                                                                                                                                                                                                             |  |

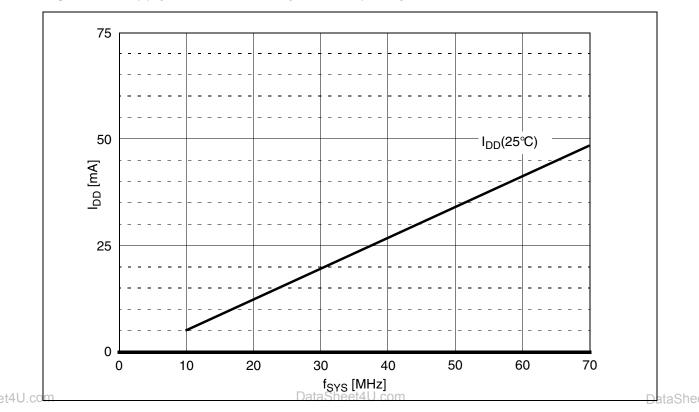

| 28.6 Supply Current Characteristics                                                                                                                                                                                                      |  |

| 28.7 Clock and Timing Characteristics                                                                                                                                                                                                    |  |

| 28.7.1 Internal clock characteristics                                                                                                                                                                                                    |  |

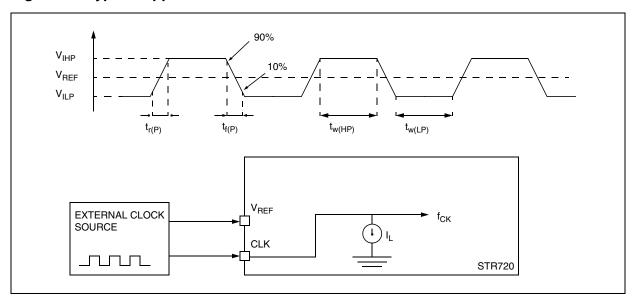

| t4U.co 28.7.2 CLK pad characteristics (External Clock Source)                                                                                                                                                                            |  |

| 28.7.3 PLL Characteristics                                                                                                                                                                                                               |  |

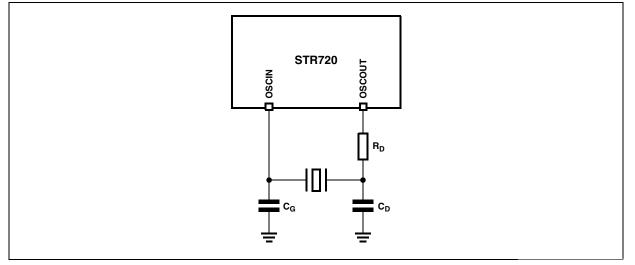

| 28.7.4 32 kHz Real-Time Clock Oscillator                                                                                                                                                                                                 |  |

| 28.8 AC and DC characteristics                                                                                                                                                                                                           |  |

| 29.0 Asymphysical Depart Input Characteristics 206                                                                                                                                                                                       |  |

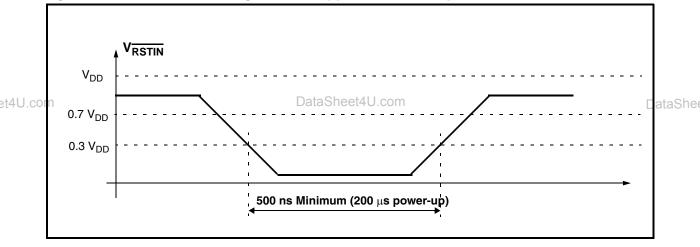

| 28.9 Asynchronous Reset Input Characteristics                                                                                                                                                                                            |  |

| 28.10 USB - Universal Bus Interface                                                                                                                                                                                                      |  |

| 28.10 USB - Universal Bus Interface38728.11 S-D ADC characteristics389                                                                                                                                                                   |  |

| 28.10 USB - Universal Bus Interface       387         28.11 S-D ADC characteristics       389         28.11.1ADC analog input pins       389                                                                                             |  |

| 28.10 USB - Universal Bus Interface38728.11 S-D ADC characteristics38928.11.1ADC analog input pins38928.11.2ADC performance392                                                                                                           |  |

| 28.10 USB - Universal Bus Interface       387         28.11 S-D ADC characteristics       389         28.11.1ADC analog input pins       389         28.11.2ADC performance       392         28.12 External Memory Bus Timing       393 |  |

| 28.10 USB - Universal Bus Interface38728.11 S-D ADC characteristics38928.11.1ADC analog input pins38928.11.2ADC performance392                                                                                                           |  |

DataSheet4U.com

#### **STR720 - INTRODUCTION**

# **1 INTRODUCTION**

STR720 is an STMicroelectronics new generation super-integrated single-chip device. It combines the high performance of ARM720T<sup>TM</sup> CPU microprocessor (revision 3) with high peripheral functionalities and enhanced I/O capabilities. It also provides on-chip high-speed RAM, clock generation via PLL and several embedded custom digital logics. STR720 is software compatible with the ARM processor family.

It is built using 0.18  $\mu m$  HCMOS8 process, with 1.8 V internal logic voltage and 3.3 V capable I/O lines.

The ARM720T<sup>TM</sup> is a member of the Advanced RISC Machines (ARM) family of general purpose 32-bit microprocessors combining in a single chip an 8 KByte cache, an enlarged write buffer, and a Memory Management Unit (MMU).

The ARM720T<sup>™</sup> belongs to the ARM7 family, making it software-compatible with all the ARM processors.

The ARM architecture is based on Reduced Instruction Set Computer (RISC) principles: its instruction set and related decode mechanism are much simpler than those of micro-programmed Complex Instruction Set Computers (CISC). This simplicity results in a high instruction throughput and impressive real-time interrupt response from a small and cost-effective chip.

The on-chip mixed data and instruction cache, together with the write buffer, substantially rise at4U.cothe average execution speed and reduce the average amount of memory bandwidth required by the processor. This allows the external memory to support Direct Memory Access (DMA) channels with minimal performance loss.

The MMU supports a conventional two-level, page-table structure and a number of extensions that make it ideal for embedded control, UNIX, and object-oriented systems. The allocation of virtual addresses with different task IDs improve performance in task switching operations with the cache enabled. These relocated virtual addresses are monitored by the Embedded-ICE block.

The memory interface is designed to allow the performance potential to be realized without incurring high costs in the memory system. Speed-critical control signals are pipelined to allow system control functions to be implemented in standard low-power logic, and these control signals facilitate the exploitation of the fast local access modes offered by industry-standard DRAMs.

For more information on the ARM720T core please refer to the ARM720T Rev 3 Technical Reference Manual.

DataSheet4U.com

10/401

# **Related Documents:**

#### Available from www.arm.com:

ARM720T (Rev 3) Technical Reference Manual

# 2 ACRONYMS

- ADC Analog to Digital Converter

- AHB Advanced High-performance Bus

- APB **Advanced Peripheral Bus**

- CPU Central Processing Unit

- DMA **Direct Memory Access**

- EIC Enhanced Interrupt Controller

- EFT **Extended Function Timer**

- EMI External Memory Interface

- GCR **Global Configuration Register**

- ICE In-Circuit Emulator

- IRQ Interrupt ReQuest

- JTAG Joint Test Access Group (IEEE 1149.1 Standard)

- PLL Phase-Locked Loop

- RAM Random Access Memory

- et4U.co∎n ROM Read-Only Memory

- RCCU **Reset and Clock Control Unit**

- RISC Reduced Instruction Set Computing

- SPI Serial Peripheral Interface

- BSPI **Buffered SPI**

- UART Universal Asynchronous Receiver Transmitter

- WDG Watch-Dog Unit

- WIU Wake-up/Interrupt Unit

**[**]

www.DataSheet4U.com

DataShe

# STR720 - ACRONYMS

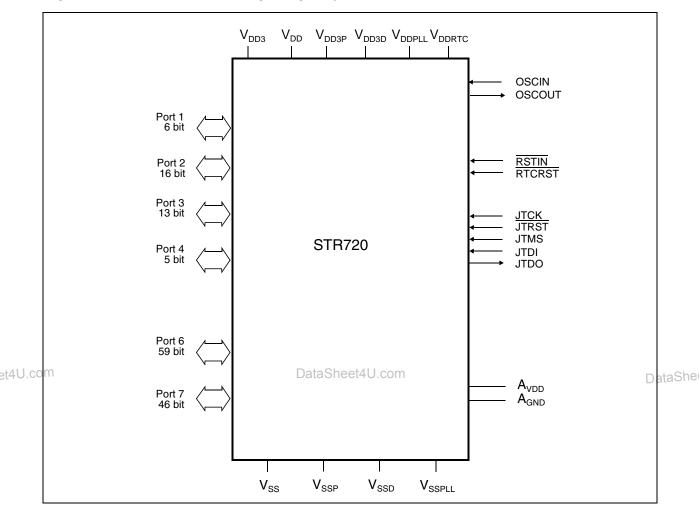

Please refer to Figure 1 for an overview of the device interfaces.

#### Figure 1. STR720 PQFP Package Logic Symbol

DataSheet4U.com

12/401

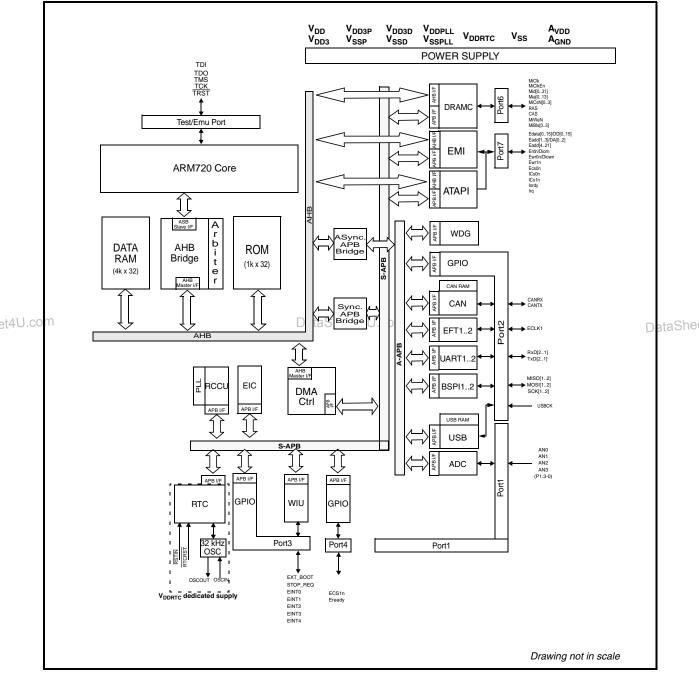

# **3 SYSTEM BLOCK DIAGRAM**

The Figure 2: STR720 Block Diagram on page 13 gives an overview of the complete STR720 microcontroller, showing how ARM720T processor and their peripherals are interfaced.

# Figure 2. STR720 Block Diagram

DataSheet4U.com

# STR720 - PIN DATA

# 4 PIN DATA

In the following tables, pin information are reported, including alternate function mapping and reference to package pin out.

#### 4.1 Power Supply pins

#### **Table 2. Power Supply Pins**

| Symbol             | Pin      | I/O | Function                                                       |      |

|--------------------|----------|-----|----------------------------------------------------------------|------|

| V <sub>DD3</sub>   | Note1    | -   | 3.3V Digital Supply Voltage for the I/O pads.                  |      |

| V <sub>DD</sub>    | Note2    | -   | 1.8V Digital Supply Voltage for core circuitry.                |      |

| V <sub>DD3P</sub>  | 22       | -   | 3.3V Supply Voltage.                                           |      |

| V <sub>SSP</sub>   | 23       | -   | Ground Voltage.                                                |      |

|                    | 24<br>30 | -   | Reserved, must be tied to GND.                                 |      |

|                    | 29<br>31 | -   | Reserved, must be tied to GND.                                 |      |

| V <sub>DDPLL</sub> | 121      | -   | 1.8 V Supply Voltage for internal PLL.                         |      |

| V <sub>SSPLL</sub> | 120      | -   | Ground Voltage for internal PLL.                               |      |

| V <sub>DDRTC</sub> | 159      | -   | 1.8V Digital Supply Voltage for RTC logic.                     |      |

| V <sub>SS</sub>    | Note3    | -   | Digital Ground.                                                |      |

| Avdd               | 32       | -   | Reference voltage for the on-chip A/D Converter (+3.0V/+3.6V). | Data |

| A <sub>GND</sub>   | 37       | -   | Reference ground for the on-chip A/D Converter.                |      |

|                    | 28       | -   | Reserved, must be tied to GND.                                 |      |

|                    | 26       | -   | Reserved, must be left floating.                               |      |

Note1: 16 Pins (1,10,46,55,66,75,84,93,103,113,129,143,163,180,196) are  $V_{DD3}$  (3.3 supply).

Note2: 3 Pins (8,59,140) are  $V_{DD}$  (1.8 supply).

Note3: 19 Pins (2,9,11,47,56,60,67,76,85,94,104,114,130,141,142,162,181,197) are  $V_{SS}$  (ground).

### 4.2 Global Pins

In Table 3 clock, reset and configuration pins of the device are reported.

#### **Table 3. Global Pins**

| Symbol                    | Pin | I/O | Function                                                                                                                                                                                                                                                                                             |

|---------------------------|-----|-----|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| OSCIN                     | 160 | I   | Input of the 32 kHz oscillator amplifier and input of the internal clock generator for RTC and WDG alternate clocks.                                                                                                                                                                                 |

| OSCOUT                    | 161 | 0   | Output of the 32 kHz oscillator amplifier circuit.                                                                                                                                                                                                                                                   |

| RSTIN <sup>(Note 1)</sup> | 157 | I   | System RESET Input with Schmitt-Trigger characteristics.<br>A low level at this pin resets asynchronously the STR720 device, except the RTC logic.<br>This has to be driven low by an external pull-down resistor when V <sub>DDRTC</sub> is connected<br>and the rest of the device is not powered. |

**47/**

ataSheet4U.com

14/401

# Table 3. Global Pins

| Symbol                     | Pin | I/O | Function                                                                                                                  |

|----------------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------|

| RTCRST <sup>(Note 1)</sup> | 158 |     | RTC RESET Input with Schmitt-Trigger characteristics.<br>A low level at this pin asynchronously resets the RTC registers. |

Note1: The signal applied to this pin is internally filtered by an on-chip RC filter whose width can range from 50 ns to 500 ns.

### 4.3 JTAG pins

In Table 4 the pins related to the JTAG interface are listed.

#### Table 4. JTAG/Emu Pins

| Symbol         Pin         I/O         Function           JTDO         42         O         ARM720 JTAG Test Data Out. JTDO is a test data serial output signal use test instructions and data. |                                                                                       | Function                                                                                                 |                                                                                                                                                    |  |

|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------|--|

|                                                                                                                                                                                                 |                                                                                       | ARM720 JTAG Test Data Out. JTDO is a test data serial output signal used for test instructions and data. |                                                                                                                                                    |  |

| ЈТСК                                                                                                                                                                                            | 39 I ARM720 JTAG Test Clock. JTCK is a test input used to synchronize the JTAG logic. |                                                                                                          |                                                                                                                                                    |  |

| JTMS                                                                                                                                                                                            | 40                                                                                    | I                                                                                                        | ARM720 JTAG Test Mode Select. JTMS is an input signal used to sequence test controller's state machine. JTMS is sampled on the rising edge of JTCK |  |

| JTDI                                                                                                                                                                                            | 41                                                                                    | I                                                                                                        | ARM720 JTAG Test Data In. JTDI is test data serial input used for test instruand data. JTDI is sampled on the rising edge of JTCK.                 |  |

| UTRST (Note 1)                                                                                                                                                                                  |                                                                                       |                                                                                                          |                                                                                                                                                    |  |

Note1: The signal applied to this pin is internally filtered by an on-chip RC filter whose width can range from 50 ns to 500 ns.

### 4.4 Port 1 pins

Port 1 is an analog port connected to the 4 analog input channels of the on-chip A/D converter are available.

### Table 5. Port 1 Pins

| Symbol | Pin | I/O | Function                            |

|--------|-----|-----|-------------------------------------|

| P1.0   | 33  | Ι   | A/D. Analog Input Channel 0 (ANA0). |

| P1.1   | 34  | I   | A/D. Analog Input Channel 1 (ANA1). |

| P1.2   | 35  | Ι   | A/D. Analog Input Channel 2 (ANA2). |

| P1.3   | 36  | Ι   | A/D. Analog Input Channel 3 (ANA3). |

| P1.4   | 27  | 0   | Reserved.                           |

| P1.5   | 25  | 0   | Reserved.                           |

DataSheet4U.com

# STR720 - PIN DATA

#### 4.5 Port 2 pins

Port 2 consists of 16 bidirectional general purpose I/O pins. They are under ARM720 control through a configuration register, a data register and a direction register. These registers are read/write registers. Port lines can be individually configured as general purpose inputs, general purpose outputs or dedicated peripheral lines. The port can be read at any time: input lines return the pin level; output lines return the level of the output driver input. When written, the port stores the data in an internal register: it drives the pins only if they are configured as general purpose outputs. Port 2 outputs can be configured as push/pull or open drain drivers.

| Symbol | Pin | I/O | Function                                                    |  |

|--------|-----|-----|-------------------------------------------------------------|--|

| P2.0   | 122 | I/O | Port 2 General Purpose Input/Output data line 0.            |  |

|        |     | I   | UART1. Receive Data Input (RxD1).                           |  |

| P2.1   | 123 | I/O | Port 2 General Purpose Input/Output data line 1.            |  |

|        |     | 0   | UART1. Transmit Data Output (TxD1).                         |  |

| P2.2   | 124 | I/O | Port 2 General Purpose Input/Output data line 2.            |  |

|        |     | I   | UART2. Receive Data Input (RxD2).                           |  |

| P2.3   | 125 | I/O | Port 2 General Purpose Input/Output data line 3.            |  |

|        |     | 0   | UART2. Transmit Data Output (TxD2).                         |  |

| P2.4   | 126 | I/O | Port 2 General Purpose Input/Output data line 4.            |  |

| m      |     | I   | BSPI1. Master Mode. Master Input/Slave Output line (MISO1). |  |

|        |     | 0   | BSPI1. Slave Mode. Master Input/Slave Output line (MISO1).  |  |

| P2.5   | 127 | I/O | Port 2 General Purpose Input/Output data line 5.            |  |

|        |     | 0   | BSPI1. Master Mode. Master Output/Slave Input line (MOSI1). |  |

|        |     | I   | BSPI1. Slave Mode. Master Output/Slave Input line (MOSI1).  |  |

| P2.6   | 128 | I/O | Port 2 General Purpose Input/Output data line 6.            |  |

|        |     | 0   | BSPI1. Master Mode. Output serial clock (SCK1).             |  |

|        |     | I   | BSPI1. Slave Mode. Input serial clock (SCK1).               |  |

| P2.7   | 131 | I/O | Port 2 General Purpose Input/Output data line 7.            |  |

|        |     | I   | BSPI2. Master Mode. Master Input/Slave Output line (MISO2). |  |

|        |     | 0   | BSPI2. Slave Mode. Master Input/Slave Output line (MISO2).  |  |

| P2.8   | 132 | I/O | Port 2 General Purpose Input/Output data line 8.            |  |

|        |     | 0   | BSPI2. Master Mode. Master Output/Slave Input line (MOSI2). |  |

|        |     | I   | BSPI2. Slave Mode. Master Output/Slave Input line (MOSI2).  |  |

| P2.9   | 133 | I/O | Port 2 General Purpose Input/Output data line 9.            |  |

BSPI2. Master Mode. Output serial clock (SCK2).

BSPI2. Slave Mode. Input serial clock (SCK2).

16/401

0

L

www.DataSheet4U.com

DataShe

| Table 0. Fort 2 Firs (Continued) |     |     |                                                                                                                                             |  |

|----------------------------------|-----|-----|---------------------------------------------------------------------------------------------------------------------------------------------|--|

| Symbol                           | Pin | I/O | Function                                                                                                                                    |  |

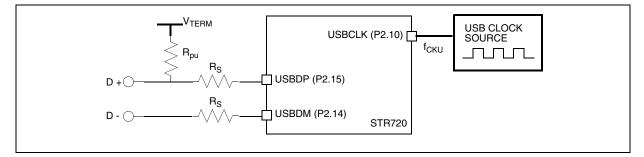

| P2.10                            | 134 | I/O | Port 2 General Purpose Input/Output data line 10.                                                                                           |  |

|                                  |     | I   | USB. USB interface 48 MHz clock input (USBCK).                                                                                              |  |

| P2.11                            | 135 | I/O | Port 2 General Purpose Input/Output data line 11.                                                                                           |  |

|                                  |     | I   | CAN. CAN module receive pin (CANRX).                                                                                                        |  |

| P2.12                            | 136 | I/O | Port 2 General Purpose Input/Output data line 12.                                                                                           |  |

|                                  |     | 0   | CAN. CAN module transmit pin (CANTX).                                                                                                       |  |

| P2.13                            | 137 | I/O | Port 2 General Purpose Input/Output data line 13.                                                                                           |  |

|                                  |     | I   | EFT1. Timer 1 External Clock Input line (ECLK1).                                                                                            |  |

| P2.14                            | 138 | I/O | Port 2 General Purpose Input/Output data line 14.                                                                                           |  |

|                                  |     | I/O | <i>USB</i> . USB interface D- signal <i>(USBDM</i> ). The usage of this alternate function require a special programming of GPIO registers. |  |

| P2.15                            | 139 | I/O | Port 2 General Purpose Input/Output data line 15.                                                                                           |  |

|                                  |     | I/O | USB. USB interface D+ signal (USBDP). The usage of this alternate function require a special programming of GPIO registers.                 |  |

|                                  |     |     |                                                                                                                                             |  |

#### Table 6. Port 2 Pins (Continued)

# 4.6 Port 3 pins

Port 3 consists of 13 bidirectional general purpose I/O pins. They are controlled through a configuration register, a data register and a direction register. These registers are read/write registers. Port lines can be individually configured as general purpose inputs, general purpose outputs or dedicated peripheral lines. The port can be read at any time: input lines return the pin level; output lines return the level of the output driver input. When written, the port stores the data in an internal register: it drives the pins only if they are configured as general purpose outputs. Port 3 outputs can be configured as push/pull or open drain drivers.

| Symbol | Pin | I/O | Function                                                                                       |

|--------|-----|-----|------------------------------------------------------------------------------------------------|

| P3.0   | 144 | I/O | Port 3 General Purpose Input/Output line 0.                                                    |

| P3.1   | 145 | I/O | Port 3 General Purpose Input/Output line 1.                                                    |

| P3.2   | 146 | I/O | Port 3 General Purpose Input/Output line 2.                                                    |

| P3.3   | 147 | I/O | Port 3 General Purpose Input/Output data line 3.                                               |

| P3.4   | 148 | I/O | Port 3 General Purpose Input/Output data line 4.                                               |

| P3.5   | 149 | I/O | Port 3 General Purpose Input/Output data line 5.                                               |

| P3.6   | 150 | I/O | Port 3 General Purpose Input/Output data line 6.                                               |

|        |     | I   | SYS <i>EXT_BOOT</i> . External boot mode selection. The state of this pin is sampled at reset. |

| P3.7   | 151 | I/O | Port 3 General Purpose Input/Output data line 7.                                               |

|        |     | 0   | WIU. Stop mode request, active low (STOP_REQ).                                                 |

### Table 7. Port 3 Pins

DataSheet4U.com

# STR720 - PIN DATA

| Symbol | Pin | I/O | Function                                          |

|--------|-----|-----|---------------------------------------------------|

| P3.8   | 152 | I/O | Port 3 General Purpose Input/Output data line 8.  |

|        |     | Ι   | External Interrupt 0 ( <i>EINT0</i> ).            |

| P3.9   | 153 | I/O | Port 3 General Purpose Input/Output data line 9.  |

|        |     | Ι   | External Interrupt 1( <i>EINT1</i> ).             |

|        |     | I   | BSPI1. Slave Mode. Slave select line (SS1).       |

| P3.10  | 154 | I/O | Port 3 General Purpose Input/Output data line 10. |

|        |     | I   | External Interrupt 2 ( <i>EINT2</i> ).            |

|        |     | Ι   | BSPI2. Slave Mode. Slave select line (SS2).       |

| P3.11  | 155 | I/O | Port 3 General Purpose Input/Output data line 11. |

|        |     | I   | External Interrupt 3 ( <i>EINT3</i> ).            |

|        |     | 0   | RCCU. PLL lock status (PLL_LOCK).                 |

| P3.12  | 156 | I/O | Port 3 General Purpose Input/Output data line 12. |

|        |     | Ι   | External Interrupt 4 ( <i>EINT4</i> ).            |

|        |     | Ι   | EFT2 Timer 2 Input Capture line B (ICAPB2).       |

#### Table 7. Port 3 Pins (Continued)

### 4.7 Port 4 pins

U.co Port 4 consists of 5 bidirectional general purpose I/O pins. They are under ARM720 control through a configuration register, a data register and a direction register. These registers are read/write registers. Port lines can be individually configured as general purpose inputs, general purpose outputs or dedicated peripheral lines. The port can be read at any time: input lines return the pin level; output lines return the level of the output driver input. When written, the port stores the data in an internal register: it drives the pins only if they are configured as general purpose outputs. Port 4 outputs can be configured as push/pull or open drain drivers.

#### Table 8. Port 4 Pins

| Symbol | Pin | I/O | Function                                         |

|--------|-----|-----|--------------------------------------------------|

| P4.0   | 16  | I/O | Port 4 General Purpose Input/Output data line 0. |

|        |     | I   | EMI External Ready signal (Eready).              |

| P4.1   | 15  | I/O | Port 4 General Purpose Input/Output data line 1. |

| P4.2   | 14  | I/O | Port 4 General Purpose Input/Output data line 2. |

| P4.3   | 13  | I/O | Port 4 General Purpose Input/Output data line 3. |

| P4.4   | 12  | I/O | Port 4 General Purpose Input/Output data line 4. |

|        |     | 0   | EMI active low Chip Select - bank 1 (Ecs1n).     |

DataSheet4U.com

18/401

| Symbol | Pin) | I/O | Function                                      |  |  |

|--------|------|-----|-----------------------------------------------|--|--|

| CLK    | 17   | I-P | This pin is used as main system clock source. |  |  |

|        | 18   | I-P | Reserved, must be tied to GND.                |  |  |

|        | 20   | I-P | Reserved, must be tied to GND.                |  |  |

|        | 21   | I-P | Reserved, must be tied to GND.                |  |  |

| VREF   | 19   | I   | CLK input reference voltage                   |  |  |

# 4.8 Main Clock input pins Table 9. Main Clock Input Pins

#### 4.9 Port 6 pins

Port 6 is a configurable 8/16/32-bit interface port used by the Synchronous DRAM memory interface. DRAMC is under STR720 control through configuration registers. Port lines are permanently assigned to the relevant pins and they are listed in the following table.

| Symbol | Pin | I/O | Function                             |       |

|--------|-----|-----|--------------------------------------|-------|

| P6.0   | 108 | I/O | SDRAM Data line 0 (Mid[0]).          |       |

| P6.1   | 107 | I/O | SDRAM Data line 1 (Mid[1]).          |       |

| P6.2   | 106 | I/O | SDRAM Data line 2 (Mid[2]).          |       |

| P6.3   | 105 | I/O | SDRAM Data line 3 ( <i>Mid[3]</i> ). | DataS |

| P6.4   | 102 | I/O | SDRAM Data line 4 (Mid[4]).          |       |

| P6.5   | 101 | I/O | SDRAM Data line 5 (Mid[5]).          |       |

| P6.6   | 100 | I/O | SDRAM Data line 6 (Mid[6]).          |       |

| P6.7   | 99  | I/O | SDRAM Data line 7 (Mid[7]).          |       |

| P6.8   | 118 | I/O | SDRAM Data line 8 (Mid[8]).          |       |

| P6.9   | 117 | I/O | SDRAM Data line 9 (Mid[9]).          |       |

| P6.10  | 116 | I/O | SDRAM Data line 10 (Mid[10]).        |       |

| P6.11  | 115 | I/O | SDRAM Data line 11 (Mid[11]).        |       |

| P6.12  | 112 | I/O | SDRAM Data line 12 (Mid[12]).        |       |

| P6.13  | 111 | I/O | SDRAM Data line 13 (Mid[13]).        |       |

| P6.14  | 110 | I/O | SDRAM Data line 14 (Mid[14]).        |       |

| P6.15  | 109 | I/O | SDRAM Data line 15 (Mid[15]).        |       |

| P6.16  | 53  | I/O | SDRAM Data line 16 (Mid[16]).        |       |

| P6.17  | 52  | I/O | SDRAM Data line 17 (Mid[17]).        |       |

| P6.18  | 51  | I/O | SDRAM Data line 18 (Mid[18]).        |       |

| P6.19  | 50  | I/O | SDRAM Data line 19 (Mid[19]).        |       |

| P6.20  | 49  | I/O | SDRAM Data line 20 (Mid[20]).        |       |

#### Table 10. Port 6 Pins

DataSheet4U.com

# STR720 - PIN DATA

# Table 10. Port 6 Pins (Continued)

| Symbol | Pin | I/O | Function                                          |      |

|--------|-----|-----|---------------------------------------------------|------|

| P6.21  | 48  | I/O | SDRAM Data line 21 (Mid[21]).                     |      |

| P6.22  | 45  | I/O | SDRAM Data line 22 (Mid[22]).                     |      |

| P6.23  | 44  | I/O | SDRAM Data line 23 (Mid[23]).                     |      |

| P6.24  | 65  | I/O | SDRAM Data line 24 (Mid[24]).                     |      |

| P6.25  | 64  | I/O | SDRAM Data line 25 (Mid[25]).                     |      |

| P6.26  | 63  | I/O | SDRAM Data line 26 (Mid[26]).                     |      |

| P6.27  | 62  | I/O | SDRAM Data line 27 (Mid[27]).                     |      |

| P6.28  | 61  | I/O | SDRAM Data line 28 (Mid[28]).                     |      |

| P6.29  | 58  | I/O | SDRAM Data line 29 ( <i>Mid[29]</i> ).            |      |

| P6.30  | 57  | I/O | SDRAM Data line 30 ( <i>Mid[30]</i> ).            |      |

| P6.31  | 54  | I/O | SDRAM Data line 31 (Mid[31]).                     |      |

| P6.32  | 83  | 0   | SDRAM Address line 0 (Mia[0]).                    |      |

| P6.33  | 82  | 0   | SDRAM Address line 1 (Mia[1]).                    |      |

| P6.34  | 81  | 0   | SDRAM Address line 2 (Mia[2]).                    |      |

| P6.35  | 80  | 0   | SDRAM Address line 3 (Mia[3]).                    |      |

| P6.36  | 79  | 0   | SDRAM Address line 4 (Mia[4]).                    |      |

| P6.37  | 78  | 0   | SDRAM Address line 5 (Mia[5]).                    |      |

| P6.38  | 77  | 0   | SDRAM Address line 6 (Mia[6]).                    | Data |

| P6.39  | 74  | 0   | SDRAM Address line 7 (Mia[7]).                    |      |

| P6.40  | 73  | 0   | SDRAM Address line 8 (Mia[8]).                    |      |

| P6.41  | 72  | 0   | SDRAM Address line 9 (Mia[9]).                    |      |

| P6.42  | 86  | 0   | SDRAM Address line 10 (Mia[10]).                  |      |

| P6.43  | 71  | 0   | SDRAM Address line 11 (Mia[11]).                  |      |

| P6.44  | 87  | 0   | SDRAM Address line 12 (Mia[12]).                  |      |

| P6.45  | 88  | 0   | SDRAM Address line 13 (Mia[13]).                  |      |

| P6.46  | N/A | N/A | Not implemented pin.                              |      |

| P6.47  | 69  | 0   | SDRAM Memory clock signal (MiClk).                |      |

| P6.48  | 70  | 0   | SDRAM Memory clock enable signal (MiClkEn).       |      |

| P6.49  | 89  | 0   | SDRAM active low Chip Select - bank 0 (MiCsN[0]). |      |

| P6.50  | 95  | 0   | SDRAM active low Chip Select - bank 1 (MiCsN[1]). |      |

| P6.51  | 97  | 0   | SDRAM active low Chip Select - bank 2 (MiCsN[2]). |      |

| P6.52  | 98  | 0   | SDRAM active low Chip Select - bank 3 (MiCsN[3]). |      |

| P6.53  | 90  | 0   | SDRAM active low Setup Active signal (RAS).       |      |

| P6.54  | 91  | 0   | SDRAM active low Access Active signal (CAS).      |      |

| P6.55  | 92  | 0   | SDRAM active low Write Enable signal (MiWeN).     |      |

DataSheet4U.com

20/401

| Symbol | Pin | I/O | Function                                               |

|--------|-----|-----|--------------------------------------------------------|

| P6.56  | 96  | 0   | SDRAM active low Byte Lane 0 Strobe signal (MiBls[0]). |

| P6.57  | 119 | 0   | SDRAM active low Byte Lane 1 Strobe signal (MiBls[1]). |

| P6.58  | 43  | 0   | SDRAM active low Byte Lane 2 Strobe signal (MiBls[2]). |

| P6.59  | 68  | 0   | SDRAM active low Byte Lane 3 Strobe signal (MiBls[3]). |

# Table 10. Port 6 Pins (Continued)

# 4.10 Port 7 pins

Port 7 is a configurable 8/16-bit data port shared between the External Memory Interface for the connection of memory components - such as ROM, FLASH or SRAM devices - and the IDE interface. Both EMI and IDE are under ARM720 control through configuration registers. Shared port lines can be selected by software using the related GCR register bit.

### Table 11. Port 7 Pins

| Symbol          | Pin | I/O | Function                                             |     |

|-----------------|-----|-----|------------------------------------------------------|-----|

| P7.0            | 194 | I/O | EMI Data line 0 (Edata[0]).                          |     |

|                 |     | I/O | IDE Data line 0 (IDD[0]).                            |     |

| P7.1            | 198 | I/O | EMI Data line 1 (Edata[1]).                          |     |

|                 |     | I/O | IDE Data line 1 (IDD[1]).                            |     |

| or <b>P</b> 7.2 | 200 | I/O | EMI Data line 2 (Edata[2]) et4U.com                  | Daʻ |

|                 |     | I/O | IDE Data line 2 (IDD[2]).                            |     |

| P7.3            | 202 | I/O | EMI Data line 3 (Edata[3]).                          |     |

|                 |     | I/O | IDE Data line 3 (IDD[3]).                            |     |

| P7.4            | 204 | I/O | EMI Data line 4 (Edata[4]).                          |     |

|                 |     | I/O | IDE Data line 4 (IDD[4]).                            |     |

| P7.5            | 206 | I/O | EMI Data line 5 (Edata[5]).                          |     |

|                 |     | I/O | IDE Data line 5 (IDD[5]).                            |     |

| P7.6            | 208 | I/O | EMI Data line 6 (Edata[6]).                          |     |

|                 |     | I/O | IDE Data line 6 (IDD[6]).                            |     |

| P7.7            | 4   | I/O | EMI Data line 7 (Edata[7]).                          |     |

|                 |     | I/O | IDE Data line 7 (IDD[7]).                            |     |

| P7.8            | 195 | I/O | EMI Data line 8 (Edata[8]).                          |     |

|                 |     | I/O | IDE Data line 8 (IDD[8]).                            |     |

| P7.9            | 199 | I/O | EMI Data line 9 (Edata[9]).                          |     |

|                 |     | I/O | IDE Data line 9 (IDD[9]).                            |     |

| P7.10           | 201 | I/O | EMI Data line 10 (Edata[10]).                        |     |

|                 |     | I/O | <i>IDE</i> Data line 10 ( <i>IDD[</i> 10 <i>]</i> ). |     |

DataSheet4U.com

# STR720 - PIN DATA

# Table 11. Port 7 Pins (Continued)

| Symbol        | Pin | I/O | Function                           |        |

|---------------|-----|-----|------------------------------------|--------|

| P7.11         | 203 | I/O | EMI Data line 11 (Edata[11]).      |        |

|               |     | I/O | IDE Data line 11 (IDD[11]).        |        |

| P7.12         | 205 | I/O | EMI Data line 12 (Edata[12]).      |        |

|               |     | I/O | IDE Data line 12 (IDD[12]).        |        |

| P7.13         | 207 | I/O | EMI Data line 13 (Edata[13]).      |        |

|               |     | I/O | IDE Data line 13 (IDD[13]).        |        |

| P7.14         | 3   | I/O | EMI Data line 14 (Edata[14]).      |        |

|               |     | I/O | IDE Data line 14 (IDD[14]).        |        |

| P7.15         | 5   | I/O | EMI Data line 15 (Edata[15]).      |        |

|               |     | I/O | IDE Data line 15 (IDD[15]).        |        |

| P7.16         | 168 | 0   | EMI Address line 0 (Eadd[0]).      |        |

|               |     | 0   | IDE Address line 0 (IDA[0]).       |        |

| P7.17         | 169 | 0   | EMI Address line 1 (Eadd[1]).      |        |

|               |     | 0   | IDE Address line 1 (IDA[1]).       |        |

| P7.18         | 170 | 0   | EMI Address line 2 (Eadd[2]).      |        |

|               |     | 0   | IDE Address line 2 (IDA[2]).       |        |

| <b>P</b> 7.19 | 191 | 0   | EMI Address line 3.(Eadd[3])4U.com | DataSl |

| P7.20         | 190 | 0   | EMI Address line 4 (Eadd[4]).      | 170100 |

| P7.21         | 189 | 0   | EMI Address line 5 (Eadd[5]).      |        |

| P7.22         | 188 | 0   | EMI Address line 6 (Eadd[6]).      |        |

| P7.23         | 187 | 0   | EMI Address line 7 (Eadd[7]).      |        |

| P7.24         | 178 | 0   | EMI Address line 8 (Eadd[8]).      |        |

| P7.25         | 177 | 0   | EMI Address line 9 (Eadd[9]).      |        |

| P7.26         | 176 | 0   | EMI Address line 10 (Eadd[10]).    |        |

| P7.27         | 175 | 0   | EMI Address line 11 (Eadd[11]).    |        |

| P7.28         | 174 | 0   | EMI Address line 12 (Eadd[12]).    |        |

| P7.29         | 173 | 0   | EMI Address line 13 (Eadd[13]).    |        |

| P7.30         | 172 | 0   | EMI Address line 14 (Eadd[14).     |        |

| P7.31         | 171 | 0   | EMI Address line 15 (Eadd[15]).    |        |

| P7.32         | 7   | 0   | EMI Address line 16 (Eadd[16]).    |        |

| P7.33         | 186 | 0   | EMI Address line 17 (Eadd[17]).    |        |

| P7.34         | 185 | 0   | EMI Address line 18 (Eadd[18]).    |        |

| P7.35         | 179 | 0   | EMI Address line 19 (Eadd[19]).    |        |

| P7.36         | 182 | 0   | EMI Address line 20 (Eadd[20]).    |        |

| P7.37         | 184 | 0   | EMI Address line 21 (Eadd[21]).    | 7      |

22/401

| Symbol | Pin | I/O | Function                                                                    |  |

|--------|-----|-----|-----------------------------------------------------------------------------|--|

| P7.38  | 193 | 0   | EMI active low External Read Strobe. (Erdn).                                |  |

|        |     | 0   | IDE active low Read strobe (IDiorn).                                        |  |

| P7.39  | 183 | 0   | EMI active low External Write Strobe, bits 7:0 of external memory (Ewr0n).  |  |

|        |     | 0   | IDE active low Write strobe (IDiown).                                       |  |

| P7.40  | 6   | 0   | EMI active low External Write Strobe, bits 15:8 of external memory (Ewr1n). |  |

| P7.41  | 192 | 0   | EMI active low Chip Select - bank 0 (Ecs0n).                                |  |

| P7.42  | 166 | 0   | IDE active low Chip select 0 (ICs0n).                                       |  |

| P7.43  | 167 | 0   | IDE active low Chip select 1 (ICs1n).                                       |  |

| P7.44  | 164 | Ι   | IDE Ready (Iordy).                                                          |  |

| P7.45  | 165 | I   | IDE Interrupt (Irq).                                                        |  |

#### Table 11. Port 7 Pins (Continued)

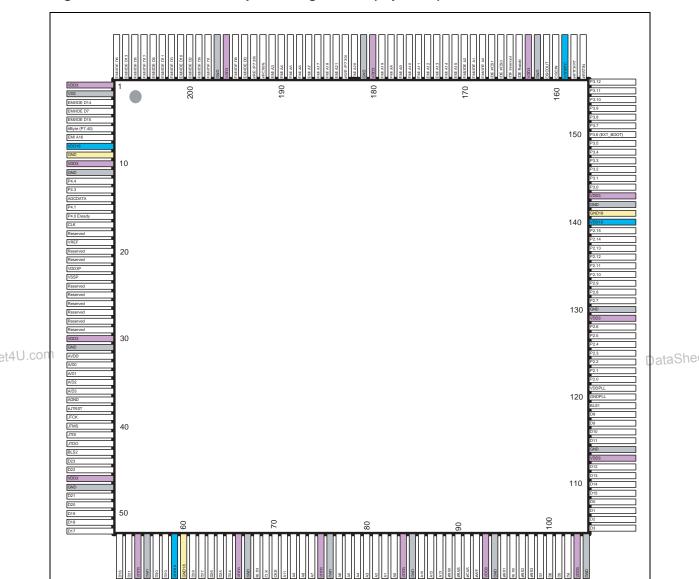

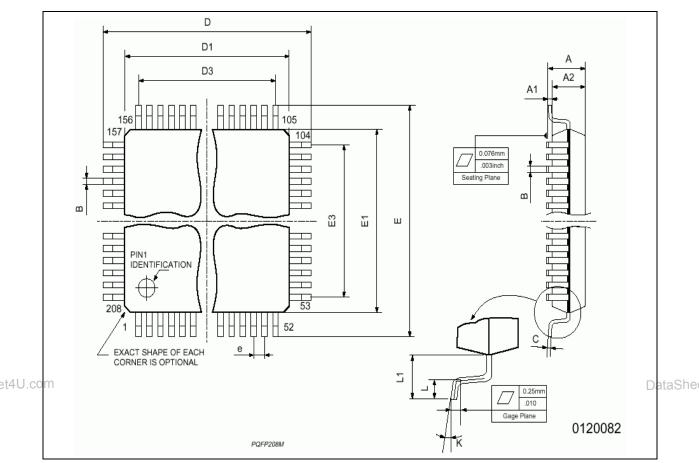

#### 4.11 PQFP208 Package Pin Configuration

The package used for STR720 device is a Plastic Quad-Flat Package supporting 208 pin. For a complete description of this package mechanical characteristics See "PACKAGE"

et4U.com

DataSheet4U.com

DataShe

DataSheet4U.com

57

23/401

# STR720 - PIN DATA

MECHANICAL DATA" on page 373. In the following drawing and table the device pin mapping is reported

# Figure 3. STR720 PQFP208 pin configuration (top view)

DataSheet4U.com

24/401

Table 12. STR720 PQFP208 pin map

|    | Pin | Symbol               | Pin | Symbol       | Pin               | Symbol     | Pin | Symbol            |          |

|----|-----|----------------------|-----|--------------|-------------------|------------|-----|-------------------|----------|

|    | 1   | VDD3                 | 53  | MID[16]      | 105               | MID[3]     | 157 | RSTIN_N           |          |

|    | 2   | VSS                  | 54  | MID[31]      | 106               | MID[2]     | 158 | RTCRST_N          |          |

|    | 3   | EDATA[14]<br>IDD[14] | 55  | VDD3         | 107               | MID[1]     | 159 | VDDRTC            |          |

|    | 4   | EDATA[7]<br>IDD[7]   | 56  | VSS          | 108               | MID[0]     | 160 | OSCIN             |          |

|    | 5   | EDATA[15]<br>IDD[15] | 57  | MID[30]      | 109               | MID[15]    | 161 | OSCOUT            |          |

|    | 6   | EWR1_N               | 58  | MID[29]      | 110               | MID[14]    | 162 | VSS               |          |

|    | 7   | EADD[16]             | 59  | VDD          | 111               | MID[13]    | 163 | VDD3              |          |

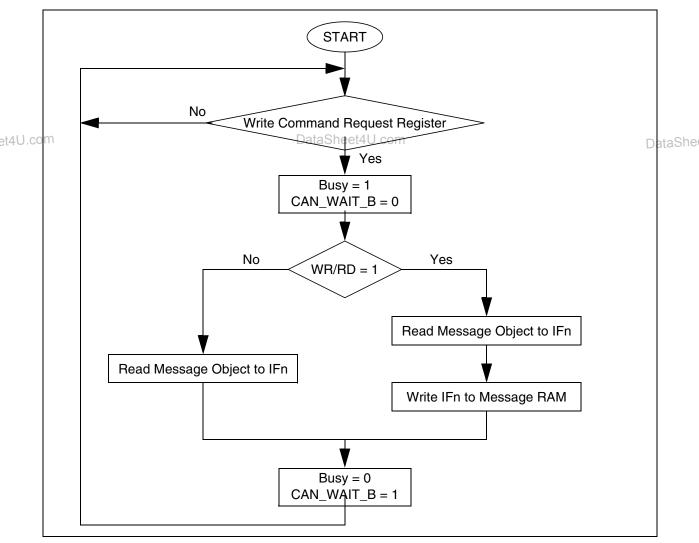

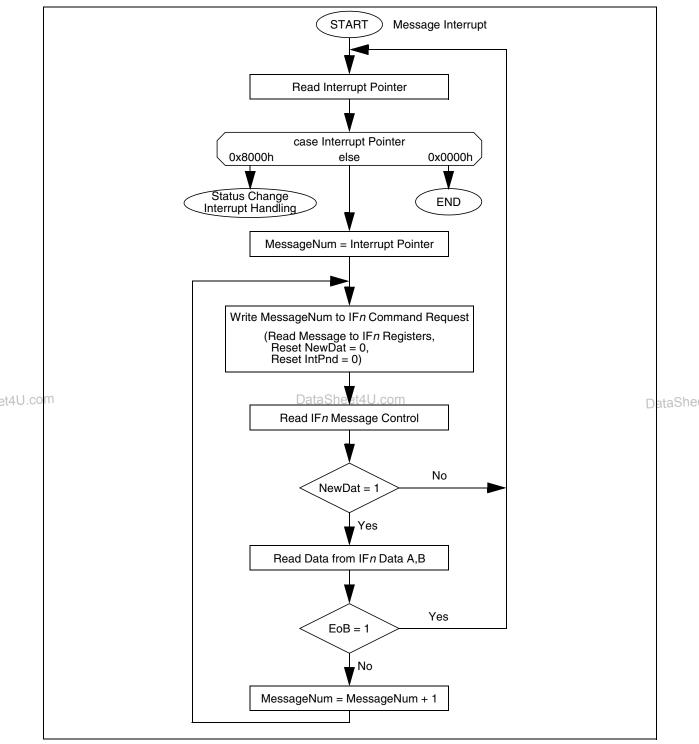

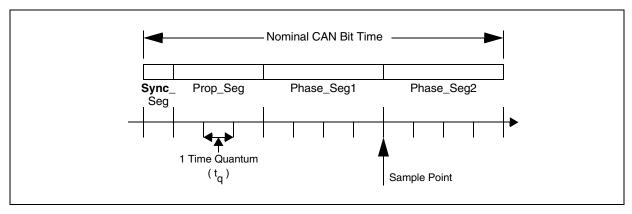

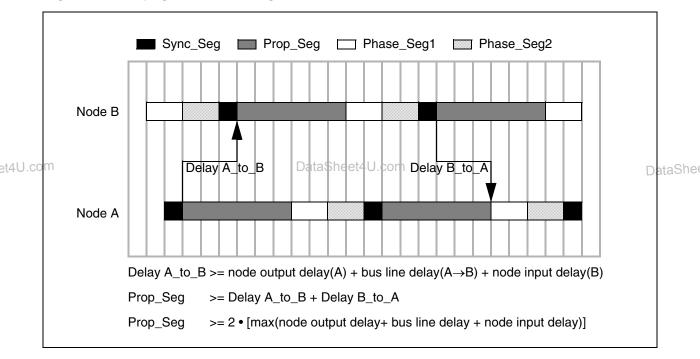

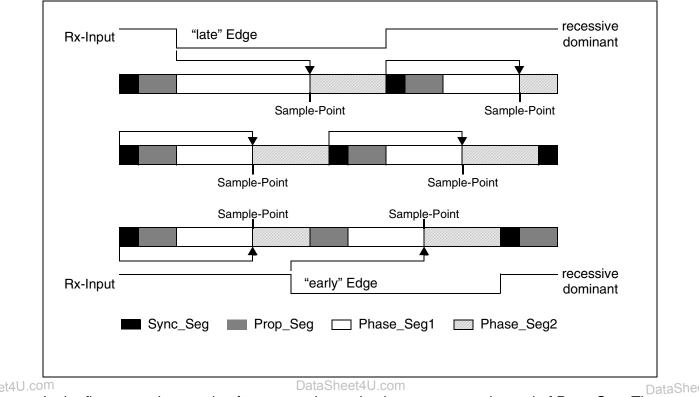

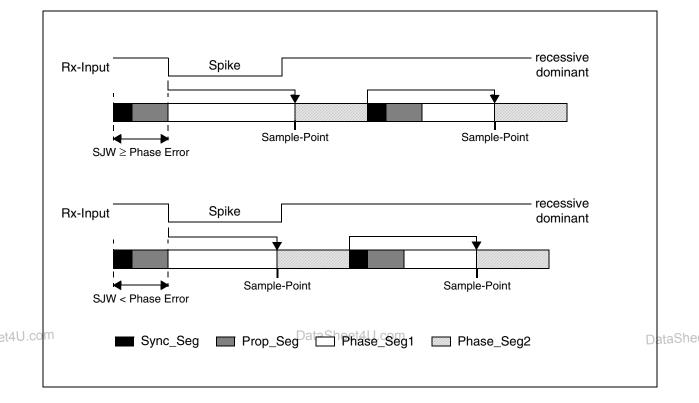

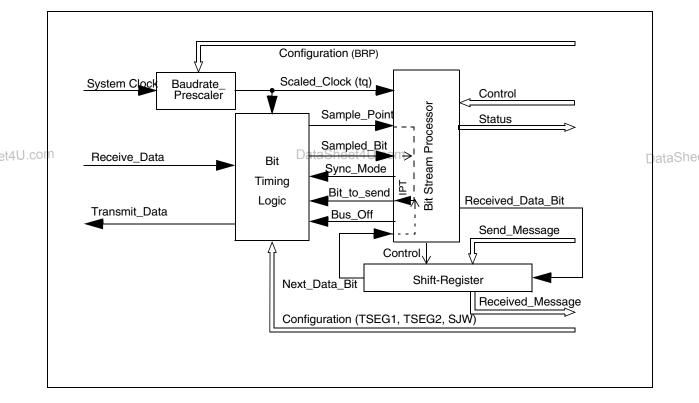

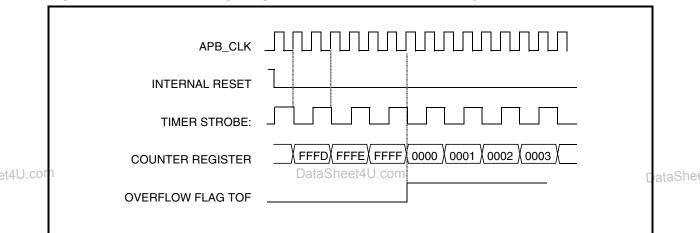

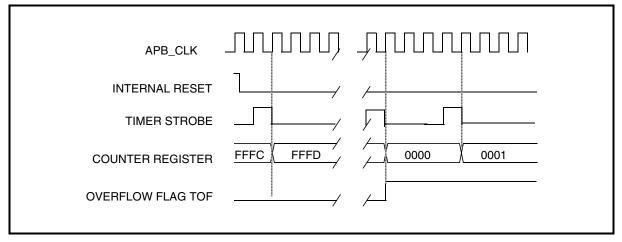

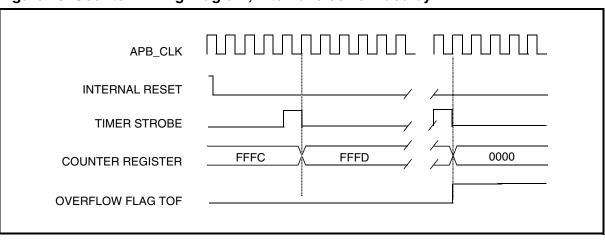

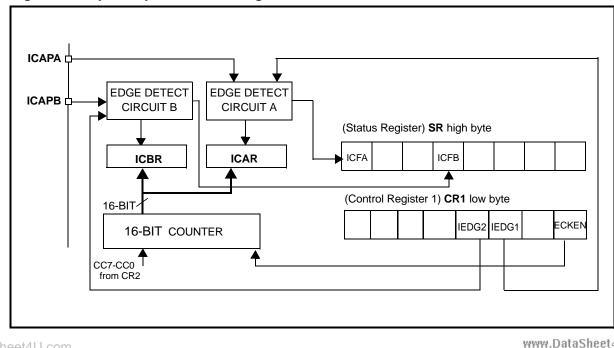

|    | 8   | VDD                  | 60  | VSS          | 112               | MID[12]    | 164 | IORDY             |          |