# STV3550

## LCD and Matrix Display TV Processor

DATASHEET

## Main Features

Fully-programmable Digital Video Output Stage for direct RGB interface to Flat Display Panel with 4- to 10-bit color resolution and pixel resolution from VGA to WXGA including HDTV2.

#### Versatile Integrated Up-Converter

- 50/60-Hz Progressive output with Line-Interpolation (A + A\*), Field-Merging (A + B) or with Motion-adaptive De-interlacing based on median f(A, B)

- Advanced Still Picture modes: AA\*AA\* and ABAB interlaced or AAAA non-interlaced

- Automatic Movie mode detection and scanning

#### Standard Definition Input

- ITU-R BT.656/601 Video Input

- Separate H/V inputs synchronous with input clock

- 3D Temporal Noise Reduction with Comet-effect Correction

- Movie Mode Detection with Motion Phase Recovery

- Scene-change Detector for Contrast Enhancer and Upconversion Control

- Letterbox Format Detection and Auto-Format Correction

#### High-Quality Video Display

- Picture Structure Improvement including Color Transition Improvement, Luma Peaking/Coring and Luma Contrast Enhancer

- H/V format conversion with Zoom In/Out (4x to 1/8x) with H/V decimation

- Letterbox and 4:3 to 16:9 format conversion with programmable 5-segment Panoramic mode

- Very flexible Sync Generator for Master and Slave modes by Vsync and Hsync signals generation

- Progressive Display mode (60 Hz, 50 Hz) for full-screen graphic planes

- Mosaic mode with up to 16 pictures displayed

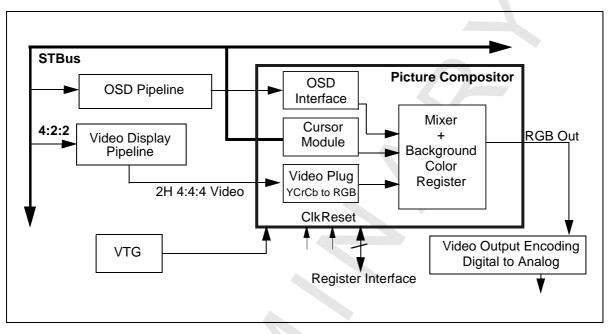

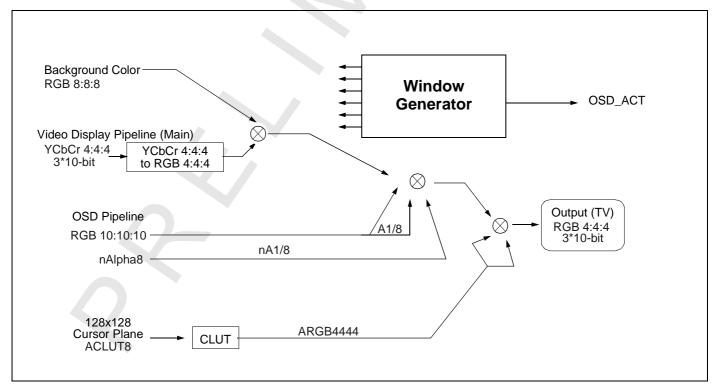

Picture Compositor to provide Transparency mode between Video and Graphic planes

#### High-Performance 8-bit Bitmap OSD Generator

- Pixel-based resolution with 10-bit RGB outputs

- Programmable Resolution up to WXGA, all standard displays are supported:

- Teletext 1.5 (480x520) and 2.5 (672x520)

- Double-page Teletext (960x520) with Picture-and-Text TeleWeb (640x480)

- 4 graphic planes with full alpha-blending capabilities: 24-bit Background Plane

- 10-bit RGB Video Plane

- Bitmap OSD Plane with Color Map

- Up to 128 x 128 pixel Cursor Plane

- 2D Graphics Accelerator

- Embedded 32-bit ST20 CPU Core

- Peripherals and I/Os for TV Chassis Control:

- 30 fully-programmable I/Os (5V tolerant)

- 4 external interrupts

- 8-bit programmable PWM with 4 inputs/outputs

- Infrared Digital Preprocessor

- Real Time Clock and Watchdog Timer

- 4 16-bit standard timers

- 10-bit ADC with 6 inputs and wake-up capability

- 2 Master/Slave I<sup>2</sup>C Bus Interfaces

- UART and support for IrDA interfaces

- Teletext 1.5 and 2.5, Closed-Caption, VPS and WSS VBI Data Decoding, TeleWeb Compliant

- Embedded Emulation Resources with In-Situ Flash Programming Capabilities

- 1.8V and 3.3V Power supplies

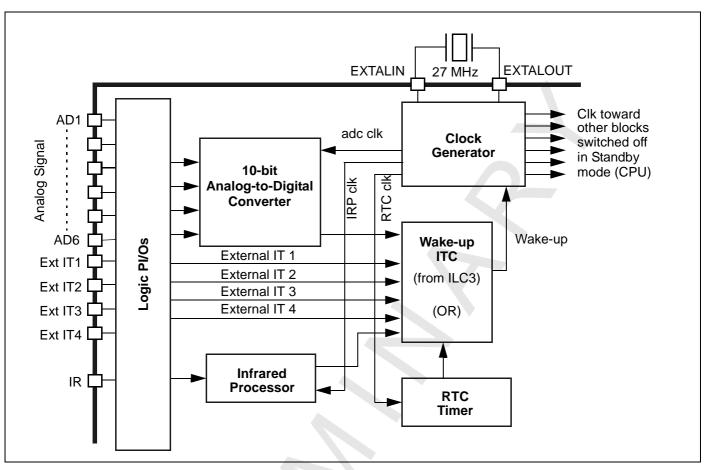

- Eco Standby mode

- 27-MHz Crystal Oscillator

- PC input compatible

www.DataSheet4U.com

Revision 1.3

#### DMS No. 03688M

This is preliminary information on a new product now in development. Details are subject to change without notice.

## STV3550

| Chapter 1 | General Information                                                                                                                                                                                                                                                                                                                                       | 7                                    |  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------|--|

| 1.1       | Introduction                                                                                                                                                                                                                                                                                                                                              | 7                                    |  |

| 1.2       | Software                                                                                                                                                                                                                                                                                                                                                  |                                      |  |

| 1.3       | Related Documentation         1.3.1       General Introduction Manual         1.3.2       User Guides         1.3.3       Reference Guide                                                                                                                                                                                                                 | 10<br>10                             |  |

| Chapter 2 | STV3550 Pin List                                                                                                                                                                                                                                                                                                                                          | 12                                   |  |

| 2.1       | Pinout                                                                                                                                                                                                                                                                                                                                                    |                                      |  |

| 2.2       | Pin Description                                                                                                                                                                                                                                                                                                                                           | 13                                   |  |

| 2.3       | Parallel I/O Pins and Alternate Functions                                                                                                                                                                                                                                                                                                                 | 19                                   |  |

| Chapter 3 | Video Functional Description                                                                                                                                                                                                                                                                                                                              | 20                                   |  |

| 3.1       | Standard Definition Input (SDIN)         3.1.1       System Description                                                                                                                                                                                                                                                                                   |                                      |  |

| 3.2       | Video Timebase Generator (VTG)         3.2.1       Synchronization Modes         3.2.2       Deinterlacing Modes and Progressive Scan Output         3.2.3       Regulation Modes                                                                                                                                                                         | 22<br>22                             |  |

| 3.3       | Video Display Pipeline         3.3.1       Main Features         3.3.2       Horizontal and Vertical Rescaling         3.3.3       Image Improvement         3.3.4       Brightness Estimator         3.3.5       Histogram         3.3.6       Contrast Enhancer         3.3.7       Spectral Processing         3.3.8       Color Transient Improvement | 25<br>27<br>28<br>28<br>28<br>28<br> |  |

| Chapter 4 | Graphics Functional Description                                                                                                                                                                                                                                                                                                                           | 37                                   |  |

| 4.1       | On-Screen Display Generator (OSD)         4.1.1       General Information         4.1.2       Main Features         4.1.3       Functional Description         4.1.4       Programming OSD Display Regions         4.1.5       Mixing OSD and Video Signals                                                                                               | 37<br>37<br>37<br>38                 |  |

| 4.2       | 2D Graphics Accelerator                                                                                                                                                                                                                                                                                                                                   | 49                                   |  |

| 4.3       | Graphic Application Examples         4.3.1       Teletext 1.5         4.3.2       Teletext Level 2.5         4.3.3       TeleWeb                                                                                                                                                                                                                          | 50<br>51                             |  |

| 4.4       | Picture Compositor                                                                                                                                                                                                                                                                                                                                        | 53                                   |  |

|           | 4.4.1 Background Color Plane                                       |    |

|-----------|--------------------------------------------------------------------|----|

|           | 4.4.2 Video Plane                                                  |    |

|           | 4.4.3 Cursor Plane                                                 |    |

|           | 4.4.4 Graphics Plane                                               | 54 |

| Chapter 5 | Output Stage                                                       | 56 |

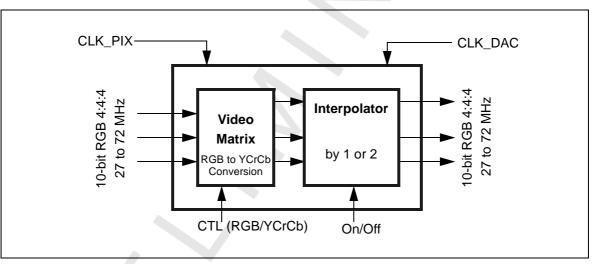

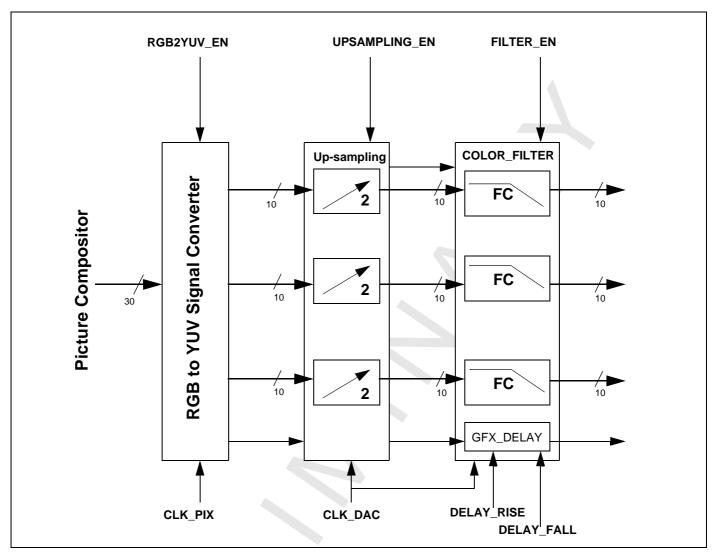

| 5.1       | Color Space Adaptor (CSA) and Interpolator                         |    |

| ••••      | 5.1.1 Main Features                                                |    |

|           | 5.1.2 General Description                                          |    |

|           | 5.1.3 Up-sampling                                                  |    |

|           | 5.1.4 GFX_ACTIVE Signal                                            |    |

| 5.2       | Gamma Correction                                                   |    |

| 5.3       | Perfect Color Engine                                               |    |

| 5.4       | Digital Video Output Stage                                         |    |

|           | 5.4.1 Introduction                                                 |    |

|           | 5.4.2 Vsync Output Capability                                      |    |

|           | 5.4.3 Hsync Output Capability                                      |    |

|           | 5.4.4 Csync Output Capability                                      |    |

|           | 5.4.5 RGB Output                                                   |    |

|           | 5.4.6 Data Enable Output                                           |    |

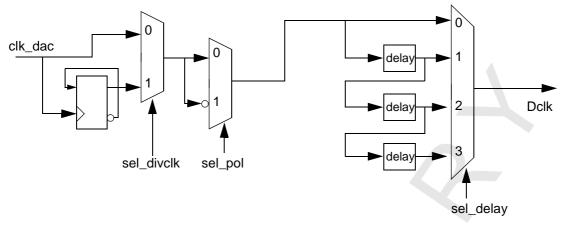

|           | 5.4.7 Data Clock Output                                            |    |

|           | 5.4.8 Pad Control                                                  |    |

|           | 5.4.9 Register                                                     | 65 |

|           |                                                                    |    |

| Chapter 6 | CPU and System Management Functional Description                   | 66 |

| 6.1       | ST20 C2C200 CPU Core                                               |    |

|           | 6.1.1 General Information                                          | 66 |

|           | 6.1.2 Main Features                                                | 66 |

| 6.2       | ST Bus Interconnect Overview                                       |    |

| 6.3       | STV3550 Memory Interface                                           | 66 |

|           | 6.3.1 Memory Devices                                               | 66 |

|           | 6.3.2 Configuring the STV3550 Memory Interface during Boot         | 67 |

|           | 6.3.3 Address Format                                               | 67 |

|           | 6.3.4 Control Registers                                            | 67 |

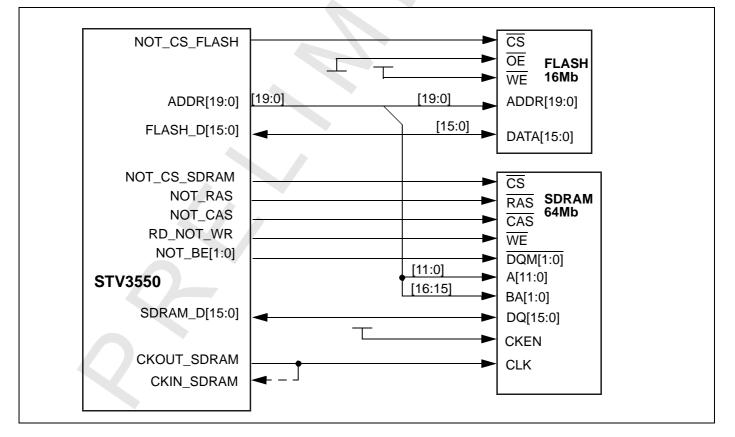

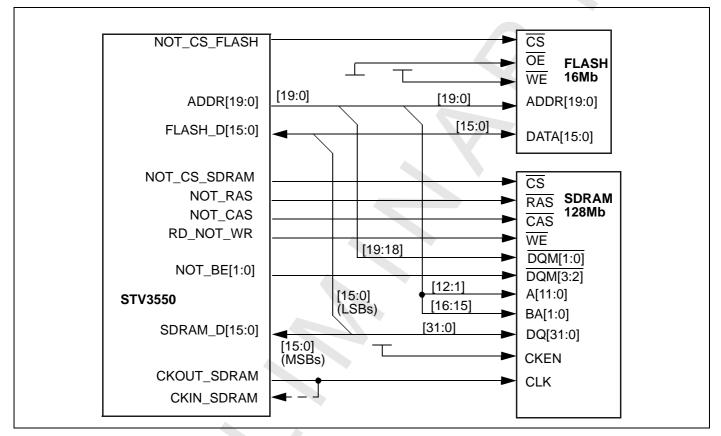

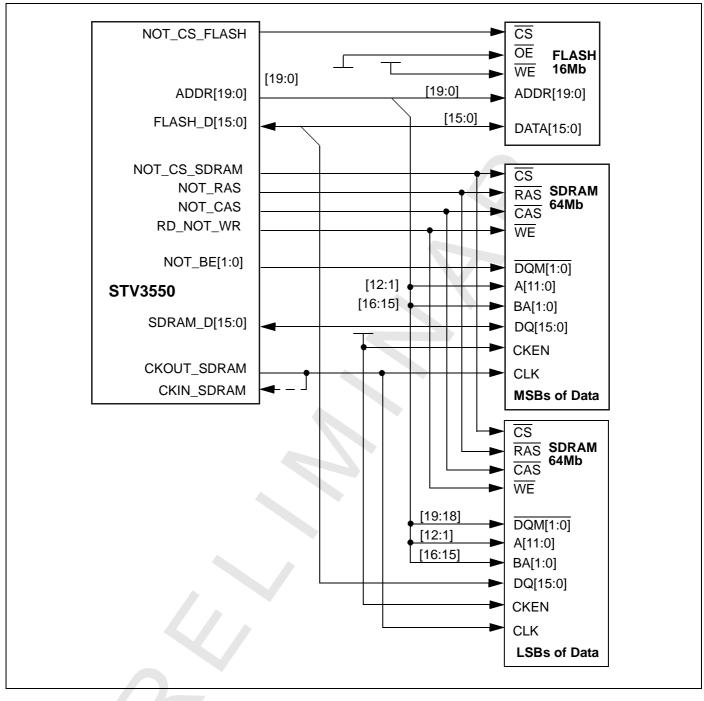

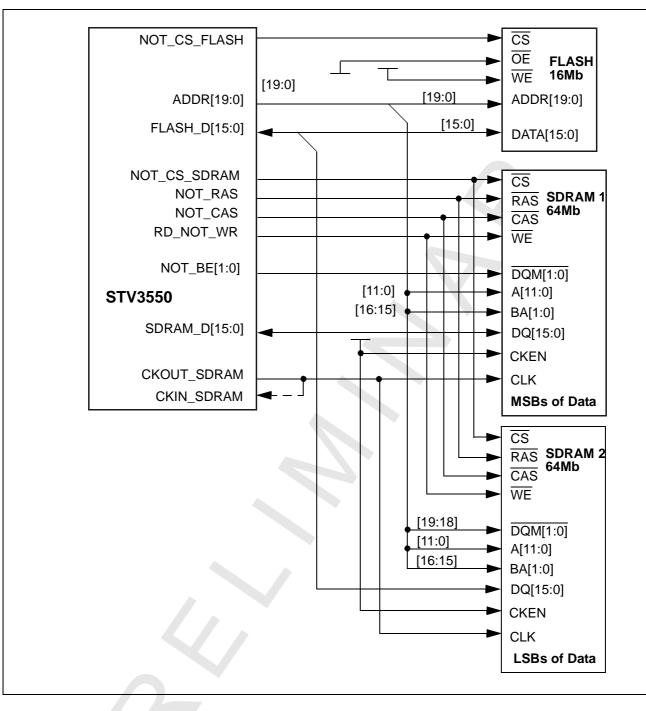

|           | 6.3.5 Memory Configurations                                        | 68 |

|           | 6.3.6 Clock Management and Timing Issues                           | 68 |

|           | 6.3.7 STV3550 Memory Interfaces                                    | 68 |

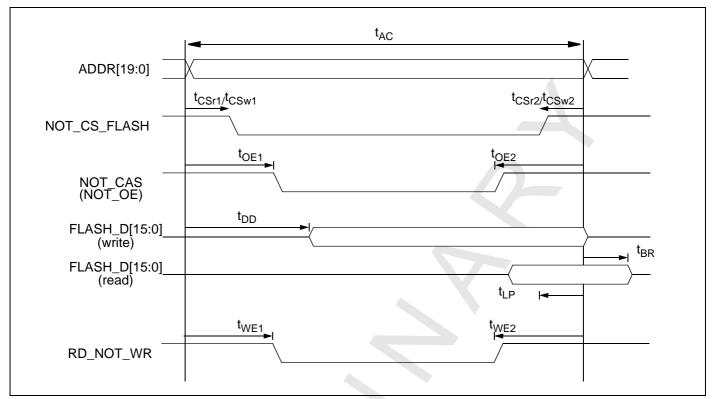

|           | 6.3.8 STV3550 Memory Interface Capabilities Regarding Flash Device | 69 |

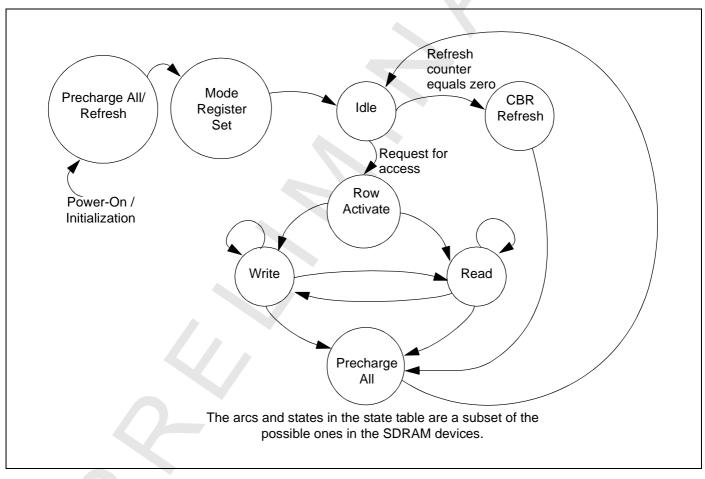

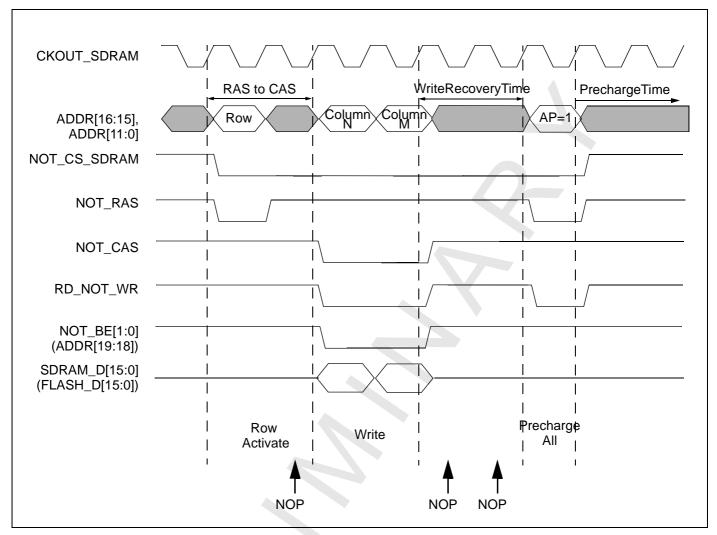

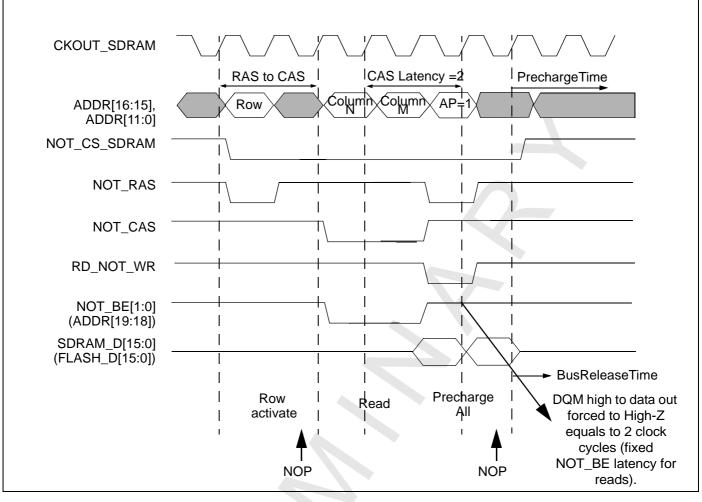

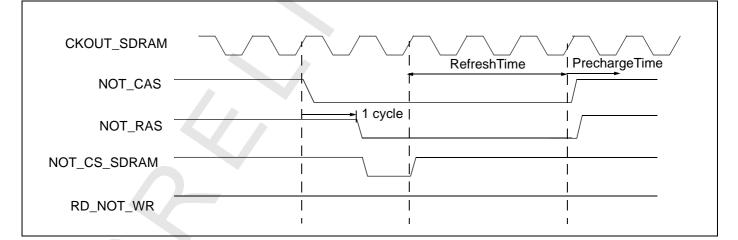

|           | 6.3.9 STV3550 Memory Interface Capabilities Regarding SDRAM Device | 71 |

|           | 6.3.10 SDRAM Low Power Mode                                        | 75 |

|           | 6.3.11 Memory Configurations                                       | 76 |

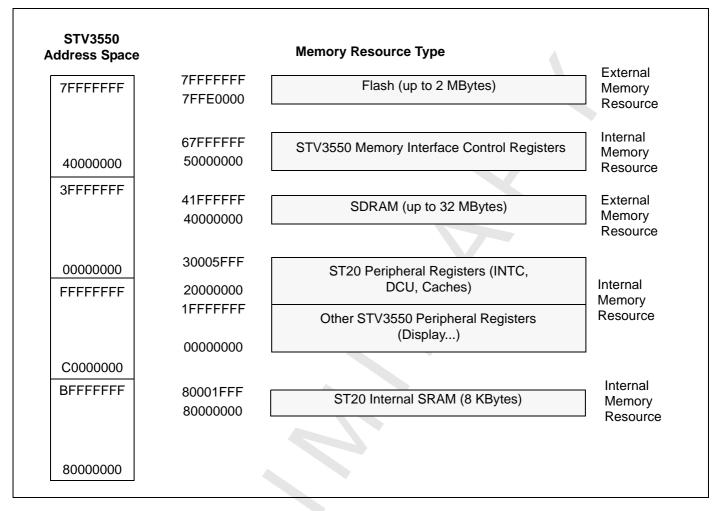

|           | 6.3.12 STV3550 External and Internal Memory Mapping                | 81 |

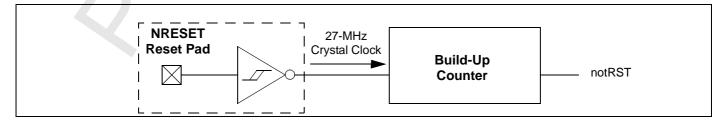

| 6.4       | Reset Strategy                                                     |    |

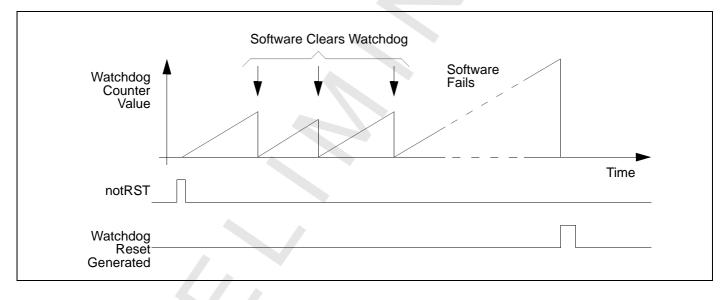

|           | <ul> <li>6.4.1 External Hard Reset</li> <li>6.4.2 Internal Reset Generated by the Watchdog</li> <li>6.4.3 Internal Soft Reset</li> </ul> | 82 |

|-----------|------------------------------------------------------------------------------------------------------------------------------------------|----|

| 6.5       | Booting the STV3550                                                                                                                      |    |

|           | 6.5.1 Typical Boot Sequence                                                                                                              |    |

|           | 6.5.2 Starting The Main Application Program                                                                                              |    |

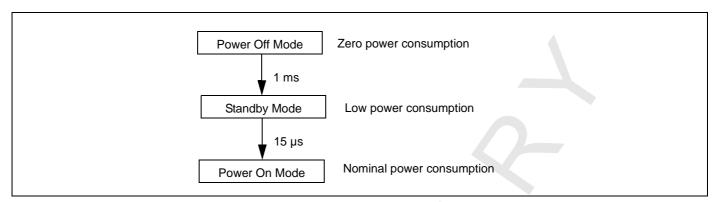

| 6.6       | Standby Mode                                                                                                                             |    |

| 6.7       | Interrupt Management                                                                                                                     |    |

| 6.8       | Clock Generator                                                                                                                          | 85 |

| Chapter 7 | TV Chassis Control                                                                                                                       |    |

| 7.1       | PWM and Counter Module                                                                                                                   |    |

|           | 7.1.1 External Interface                                                                                                                 | 86 |

|           | 7.1.2 PWM Functions                                                                                                                      | 86 |

|           | 7.1.3 Counter Functions                                                                                                                  | 87 |

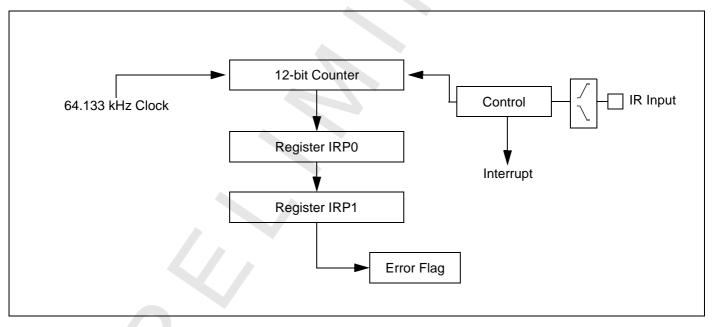

| 7.2       | Infrared Receiver Preprocessor                                                                                                           |    |

| 7.3       | Watchdog Timer (WDT)                                                                                                                     |    |

|           | 7.3.1 Clearing the Counter                                                                                                               | 89 |

|           | 7.3.2 Generation of Internal Watchdog Reset Signal                                                                                       | 90 |

| 7.4       | Real Time Clock (RTC)                                                                                                                    | 91 |

|           | 7.4.1 Real Time Clock (RTC)                                                                                                              | 91 |

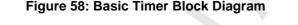

| 7.5       | Basic Timer                                                                                                                              |    |

|           | 7.5.1 Functional Description                                                                                                             | 92 |

|           | 7.5.2 Interrupt Selection                                                                                                                | 93 |

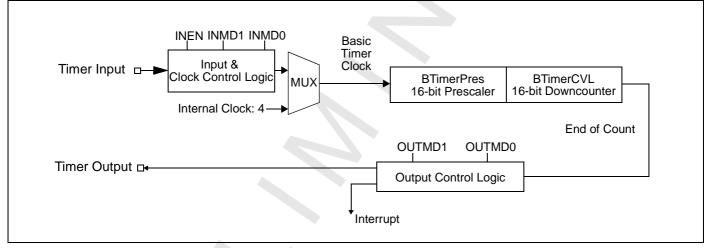

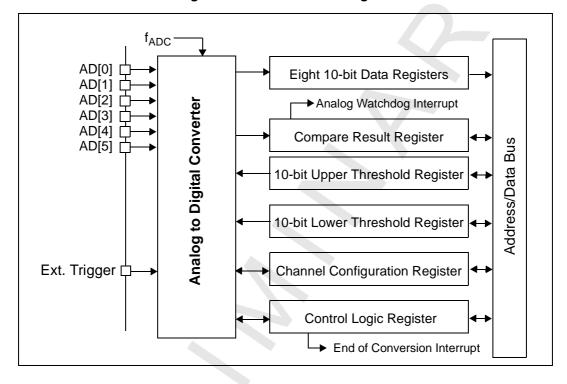

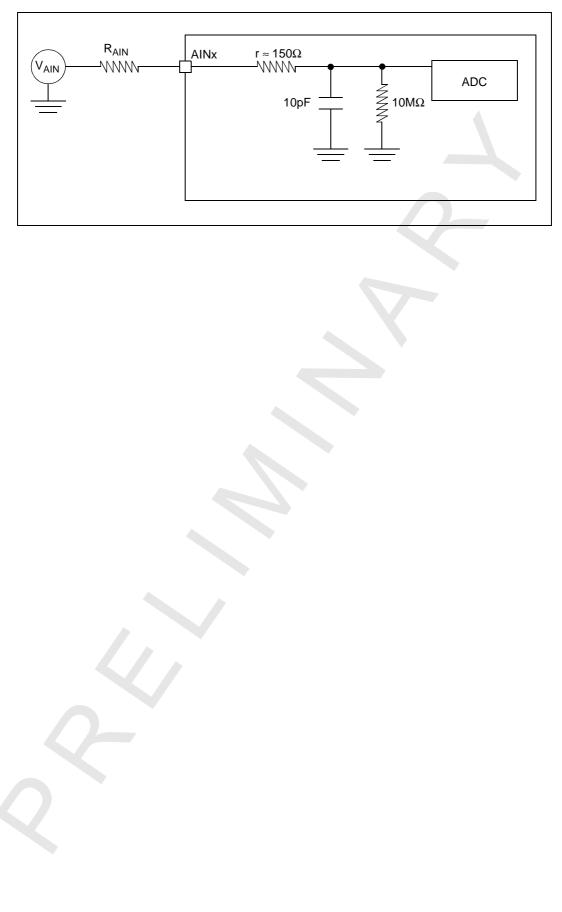

| 7.6       | Analog to Digital Converter                                                                                                              | 94 |

|           | 7.6.1 Introduction                                                                                                                       | 94 |

|           | 7.6.2 Main Features                                                                                                                      |    |

|           | 7.6.3 General Description                                                                                                                |    |

|           | <ul><li>7.6.4 Analog Watchdog</li><li>7.6.5 Low Power Modes</li></ul>                                                                    |    |

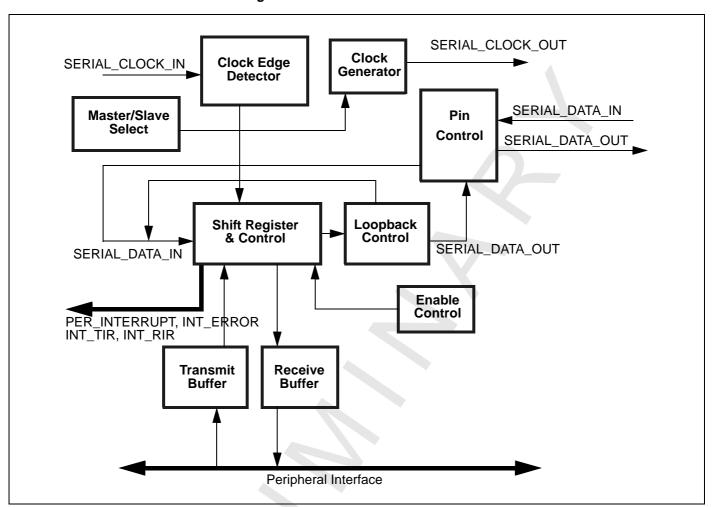

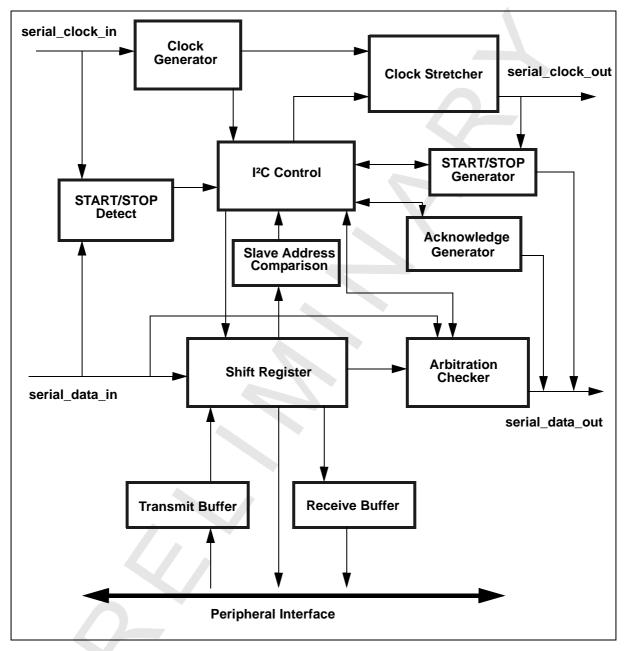

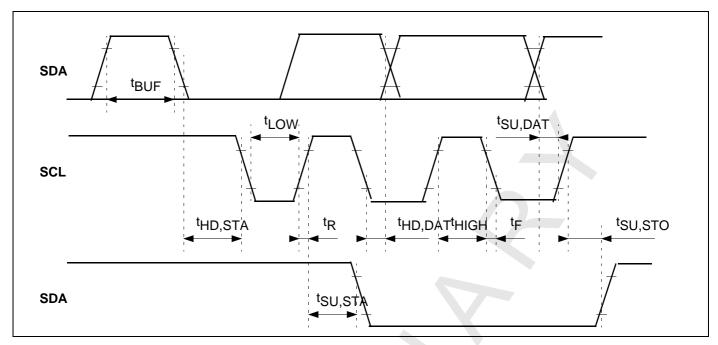

| 7.7       | Inter Integrated Circuit Bus (I <sup>2</sup> C)                                                                                          |    |

|           |                                                                                                                                          |    |

|           | 7.7.1 Basic Features                                                              |     |

|-----------|-----------------------------------------------------------------------------------|-----|

|           | 7.7.2 Functional Description                                                      |     |

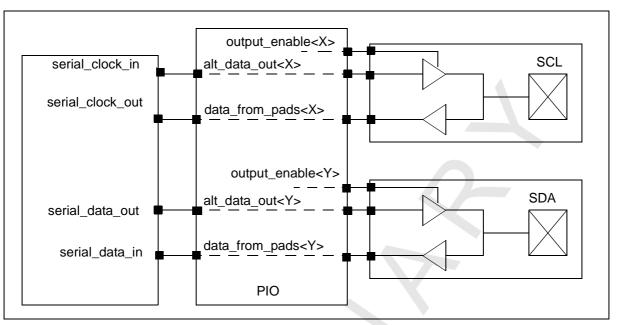

|           | 7.7.3 PIO Pad Connection & Control                                                |     |

|           | 7.7.4 Clock Generation                                                            |     |

|           | 7.7.5 Clock Control                                                               | 99  |

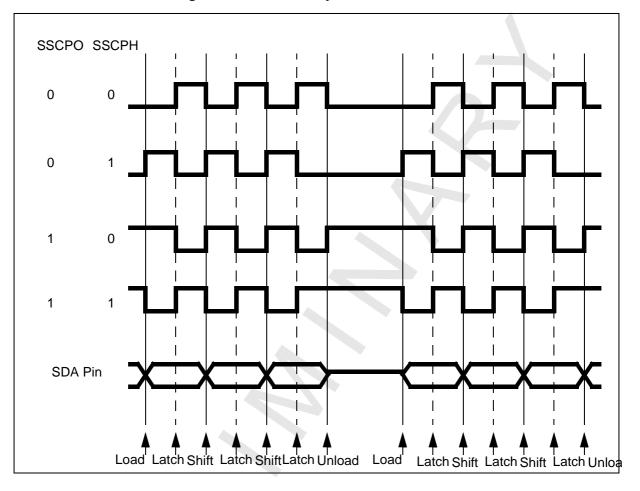

|           | 7.7.6 Shift Register                                                              |     |

|           | 7.7.7 Clock Edge Detection                                                        |     |

|           | 7.7.8 Receive Data Sampling                                                       |     |

|           | 7.7.9 Transmit & Receive Buffers                                                  |     |

|           | 7.7.10 Loopback Mode                                                              |     |

|           | <ul><li>7.7.11 Enabling Operation</li><li>7.7.12 Master/Slave Operation</li></ul> |     |

|           | <ul><li>7.7.12 Master/Slave Operation</li><li>7.7.13 Error Detection</li></ul>    |     |

|           | 7.7.14 Interrupt Mechanism                                                        |     |

|           | 7.7.15 Software Reset                                                             |     |

|           | 7.7.16 I <sup>2</sup> C Operation                                                 |     |

|           | 7.7.17 Clock Period In I <sup>2</sup> C Mode                                      |     |

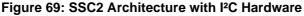

|           | 7.7.18 Clock Synchronization                                                      |     |

|           | 7.7.19 START/STOP Condition Detection                                             |     |

|           | 7.7.20 Slave Address Comparison                                                   |     |

|           | 7.7.21 Clock Stretching                                                           |     |

|           | 7.7.22 START/STOP Condition Generation                                            |     |

|           | 7.7.23 Acknowledge Bit Generation                                                 | 113 |

|           | 7.7.24 Arbitration Checking                                                       | 113 |

|           | 7.7.25 I <sup>2</sup> C Timing Specification                                      | 114 |

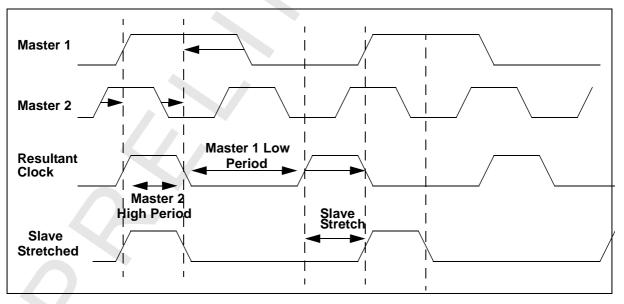

| 7.8       | Asynchronous Serial Controller (ASC)                                              |     |

|           | 7.8.1 Control                                                                     |     |

|           | 7.8.2 Data Frames                                                                 |     |

|           | 7.8.3 Transmission                                                                |     |

|           | 7.8.4 Reception                                                                   | 119 |

|           | 7.8.5 Baud Rate Generation                                                        | 121 |

|           | 7.8.6 Interrupt Control                                                           | 123 |

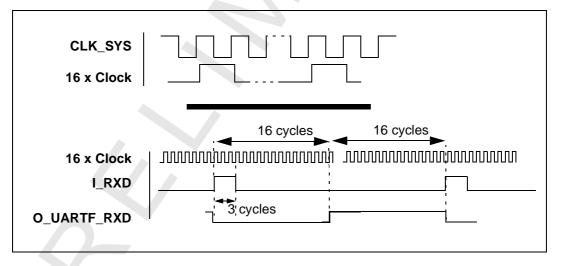

| 7.9       | IrDA Encoder/Decoder                                                              |     |

|           | 7.9.1 Encoding Scheme                                                             |     |

|           | 7.9.2 Decoding Scheme                                                             |     |

|           | 7.9.3 Register                                                                    |     |

|           |                                                                                   |     |

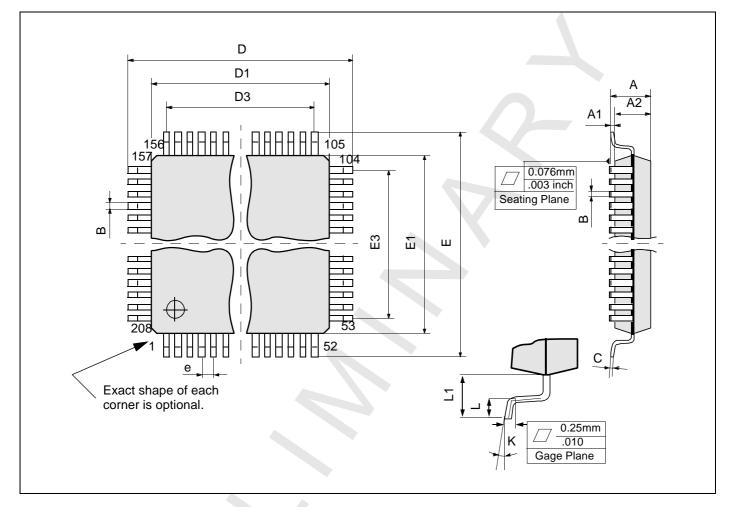

| Chapter 8 | General Package Information                                                       | 128 |

| •         |                                                                                   |     |

| 8.1       | Package Mechanical Data                                                           |     |

|           |                                                                                   |     |

| Chapter 9 | Electrical Characteristics                                                        |     |

| 9.1       | Absolute Maximum Ratings                                                          | 130 |

| 9.2       | Thermal Data                                                                      | 131 |

| 9.3       | DC Electrical Characteristics                                                     | 131 |

| 9.4       | Supply Current Characteristics                                                    |     |

| 9.5       | H/V Synchronization Characteristics                                               | 132 |

| 9.6        | Clock Characteristics                                                                                                                                  | 132 |

|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 9.7        | ADC Characteristics                                                                                                                                    | 133 |

| 9.8        | I <sup>2</sup> C Bus Characteristics                                                                                                                   |     |

| Chapter 10 | Timing Specifications                                                                                                                                  |     |

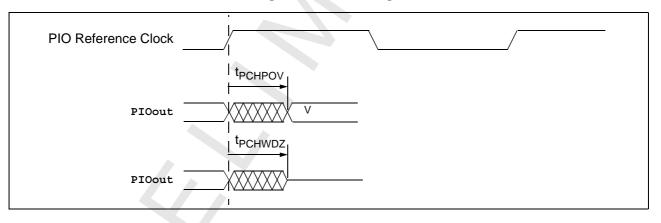

| 10.1       | PIO Timings                                                                                                                                            | 137 |

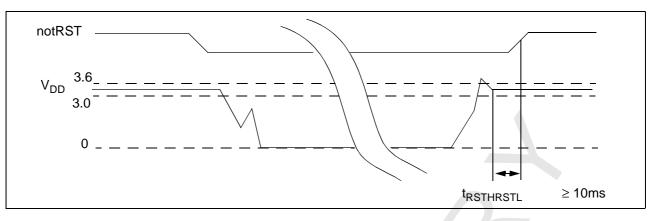

| 10.2       | Reset Timings                                                                                                                                          |     |

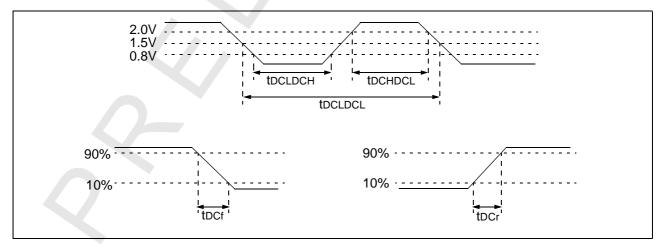

| 10.3       | Clock Timings<br>10.3.1 XTALIN Timings                                                                                                                 |     |

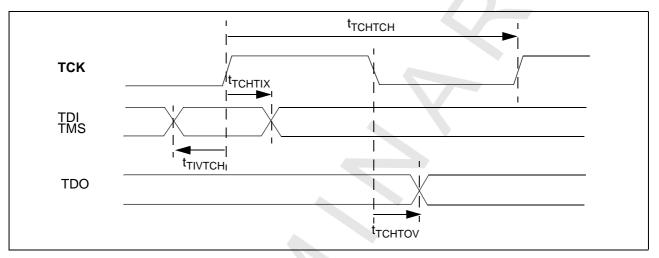

| 10.4       | TAP Timings                                                                                                                                            |     |

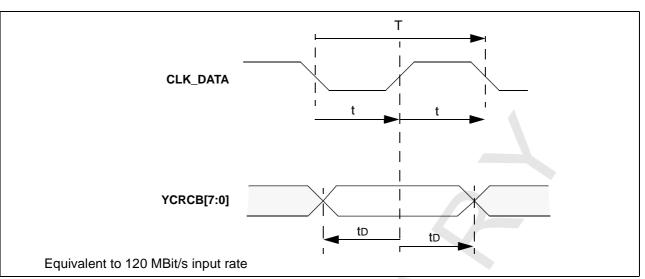

| 10.5       | Input Video Stream Timings<br>10.5.1 SDIN Interface                                                                                                    |     |

| 10.6       | Output Video Port Interface (AC Electrical Characteristics)10.6.1Normal Mode (single edge clock output)10.6.2Multiplexed Mode (dual edge clock output) | 140 |

| Chapter 11 | Revision History                                                                                                                                       |     |

## **1 General Information**

## 1.1 Introduction

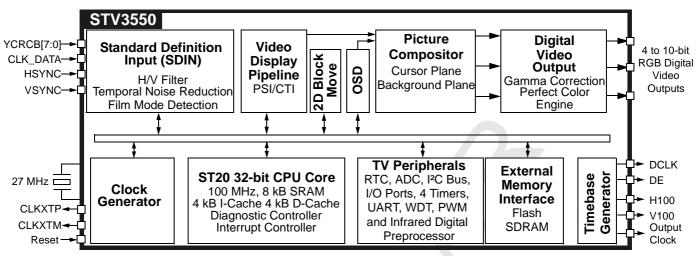

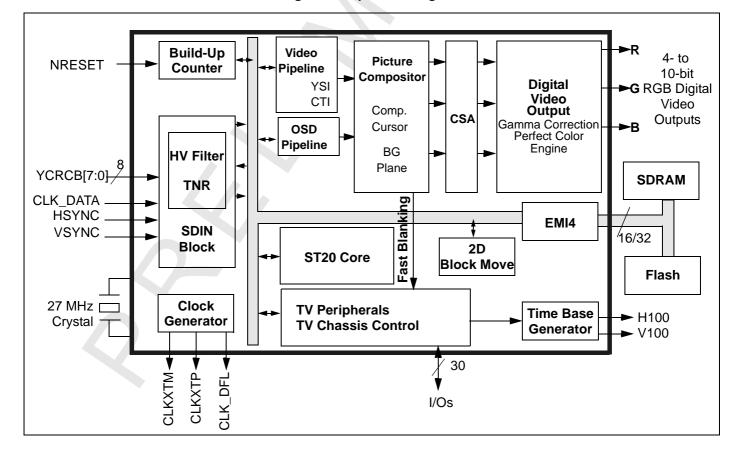

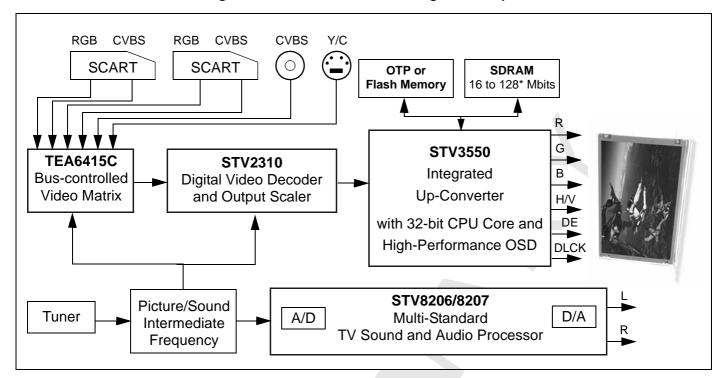

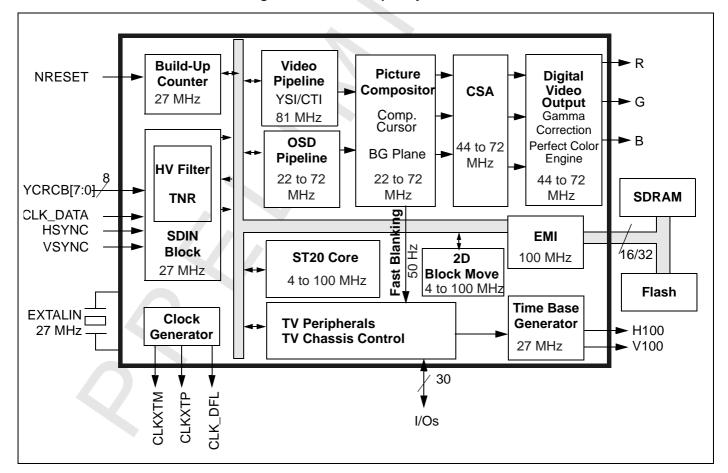

This integrated circuit (IC) is dedicated to flat panel display TV chassis. Combined with a digital multi-standard video decoder (STV2310) delivering an ITU-R BT.601/656 video stream, it provides a cost-effective, high-performance solution for plasma or LCD TV applications. The STV3550 includes an up-converter, a 32-bit ST20 CPU core with all peripherals required for controlling the TV chassis. Teletext data is extracted from the incoming stream and decoded by the CPU. An embedded On-Screen Display (OSD) generator delivers the text and graphics. The Video Display Pipeline performs feature box image processing such as picture improvement, horizontal and vertical rescaling and Temporal Noise Reduction.

The chip operates with an external SDRAM that is used for the field-rate up-conversion and text and graphic generations. The external SDRAM can be configured as a single bank of 16/64/128 Mb (16-bit configuration) or a dual bank of 16/64 or 128 Mb (32-bit configuration). Application program codes are stored in an external Flash memory.

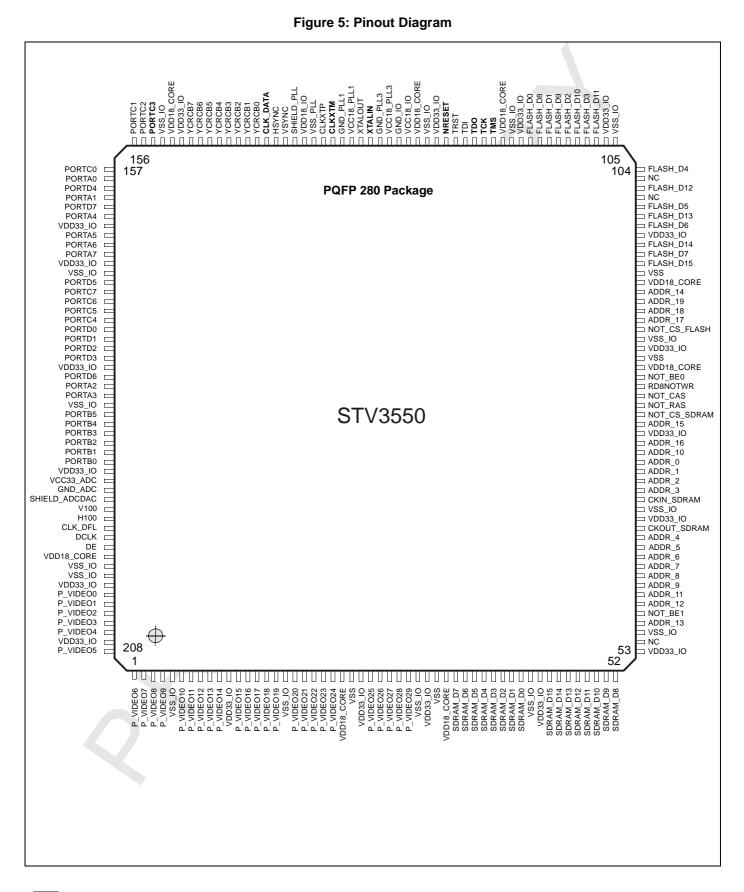

The STV3550 is designed using an 0.18 micron CMOS process and delivered in a 208-pin PQFP (0.5 mm pitch) package.

The STV3550 completes the Digital IC Core family (STi5xxx, STi7xxx) which offers common CPU and software platforms based on STMicroelectronics' 32-bit ST20 CPU core. This device, which is specifically designed for plasma or LCD TV applications, is completely compatible with the architecture and software of the STV3500 CTV100-CRT platform that targets CRT-based TV chassis.

#### Figure 1: Top Level Diagram

Figure 2: CTV100-LCD Platform Diagram Example

\* one or two banks

### 1.2 Software

<u>ل</u>حک

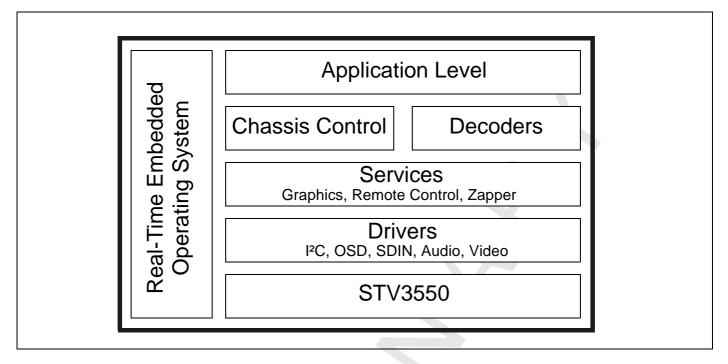

The layering model adopted for the CTV100-LCD Software Stack is based on certain non-functional requirements:

- Re-usable

- Portable

- Modular

- Reliable and robust

**47/**

• Readable and maintainable

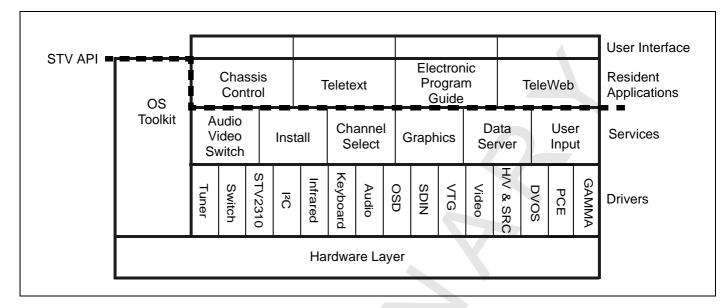

Figure 3: Global Software Architecture

The CTV100-LCD application software consists of 4 main layers based on these non-functional requirements:

- System Layer provides certain general-purpose components such as Handle or Link List Managers. This layer also contains the Operating System Abstraction Layer (OSAL) components which enable other layers to be OS-independent.

- Driver Layer provides a hardware abstraction to the upper layers making them hardwareindependent.

- Service Layer contains the components that provide the Application layer with high level interfaces in order to manage the TV set. The set of Service components included in the demonstration application are very useful for developing applications.

• Application Layer which contains the software that defines the "Look & Feel" of the TV set. This layer, for instance, contains the components that are responsible for the following features: interpretation of user inputs, display and navigation functions and Teletext applications.

#### Figure 4: Software Architecture Example

## **1.3** Related Documentation

There are several documents available that explain the various software capabilities. There are three different types of documents:

- 1. General Introduction Manual

- 2. User Guides

- 3. Reference Guide

#### 1.3.1 General Introduction Manual

This document describes the general architecture of the features listed in Section 1.2: Software.

It also describes the relationships between the various service, driver, system and application modules. It lists all the available modules and their version number. A brief description of each function is also provided.

#### 1.3.2 User Guides

**ل\_م**ا

A user guide is provided for each set of selected features. These documents will enable the user to get started with the relevant features. An example code is also included as well as a troubleshooting section.

A list (non-exhaustive) of existing user guides is given below.

- 1. CTV100-LCD: STV3550 User Controls User Guide

- The Remote Control Service is responsible for the byte assembly of infrared frames coming from a Remote Control device. It provides the client with a high-level interface to manage Remote Control inputs.

- The User Interface Service provides the client with a high-level interface to manage both Remote Control and Keyboard inputs. The client provides its own code, with which it will be notified.

- 2. CTV100-LCD: STV3550 Video and Sync User Guide

47/

The Video Service provides the client with a high-level interface for managing the Video. This service is responsible for the complete management of the video buffers and the

video display, according to client configuration, in terms of the video mode (Up-conversion, Proscan...).

It also offers video-related features, such as zoom or freeze frame, among others.

- The Synchronization Service is responsible for programming the field polarity. It provides the client with a high level interface for managing the Field Polarity sequences.

- 3. CTV100-LCD: STV3550 Source Selection User Guide

- The Audio/Video Switch service is responsible for managing the connections between audio and video inputs and outputs by using drivers that provide audio/video switching functions.

The Audio/Video Switch component is also responsible for detecting changes in the Slow Blanking Level (available on SCART connections) by using the ADC driver.

- The Front End service is responsible for the tuning and the scanning operations. It provides the client with a high level interface working in the frequency domain.

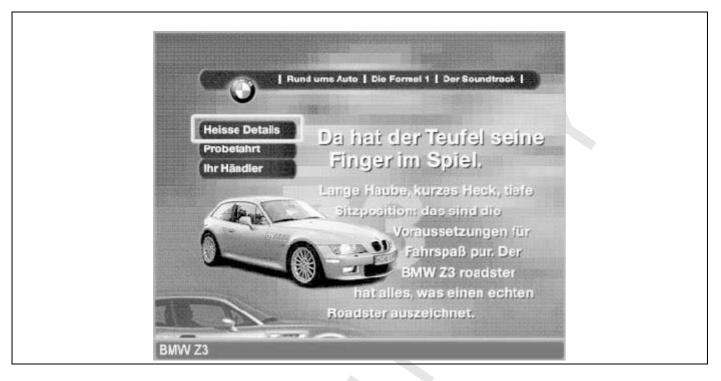

- 4. CTV100-LCD: STV3550 Graphics User Guide

- It provides the necessary software for creating cursors and graphic planes using respectively the Cursor Driver (DV\_GAM) and the On-Screen Display Driver (STOSD).

- It also includes the Two Dimensional Block Move Driver (DV\_BME) in order to improve graphical applications which often require moving blocks of data.

This document will describe the CTV100-LCD Basic Graphics Stack and also provide a guide for the implementation and configuration of a graphical user interface (GUI) stack based on the OSD.

#### 1.3.3 Reference Guide

There is one reference guide for each component (service, driver, etc.). This document includes the API as well as an Example of Use. This document specifically targets design engineers.

11/144

## 2 STV3550 Pin List

## 2.1 Pinout

## 2.2 Pin Description

### Table 1: Digital Video Input Stage

| Pin No. | Pin Name | Pin Description                        |

|---------|----------|----------------------------------------|

| 140     | VSYNC    | Vertical Sync Input                    |

| 141     | HSYNC    | Horizontal Sync Input                  |

| 142     | CLK_DATA | Video Input Clock from STV2310         |

| 143     | YCRCB0   | 4:2:2 Data Stream Input 0 from STV2310 |

| 144     | YCRCB1   | 4:2:2 Data Stream Input 1 from STV2310 |

| 145     | YCRCB2   | 4:2:2 Data Stream Input 2 from STV2310 |

| 146     | YCRCB3   | 4:2:2 Data Stream Input 3 from STV2310 |

| 147     | YCRCB4   | 4:2:2 Data Stream Input 4 from STV2310 |

| 148     | YCRCB5   | 4:2:2 Data Stream Input 5 from STV2310 |

| 149     | YCRCB6   | 4:2:2 Data Stream Input 6 from STV2310 |

| 150     | YCRCB7   | 4:2:2 Data Stream Input 7 from STV2310 |

#### Table 2: Digital Video Output Stage

| Pin No. | Pin Name  | Pin Description         |

|---------|-----------|-------------------------|

| Digital |           |                         |

| 193     | V100      | Vertical Sync Output    |

| 194     | H100      | Horizontal Sync Output  |

| 195     | CLK_DFL   | Clock Output            |

| 202     | P_VIDEO0  | Digital Video Output 0  |

| 203     | P_VIDEO1  | Digital Video Output 1  |

| 204     | P_VIDEO2  | Digital Video Output 2  |

| 205     | P_VIDEO3  | Digital Video Output 3  |

| 206     | P_VIDEO4  | Digital Video Output 4  |

| 208     | P_VIDEO5  | Digital Video Output 5  |

| 1       | P_VIDEO6  | Digital Video Output 6  |

| 2       | P_VIDEO7  | Digital Video Output 7  |

| 3       | P_VIDEO8  | Digital Video Output 8  |

| 4       | P_VIDEO9  | Digital Video Output 9  |

| 6       | P_VIDEO10 | Digital Video Output 10 |

| 7       | P_VIDEO11 | Digital Video Output 11 |

| 8       | P_VIDEO12 | Digital Video Output 12 |

| 9       | P_VIDEO13 | Digital Video Output 13 |

| 10      | P_VIDEO14 | Digital Video Output 14 |

| 12      | P_VIDEO15 | Digital Video Output 15 |

| 13      | P_VIDEO16 | Digital Video Output 16 |

| 14      | P_VIDEO17 | Digital Video Output 17 |

| 15      | P_VIDEO18 | Digital Video Output 18 |

| Pin No. | Pin Name  | Pin Description          |

|---------|-----------|--------------------------|

| 16      | P_VIDEO19 | Digital Video Output 19  |

| 18      | P_VIDEO20 | Digital Video Output 20  |

| 19      | P_VIDEO21 | Digital Video Output 21  |

| 20      | P_VIDEO22 | Digital Video Output 22  |

| 21      | P_VIDEO23 | Digital Video Output 23  |

| 22      | P_VIDEO24 | Digital Video Output 24  |

| 26      | P_VIDEO25 | Digital Video Output 25  |

| 27      | P_VIDEO26 | Digital Video Output 26  |

| 28      | P_VIDEO27 | Digital Video Output 27  |

| 29      | P_VIDEO28 | Digital Video Output 28  |

| 30      | P_VIDEO29 | Digital Video Output 29  |

| 196     | DCLK      | Digital CMOS Clock       |

| 197     | DE        | Digital CMOS Data Enable |

#### Table 2: Digital Video Output Stage (continued)

## Table 3: Parallel Input/Output Pins

| Pin No. | Pin Name | Main Function (after Reset) | Alternate Function            |

|---------|----------|-----------------------------|-------------------------------|

| 158     | PORTA0   | Port A0                     | PWMCapture0/PWM0              |

| 160     | PORTA1   | Port A1                     | PWMCapture1/INT2/PWM1         |

| 180     | PORTA2   | Port A2                     | PWMCapture2/INT3/extreg/PWM2  |

| 181     | PORTA3   | Port A3                     | PWMCapture3/PWM3              |

| 162     | PORTA4   | Port A4                     | UARTF TXD                     |

| 164     | PORTA5   | Port A5                     | UARTF RXD/UARTF TXD Smartcard |

| 165     | PORTA6   | Port A6                     | UARTF CTS                     |

| 166     | PORTA7   | Port A7                     | UARTF RTS                     |

| 188     | PORTB0   | Port B0                     | AD_0                          |

| 187     | PORTB1   | Port B1                     | AD_1                          |

| 186     | PORTB2   | Port B2                     | AD_2                          |

| 185     | PORTB3   | Port B3                     | AD_3                          |

| 184     | PORTB4   | Port B4                     | AD_4 / Timer Output 0         |

| 183     | PORTB5   | Port B5                     | AD_5/ Timer Output 1          |

| 157     | PORTC0   | Port C0                     | SDA_0                         |

| 156     | PORTC1   | Port C1                     | SCL_0                         |

| 155     | PORTC2   | Port C2                     | SDA_1                         |

| 154     | PORTC3   | Port C3                     | SCL_1                         |

| 173     | PORTC4   | Port C4                     | SDA_2                         |

| 172     | PORTC5   | Port C5                     | SCL_2                         |

| 171     | PORTC6   | Port C6                     | SDA_3                         |

| 170     | PORTC7   | Port C7                     | SCL_3                         |

| 174     | PORTD0   | Port D0                     | Timer Input 0                 |

| Pin No. | Pin Name | Main Function (after Reset) | Alternate Function             |

|---------|----------|-----------------------------|--------------------------------|

| 175     | PORTD1   | Port D1                     | Timer Input 1                  |

| 176     | PORTD2   | Port D2                     | Timer Input 2 / Timer Output 2 |

| 177     | PORTD3   | Port D3                     | Timer Input 3/ Timer Output 3  |

| 159     | PORTD4   | Port D4                     | IR_in                          |

| 169     | PORTD5   | Port D5                     | GFX_ACTIVE                     |

| 179     | PORTD6   | Port D6                     | INTO                           |

| 161     | PORTD7   | Port D7                     | INT1/16 x UART Clock           |

### Table 3: Parallel Input/Output Pins (continued)

## Table 4: External Memory Interface Pins

| Pin No.        | Pin Name  | Pin Description   |

|----------------|-----------|-------------------|

| Flash Data Bus |           |                   |

| 114            | FLASH_D0  | Flash Data Bus 0  |

| 112            | FLASH_D1  | Flash Data Bus 1  |

| 110            | FLASH_D2  | Flash Data Bus 2  |

| 108            | FLASH_D3  | Flash Data Bus 3  |

| 104            | FLASH_D4  | Flash Data Bus 4  |

| 100            | FLASH_D5  | Flash Data Bus 5  |

| 98             | FLASH_D6  | Flash Data Bus 6  |

| 95             | FLASH_D7  | Flash Data Bus 7  |

| 113            | FLASH_D8  | Flash Data Bus 8  |

| 111            | FLASH_D9  | Flash Data Bus 9  |

| 109            | FLASH_D10 | Flash Data Bus 10 |

| 107            | FLASH_D11 | Flash Data Bus 11 |

| 102            | FLASH_D12 | Flash Data Bus 12 |

| 99             | FLASH_D13 | Flash Data Bus 13 |

| 96             | FLASH_D14 | Flash Data Bus 14 |

| 94             | FLASH_D15 | Flash Data Bus 15 |

| SDRAM Da       | ata Bus   |                   |

| 42             | SDRAM_D0  | SDRAM Data Bus 0  |

| 41             | SDRAM_D1  | SDRAM Data Bus 1  |

| 40             | SDRAM_D2  | SDRAM Data Bus 2  |

| 39             | SDRAM_D3  | SDRAM Data Bus 3  |

| 38             | SDRAM_D4  | SDRAM Data Bus 4  |

| 37             | SDRAM_D5  | SDRAM Data Bus 5  |

| 36             | SDRAM_D6  | SDRAM Data Bus 6  |

| 35             | SDRAM_D7  | SDRAM Data Bus 7  |

| 52             | SDRAM_D8  | SDRAM Data Bus 8  |

| 51             | SDRAM_D9  | SDRAM Data Bus 9  |

| 50             | SDRAM_D10 | SDRAM Data Bus 10 |

| Pin No.   | Pin Name     | Pin Description                                    |

|-----------|--------------|----------------------------------------------------|

| 49        | SDRAM_D11    | SDRAM Data Bus 11                                  |

| 48        | SDRAM_D12    | SDRAM Data Bus 12                                  |

| 47        | SDRAM_D13    | SDRAM Data Bus 13                                  |

| 46        | SDRAM_D14    | SDRAM Data Bus 14                                  |

| 45        | SDRAM_D15    | SDRAM Data Bus 15                                  |

| Address B | us           |                                                    |

| 73        | ADDR_0       | Address Bus 0                                      |

| 72        | ADDR_1       | Address Bus 1                                      |

| 71        | ADDR_2       | Address Bus 2                                      |

| 70        | ADDR_3       | Address Bus 3                                      |

| 65        | ADDR_4       | Address Bus 4                                      |

| 64        | ADDR_5       | Address Bus 5                                      |

| 63        | ADDR_6       | Address Bus 6                                      |

| 62        | ADDR_7       | Address Bus 7                                      |

| 61        | ADDR_8       | Address Bus 8                                      |

| 60        | ADDR_9       | Address Bus 9                                      |

| 74        | ADDR_10      | Address Bus 10                                     |

| 59        | ADDR_11      | Address Bus 11                                     |

| 58        | ADDR_12      | Address Bus 12                                     |

| 56        | ADDR_13      | Address Bus 13                                     |

| 91        | ADDR_14      | Address Bus 14                                     |

| 77        | ADDR_15      | Address Bus 15 / BA0                               |

| 75        | ADDR_16      | Address Bus 16 / BA1                               |

| 88        | ADDR_17      | Address Bus 17                                     |

| 89        | ADDR_18      | Address Bus 18 / Not_BE2                           |

| 90        | ADDR_19      | Address Bus 19 / Not_BE3                           |

| Controls  |              |                                                    |

| 81        | RD_NOTWR     | SDRAM Write Enable / Flash Write Enable*           |

| 87        | NOT_CS_FLASH | Flash Chip Select                                  |

| 78        | NOT_CS_SDRAM | SDRAM Chip Select                                  |

| 79        | NOT_RAS      | SDRAM Row Address Strobe                           |

| 80        | NOT_CAS      | SDRAM Column Address Strobe / Flash Output Enable* |

| 82        | NOT_BE0      | SDRAM Byte Enable 0                                |

| 57        | NOT_BE1      | SDRAM Byte Enable 1                                |

| 66        | CKOUT_SDRAM  | Clock Output for SDRAM                             |

| 69        | CKIN_SDRAM   | SDRAM Clock Feedback                               |

## Table 4: External Memory Interface Pins (continued)

#### Table 5: System Controls

| Pin No. | Pin Name | Pin Description                       |  |  |  |

|---------|----------|---------------------------------------|--|--|--|

| 132     | XTALOUT  | 27 MHz Crystal Output                 |  |  |  |

| 131     | XTALIN   | 27 MHz Crystal Input                  |  |  |  |

| 135     | CLKXTM   | 27 MHz Differential Clock for STV2310 |  |  |  |

| 136     | CLKXTP   | 27 MHz Differential Clock for STV2310 |  |  |  |

| 119     | ТСК      | Test Clock Input                      |  |  |  |

| 121     | TDI      | Test Data Input                       |  |  |  |

| 120     | TDO      | Test Data Output                      |  |  |  |

| 118     | TMS      | Test Mode Select Input                |  |  |  |

| 122     | TRST     | Test Reset Input                      |  |  |  |

| 123     | NRESET   | STV3500 Reset Input (Active Low)      |  |  |  |

## Table 6: Power Supplies

| Pin No. | Pin Name      | Pin Description                               |

|---------|---------------|-----------------------------------------------|

| Analog  | L             |                                               |

| 192     | SHIELD_ADCDAC |                                               |

| 139     | SHIELD_PLL    | To connect to Analog Ground Supply for PLL    |

| 190     | VCC33_ADC     | 3.3 V Analog Voltage Supply for A/D Converter |

| 191     | GND_ADC       | Analog Ground Supply for ADC                  |

| 133     | VCC18_PLL1    | 1.8 V Analog Voltage Supply for PLL           |

| 134     | GND_PLL1      | Analog Ground Supply for PLL                  |

| 129     | VCC18_PLL3    | 1.8 V Analog Voltage Supply for PLL           |

| 130     | GND_PLL3      | Analog Ground Supply for PLL                  |

| 127     | VCC18_IO      | 1.8 V Analog Voltage Supply for PLL I/Os      |

| 128     | GND_IO        | Analog Ground Supply for PLL I/Os             |

| 138     | VDD18_PLL     | 1.8 V Analog Voltage Supply for PLL           |

| 137     | VSS_PLL       | Analog Ground Supply for PLL                  |

| Digital |               |                                               |

| 11      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 25      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 32      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 44      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 53      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 67      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 76      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 85      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 97      | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 106     | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 115     | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

| 124     | VDD33_IO      | 3.3 V Digital Voltage Supply                  |

## Table 6: Power Supplies (continued)

| Pin No. | Pin Name   | Pin Description              |  |  |  |

|---------|------------|------------------------------|--|--|--|

| 151     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 163     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 167     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 178     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 189     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 201     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 207     | VDD33_IO   | 3.3 V Digital Voltage Supply |  |  |  |

| 5       | VSS_IO     | Digital Ground Supply        |  |  |  |

| 17      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 31      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 43      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 55      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 68      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 86      | VSS_IO     | Digital Ground Supply        |  |  |  |

| 105     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 116     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 125     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 153     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 168     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 182     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 199     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 200     | VSS_IO     | Digital Ground Supply        |  |  |  |

| 23      | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 34      | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 83      | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 92      | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 117     | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 126     | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 152     | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 198     | VDD18_CORE | 1.8 V Digital Voltage Supply |  |  |  |

| 24      | VSS        | Digital Ground Supply        |  |  |  |

| 33      | VSS        | Digital Ground Supply        |  |  |  |

| 84      | VSS        | Digital Ground Supply        |  |  |  |

| 93      | VSS        | Digital Ground Supply        |  |  |  |

|         |            |                              |  |  |  |

#### Table 7: Not Connected

| Pin No. | Pin Name | Pin Description |

|---------|----------|-----------------|

| 54      | NC       |                 |

| 101     | NC       |                 |

| 103     | NC       |                 |

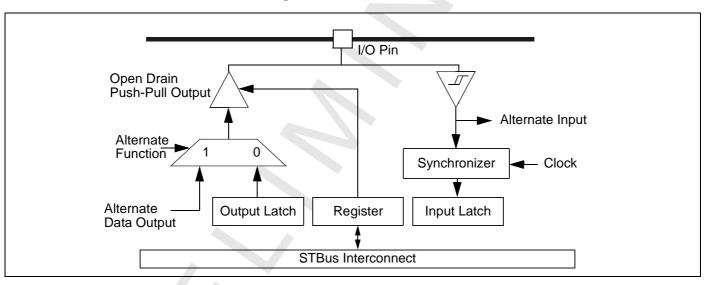

## 2.3 Parallel I/O Pins and Alternate Functions

The STV3550 includes 30 Parallel I/O pins arranged in 4 banks of 6 to 8-bit ports. The pins can be programmable in input, output, bi-directional or as alternate function pins. The ports are listed in Table 3 on page 14.

When configured as an output, the pin can be either open drain or with weak pull-up.

The input to any pin can be compared to a stored value, and if not equal, can produce an interrupt.

Any pin can be configured to output an alternate functions rather than programmed value. The input channel can be directly connected to a peripheral device to make the pin as a primary input of the device. The following table shows the assignments of the alternate functions for the 30 I/O pins.

#### **Figure 6: Pin Connections**

## 3 Video Functional Description

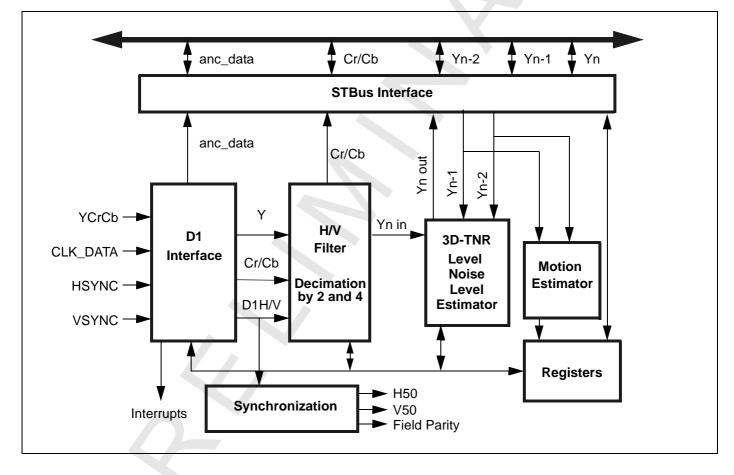

## 3.1 Standard Definition Input (SDIN)

The Standard Definition Input (SDIN) processes video signals before their storage in the external SDRAM. The SDIN includes the following features and functions:

- 4:2:2 D1 Input Stream De-multiplexing including ancillary data extraction

- Horizontal and Vertical Decimation by 2 and 4 with horizontal and vertical anti-aliasing filters (with programmable coefficients)

- 3D-Temporal Noise Reduction based on a proprietary ST algorithm

- Noise Level Estimator used to control the 3D-TNR through a software loop

- Motion Estimator to perform film mode detection or scene change detection through a software loop

#### Figure 7: SDIN Block Diagram

## 3.1.1 System Description

#### 3.1.1.1 D1 Interface

The D1 interface extracts the luma and chroma pixels from the 8-bit data stream as well as the ancillary data embedded in the horizontal and vertical blanking interval (VBI). This data includes VBI data such as Teletext, Closed Caption, WSS, VPS, etc... and sync pulses for horizontal and vertical synchronization.

The ancillary data is stored aligned in 32-bit packets. If necessary, the packets are completed by a filler with programmable data (060h, by default).

The parity of each field is extracted from the embedded F pulse or from the external H/V pulse. The field can be determined as top first or bottom first by programming.

The data stream sequence for the Y, Cr or Cb samples is programmable.

#### 3.1.1.2 D1 Formats

The typical input format supported by the SDIN is 720 pixels per line and 480 lines per frame for the 60-Hz source or 576 lines per frame for 50-Hz source (ITU-R BT.656) with a 27-MHz pixel clock.

The D1 interface can also support other formats with a pixel clock up to 30 MHz. The input format is given by the configuration of the interface that is programmable up to 960 pixels per line and 1024 lines per frame.

The 3D-TNR and the Motion Estimator can be used only with standardized line length of 720 pixels per line.

#### 3.1.1.3 Synchronization Pulse Extraction

The SDIN interface is able to extract either the sync pulses embedded in the data stream as described in specification ITU-R BT.656 or external H/V pulses sent on the H/V inputs.

After extraction, the sync pulses are used to capture the data which is then sent to the Video Timebase Generator (VTG) to synchronize the chip. Synchronization modes are described in Section 3.2: Video Timebase Generator (VTG).

The following sync pulses can be extracted and are selected using the registers:

- Embedded F and H sync pulses (for the vertical sweep, and EAV or SAV pulse for the horizontal sweep),

- Embedded V and H sync pulses (rising or falling edge of the V sync pulse, for the vertical sweep, and EAV or SAV pulse for the horizontal sweep),

- External H/Vsync pulses (rising or falling edge of the external V sync pulse, for the vertical sweep, and rising or falling edge of the external H pulse for the horizontal sweep),

- External H/Fsync pulses (rising and falling edge of the external F sync pulse, for the vertical sweep, and rising or falling edge of the external H pulse for the horizontal sweep).

#### 3.1.1.4 Horizontal and Vertical Filter

To perform high-factor Zoom-out on a picture (from 1/4 to 1/16 of the screen) with no extra load on the memory bandwidth, the SDIN can perform a horizontal and vertical decimation by 2 or 4 on the input signal. This means that unused pixels are not stored in the SDRAM and the memory bandwidth is not penalized.

Before decimation, the input signal passes through a horizontal and vertical filter to prevent aliasing effects. The coefficient of this filter is programmable and then can be optimized for each decimation factor. This filter and the decimator can be by-passed. The decimation factor is selectable by programming. When the decimator is active, the 3D-TNR is by-passed.

The vertical filter line-memories are limited to 720 pixels. When a line exceeds 720 pixels, the input line must be truncated to 720 pixels by the D1 interface (configured at 720 pixels per line).

#### 3.1.1.5 3D Temporal Noise Reduction (TNR)

When the D1 interface is set in a standard configuration (720 pixels per line and 288 or 240 lines per field) and the decimation filter is by-passed, the luma signal can be filtered in the spatial and temporal domain in order to reduce in-band noise. The noise reduction is based on a proprietary ST

algorithm that includes a comet-effect canceller. The strength of the noise reduction can be adjusted in 32 steps depending on the noise level.

The SDIN includes a Noise Estimator that delivers a 32-step data item on the noise level for each field. This data can be processed by the CPU to control the 3D-Temporal Noise Reductor and then performs an adaptive noise reduction. This function is available in standard configurations only.

#### 3.1.1.6 Motion Estimator

When the D1 interface is set in a standard configuration (720 pixels per line and 288 or 240 lines per field), the SDIN provides scene change and video picture format data based on 3 consecutive fields.

This information can be processed by the CPU to determine if the signal is from a video or a film source, and then the CPU can select the optimized up-conversion mode (Proscan field merging or interpolation).

This data is also used to determine the polarity of the field: Top First (generally used) or Bottom First.

## 3.2 Video Timebase Generator (VTG)

This block generates the up-converted horizontal and vertical sync pulses required to drive the video output stages. It receives the extracted H/V sync pulses from the SDIN block, in the 1H domain, and, depending on the selected synchronization mode, provides H/V sync pulses for the 2H domain.

The VTG is able to generate all output synchronization pulses from 1H to 3H for horizontal sweep and 50 Hz to 120 Hz for Vertical sweep, in Interlaced or Progressive mode.

The VTG clock is derived from the on-board crystal oscillator to reduce jitter. Vertical and horizontal sync pulses are generated by the division of the VTG\_CLK signal frequency.

The CPU manages the division factors and processes the incoming 50-Hz H and V pulses to generate the required 100-Hz scanning sequences.

#### 3.2.1 Synchronization Modes

- Slave by H and V signals (embedded or external)

- Slave by V signals (embedded or external)

- Master mode.

**ل ۲**

• Pass-through (for VGA application) with generator-locking of the OSD clock.

#### 3.2.2 Deinterlacing Modes and Progressive Scan Output

The de-interlacing can be done in the following modes:

- Spatial line interpolation, using the high resolution vertical polyphase filter

- Motion adaptive spatial-temporal interpolation, using the median filter

- Field merging for film sources

- Note: The scrolling mode is done by programming the Video Timebase Generator (VTG) that defines the output number of lines/field, and by programming the Video Display Pipeline that performs the number of pixel/line interpolations.

The following table shows typical de-interlacing modes, according to the input format:

|        | INPUT                       |                                                                           |                                                 |                                                                           |                                                                           |                                                   |                                                 |                                                                           |

|--------|-----------------------------|---------------------------------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------------------------------|---------------------------------------------------|-------------------------------------------------|---------------------------------------------------------------------------|

|        | Panels &<br>Output<br>modes | 50 Hz<br>interlaced<br>Video                                              | 50 Hz<br>interlaced<br>movie                    | 50 Hz<br>n-interlaced<br>game                                             | 60 Hz<br>interlaced<br>Video                                              | 60 Hz<br>interlaced<br>movie (3:2)                | 60 Hz<br>interlaced<br>movie (2:2)              | 60 Hz<br>n-interlaced<br>game                                             |

| OUTPUT | VGA                         | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Z out H<br>720>640<br>Z out V<br>576>480 | A+B<br>Z out H<br>720>640<br>Z out V<br>576>480 | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Z out H<br>720>640<br>Z out V<br>576>480 | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Z out H<br>720>640<br>Z out V<br>576>480 | 3:2pd<br>Z out H<br>720>640<br>Z out V<br>576>480 | A+B<br>Z out H<br>720>640<br>Z out V<br>576>480 | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Z out H<br>720>640<br>Z out V<br>576>480 |

|        | XGA                         | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Z in H<br>720>1024<br>Z in V<br>576>768  | A+B<br>Z in H<br>720>1024<br>Z in V<br>576>768  | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Zin H<br>720>1024<br>Z in V<br>576>768   | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Zin H<br>720>1024<br>Z in V<br>576>768   | 3:2pd<br>Zin H<br>720>1024<br>Z in V<br>576>768   | A+B<br>Zin H<br>720>1024<br>Z in V<br>576>768   | A+A*B*+B<br>Or<br>A+Med (A,B)<br>Zin<br>H720>1024<br>Z in V<br>576>768    |

Note: 720 pixels/line refers to ITU-R BT 601/656 video input standard resolution.

#### 3.2.3 Regulation Modes

The regulation modes of the input and output dataflows are based on the configurations of several blocks such as the SDIN, VTG, Display, and also depends on the selected synchronization modes.

These regulation modes are then managed by a software layer that controls the various registers and includes algorithms to maintain the balance between the input and output dataflows. This service software layer allows various regulation modes as described below, selectable at the application level.

When the VTG block is set in Slave mode, the PLL that line-locks the clock pixel to the Hsync signal is used to regulate the input and output dataflows.

When the VTG block is set in Master mode, the following regulation modes are possible:

1. Frame Skip & Repeat Mode (used for Proscan mode)

In this mode, depending on the speed variations between the input flow and the output flow, a frame is repeated or skipped from time to time (1 to 2 per second).

2. Field Skip & Repeat Mode (used for field rate up-conversion as 100 Hz)

In this mode, depending on the speed variations between the input flow and the output flow, a field is repeated or skipped from time to time (1 to 2 per second).

3. Line Skip & Repeat Mode

In this mode, certain lines are repeated or skipped during the VBI, depending on the delay between the input and output Vsync signals.

4. Pixel Skip & Repeat Mode

In this mode; pixel periods are repeated or skipped during the horizontal or vertical blanking interval, depending on the delay between each Vsync signal.

## 3.3 Video Display Pipeline

The Video Display block includes all the processing required for adapting the incoming video stream to the selected display format. Depending on the up-conversion mode, this block generates the correct video sequence with the selected number of pixels per line, lines per field or fields per second. It uses high-resolution horizontal and vertical polyphase filters to interpolate the additional pixels and lines required for the selected display format. These filters are also used for zoom-in and zoom-out rescaling.

It also includes picture improvement algorithms (PSI/CTI) to provide the picture with a more "high-resolution" aspect.

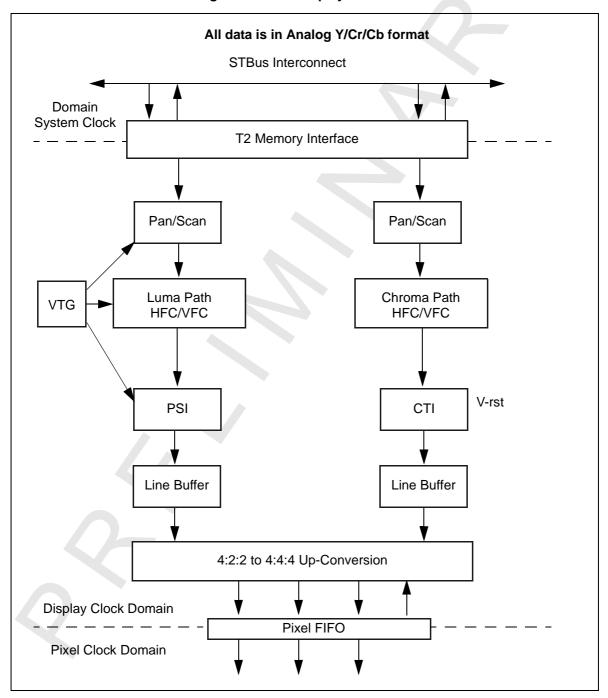

Figure 8: Video Display Flowchart

### 3.3.1 Main Features

- Horizontal resizing using a Sample Rate Converter based on an 8-tap, 32-phase polyphase filter with a programmable factor from 0.25 to 4.

- Vertical resizing using a Sample Rate Converter based on a 4-tap, 32-phase polyphase filter with a programmable factor from 0.5 to 4.

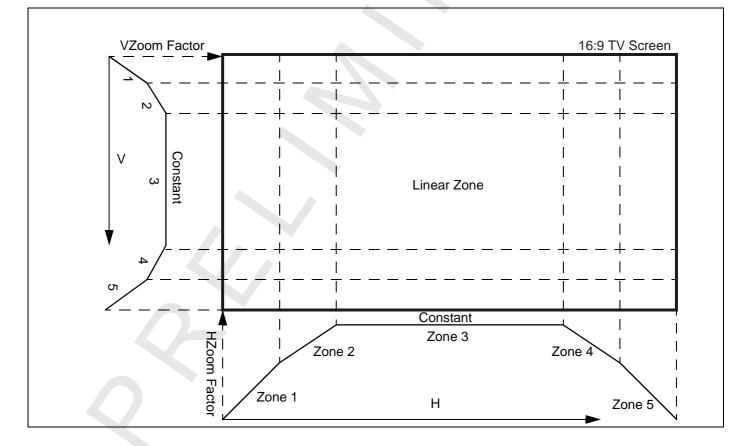

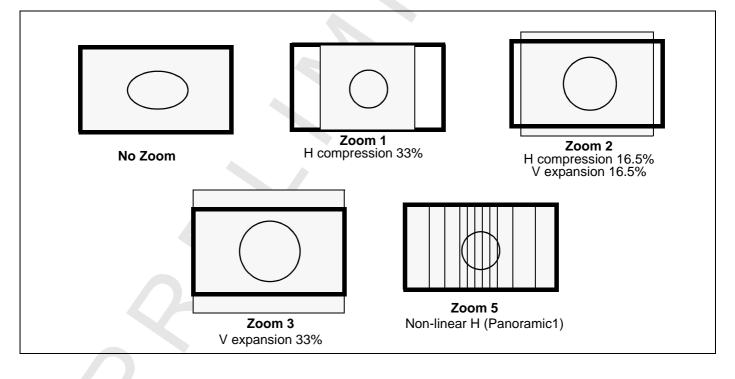

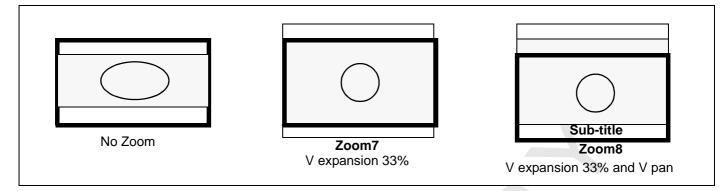

- Non-linear horizontal and vertical format conversion with up to 5 programmable segments.

- Horizontal video output resolution adjustable between 360 and 1920 active pixels per line by using a programmable pixel clock frequency.

- Vertical video output resolution adjustable between 240 and 1080 active lines per field.

- Field parity interpolation by controlling the phase offset in the vertical polyphase filter.

- Programmable Pan and Scan video positioning.

- Color Edge Replacement for Color Transient Improvement (CTI).

- Horizontal and Vertical Luma Peaking.

- Contrast Enhancement: Black, Grey, and White Stretch.

- 4:2:2 to 4:4:4 Chroma Up-sampling

- 10-bit RGB output

#### 3.3.2 Horizontal and Vertical Rescaling

#### Figure 9: Zoom Rescaling Diagram

The rescaling function is performed by two 32-phase polyphase filters (Horizontal and Vertical), of which all coefficients are stored in a programmable table. In this case, if needed, the transfer function of the filter can be optimized by referring to a specific up-conversion process. This scaling

**Δγ**/

factor is programmable from 0.25 to 4 for horizontal scaling and 0.5 to 4 for vertical scaling with an accuracy of 1/8192. This allows for continuous linear zoom variations.

#### 3.3.2.1 Non-Linear Zoom

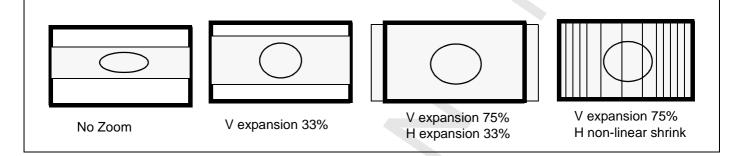

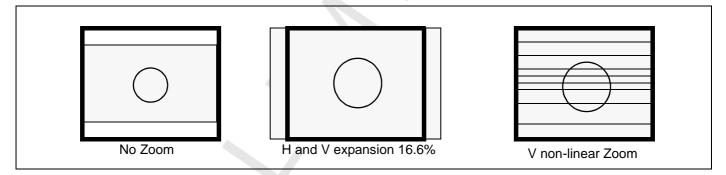

The rescaling block performs the horizontal and vertical non-linear zoom as shown in Figure 9. The picture can be divided into 5 different segments in all directions.

#### 3.3.2.2 Letter-box Format Detection

Letter-box format detection is included in order to automatically detect the horizontal black bars used with letter-box input video (Cinemascope,...) signals. This detection system is based on a proprietary algorithm that measures a certain level of data on a field basis.

This function can also detect video effects such as logos or subtitles inserted in the black parts of the video. The programmer can use this data to create an automatic format conversion for all the various cinema formats.

#### 3.3.2.3 Format Conversion

47/

The horizontal and vertical polyphase filters can be also used for the format conversions required for adapting the input video to the display format. Various examples are shown in the following figures. All formats are software-controlled and the letter-box format detector can also be used to automatically select the best-suited display format to prevent the horizontal black bars from being displayed.

#### Figure 10: Display Formats for 4:3 Input, 4:3 Aspect Ratio and 16:9 TV Screen

#### Figure 11: Display Formats for 4:3 Input, 16:9 Aspect Ratio (Letter-box) and 16:9 TV Screen

#### Figure 12: Display Formats for 4:3 Input, 2.35 Aspect Ratio (Wide Film) and 16:9 TV Screen

#### Figure 13: Display Formats for 4:3 Input, 16:9 Aspect Ratio and 4:3 TV Screen

#### 3.3.3 Image Improvement

#### 3.3.3.1 Main Features

- Contrast Enhancement with 4 different modes: Black Stretch, White Stretch, Grey Stretch and Black & White Shrink

- Vertical and Horizontal peaking,

- Luma Coring

- Color Edge Replacement for Color Transition Improvement (CTI)

- Brightness Estimator

- Histogram

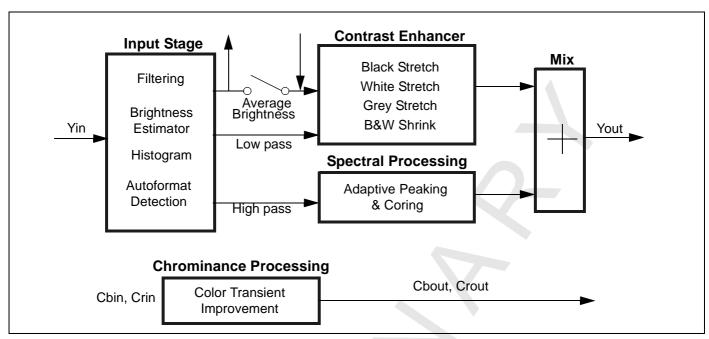

#### Figure 14: Image Improvement Block Diagram

#### 3.3.4 Brightness Estimator

The Brightness Estimator provides the value of the average field brightness of the picture. It can be used to hardware tune the two brightness correction functions (spectral processing and contrast enhancer).

Otherwise, a manual mode enables the CPU to force the average brightness value of the image.

#### 3.3.5 Histogram

47/

A high-resolution, non-linear histogram that uses 16 levels to characterize the image luminance is included.

The accumulation of the histogram is done through an entire field and is ready to be used at the next V sync signal. A window for histogram calculation can be selected for reducing the image size which will be used for histogram processing.

#### 3.3.6 Contrast Enhancer

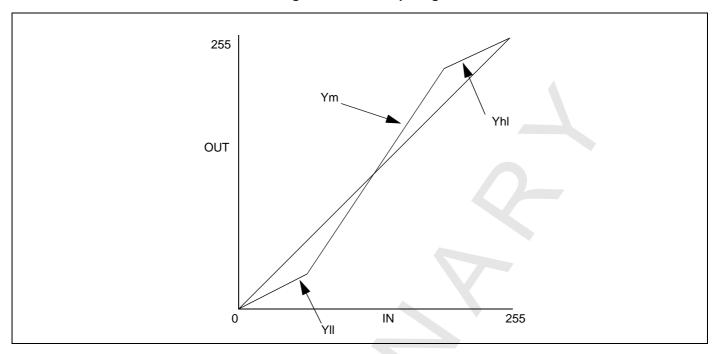

The luminance processing block works only on the low pass spectrum of the input signal.

All these algorithms are based on the same model (Figure 15) that uses three different segments for contrast modification: the high limit (Yhl), the low limit (Yll) and the middle segment (Ym).

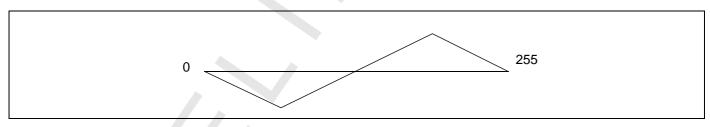

Figure 15: Yce = Ylp + Yg

- The Inflexion point is dependant either on the average brightness (when using brightness estimator values) or the input value (when using manual mode).

- The Range parameter modifies the slope of the Ym segment. Slope values are algorithmdependant.

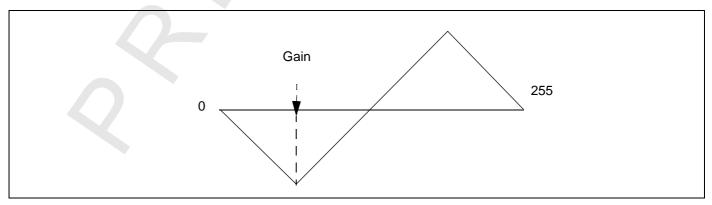

The Gain parameter modifies the overall curve gain in relation to the transfer curve (Yout = Yin).

Figure 17: Example Curve after applying a Gain Factor of 2

Table 9 shows the relation between the gain parameter and the gain factor values.

| Gain Parameter | Gain Factor | ] |

|----------------|-------------|---|

| 0              | 0.500       |   |

| 1              | 0.750       |   |

| 2              | 0.825       |   |

| 3              | 1.000       |   |

| 4              | 1.125       |   |

| 5              | 1.500       |   |

| 6              | 1.750       |   |

| 7              | 2.000       |   |

#### **Table 9: Gain Factor**

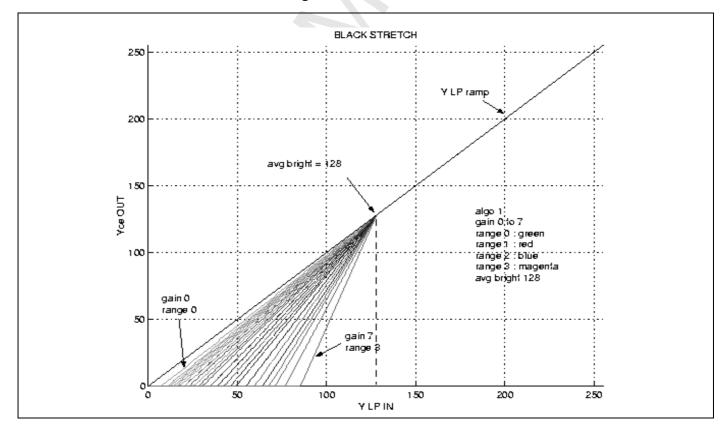

#### 3.3.6.1 Black Stretch

47/

The Black Stretch algorithm is used to decrease the black part under the average brightness point. The inflection point is based on the average brightness, but another value can be set by user. The range and gain parameters are used to set the correction slope value.

This filter can be used when the overall picture is bright in order to improve the overall contrast. Figure 18 shows samples of the black stretch algorithm with an average brightness of 128 with various gain and range values.

#### Figure 18: Black Stretch

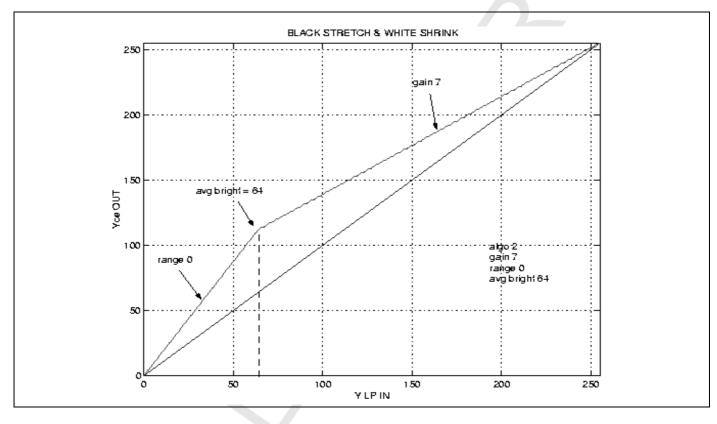

#### 3.3.6.2 White Stretch

The White Stretch algorithm is used on a dark sequence in order to increase the contrast on the entire image. By default, the inflexion point is based on the average brightness, but another value can be set by user. Two modes are available by setting the range parameter:

- 1. When Range = 0, the inflection point is based on the value the average brightness.

- 2. When Range = 1, 2 or 3, the inflexion point IS NOT BASED on the value of the average brightness, but is used as parameter for an extended set of possibilities.

The following figures shows various examples of the white stretch algorithm with the following values: Gain = 7, Range = 0 and an Average Brightness of 64.

#### Figure 19: White Stretch 1

Figure 20: White Stretch 2

Figure 21 shows the special case of range values of 1, 2 and 3 in which the inflexion point is set by the user and is not based on the value of the average brightness.

Figure 21: White Stretch 3

#### 3.3.6.3 Grey Stretch

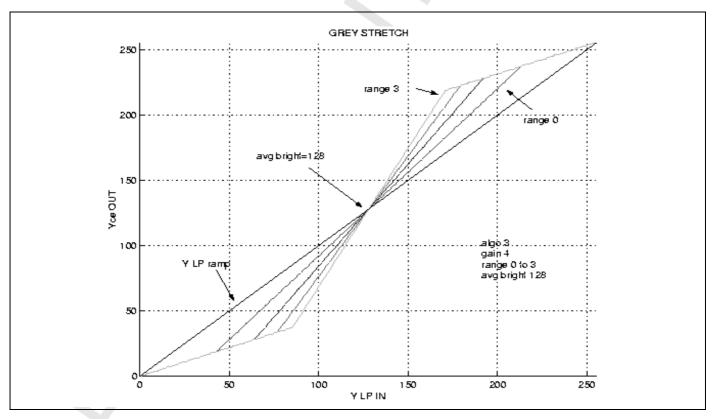

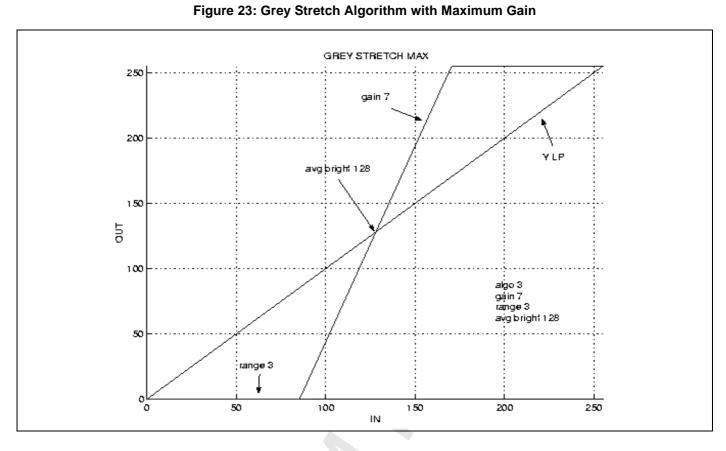

In Grey Stretch mode, the Black and White Stretch values are combined to increase the contrast in both the black and white parts of the image. This function decreases the black level in the dark part of the image and increases the white level in the bright part. It can be used to increase the global contrast on low-contrast sequences that are centered on the average brightness. By default, the inflection point is based on the value of the average brightness, but another value can be set by the user. In this case, the range parameter is used to modify the slope of the central segment.

| Range | Slope |  |

|-------|-------|--|

| 0     | 0.25  |  |

| 1     | 0.50  |  |

| 2     | 0.75  |  |

| 3     | 1.00  |  |

| Table 10: | Range | and | Slope | Values |

|-----------|-------|-----|-------|--------|

|-----------|-------|-----|-------|--------|

The gain parameter magnifies the correction factor and modifies the global curves in relation to the standard linear curve.

Figure 22 shows the grey stretch algorithm with various range values.

#### Figure 22: Grey Stretch

Figure 23 shows the grey stretch algorithm with the maximum gain value.

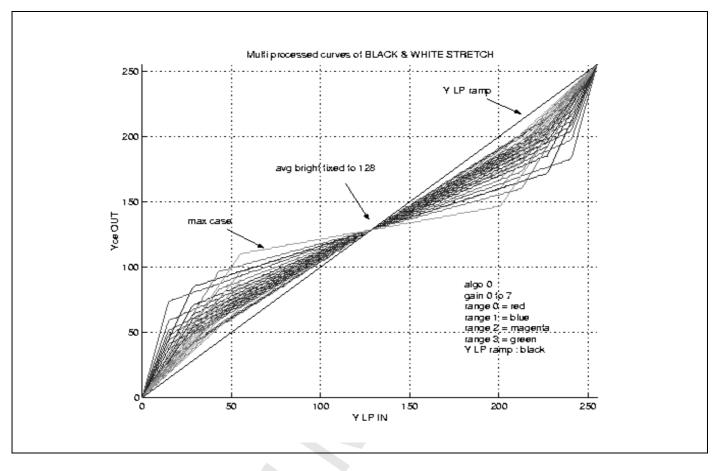

#### 3.3.6.4 Black & White Shrink

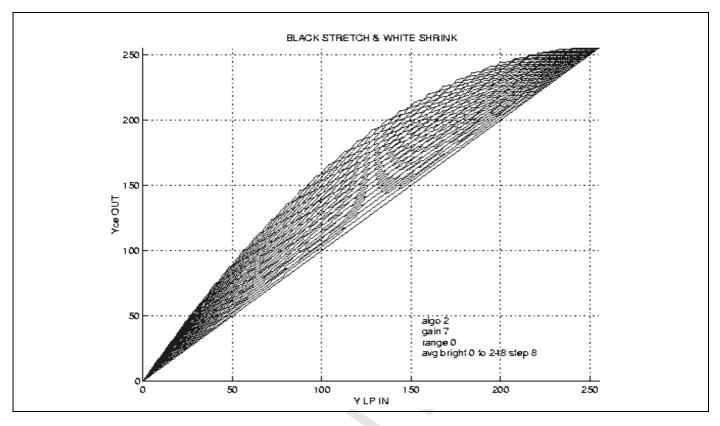

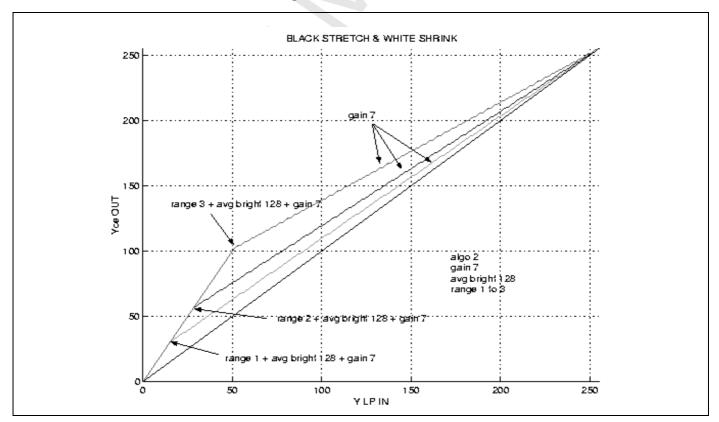

The Black and White Shrink function increases the black level in the dark part of the picture and decreases the white level in the bright part while maintaining the average brightness of the image. The inflection point is set at a value of 128 and cannot be seen.

This function is used to reduce the global contrast on an over-contrasted sequence or to reveal details in the dark and bright areas. The Black and White Shrink function acts in the opposite manner of the Grey Stretch function.

#### 3.3.7 Spectral Processing

#### 3.3.7.1 Adaptive Peaking

The luminance bandwidth must be improved when processing decoded composite signals and especially when a notch filter from the external digital video decoder is used. Luminance is improved in the STV3550 by adaptive peaking which increases the signal amplitude of a high-frequency spectrum.

This improves the outline of objects in a picture and increases the sharpness of the image.

Peaking effect is auto-adaptive and depends on image brightness.

In addition to the typical horizontal peaking, a vertical peaking mode can be selected in which vertical luminance components are used in the peaking algorithm. In this mode, vertical edges are also amplified. In this case, the vertical sharpness is much more sensitive to input noise and should be disabled.

#### 3.3.7.2 Coring

If certain noisy sources are input (RF broadcast or VCR, for example), noise may be present in the signal. To prevent peaking due to noise amplification, certain coring thresholds must be used to suppress any increase of small-amplitude high-frequency signals (noise). The coring effect is programmable from 0 to 16 LSB.

**ل\_م**ا

As an example, the strength of the peaking is adjustable up to 64 steps from 0 to +10 dB. The frequency peaking is adjustable from 1.5 MHz to 3.5 MHz by software (1H domain frequencies).

Coring is set using the coring level parameter which gives the strength of the noise suppression in 32 steps.

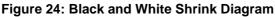

#### 3.3.8 Color Transient Improvement

Color Transient Improvement (CTI) is used to improve color transitions and chroma resolution. It uses a custom filter to enhance chroma transitions. Overshoots and undershoots of correction are suppressed to eliminate incorrect colors at the output of the algorithm. Also small amplitudes are not amplified and are further reduced to suppress noise amplification.

Figure 25 shows an example of step enhancement and noise pass through.

#### Figure 25: Step Enhancement and Noise Pass Through

# 4 Graphics Functional Description

Note: Some descriptions in this section are not applicable for LCD applications.

## 4.1 On-Screen Display Generator (OSD)

#### 4.1.1 General Information

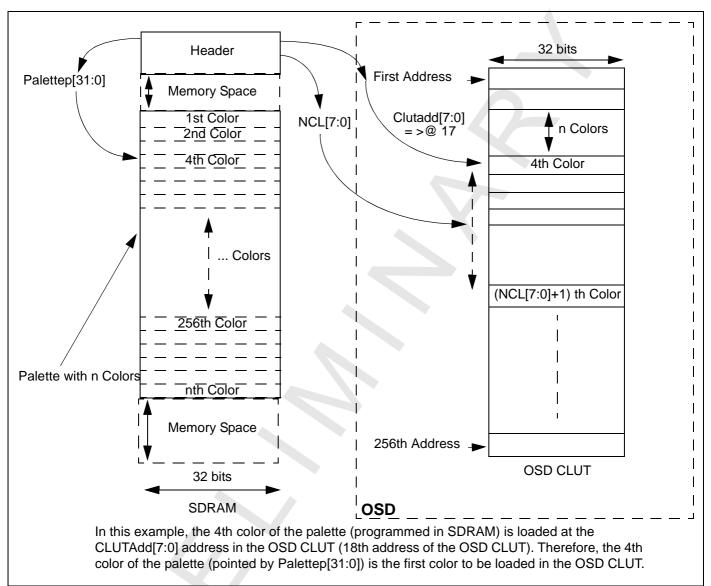

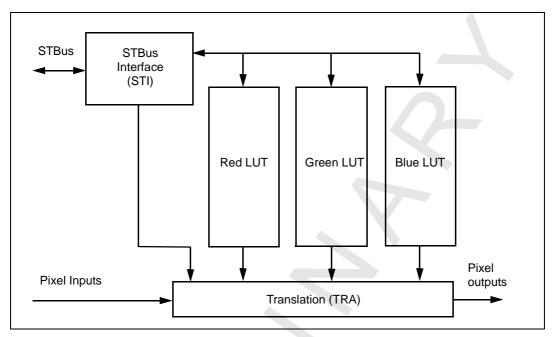

The On-Screen Display (OSD) unit is used to overlay the video image with graphics or Teletext information generated by software. The OSD pipeline uses color look-up tables (CLUTs) also called palettes, with an 8-bit input. The CLUTs can then generate 256 predefined colors that are stored in the external SDRAM. The CLUT also includes 8 bits for Transparency Mode control. The output from the CLUT is in ARGB 32-bit/pixel format (8-A, 8-R, 8-G, 8-B). The OSD plane can consist of several display regions. For each region, a different CLUT can be defined.

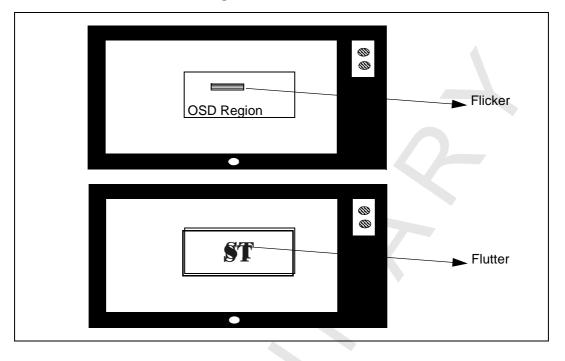

Before being mixed with the video signal, the OSD output can be filtered by Anti-Flicker and Anti-Flutter filters. These filters are used to build an OSD plane in Progressive mode and store it in a field-based format so that it may be displayed in Interlaced mode. Other display modes can be used for a full-page graphic plane: Progressive mode or Non-Interlaced mode.

#### 4.1.2 Main Features

- 8 bit per pixel Bitmap OSD with 10-bit RGB output resolution through a 32-bit CLUT

- Up to 1920 pixels per line and 1024 lines per field

- Capable of displaying Teletext 1.5 to 2.5, Teleweb and EPG applications

- 4 display planes (Video, Background, Graphics and Cursor) with mixing capabilities:

- Global, pixel-based and proportional mixing

- > Programmable 8-bit color-based mixing factor for anti-aliasing effect on character edges

- > Programmable 8-bit region-based mixing factor for transparency effect

- Interlaced or Progressive Display Mode

- Anti-Flicker and Anti-Flutter filters

- 2-D Graphics Accelerator

- Programmable RGB gain and offset

- Field- or frame-based storage

- Embedded display special effects controlled by software

- > Flash, Underline, Italics, Fringe, Rounding and Shadow

- > Vertical Scrolling

- Horizontal Scrolling

- Rolling Scrolling

- > Opening Window

### 4.1.3 Functional Description

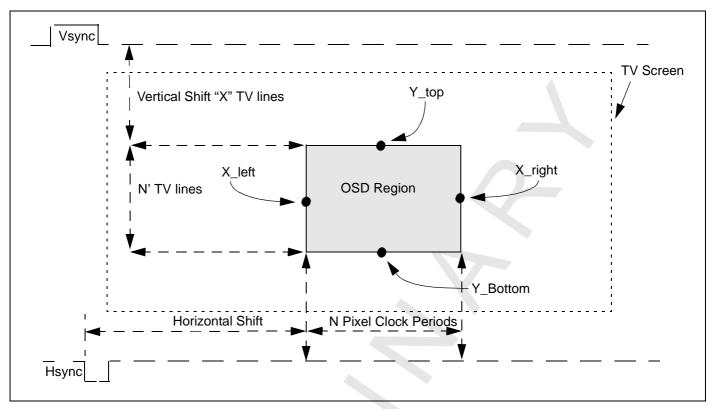

The OSD function displays a user-defined bitmap over any part of the displayable (i.e. non-blanked) screen, independent of the size and location of the active video area. This bitmap can be defined independently for each field. The OSD is enabled by setting the OSDON bit in the OSD\_CONFIG register. The OSD bitmap is defined in relation to the display region and is independent of the decoded picture size and any pan/scan offset.

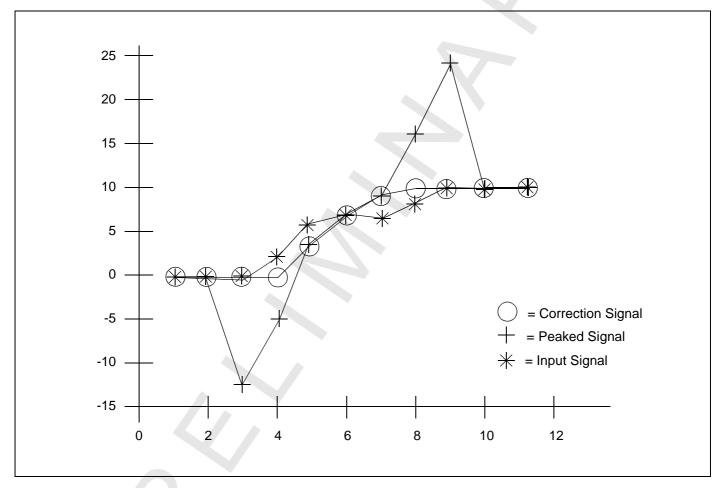

#### 4.1.3.1 OSD Display Regions

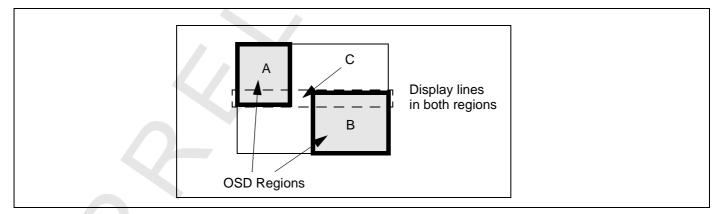

The OSD consists of one or more display regions. Each display region is rectangular and can have its own color palette and other properties. Three examples of OSD regions are shown in Figure 26. In this figure, Region 3 shows that an OSD region can be displayed outside the active video area.

A single display line cannot be included in more than one active OSD region, i.e. only one OSD region can be active on a single line. If two OSD regions are required to be displayed on the same display line, a new OSD region must be defined that includes both regions.

For example, in Figure 27, two different OSD regions (A and B) use some of the same display lines. If both OSD regions are to be active at the same time, a new region (C) must be defined including both regions A and B. The area of region C that is outside regions A and B can be defined as transparent.

#### Figure 27: Two Display Regions using the same Display Lines

### 4.1.4 Programming OSD Display Regions

**ل\_م**ا

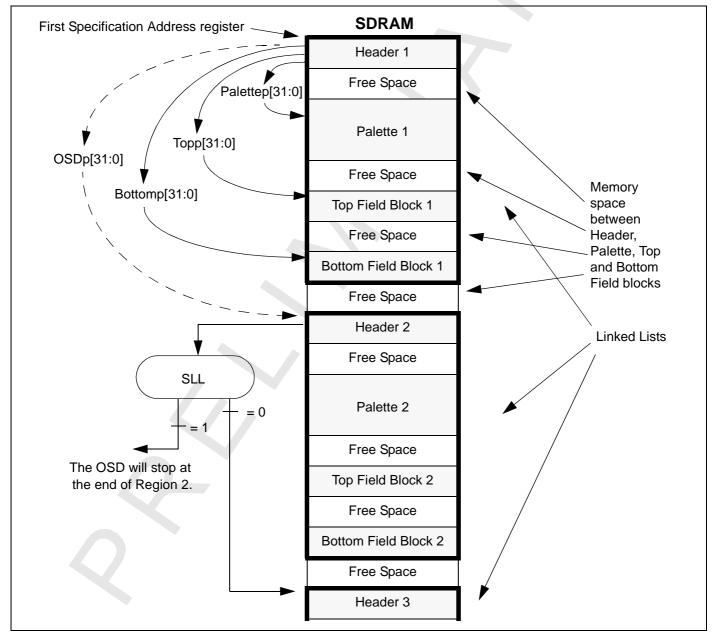

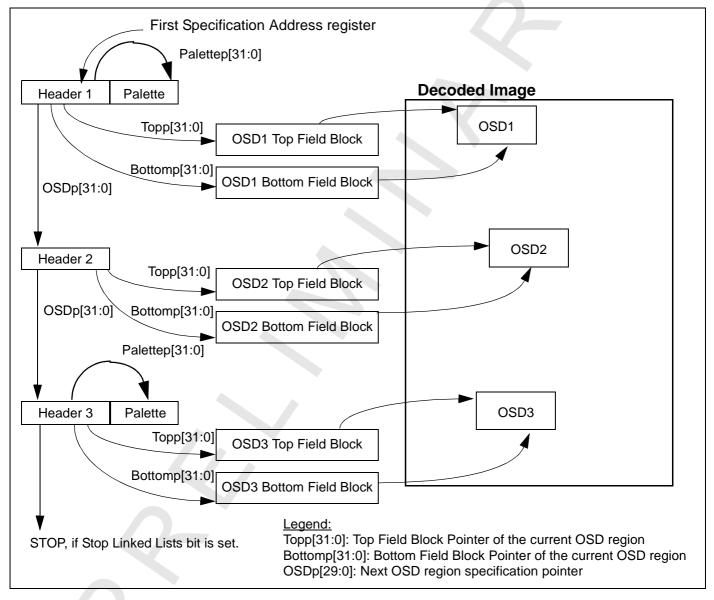

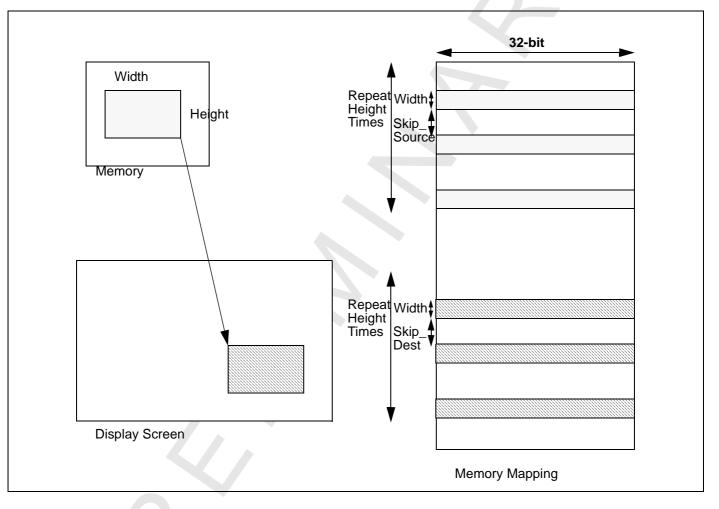

The characteristics of each OSD region are contained in an OSD specification which is stored in the 64-Mbit SDRAM. The following data is contained in the OSD specification:

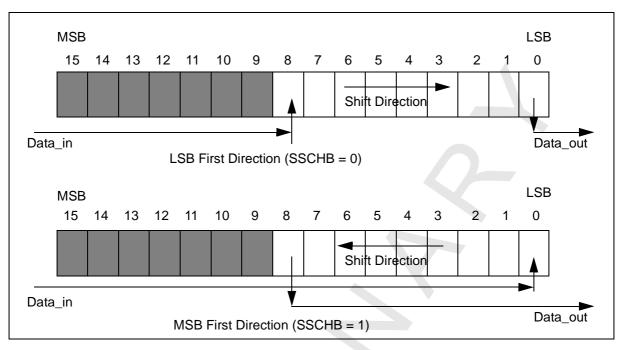

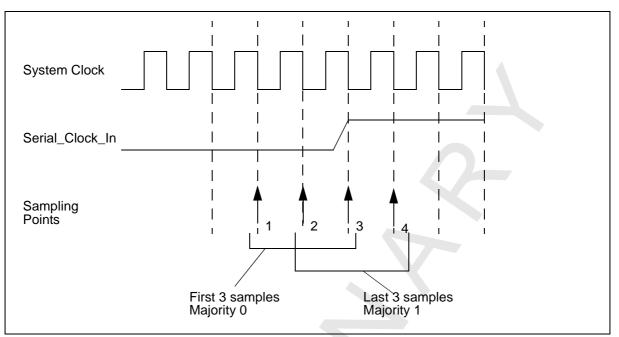

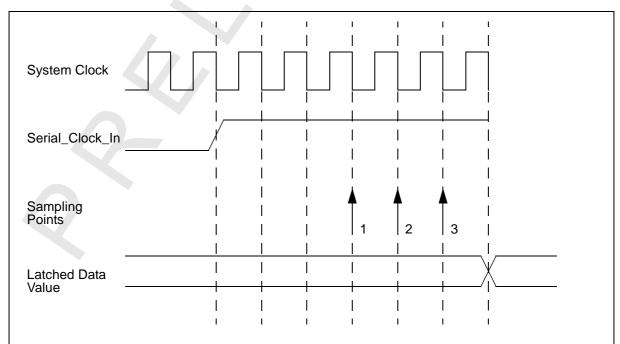

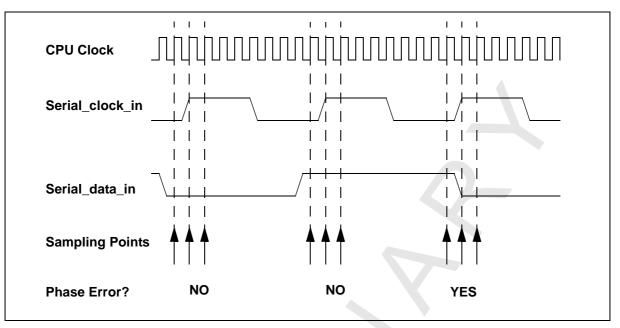

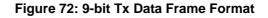

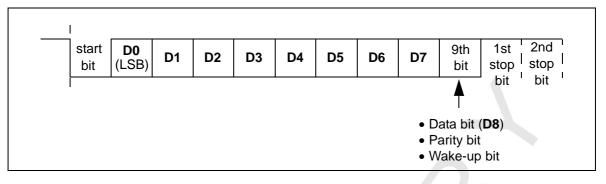

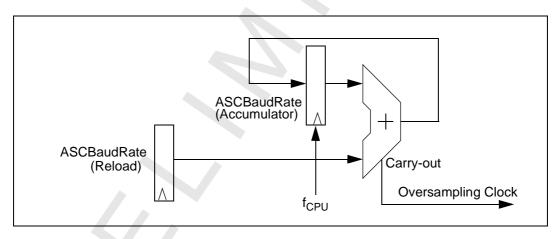

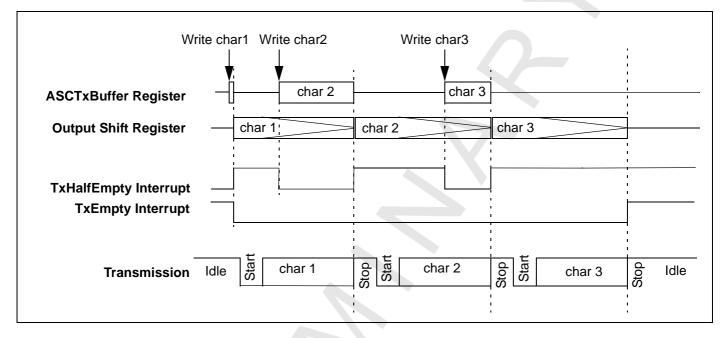

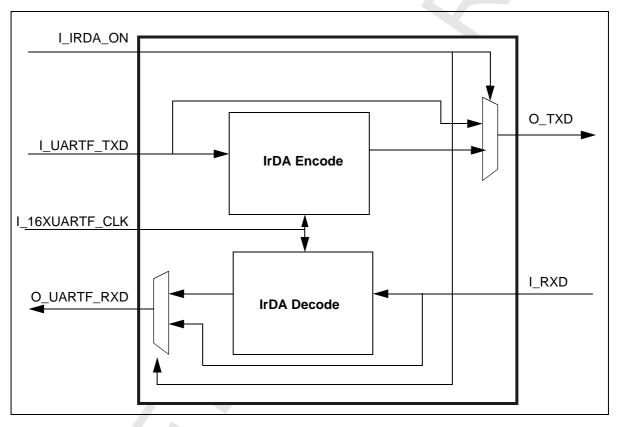

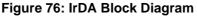

• A **header** which defines the boundaries of the region and contains 4 pointers that are used to identify the SDRAM location of the current palette, the current top block, the current bottom block, the next OSD region and other control information.