# Qi compatible wireless power transmitter for 5W applications with integrated full bridge

# Features

- WPC Qi 1.2.4 compatible Power Class 0 BPP

- Power Tx reference design based on A11a topology

- Up to 5W output power transfer on the receiver side

- Wide input voltage range 4.75V to 20V

- Monolithic solution with integrated Half-bridge/Full-bridge inverter and drivers for high efficiency and low BOM

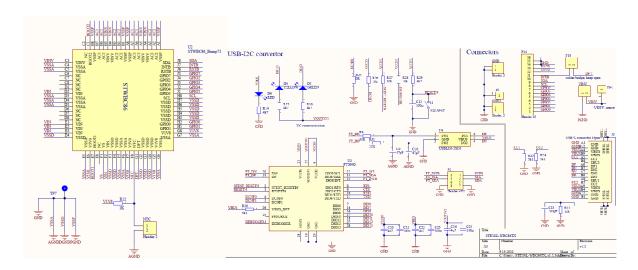

- 32-bit, 64MHz ARM Cortex micro controller with 8KB SRAM

- FTP (Few Times Programmable) for Firmware patching and advanced features

- On-chip current sense

- 10-bit A/D converter

- I<sup>2</sup>C interface

- · Fully Configurable GPIOs

- Accurate voltage/current measurements for FOD

- Current limit and Thermal protection

- Robust ASK,FSK communication

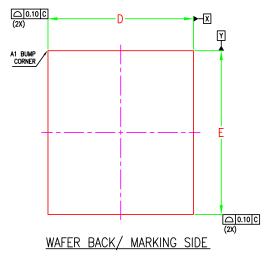

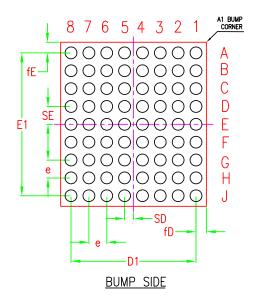

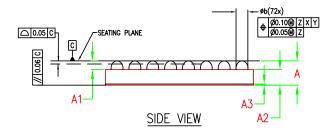

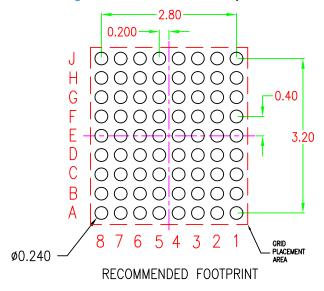

- Flip chip 72 bumps (3.26mm x 3.67mm)

#### Product status link

STWBC86

| Product summary |               |  |  |  |  |

|-----------------|---------------|--|--|--|--|

| Order code      | STWBC86JR     |  |  |  |  |

| Package         | WLCSP72       |  |  |  |  |

| Packing         | Tape and reel |  |  |  |  |

#### **Application**

- · Smartphone charging

- · Medical electronics

- · Smart Wearable, Hearable Charging

#### **Description**

The STWBC86 is a highly integrated monolithic wireless power transmitter solution suitable for applications up to 5W.

This solution requires low external BOM count. Because of the integrated low impedance Full/Half bridge inverter, STWBC86 achieves high efficiency and low power dissipation.

I<sup>2</sup>C interface allows firmware and platform parameters to be customized and the device can be configured using the embedded FTP.

Additional firmware patching also improves application flexibility of STWBC86.

The Flip Chip package and low BOM count make the device suitable for very compact applications.

#### 1 Introduction

STWBC86 is primarily a wireless power transmitter that provides up to 5W of power.

It offers the most flexible and efficient solution for controlling the power transfer to a receiver (RX) in applications such as smart phones, smart wearable, hearable devices that use electromagnetic induction for recharging.

The 32-bit core MCU is the supervisor of the whole device and manages all the functional blocks to

- establish and maintain communication with the receiver,

- optimize the efficiency by properly adjusting the operating point

- guarantee reliability by monitoring and protecting both the load and the device itself.

The Tx is responsible for controlling the transmitting coil and generating correct amount of power requested by

Transferring a correct amount of power ensures the highest level of end to-end efficiency due to reduced energy losses. It also helps maintaining a lower operational temperature.

The I<sup>2</sup>C interface provides access to the internal registers of the STWBC86 for applications in which the host system directly monitors or controls the power transfer.

The Tx can adapt to the amount of energy transferred by the coil by adjusting the frequency, duty cycle of the PWM voltage on the transmitting coil.

The power transmitter firmware is placed in ROM and is able to operate fully autonomously. This firmware is patchable with 8kB on-board FTP.

STWBC86 comes with a current limit and over-temperature protections to ensure safety of the device.

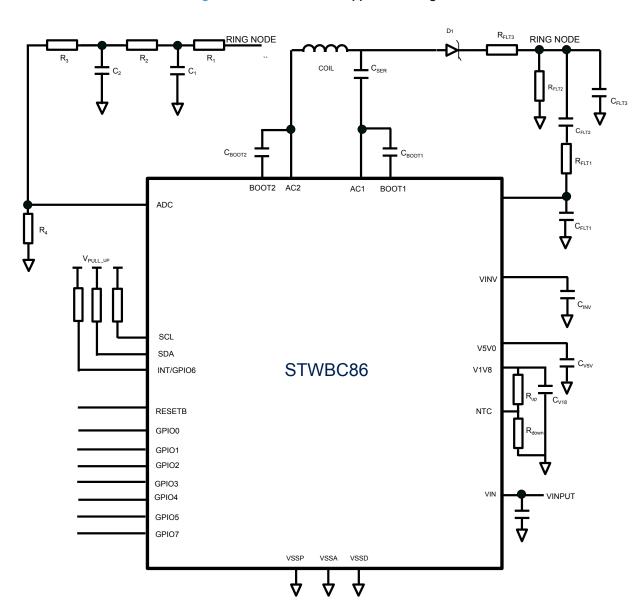

Figure below shows a block diagram of the device with simplified interconnections among the functional blocks.

The inverter converts the DC input voltage into an AC voltage, which is used to drive the coil. The four switches of the inverter (essentially an H-bridge) are controlled by the digital core in order to minimize both conduction and switching losses.

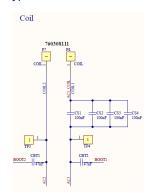

Two bootstrap capacitors are externally connected to the BOOT1-BOOT2 pins to correctly drive the high-side switches of the inverter.

VIN power supply is also the input rail for auxiliary linear regulators in charge of deriving the 5 V and 1.8 V supply voltages.

DS14079 - Rev 1 page 2/40

# 2 Block Diagram

Своот1 Своот2 BST1 BST2 CINV VINV Inverter V5V LDO vs ASK LDO Demod VIN ADC FTP SDA (config) Digital core (MCU) SCL RAMINT (code/data) RSTB, ROM (FW code) GPIOGPIOGPIO GPIO GPIO

Figure 1. Simplified block diagram

DS14079 - Rev 1 page 3/40

# **Device pinout**

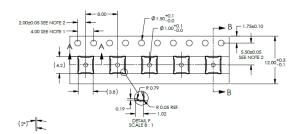

4 В С D Ε VSSD G VSSD VSSD VSSD Н GPIO2

Figure 2. Pin assignment (through top view)

Table 1. Pin description

| Pin name | Pin location                                     | Pin function                                                                                                                                                                                                                                                                         |  |  |  |

|----------|--------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|          | C4,C5,D3,D4,                                     |                                                                                                                                                                                                                                                                                      |  |  |  |

| VSSA     | D5,E5,F5,F6,                                     | Analog ground.                                                                                                                                                                                                                                                                       |  |  |  |

|          | G6,G7                                            |                                                                                                                                                                                                                                                                                      |  |  |  |

| VSSD     | E4, F3, F4, G2, G3,<br>G4, H3, H4, H5, H6,<br>H7 | Digital ground. Reference for digital input and output signals.                                                                                                                                                                                                                      |  |  |  |

| VSSP     | A1, A8, B1, B8                                   | Power ground. Power return for the inverter.                                                                                                                                                                                                                                         |  |  |  |

| AC1      | A6, A7, B6, B7                                   | AC power input: Output of the inverter. Connect to the Tx series resonant circuit.                                                                                                                                                                                                   |  |  |  |

| AC2      | A2, A3, B2, B3                                   | AC power input: Output of the inverter. Connect to the Tx series resonant circuit.                                                                                                                                                                                                   |  |  |  |

| BOOT1    | E7                                               | Inverter bootstrap capacitor, connect a 47 nF (typical) ceramic capacitor between this pin and AC1.                                                                                                                                                                                  |  |  |  |

| BOOT2    | C1                                               | Inverter bootstrap capacitor, connect a 47 nF (typical) ceramic capacitor between this pin and AC2.                                                                                                                                                                                  |  |  |  |

| VINV     | A4, A5, B4,                                      | Inverter input supply. A suitable capacitor between these pins and VSSP ensures                                                                                                                                                                                                      |  |  |  |

| VIIIV    | B5, C3                                           | residual AC ripple filtering.                                                                                                                                                                                                                                                        |  |  |  |

| VS       | F1                                               | ASK demodulation input. (optional) ADC in: Ring node voltage input used for FOD                                                                                                                                                                                                      |  |  |  |

| ADC      | G1                                               | ASK demodulation input. (optional) ADC in. King node voltage input used for POD                                                                                                                                                                                                      |  |  |  |

| NTC      | F8                                               | Coil temperature sensing input: connect to the center tap of a resistor divider having an NTC in the low-side position. If this function is not used, the pin must be pulled-up to V1V8 through a 10 k $\Omega$ resistor to prevent triggering the coil over-temperature protection. |  |  |  |

| VIN      | D2, E1, E2,<br>E3, F2                            | Power supply input. Connect a suitable filtering capacitor between these pins and ground to ensure stable operation and proper load transient response in all operating conditions.                                                                                                  |  |  |  |

page 4/40

| Pin name   | Pin location                   | Pin function                                                                                                                                                              |  |  |  |

|------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| V1V8       | G5, G8                         | 1.8V LDO output and supply rail for the digital core, the ADC and the analog circuit Connect a 1 $\mu$ F filtering capacitor between this pin and ground.                 |  |  |  |

| V5V0       | F7, E6                         | 5V LDO output and supply rail for the auxiliary circuitry. Connect a 4.7 $\mu$ F filtering capacitor between this pin and ground.                                         |  |  |  |

| RSTB       | J6                             | Chip-reset input. If set low, the internal digital core is reset. This pin can also be use by the host controller to control the power transfer process.                  |  |  |  |

| SCL        | H8                             | I2C bus, clock line input. A pull-up resistor to the supply rail of the host controller is                                                                                |  |  |  |

| SDA        | J8                             | required to ensure correct digital levels. I2C bus, data line I/O. A pull-up resistor to supply rail of the host controller is required to ensure correct digital levels. |  |  |  |

| GPI00      | H2                             |                                                                                                                                                                           |  |  |  |

| GPIO1      | H1                             |                                                                                                                                                                           |  |  |  |

| GPIO2      | J4                             |                                                                                                                                                                           |  |  |  |

| GPIO3      | J3                             | Programmable general-purpose I/Os: the function of these pins depends on the configuration of the device.                                                                 |  |  |  |

| GPIO4      | J2                             |                                                                                                                                                                           |  |  |  |

| GPIO5      | J1                             |                                                                                                                                                                           |  |  |  |

| GPIO7      | J5                             |                                                                                                                                                                           |  |  |  |

| INTB/GPIO6 | J7                             | Interrupt output (active low). Programmable open-drain output used to generate an interrupt on specific events for the host controller.                                   |  |  |  |

| NC         | C2,C6,C7,C8,<br>D1,D6,D7,D8,E8 | Not connected pins , to be left floating.                                                                                                                                 |  |  |  |

DS14079 - Rev 1 page 5/40

### 4 Electrical and thermal specifications

#### 4.1 Absolute maximum ratings

Stresses beyond those listed in Table 2 may cause permanent damage to the device. These are stress ratings only and operation of the device at these or any other condition above those indicated in Table 2 is not implied. Exposure to absolute maximum rated conditions for extended periods may affect device reliability.

Table 2. Absolute maximum ratings

| Parameter              | Pin(s)                                                                                       | Min. | Max. | Unit |

|------------------------|----------------------------------------------------------------------------------------------|------|------|------|

|                        | AC1, AC2 respect to ground (VSSA, VSSD and VSSP pins)                                        | -0.9 | 27   |      |

|                        | BOOT1 to AC1                                                                                 | -0.3 | 5.5  |      |

|                        | BOOT2 to AC2                                                                                 | -0.3 | 5.5  |      |

|                        | BOOT1 and BOOT2 respect to ground (VSSA, VSSD and VSSP pins)                                 | -0.3 | 27   |      |

| Pin voltage range      | VINV, VIN respect to ground (VSSA, VSSD and VSSP pins)                                       | -0.7 | 27   | V    |

|                        | V1V8, NTC, VS and ADC respect to ground (VSSA, VSSD and VSSP pins)                           | -0.3 | 1.98 |      |

|                        | V5V0 respect to ground (VSSA, VSSD and VSSP pins)                                            | -0.7 | 5.5  |      |

|                        | GPIO0 through GPIO5,GPIO7, INTB, RSTB, SDA, SCL respect to ground (VSSA, VSSD and VSSP pins) | -0.7 | 5.5  |      |

|                        | Relative voltage between any ground pin (VSSA, VSSD, VSSP)                                   | -0.3 | 0.3  |      |

| RMS Current            | AC1,AC2,VINV                                                                                 |      | 2.0  | А    |

| HBM ESD susceptibility | All pins                                                                                     |      | 2000 | V    |

| JEDEC JS001-2012       | All pills                                                                                    |      | 2000 | V    |

| CDM ESD susceptibility |                                                                                              |      | 500  |      |

| JEDEC JS002-2012       |                                                                                              |      | 300  |      |

| Latch-Up EIA/JESD78E   |                                                                                              | -200 | 200  | mA   |

#### 4.2 Thermal characteristics

Table 3. Thermal characteristics

| Symbol                           | Parameter                              | Conditions | Min. | Тур. | Max. | Unit |

|----------------------------------|----------------------------------------|------------|------|------|------|------|

| T <sub>A,OP</sub> <sup>(1)</sup> | Operating ambient temperature          |            | -40  |      | 85   | °C   |

| T <sub>J,OP</sub>                | Operating junction temperature         |            | 0    |      | 125  |      |

| R <sub>OJA</sub> <sup>(2)</sup>  | Junction to ambient thermal resistance | 2s2p       |      | 47   |      | °C/W |

<sup>1.</sup> Ta -40°C to 85°C, limits over the operating temperature range and relevant supply voltage range are guaranteed by design and characterization, if not otherwise specified.

DS14079 - Rev 1 page 6/40

<sup>2.</sup> Device mounted on a standard JESD51-5 test board

#### 4.3 Electrical characteristics

0 °C <  $T_A$  < 85 °C;  $V_{VINPUT}$  = 5 V to 10 V. Typical values are at  $T_J$  = 25 °C, if not otherwise specified.

**Table 4. Electrical characteristics**

| Symbol                | Parameter                                            | Test Conditions                                                    | Min. | Тур. | Max. | Unit |

|-----------------------|------------------------------------------------------|--------------------------------------------------------------------|------|------|------|------|

| Supply section        |                                                      |                                                                    |      |      |      |      |

| V <sub>VIN,UVLO</sub> | VIN Under-Voltage Lock-Out upper (turn-on) threshold | VIN pin voltage, rising edge                                       |      | 3.0  | 3.3  | V    |

| $V_{VIN,MAX}$         | VIN maximum operating supply voltage                 | Voltage on VIN pin                                                 |      |      | 20   | V    |

| I <sub>VIN,Q</sub>    | VIN current consumption in shut-down mode            | RSTB low for more than 1 ms, supply voltage (5 V) applied to VIN   |      | 400  | 750  | μА   |

| I <sub>VIN,OP</sub>   | Operating current consumption                        | RSTB high, supply voltage applied to VIN                           |      | 14.7 |      | mA   |

| I.8V supply volta     | age LDO linear regulator                             |                                                                    |      |      |      |      |

| .,,                   | LDO output voltage                                   | I <sub>V1V8</sub> = 5 mA                                           | 1.79 | 1.8  | 1.81 | V    |

| $V_{V1V8}$            | LDO load regulation                                  | 0 mA < I <sub>V1V8</sub> < 10 mA                                   |      | 5    | 20   | mV   |

| 5V supply voltag      | e LDO linear regulator                               |                                                                    |      | ı    |      |      |

|                       | LDO output voltage                                   | I <sub>V5V0</sub> = 5 mA                                           | 4.8  | 5    | 5.2  | V    |

| $V_{V5V0}$            | LDO load regulation                                  | 0 mA <i<sub>V5V0 = 0 mA &lt;10 mA</i<sub>                          |      | 2    | 20   | mV   |

|                       | LDO UVLO upper threshold                             |                                                                    | 2.8  | 3    | 3.2  | V    |

| I <sub>V5V0,EXT</sub> | Maximum current with external load                   |                                                                    |      |      | 15   | mA   |

| nverter               |                                                      |                                                                    |      |      |      |      |

| Efficiency            | Torque roctifier officiency                          | $I_{VINV}$ = 1 A, $V_{VIN}$ = 5.2 V, $f_{AC}$ = 100 kHz to 250 kHz |      | 97   |      | 0/   |

|                       | Target rectifier efficiency                          | $I_{VIN}$ = 1 A, $V_{VIN}$ = 9.2 V, $f_{AC}$ = 100 kHz to 250 kHz  |      | 97   |      | %    |

| F <sub>FREQ</sub>     | Inverter frequency range                             |                                                                    | 100  |      | 500  | KHZ  |

| V <sub>IN</sub>       | Input voltage range                                  | VIN                                                                | 4.95 |      | 20   | V    |

| I <sub>SENSE</sub>    | Input current sense range                            |                                                                    | 0    |      | 2500 | mA   |

| Micro controller      |                                                      |                                                                    |      | 1    |      |      |

| Architecture          | Arm® Cortex®                                         |                                                                    |      | 32   |      | bit  |

| RAM                   | RAM Size                                             |                                                                    |      | 8    |      | KB   |

| ew Times Progr        | rammability                                          |                                                                    |      |      |      |      |

| FTP                   | Memory size for configuration and firmware patch     |                                                                    |      | 8    |      | KB   |

| Clock generator       |                                                      |                                                                    |      |      |      |      |

| Fosc                  | Clock generator & PWM timer frequency                |                                                                    |      | 64   |      |      |

| F <sub>OSC_TOL</sub>  | Tolerance of the clock generator frequency           |                                                                    | -4   |      | +4   | %    |

| Digital signals       | <u> </u>                                             |                                                                    |      |      |      |      |

| V <sub>IL</sub>       | Low level input voltage                              |                                                                    |      |      | 0.55 |      |

| V <sub>IH</sub>       | High level input voltage                             |                                                                    | 1.14 |      |      | V    |

| V <sub>OH</sub>       | GPIOx high level output voltage                      | Output high, I <sub>SOURCE</sub> = 3mA                             | 1.25 |      |      |      |

DS14079 - Rev 1 page 7/40

| Symbol          | Parameter                    | Test Conditions                    | Min. | Тур. | Max. | Unit |

|-----------------|------------------------------|------------------------------------|------|------|------|------|

| I <sub>OH</sub> | GPIOx pin current capability | Output high                        | 3    |      |      | mA   |

| V <sub>OL</sub> | Low level output voltage     | Output low, I <sub>SINK</sub> =3mA |      |      | 0.4  | V    |

DS14079 - Rev 1 page 8/40

### 5 Device description

#### 5.1 Wireless power interface

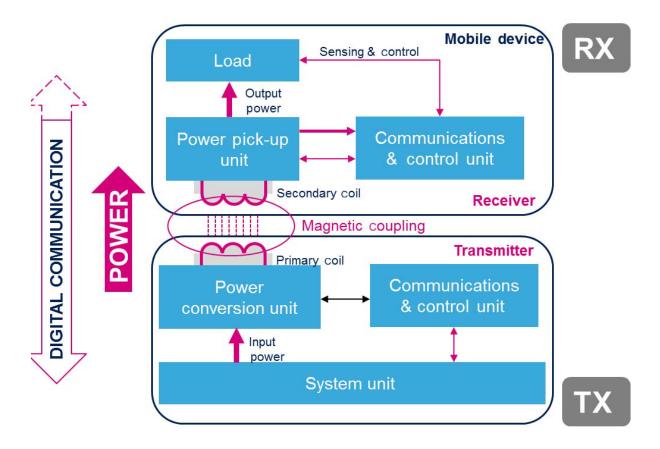

Wireless charging system diagram is shown below. The key blocks are Inverter (Power conversion unit), Communications and Control unit.

The Tx is responsible for controlling the transmitting coil and transferring the correct amount of power requested by the Rx.

The Rx modulates the power signal using resistive and capacitive load to communicate to the Tx requested power level.

Transferring the correct amount of power ensures the highest level of end to-end efficiency due to reduced energy losses. It also helps maintaining a lower operational temperature.

The Tx can adapt to the amount of energy transferred by the coil by adjusting the frequency, duty cycle of the PWM voltage on the transmitting coil.

Figure 3. Wireless charging system

#### 5.2 Inverter

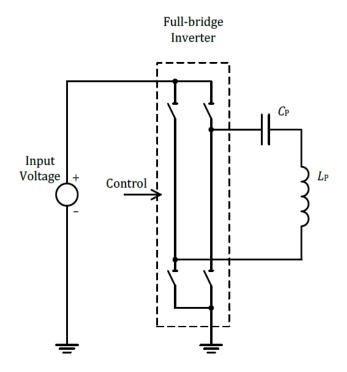

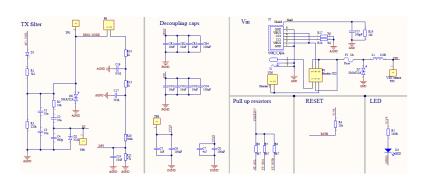

The power transmitter design uses a Full bridge inverter to drive the primary coil and series capacitance. The power transmitted to the coil is regulated by varying switching frequency and/or duty cycle of the bridge.

A higher operating frequency (for example 200kHz) leads to lower transmitted power, while a lower frequency (for example 110kHz) leads to higher transmitted power.

The LC resonant circuit optimization to be done based on power transfer requirements.

Full bridge inverter circuit is shown below.

DS14079 - Rev 1 page 9/40

Figure 4. Full bridge inverter

Typical Operating Frequency range of the full-bridge inverter is op =  $120 \dots 148 \text{ kHz}$ , duty cycle range 10% to 50%.

Primary Coil and Shielding has a self-inductance P = 6.3±10% µH.

The value of the series capacitance is P =0.4 $\pm$ 5%  $\mu$ F.

The input voltage to the full-bridge inverter is  $5\pm5\%$  V.

#### 5.3 ASK communication

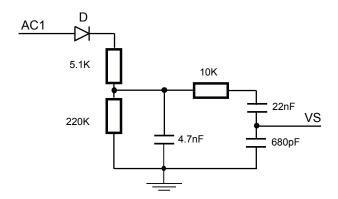

Robust and reliable in-band ASK communication is critical to the operation of any Qi compliant devices.

Using ASK modulation, the receiver sends Control Error Packets (CEP) to tune the operating point to match load requirements.

The coil signal is demodulated using a circuit shown below and fed to the VS pin of STWBC86.

Figure 5. ASK demodulation filter circuit

DS14079 - Rev 1 page 10/40

#### 5.4 Chip reset pin

The RSTB pin, active low, can block operation of the device by forcing the digital core in reset state. After releasing the reset pin, STWBC86 can resume normal operation mode.

#### 5.5 GPIOx and INTB pins

The GPIO0 through GPIO7 pins are programmable general-purpose I/O pins. These pins can be configured as inputs or outputs (push-pull or open-drain) according to the selected function.

The INTB(GPIO6) pin is an interrupt output line that can be associated to any internal interrupt condition and used to inform the host system about specific events.

#### 5.6 Device protections

Input voltage and input current are monitored by an internal ADC.

Both input voltage and input current can be limited by setting OVP and OCP thresholds.

Exceeding either threshold triggers a corresponding protection.

Internal temperature is also measured using the internal ADC and it's threshold can be set in °C.

When the internal temperature exceeds the set threshold, the OTP protection is triggered.

DS14079 - Rev 1 page 11/40

#### 6 I2C interface

The STWBC86 can operate fully independently, i.e. without being interfaced with a host system.

In applications in which the STWBC86 has to be a part of peripherals managed by the host system, the two SDA and SCL pins could be connected to the existing I<sup>2</sup>C bus.

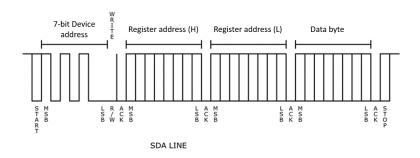

The device works as an I<sup>2</sup>C slave and supports standard (100 kbps) fast (400 kbps) data transfer modes.

The STWBC86 has been assigned 0x61, a 7-bit hardware address. The pull-up resistors should be selected as a trade-off between communication speed (lower resistors lead to faster edges) and data integrity (the input logic levels have to be guaranteed to preserve communication reliability).

When the bus is idle, both SDA and SCL lines are pulled HIGH.

#### **Data Validity**

The data on the SDA line must be stable during the high period of the clock. The high and low states of the SDA line can only change when the SCL clock signal is low.

#### **Start and Stop Conditions**

Both the SDA and the SCL lines remain high when the I<sup>2</sup>C bus is not busy. A START condition is a high-to-low transition of the SDA line when SCL is HIGH, while the STOP condition is a low-to-high transition of the SDA line when SCL is HIGH. A STOP condition must be sent before each START condition.

SDA

SCL

START condition

STOP condition

Figure 6. Start and Stop Condition on the I2C Bus

#### **Byte format**

Every byte transferred over the SDA line must contain 8 bits. Each byte received by the STWBC86 generally is followed by an acknowledge (ACK) bit. The MSB is transferred first. One data bit is transferred during each clock pulse. The data on the SDA line must remain stable during the high state of each SCL clock pulse.

The device generates the ACK pulse (by pulling-down the SDA line during the acknowledge clock pulse) to confirm the correct device address or received data bytes.

#### Interface protocol

The interface protocol consists of

- Start condition (START)

- 7-bit device address (0x61) + R/W bit (read = 1 / write = 0)

- Register pointer, high-byte

- · Register pointer, low-byte

- Data sequence: N x (data byte + ACK)

- Stop condition (STOP)

The register pointer (or address) byte defines the destination register to which the read or write operation applies. When the read or write operation is finished, the register pointer is automatically incremented.

DS14079 - Rev 1 page 12/40

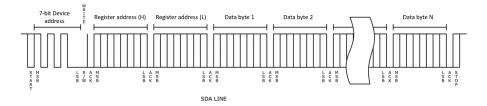

#### Writing to a single register

Writing to a single register begins with a START condition followed by device address 0xC2 (7-bit device address plus R/W bit cleared), two bytes of the register pointer and the data byte to be written in the destination register. Each transmitted byte is acknowledged by the STWBC86 through an ACK pulse.

Figure 7. Writing to single register byte

#### Writing to multiple registers (page write)

The STWBC86 supports writing to multiple registers with auto-incremental addressing. When data is written into a register, the register pointer is automatically incremented, therefore transferring data to a set of subsequent registers (also know as page write) is a straightforward operation.

Figure 8. Writing multiple register bytes

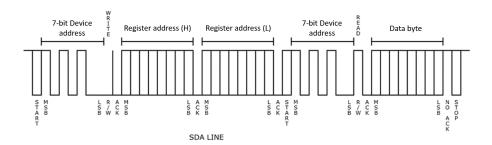

#### Reading from a single register

Reading from a single register begins with a START condition followed by the device address byte 0xC2 (7-bit device address plus R/W bit cleared) and two bytes of register pointer, then a re-START condition is generated and the device address 0xC3 (7-bit device address plus R/W bit asserted) is sent, followed by data reading. ACK pulse is generated by the STWBC86 at the end of each byte, but not for data bytes retrieved from the register. A STOP condition is finally generated to terminate the operation.

Figure 9. Reading single register byte

DS14079 - Rev 1 page 13/40

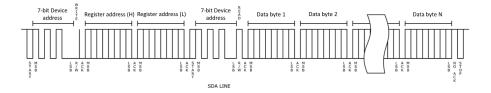

#### Reading from multiple registers (page reading)

Similarly to multiple (page) writing, reading from subsequent registers relies on an auto-increment of the register: the master can extend data reading to the following registers by generating and an ACK pulse at the end of each byte. Data reading starts immediately and the stream is terminated by a NMAK pulse at the end of the last data byte, followed by a STOP condition.

Figure 10. Reading multiple bytes

DS14079 - Rev 1 page 14/40

# 7 I<sup>2</sup>C register map

The STWBC86 can be monitored and controlled by accessing the internal registers via  $I^2C$  interface. The following registers map reports the accessible addresses. Addresses not shown in the map and blank bits have to be considered reserved and not altered as well.

Table 5. Register abbreviations

| Register type | Description                 |

|---------------|-----------------------------|

| R/W           | can read and write the bits |

| R             | can read only               |

| W             | can write only              |

**Table 6. Chip information**

| Address          | Register name    | R/W | Default | Description                                    |

|------------------|------------------|-----|---------|------------------------------------------------|

| 0x0000           | Chip ID Low      | R   | 0x56    | Chip ID [70]                                   |

| 0x0001           | Chip ID High     | R   | 0x00    | Chip ID [158]                                  |

| 0x0002           | Chip revision    | R   | 0x02    | Chip revision [70]                             |

| 0x0003           | Customer ID      | R   | 0x00    | Customer ID [70]                               |

| 0x0004           | ROM ID           | R   | 0x18    | ROM ID [70]                                    |

| 0x0005           | ROM ID           | R   | 0x01    | ROM ID [158]                                   |

| 0x0006           | NVM Patch ID     | R   | -       | NVM patch ID [70]                              |

| 0x0007           | NVM Patch ID     | R   | -       | NVM patch ID [158]                             |

| 0x000A           | Configuration ID | R   | -       | Configuration ID [70]                          |

| 0x000B           | Configuration ID | R   | -       | Configuration ID [158]                         |

| 0x000C           | Production ID    | R   | 0x07    | PE ID [70]                                     |

| 0x000E           | Operation mode   | R   | 0x03    | 0x1: Standalone (debug) mode ; 0x3: Qi TX mode |

| 0x00100<br>x001F | Device ID        | R   | -       | Device ID Bytes 015                            |

**Table 7. System information**

| Address | Register name         | R/W | Default | Description                     |

|---------|-----------------------|-----|---------|---------------------------------|

|         |                       |     |         | Bit 0: Switch to TX command     |

| 0x0020  | 0x0020 System command | RW  | -       | Write 1 to switch to Qi TX mode |

|         |                       |     |         | Bit 17 Reserved                 |

|         |                       |     |         | Bit 0: Core hard fault error    |

|         |                       | R   |         | 0: No hard fault error detected |

|         |                       |     |         | 1: Hard fault error detected    |

| 0x002C  | System error          | R   |         | Bit 1: HW WDT trigger latch     |

| 0x0020  | System end            |     |         | 0: HW WDT not triggered         |

|         |                       |     |         | 1: HW WDT triggered             |

|         |                       | R   |         | Bit 2: FTP IP error             |

|         |                       | K   | -       | 0: No FTP IP error detected     |

DS14079 - Rev 1 page 15/40

| Address | Register name                           | R/W | Default | Description                               |

|---------|-----------------------------------------|-----|---------|-------------------------------------------|

|         |                                         |     |         | 1: FTP IP error detected                  |

|         | _                                       | R   | -       | Bit 4: FTP Boot error                     |

|         |                                         |     |         | Bit [98] FTP PE error                     |

|         |                                         |     |         | 0: No error                               |

|         |                                         | R   | -       | 1: Section header error                   |

|         |                                         |     |         | 2: Section CRC failed                     |

|         |                                         |     |         | 3: Reserved                               |

|         |                                         |     |         | Bit [1110] FTP Configuration error        |

|         |                                         |     |         | 0: No error                               |

|         |                                         | R   | -       | 1: Section header error                   |

| 0x002C  | System error                            |     |         | 2: Section CRC failed                     |

|         | , , , , , , , , , , , , , , , , , , , , |     |         | 3: Reserved                               |

|         |                                         |     |         | Bit [1312] FTP Patch error                |

|         |                                         |     | R -     | 0: No error                               |

|         |                                         | R   |         | 1: Section header error                   |

|         |                                         |     |         | 2: Section CRC failed                     |

|         |                                         |     |         | 3: Reserved                               |

|         |                                         |     |         | Bit[1514]FTP Production Information error |

|         |                                         |     |         | 0: No error                               |

|         |                                         | R   | -       | 1: Section header error                   |

|         |                                         |     |         | 2: Section CRC failed                     |

|         |                                         |     |         | 3: Reserved                               |

#### **Table 8. Commands**

| Address | Register name | R/W | Default | Description                                                 |

|---------|---------------|-----|---------|-------------------------------------------------------------|

| 0x0020  | TX EN         | RW  | -       | Bit 0: Switch to TX command Write 1 to switch to Qi TX mode |

#### Table 9. Mode monitor

| Address | Register name   | R/W | Default | Description                    |

|---------|-----------------|-----|---------|--------------------------------|

| 0x0040  | VINV Byte 01    | R   |         | Inverter voltage in mV [70]    |

| 0x0041  | VIIV Byte U I   | K   | -       | [158]                          |

| 0x0042  | VIN Byte 01     | R   |         | Main Voltage input in mV [70]  |

| 0x0043  | VIIN Byte U I   | R   | -       | Main Voltage input in mV [158] |

| 0x0044  | TX ICUR Byte 01 | R   | -       | Input current in mA [70]       |

| 0x0045  |                 |     |         | [158]                          |

| 0x0046  | TMEAS Byte 01   | R   | -       | Chip temperature in deg C [70] |

| 0xx0047 | TWEAS Byle U I  |     |         | [158]                          |

| 0x0048  | NTC Byte 01     | R   | -       | NTC measurement [70]           |

| 0x0049  | INTO Byle U I   |     |         | [158]                          |

| 0x004A  | ADC IN Byte 01  | R   | -       | ADC IN Measurement [70]        |

DS14079 - Rev 1 page 16/40

map

| Address | Register name       | R/W | Default | Description                                         |

|---------|---------------------|-----|---------|-----------------------------------------------------|

| 0x004B  | ADC IN Byte 01      | R   | -       | [158]                                               |

| 0x004C  | OP FREQ             | R   |         | Operating frequency specified in units of 4kHz [70] |

| 0x004D  | OP FREQ             | K   | -       | [158]                                               |

| 0x006E  | POWER RX Byte 01    | R   | -       | RX received power in mW [70]                        |

| 0x006F  |                     |     |         | [158]                                               |

| 0x0070  | DOWED TV D. 4- 0. 4 | R   | -       | Power transmitted to RX [70]                        |

| 0x0071  | POWER TX Byte 01    |     |         | [158]                                               |

| 0x0072  | POWER RPP           | R   | -       | Last value sent in received power packet [70]       |

| 0x0073  | FOWLKKEF            |     |         | [158]                                               |

| 0x0074  | RECENT CEP          | R   |         | Last CEP value received from RX [70]                |

| 0x0075  | RECEIVI CEF         | K   | -       | [158]                                               |

| 0x0076  | SIG STREN           | R   | -       | Signal strength measured in RX [70]                 |

| 0x0077  | SIG STREM           |     |         | [158]                                               |

| 0x00E9  | OP DUTY             | R   | -       | TX operating duty cycle in % [70]                   |

#### Table 10. GPIO

| Address | Register name | R/W | Default | Description                                     |

|---------|---------------|-----|---------|-------------------------------------------------|

| 0x30    | GPIO0 Fun     | RW  | -       | Please refer to GPIO configuration description. |

| 0x31    | GPIO1 Fun     | RW  | -       |                                                 |

| 0x32    | GPIO2Fun      | RW  | -       |                                                 |

| 0x33    | GPIO03Fun     | RW  | -       |                                                 |

| 0x34    | GPIO04Fun     | RW  | -       |                                                 |

| 0x35    | GPIO05Fun     | RW  | -       |                                                 |

| 0x36    | GPIO06Fun     | RW  | -       | Configured as Interrupt - INTB Pin              |

| 0x37    | GPIO07Fun     | RW  | -       |                                                 |

#### GPIO configuration - alternate functions

- 0x00: GPIO configured as Input, FLOATING (Default)

- 0x01: GPIO configured as Input , Pull up resistor to internal 1.8V.

- 0x02: GPIO configured as Input ,Pull down resistor to Internal Ground.

- 0x03: GPIO configured as Output , Open Drain (Active High)

- 0x04: GPIO configured as Output , Open Drain (Active Low)

- 0x05:GPIO configured as Interrupt pin , Open Drain output.

- 0x06: Initialization complete, FW ready.

**Table 11. TX Commands**

| Address | Register name | R/W | Default | Description                                                          |

|---------|---------------|-----|---------|----------------------------------------------------------------------|

|         |               | RW  |         | Bit0: TX EN                                                          |

|         |               | KVV | -       | Enable the TX. Write 1 to start Ping                                 |

| 0x00D0  |               |     |         | Bit1:TX DIS                                                          |

|         |               | RW  | -       | Disable the TX. Write 1 to stop the inverter and cut the power to Rx |

DS14079 - Rev 1 page 17/40

Table 12. TX Interrupt enable

| Address | Register name             | R/W      | Default | Description                              |

|---------|---------------------------|----------|---------|------------------------------------------|

|         |                           |          |         | Bit 0: TX OVTP EN                        |

|         |                           | 514      |         | Over temperature protection enable       |

|         |                           | RW       | -       | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          |         | Bit 1: TX OCP EN                         |

|         |                           | 514      |         | Over current protection enable           |

|         |                           | RW       | -       | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          |         | Bit 2:TX OVP EN                          |

|         |                           | RW       |         | Over voltage protection enable           |

|         |                           | IXVV     | _       | 0: disable                               |

|         |                           | RW<br>RW |         | 1: enable                                |

|         |                           |          |         | Bit 3:TX SYS ERR EN                      |

|         |                           |          | _       | System error enable                      |

|         |                           |          |         | 0: disable                               |

| 0x00C0  | TX interrupt enable Byte0 |          |         | 1: enable                                |

| 0,0000  | 17 interrupt enable Bytes |          | -       | Bit4: TX RP PKT RCVD EN                  |

|         |                           |          |         | RP packet received interrupt enable      |

|         |                           |          |         | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          | -       | Bit5: TX CE PKT RCVD EN                  |

|         |                           |          |         | CE packet received interrupt enable      |

|         |                           |          |         | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          | -       | Bit6: TX SEND PKT SUC EN                 |

|         |                           |          |         | Packet sent interrupt enable             |

|         |                           |          |         | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          |         | Bit7: TX EXT MON EN                      |

|         |                           | RW       | -       | Ext TX Detect interrupt enable           |

|         |                           |          |         | 0: disable                               |

|         |                           |          |         | 1: enable                                |

|         |                           |          |         | Bit0: TX CEP TO EN                       |

|         |                           | RW       | _       | CEP Timeout interrupt enable             |

|         |                           |          |         | 0: disable 1: enable                     |

|         |                           | RW       |         |                                          |

| 0x00C1  | TX interrupt enable Byte1 |          |         | Bit1: TX RPP TO EN                       |

|         |                           |          | -       | RPP Timeout interrupt enable  0: disable |

|         |                           |          |         | 1: enable                                |

|         |                           |          |         |                                          |

|         |                           | RW       | -       | Bit2: TX EPT EN                          |

|         |                           |          |         | AC powered down interrupt enable         |

DS14079 - Rev 1 page 18/40

| Address | Register name                | R/W   | Default | Description                                                                         |

|---------|------------------------------|-------|---------|-------------------------------------------------------------------------------------|

|         |                              |       |         | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit3: TX START PING EN                                                              |

|         |                              | D)A(  |         | Ping started interrupt enable                                                       |

|         |                              | RW    | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit4:TX SS PKT RCVD EN                                                              |

|         |                              | DW    |         | SS ID packet received interrupt enable                                              |

|         |                              | RW    | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

| 0,,0004 | TV into my unt on ohio Dutod |       |         | Bit5: TX ID PKT RCVD EN                                                             |

| 0x00C1  | TX interrupt enable Byte1    | RW RW |         | ID packet received interrupt enable                                                 |

|         |                              |       | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit6: TX CFG PKT RCVD EN                                                            |

|         |                              |       |         | Configuration packet received interrupt                                             |

|         |                              |       | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit7: TX PP PKT RCVD EN                                                             |

|         |                              |       |         | PP packet received interrupt enable                                                 |

|         |                              |       | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit0:TX BRIDGE MD EN                                                                |

|         |                              | RW    |         | Bridge mode (half/full) changed interrupt                                           |

|         |                              |       | _       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       | -       | Bit1: TX FOD DET EN                                                                 |

|         |                              | RW    |         | TX FOD detect interrupt enable                                                      |

|         |                              | IXVV  |         | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit2:TX PTC UPDATE EN                                                               |

|         |                              |       |         | The power transfer contract is successfully updated after negotiation/renegotiation |

| 0x00C2  | TX interrupt enable Byte2    | RW    | -       | negotiation/renegotiation  0: disable                                               |

| 0,10002 | apt ondate 2,te2             |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit 3: TX DTS SUCC EN                                                               |

|         |                              | RW    |         | DTS send data stream successfully                                                   |

|         |                              |       | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         | Bit 4: TX DTS SEND END TO EN                                                        |

|         |                              |       |         | DTS stopped sending due to time out                                                 |

|         |                              | RW    | -       | 0: disable                                                                          |

|         |                              |       |         | 1: enable                                                                           |

|         |                              |       |         |                                                                                     |

|         |                              | RW    | -       | Bit 5: TX DTS SEND END RST EN                                                       |

DS14079 - Rev 1 page 19/40

| Address | Register name             | R/W | Default | Description                           |

|---------|---------------------------|-----|---------|---------------------------------------|

|         |                           |     |         | DTS stopped sending due to reset      |

|         |                           |     |         | 0: disable                            |

|         |                           |     |         | 1: enable                             |

|         |                           |     |         | Bit 6: TX DTS RCVD SUCC EN            |

|         |                           | RW  | -       | DTS received data successfully        |

| 0x00C2  | TX interrupt enable Byte2 |     |         | 0: disable                            |

|         |                           |     |         | 1: enable                             |

|         |                           |     |         | Bit7: TX DTS RCVD END TO EN           |

|         |                           | RW  | -       | DTS stopped receiving due to time out |

|         |                           | KVV |         | 0: disable                            |

|         |                           |     |         | 1: enable                             |

| 0x00C3  | TX interrupt enable Byte3 |     |         | Reserved                              |

Table 13. TX Interrupt clear

| Address | Register name            | R/W | Default | Description                        |

|---------|--------------------------|-----|---------|------------------------------------|

|         |                          |     |         | Bit 0:TX OVTP CLR                  |

|         |                          | R   | -       | Over temperature protection clear  |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit 1:TX OCP CLR                   |

|         | -                        | R   | -       | Over current protection clear      |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit 2:TX OVP CLR                   |

|         |                          | R   | -       | Over voltage protection clear      |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit 3:TX SYS ERR CLR               |

|         | TX interrupt clear Byte0 | R   | -       | System error clear                 |

| 0×0004  |                          |     |         | 1: clear                           |

| 0,0004  |                          |     |         | Bit4: TX RP PKT RCVD CLR           |

|         |                          | R   | -       | RP packet received interrupt clear |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit5:TX CE PKT RCVD CLR            |

|         |                          | R   | -       | CE packet received interrupt clear |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit6: TX SCLRD PKT SUC CLR         |

|         |                          | R   | -       | Packet sent interrupt clear        |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit7:TX EXT MON CLR                |

|         |                          | R   | -       | Ext TX Detect interrupt clear      |

|         |                          |     |         | 1: clear                           |

|         |                          |     |         | Bit0:TX CEP TO CLR                 |

| 0x00C5  | TX interrupt clear Byte1 | R   | -       | CEP Timeout interrupt clear        |

|         |                          |     |         | 1: clear                           |

DS14079 - Rev 1 page 20/40

|                                         | Default | Description                                               |

|-----------------------------------------|---------|-----------------------------------------------------------|

|                                         |         | Bit1: TX RPP TO CLR                                       |

| R                                       | _       | RPP Timeout interrupt clear                               |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit2: TX EPT CLR                                          |

| R                                       | _       | AC powered down interrupt clear                           |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit3: TX START PING CLR                                   |

| R                                       | _       | Ping started interrupt clear                              |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit4:TX SS PKT RCVD CLR                                   |

| 0x00C5 TX interrupt clear Byte1 R       | _       | SS ID packet received interrupt clear                     |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit5:TX ID PKT RCVD CLR                                   |

| R                                       | _       | ID packet received interrupt clear                        |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit6: TX CFG PKT RCVD CLR                                 |

| R                                       | _       | Configuration packet received interrupt clear             |

|                                         | _       | 1: clear                                                  |

|                                         |         | Bit7: TX PP PKT RCVD CLR                                  |

| R                                       | _       | PP packet received interrupt clear                        |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit0: TX BRIDGE MD CLR                                    |

| R                                       | _       | Bridge mode (half/full) changed interrupt clear           |

|                                         | -       | 1: clear                                                  |

|                                         |         | Bit1: TX FOD DET CLR                                      |

| R                                       | _       | TX FOD detect interrupt clear                             |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit2:TX PTC UPDATE CLR                                    |

|                                         |         | the power transfer contract is successfully updated after |

| R                                       | -       | negotiation/renegotiation clear                           |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit 3: TX DTS SUCC CLR                                    |

| 0x00C6 TX interrupt clear Byte2 R       | -       | DTS send data stream successfully clear                   |

| , , , , , , , , , , , , , , , , , , , , |         | 1: clear                                                  |

|                                         |         | Bit 4: TX DTS SEND END TO CLR                             |

| R                                       | -       | DTS stopped sending due to time out clear                 |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit 5: TX DTS SEND END RST CLR                            |

| R                                       | -       | DTS stopped sending due to reset clear                    |

|                                         |         | 1: clear                                                  |

|                                         |         | Bit 6: TX DTS RCVD SUCC CLR                               |

| R                                       | -       | DTS received data successfully clear                      |

|                                         |         | 1: clear                                                  |

| R                                       | -       | Bit7: TX DTS RCVD END TO CLR                              |

DS14079 - Rev 1 page 21/40

map

|   | Address | Register name            | R/W | Default | Description                                 |

|---|---------|--------------------------|-----|---------|---------------------------------------------|

| ſ | 0x00C6  | TX interrupt clear Byte2 |     |         | DTS stopped receiving due to time out clear |

|   | 020000  | 17 Interrupt clear Byte2 |     |         | 1: clear                                    |

|   | 0x00C7  | TX interrupt clear Byte3 |     |         | Reserved                                    |

Table 14. TX interrupt latch

| Address | Register name             | R/W | Default | Description                           |

|---------|---------------------------|-----|---------|---------------------------------------|

|         |                           |     |         | Bit 0: TX OVTP LTCH                   |

|         |                           | R   | _       | Over temperature protection latch     |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit 1: TX OCP LTCH                    |

|         |                           | R   | _       | Over current protection latch         |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit 2:TX OVP LTCH                     |

|         |                           | R   | _       | Over voltage protection latch         |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit 3: TX SYS ERR LTCH                |

|         |                           | R   | -       | System error latch                    |

|         |                           |     |         | 1: latch                              |

| 0x00C8  | TX interrupt latch Byte 0 |     |         | Bit4: TX RP PKT RCVD LTCH             |

|         |                           | R   | -       | RP packet received interrupt latch    |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit5:TX CE PKT RCVD LTCH              |

|         |                           | R   | -       | CE packet received interrupt latch    |

|         |                           |     |         | 1: latch                              |

|         |                           | R   | -       | Bit6: TX SLTCHD PKT SUC LTCH          |

|         |                           |     |         | Packet sent interrupt latch           |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit7: TX EXT MON LTCH                 |

|         |                           | R   | -       | Ext TX Detect interrupt latch         |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit0: TX CEP TO LTCH CEP              |

|         |                           | R   | -       | Timeout interrupt latch               |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit1:TX RPP TO LTCH RPP               |

|         |                           | R   | -       | Timeout interrupt latch               |

|         |                           |     |         | 1: latch                              |

| 0x00C9  | TX interrupt latch Byte 1 |     |         | Bit2: TX EPT LTCH AC                  |

|         | Transcript lates: 27to 1  | R   | -       | Powered down interrupt latch          |

|         |                           |     |         | 1: latch                              |

|         |                           |     |         | Bit3: TX START PING LTCH              |

|         |                           | R   |         | Ping started interrupt latch          |

|         |                           |     |         | 1: latch                              |

|         |                           | R   | _       | Bit4: TX SS PKT RCVD LTCH             |

|         |                           |     |         | SS ID packet received interrupt latch |

DS14079 - Rev 1 page 22/40

map

| Address | Register name             | R/W | Default | Description                                                                         |

|---------|---------------------------|-----|---------|-------------------------------------------------------------------------------------|

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit5: TX ID PKT RCVD LTCH                                                           |

|         |                           | R   | -       | ID packet received interrupt latch                                                  |

|         |                           |     |         | 1: latch                                                                            |

| 0x00C9  | TX interrupt latch Byte 1 |     |         | Bit6: TX CFG PKT RCVD LTCH                                                          |

| 0,00009 | 17 interrupt later byte 1 | R   | -       | Configuration packet received interrupt latch                                       |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit7: TX PP PKT RCVD LTCH                                                           |

|         |                           | R   | -       | PP packet received interrupt latch                                                  |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit0: TX BRIDGE MD LTCH                                                             |

|         |                           | R   | -       | Bridge mode (half/full) changed interrupt latch                                     |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit1: TX FOD DET LTCH                                                               |

|         |                           | R   | -       | TX FOD detect interrupt latch                                                       |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     | -       | Bit2: TX PPTC UPDATE LTCH                                                           |

|         |                           | R   |         | The power transfer contract is successfully updated after negotiation/renegotiation |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit 3: TX DTS SUCC LTCH DTS                                                         |

|         |                           | R   | _       | Send data stream successfully latch                                                 |

| 0,0000  | TV interrupt letch Dute 2 | R   |         | 1: latch                                                                            |

| 0x00CA  | TX interrupt latch Byte 2 |     |         | Bit 4: TX DTS SEND END TO LTCH                                                      |

|         |                           | R   | _       | DTS stopped sending due to time out latch                                           |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit 5: TX DTS SEND END RST LTCH                                                     |

|         |                           | R   | _       | DTS stopped sending due to reset latch                                              |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit 6: TX DTS RCVD SUCC LTCH                                                        |

|         |                           | R   | -       | DTS received data successfully latch                                                |

|         |                           |     |         | 1: latch                                                                            |

|         |                           |     |         | Bit7: TX DTS RCVD END TO LTCH                                                       |

|         |                           | R   | -       | DTS stopped receiving due to time out latch                                         |

|         |                           | IX  |         | 1: latch                                                                            |

| 0x00CB  | TX interrupt latch Byte 3 |     |         | Reserved                                                                            |

#### Table 15. TX Interrupt status

| Address | Register name                    | R/W | Default | Description                                             |

|---------|----------------------------------|-----|---------|---------------------------------------------------------|

| 0x00CC  | x00CC TX interrupt status Byte 0 | R   | -       | Bit 0: TX OVTP STAT  Over temperature protection status |

|         |                                  | R   | -       | Bit 1: TX OCP STAT                                      |

DS14079 - Rev 1 page 23/40

| Address | Register name                 | R/W | Default | Description                                                                         |

|---------|-------------------------------|-----|---------|-------------------------------------------------------------------------------------|

|         |                               |     |         | Over current protection status                                                      |

|         |                               |     | -       | Bit 2: TX OVP STAT                                                                  |

|         |                               | R   |         | Over voltage protection status                                                      |

|         |                               |     |         | -                                                                                   |

|         |                               | R   | _       | Bit 3:TX SYS ERR STAT                                                               |

|         |                               |     |         | System error status                                                                 |

| 0x00CC  | TX interrupt status Byte 0    | R   |         | Bit4: TX RP PKT RCVD STAT                                                           |

| 0,0000  | 17 interrupt status byte o    | K   | _       | RP packet received interrupt status                                                 |

|         |                               | R   | _       | Bit5: TX CE PKT RCVD STAT                                                           |

|         |                               |     | _       | CE packet received interrupt status                                                 |

|         |                               | R   | _       | Bit6: TX SSTATD PKT SUC STAT                                                        |