## STx7100 (STb7100, STi7100, STm7100)

## Low-cost HDTV set-top box decoder for H.264/AVC and MPEG-2

ADVANCE DATA

#### **Features**

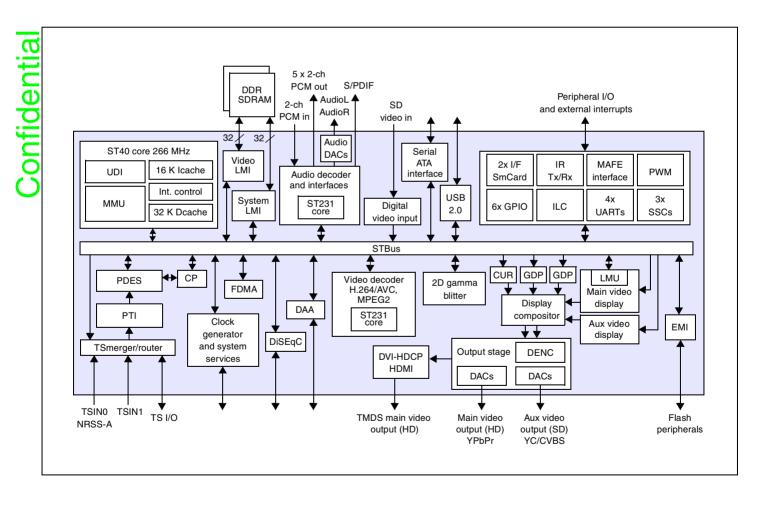

- The STx7100 is a single-chip, highdefinition STB decoder including:

- ST40 CPU core, 266 MHz

- dual ST231 CPU cores for audio and video decoding, both 400 MHz

- transport filtering and descrambling

- video decoder: H.264/AVC and MPEG-2

- graphics engine and dual display: high-definition (HD) and standard definition (SD)

- audio decoder

- The STx7100 also features the following embedded interfaces:

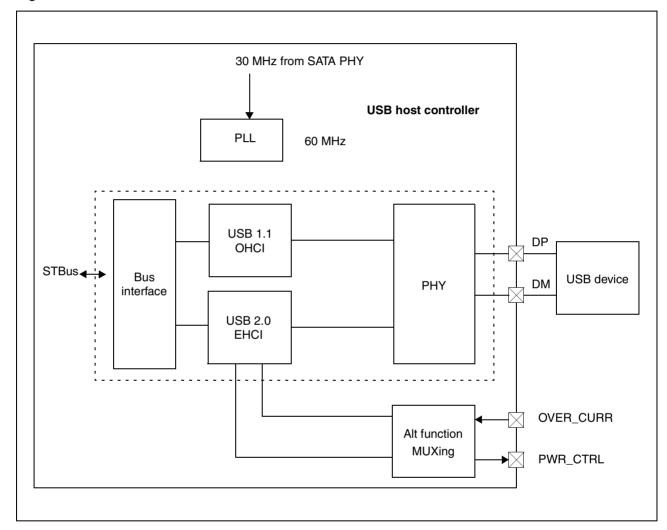

- USB 2.0

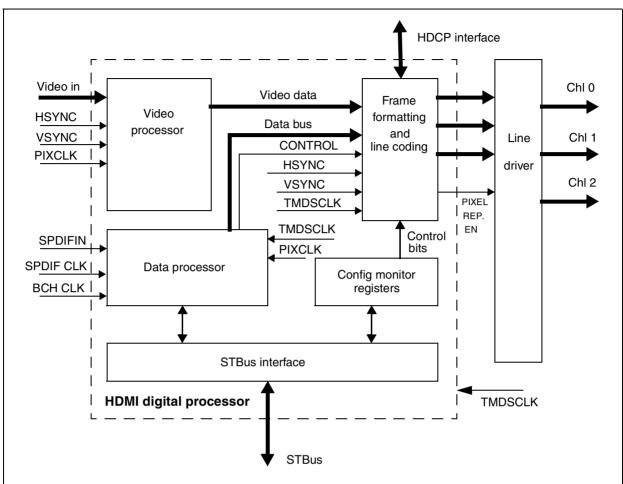

- DVI/HDMI output

- digital audio and video auxiliary input

- modem

- serial ATA

## **Processor subsystem**

#### ■ ST40 32-bit superscalar RISC CPU

- 266 MHz, 2-way set associative 16-Kbyte ICache, 32-Kbyte DCache, MMU

- 5-stage pipeline, delayed branch support

- floating point unit, matrix operation support

- debug port, interrupt controller

## **Transport subsystem**

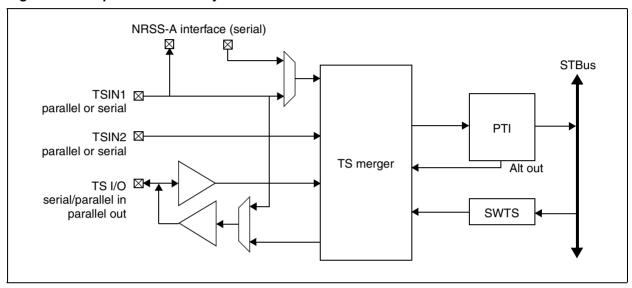

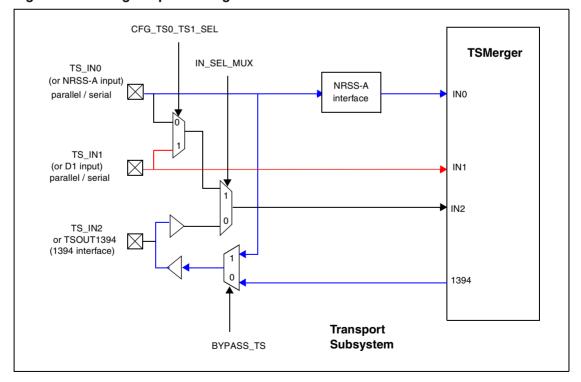

## **■** TS merger/router

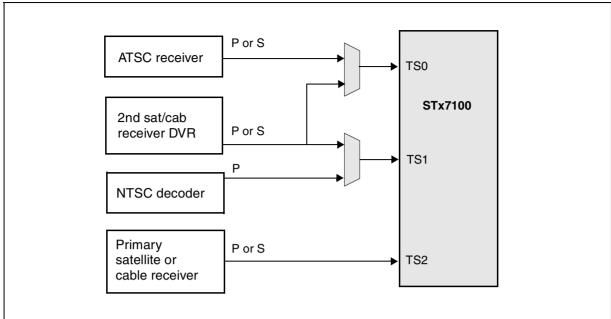

- 2 serial/parallel inputs

- 1 bidirectional interface

- merging of 3 transport streams

- transport stream from memory support

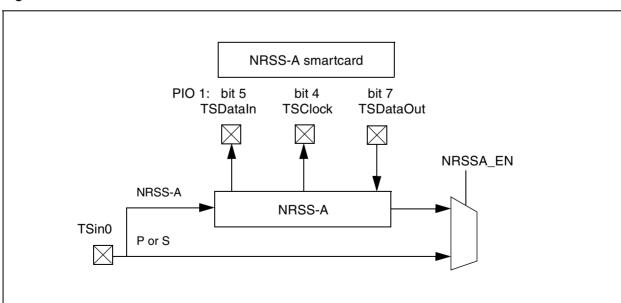

- NRSS-A module interface

- TS routing for DVB-Cl and CableCARD™ modules

## ■ Programmable transport interface (PTI)

- transport stream demux: DVB, DIRECTV®, ATSC, ARIB, OpenCable, DCII

- integrated DES, AES, DVB, ICAM and Multi2 descramblers

- NDS random access scrambled stream protocol (RASP) compliant

- NDS ICAM CA

- support for VGS, Passage and DVS042 residue handling

## Video/graphics subsystem

## I MPEG-4 AVC high profile level 4.1/ MPEG-2 MP@HL video decoder

- hardware/firmware mixed architecture

- advanced error concealment and trick mode support

- dual MPEG-2 MP@HL decode

#### ■ SD (ITU-R BT 601/656) D1 digital video input

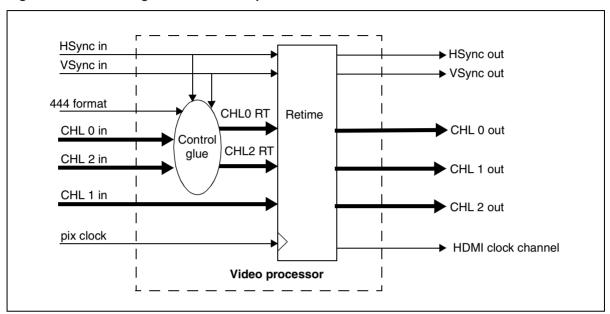

- HD display, multiformat capable (1080I, 720P, 480P/576P, 480I/576I)

- Analog HD output RGB or YPbPr

- HDMI encoded output

- SD display

- Analog SD output: YPbPr or YC and CVBS

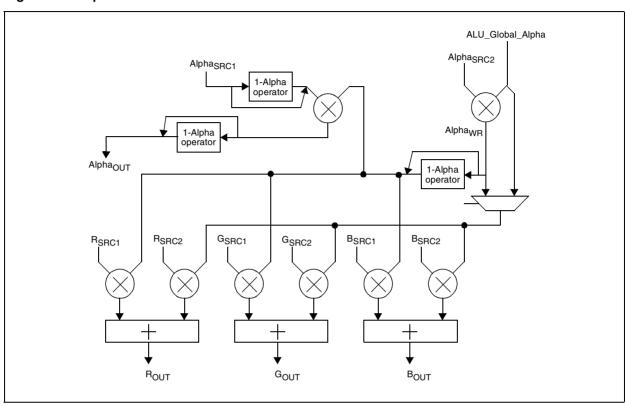

## ■ Gamma 2D/3D graphics processor

- dual source blitter engine

- alpha blending and logical operations

- color space and format conversion

- fast color fill

- arbitrary resizing with high quality filters

- acceleration of direct drawing by CPU

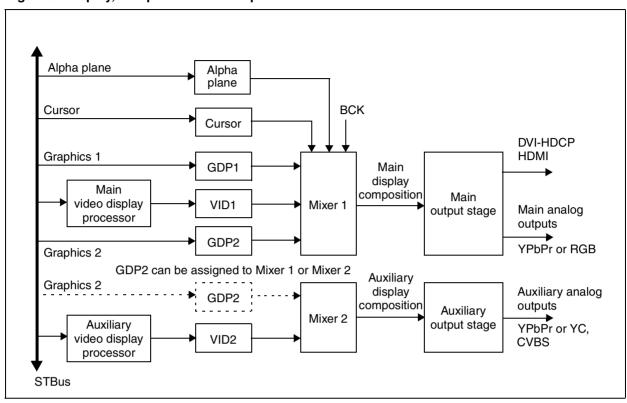

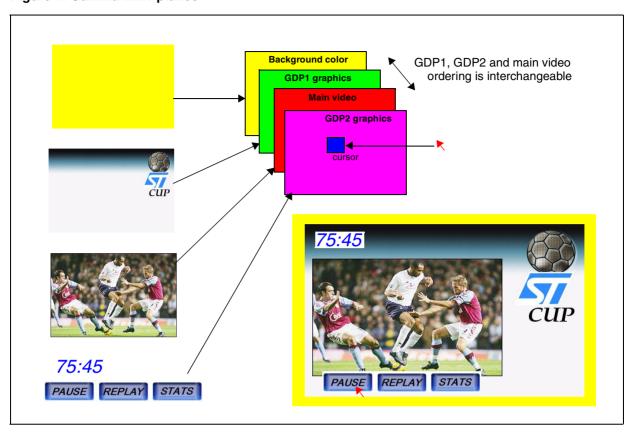

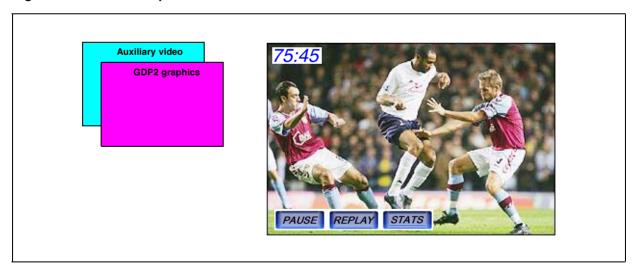

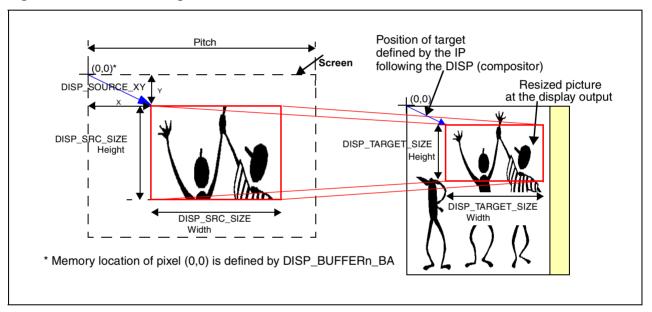

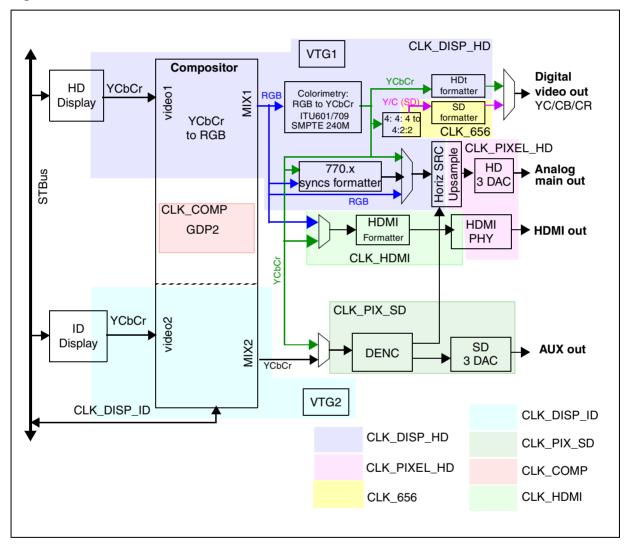

## Gamma compositor and video processor

- 5 channels mixer for HD output

- independent 2-channel mixer for SD output

- 2 graphic display planes

- high-quality video scaler

- picture up-conversion hardware

- linear resizing and format conversions

- horizontal and vertical filtering

#### ■ Copy protection

- HDMI 1.0/HDCP 1.1 copy protection hardware

- Macrovision<sup>™</sup> copy protection for 480I, 480P, 576I, 576P outputs

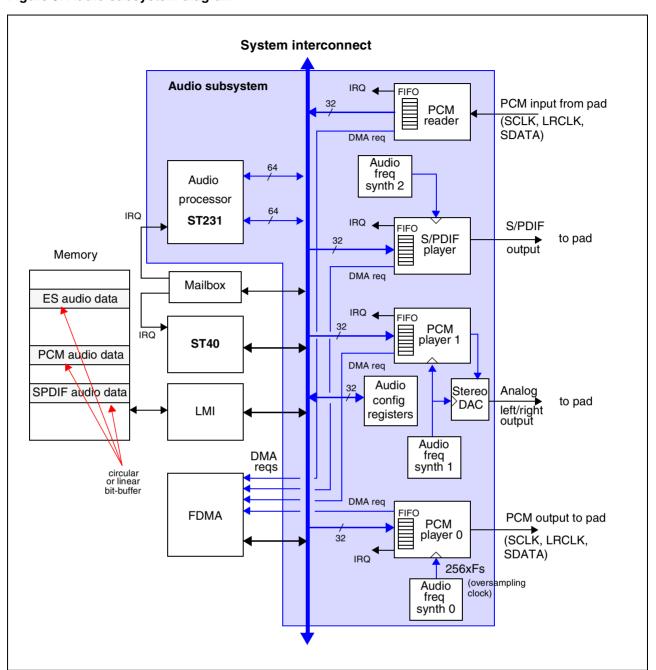

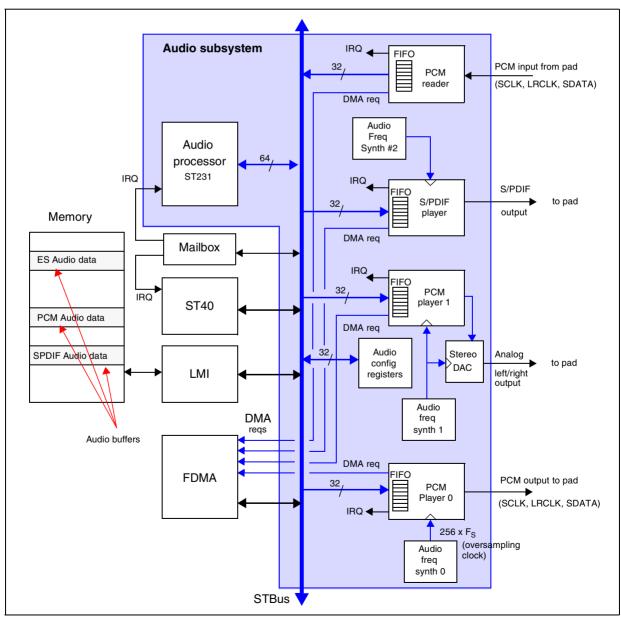

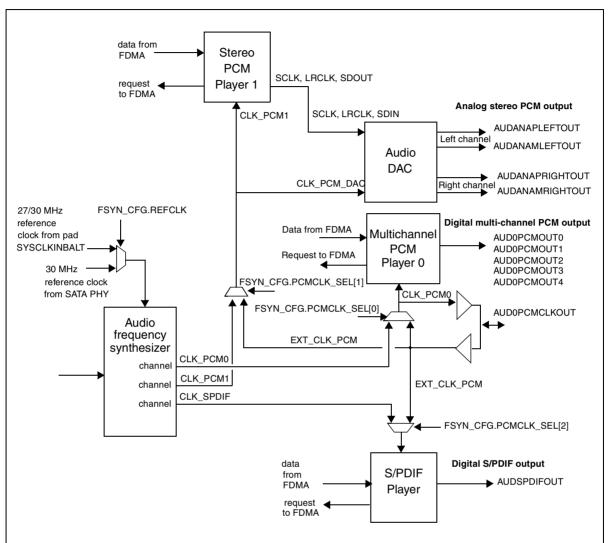

## **Audio subsystem**

## ■ Digital audio decoder

- compatible with all popular audio standards

- PCM mixing with internal or external source and sample rate conversion

- independent multichannel PCM output, S/PDIF output and analog output

- 6 to 2 channel downmixing

- PCM audio input

## ■ Stereo 24-bit audio DAC for analog output

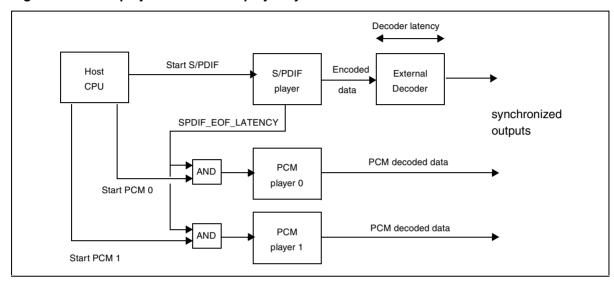

## ■ IEC958/IEC1937 digital audio output interface (S/PDIF)

#### Interfaces

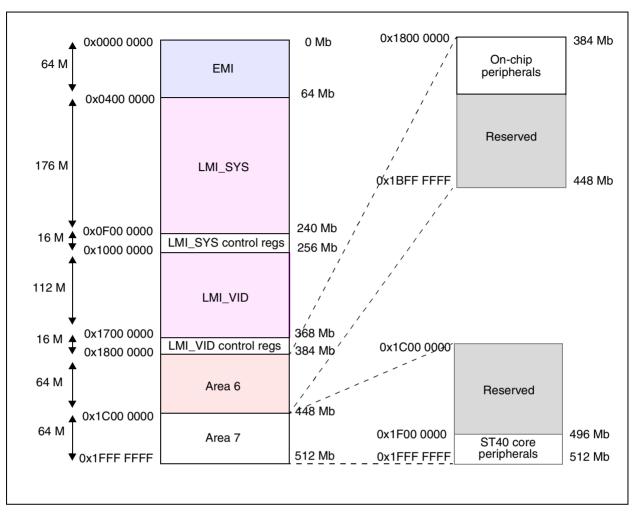

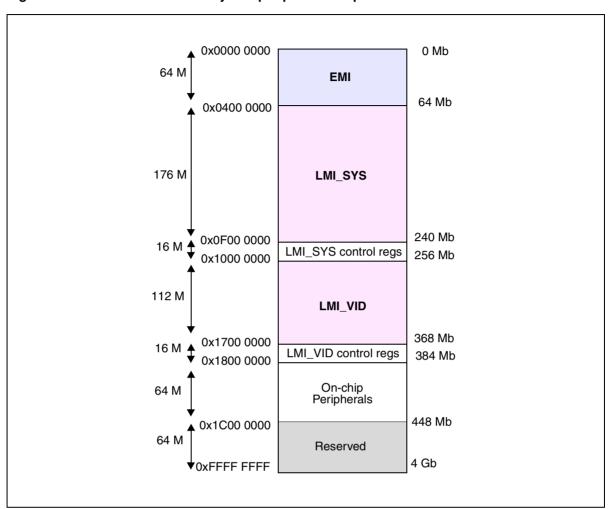

## **■** External memory interface (EMI)

- 16-bit interface supporting ROM, Flash, SFlash, SRAM, peripherals

- access in 5 banks

- master/slave support for interconnecting two STx7100

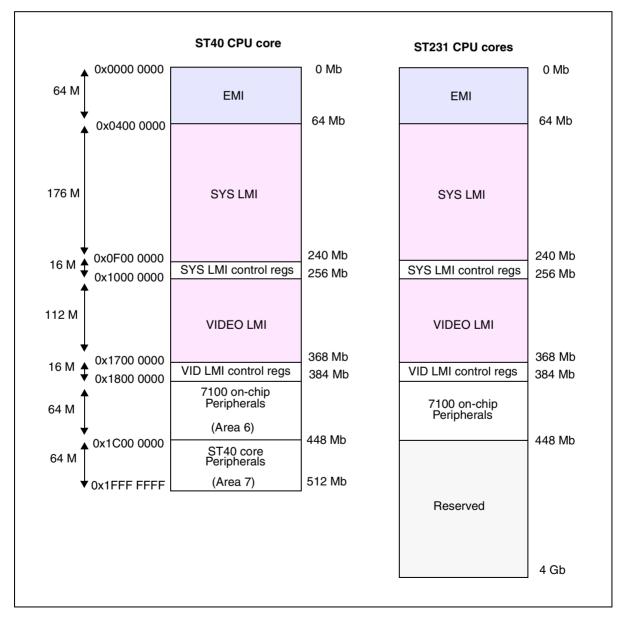

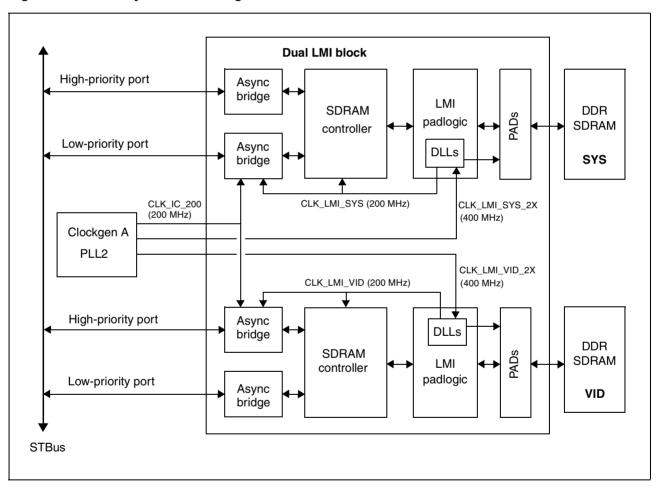

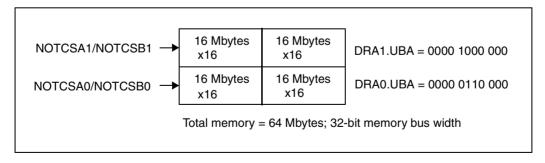

## ■ Dual local memory interface (LMI)

dual interface for 32-bit DDR1 200-MHz (DDR400) memories, supports 64, 128, 256 and 512 Mbit devices

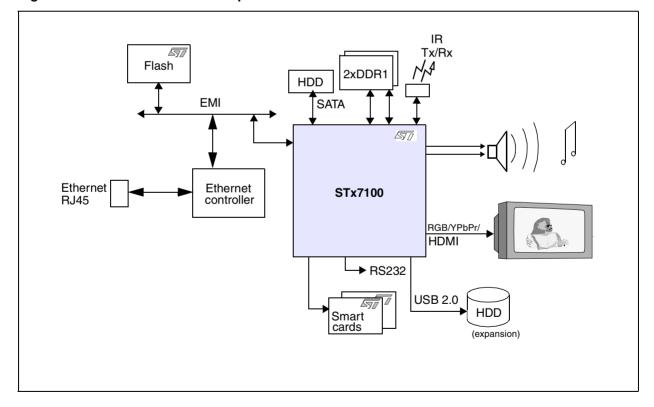

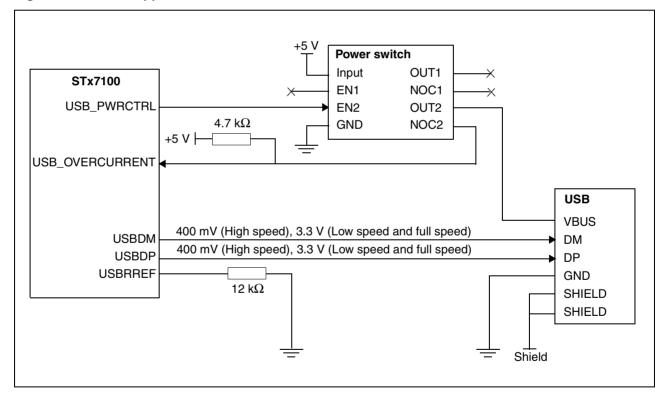

#### ■ USB 2.0 host interface

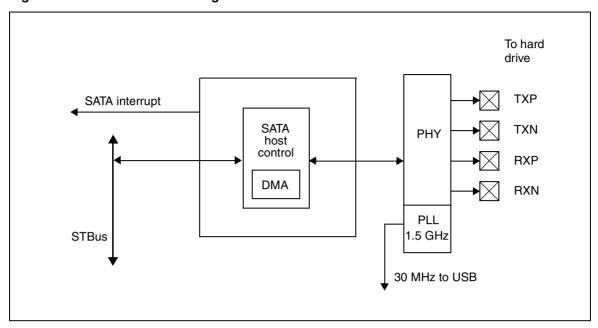

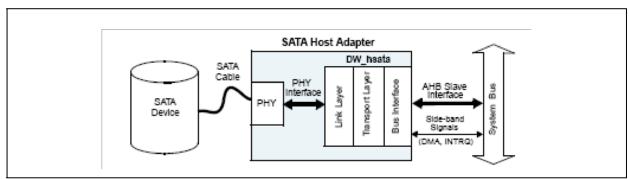

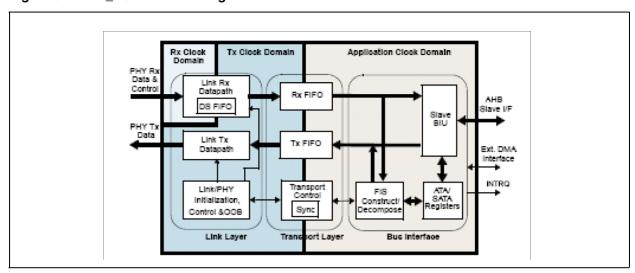

## ■ Serial ATA hard-disk drive support

- record and playback with trick modes

- pause and time shifting

- watch and record

#### ■ On-chip peripherals

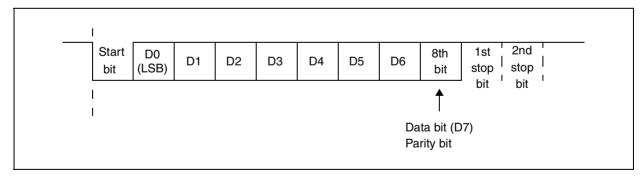

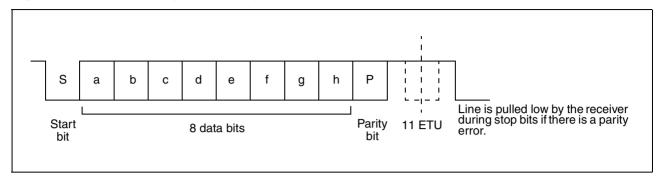

- 4 ASCs (UARTs) with Tx and Rx FIFOS, two of which can be used in smartcard interfaces

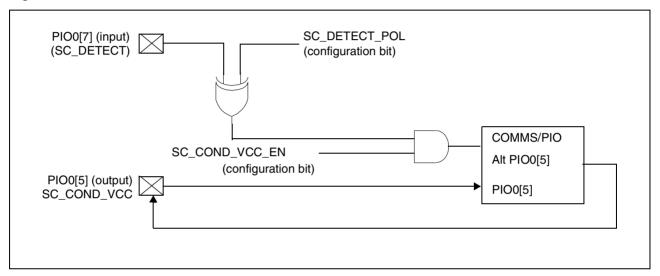

- 2 smartcard interfaces and clock generators (improved to reduce external circuitry)

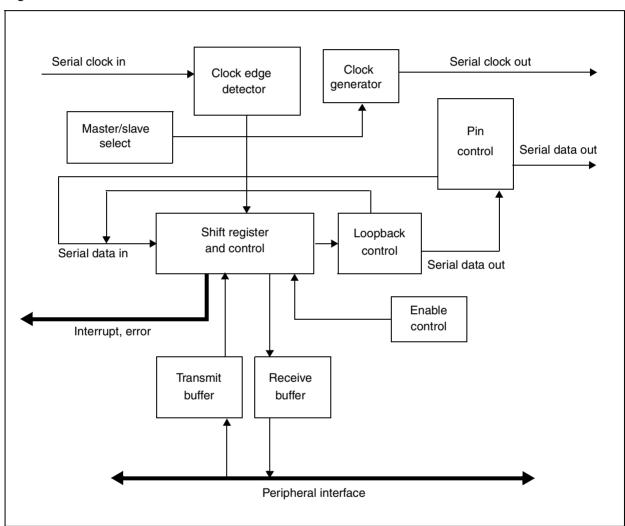

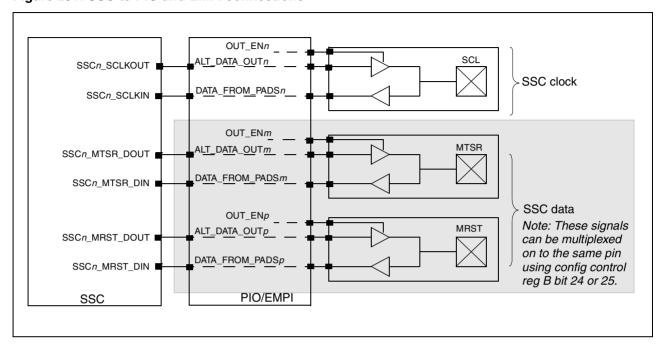

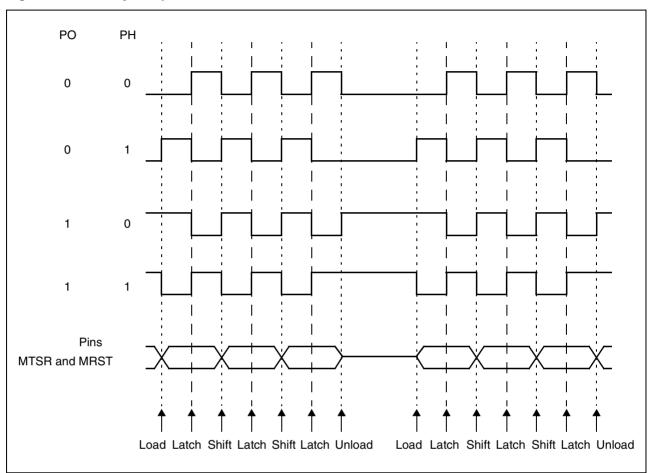

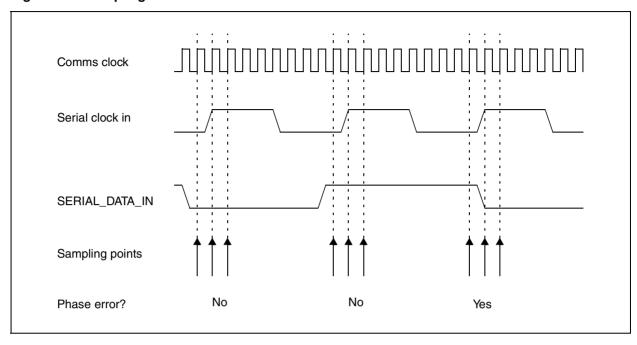

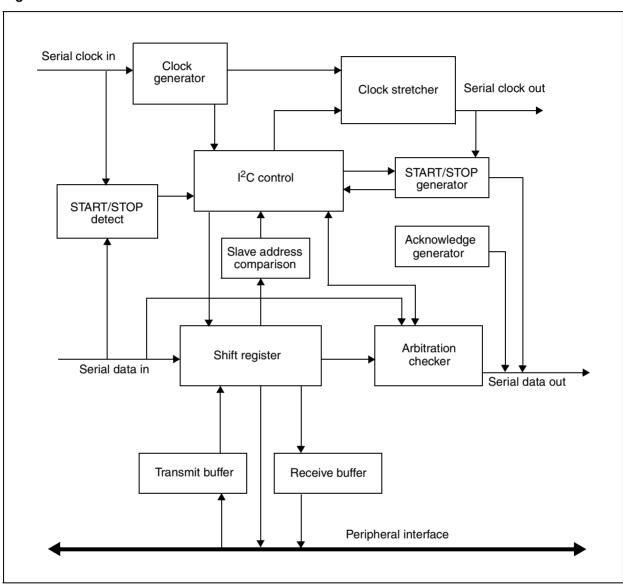

- 3 SSCs for I2C/SPI master slaves interfaces

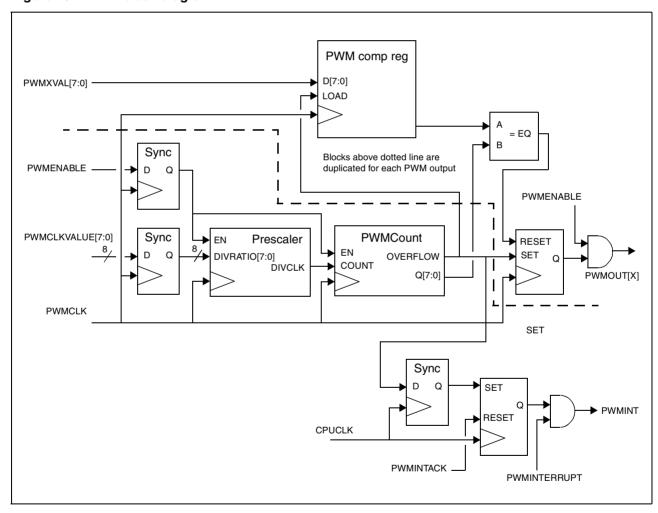

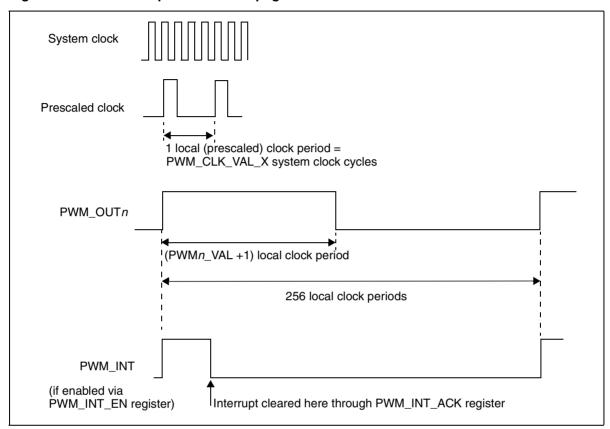

- 2 PWM outputs

- teletext serializer and DMA module

- 6 banks of general purpose I/O, 3.3 V tolerant

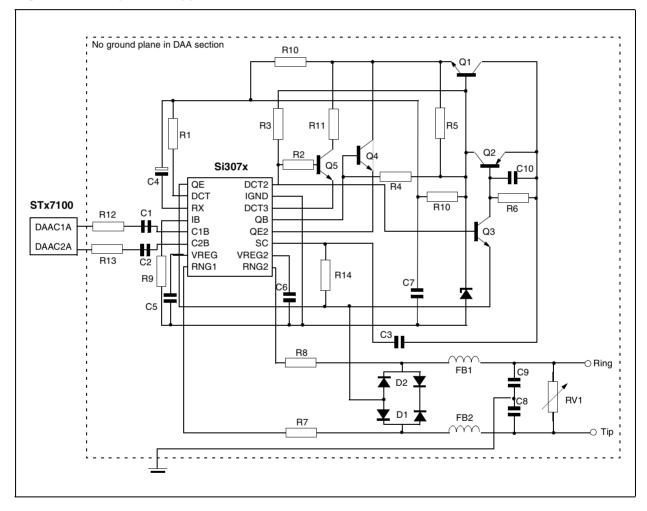

- SiLabs line-side (DAA) interface

- Modem analog front end (MAFE/DAA) interface

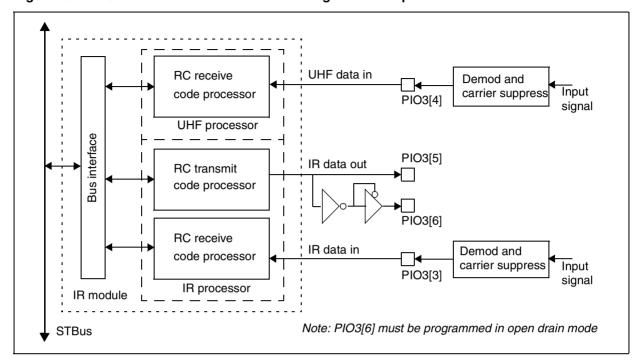

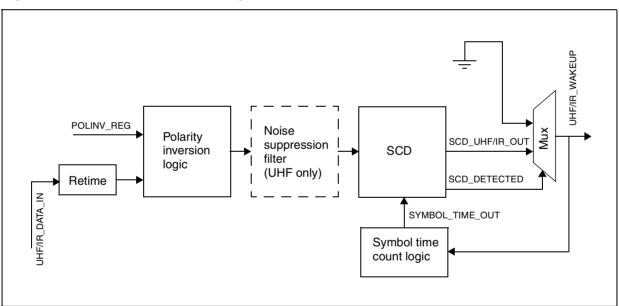

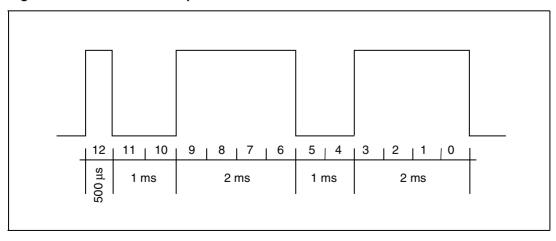

- infrared transmitter/receiver supporting RC5, RC6 and RECS80 codes

- UHF remote receiver input interface

- interrupt level controller and external interrupts, 3.3 V tolerant

- low power/RTC/watchdog controller

- integrated VCXO

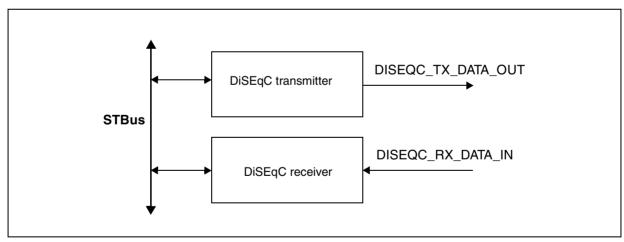

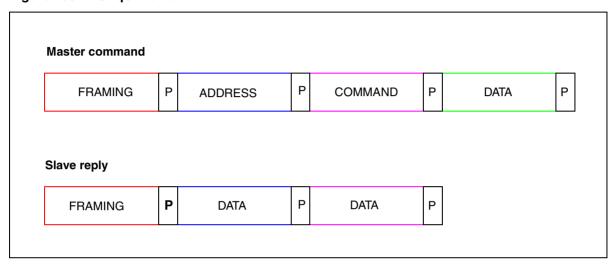

- DiSEqC<sup>TM</sup> 2.0 interface

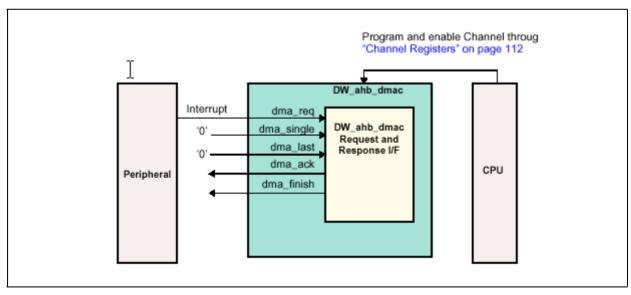

## **■** Flexible multichannel DMA

## Services and package

- **■** JTAG/TAP interface

- ST40 and ST231 toolset support

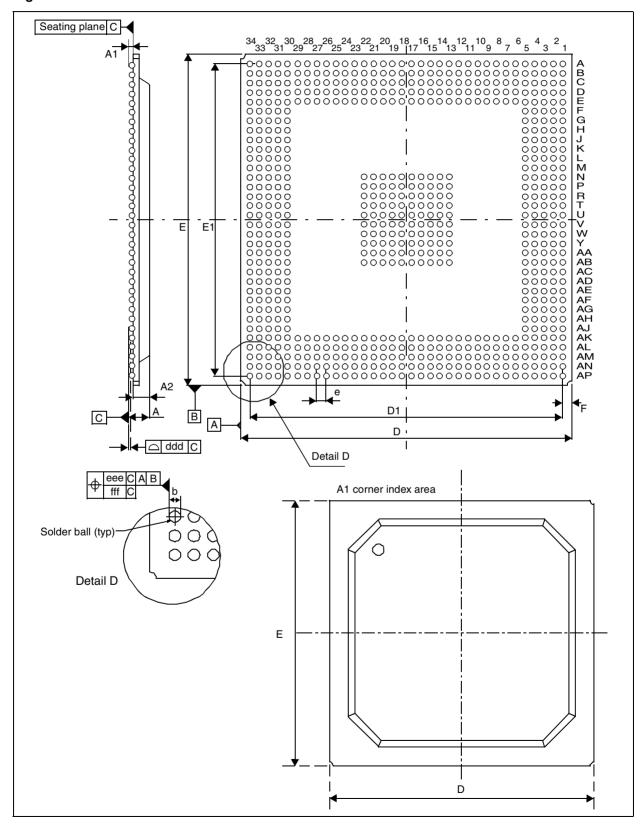

- 35 x 35 PGBA package, 580+100 balls

## **Contents**

| Part 1    | Overview19                                     |

|-----------|------------------------------------------------|

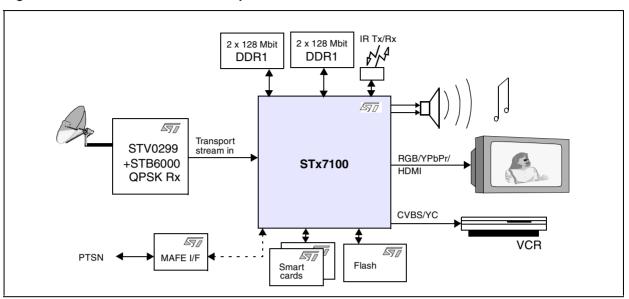

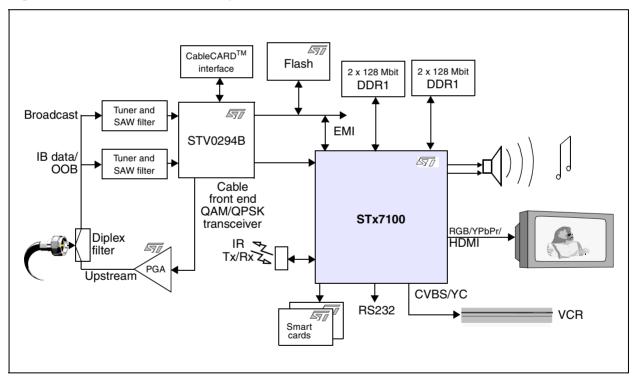

| Chapter 1 | Applications overview                          |

| Chapter 2 | Device variants                                |

| Chapter 3 | Architecture                                   |

| 3.1       | Overview                                       |

| 3.2       | Omega2 (STBus) interconnect                    |

| 3.3       | Processor cores                                |

| 3.4       | Dual local memory interface (LMI)              |

| 3.5       | External memory interface (EMI)25              |

| 3.6       | Transport subsystem                            |

| 3.7       | H.264/MPEG-2 video decoder                     |

| 3.8       | Digital video input                            |

| 3.9       | Video display processors                       |

| 3.10      | Graphics display                               |

| 3.11      | Display compositor                             |

| 3.12      | Main display output stage                      |

| 3.13      | Auxiliary display output stage                 |

| 3.14      | Gamma 2D blitter                               |

| 3.15      | Audio subsystem                                |

| 3.16      | FDMA controller                                |

| 3.17      | Interfaces                                     |

| 3.18      | Clock generation                               |

| 3.19      | System services                                |

| Chapter 4 | CPUs                                           |

| 4.1       | ST40                                           |

| 4.2       | ST231 CPU                                      |

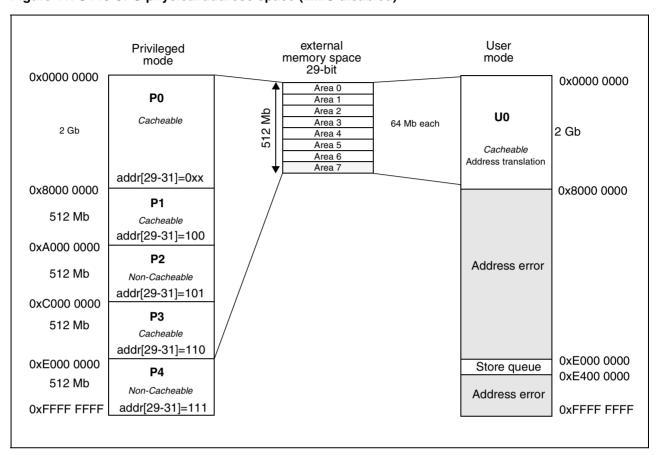

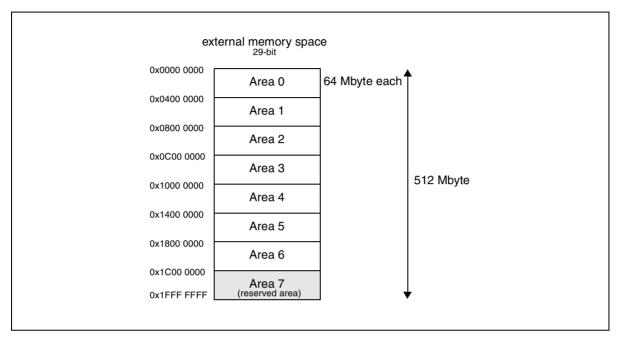

| Chapter 5 | Memory map                                     |

| 5.1       | Memory map                                     |

| <b>A</b>  | 7901570A STMigraplastranias Confidential 2/109 |

| 5.2        | Internal peripherals map                   |

|------------|--------------------------------------------|

| 5.3        | Memory management and organization         |

| 5.4        | Memory space access per initiator          |

| Part 2     | Hardware                                   |

| Chapter 6  | Package 48                                 |

| Chapter 7  | Pin list and alternative functions 50      |

| 7.1        | Pin-out                                    |

| 7.2        | Alternative functions                      |

| Chapter 8  | Connections                                |

| 8.1        | Power supplies                             |

| 8.2        | System                                     |

| 8.3        | JTAG                                       |

| 8.4        | Transport, NRSS-A and D1 input interface69 |

| 8.5        | Display digital output interface71         |

| 8.6        | Display analog output interface72          |

| 8.7        | HDMI interface72                           |

| 8.8        | Audio digital interface73                  |

| 8.9        | Audio analog interface73                   |

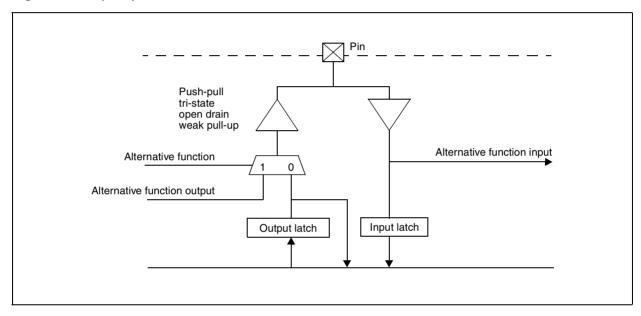

| 8.10       | Programmable inputs/outputs                |

| 8.11       | External memory interface (EMI)75          |

| 8.12       | System local memory interface (LMISYS)78   |

| 8.13       | Video local memory interface (LMIVID)80    |

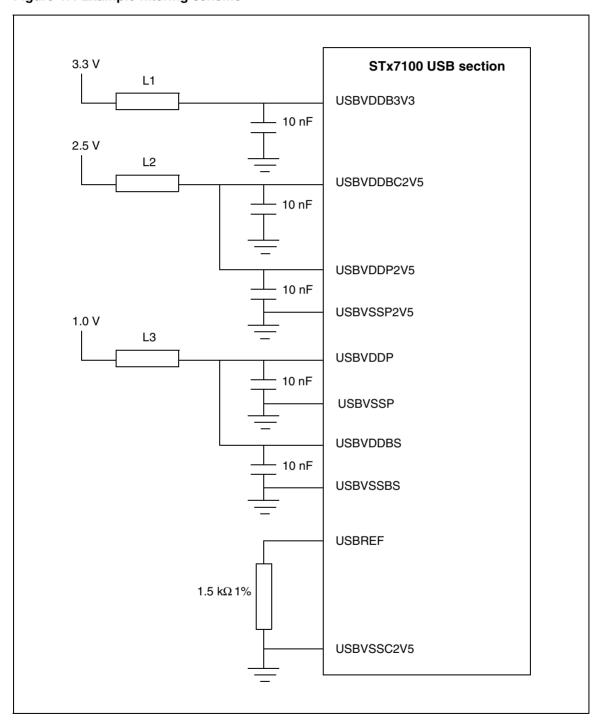

| 8.14       | USB 2.0 interface                          |

| 8.15       | SATA-I interface83                         |

| 8.16       | Peripherals84                              |

| Chapter 9  | Reset configuration (mode pins)            |

| Chapter 10 | Electrical specifications 90               |

| 10.1       | Video DACs90                               |

|                                                                                             | Chapter 11                                                                                   | Timing specifications                                                                                                                                                                                                                                                                                                                                                                       |

|---------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

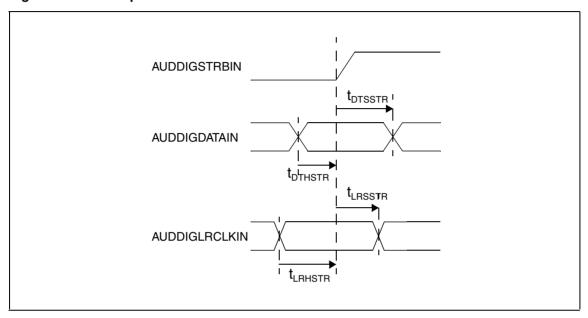

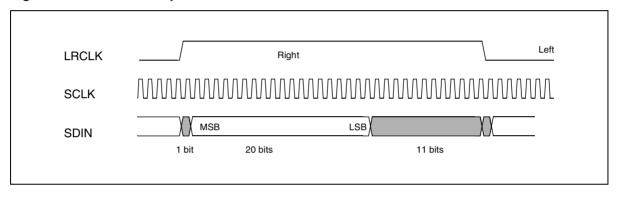

|                                                                                             | 11.1                                                                                         | Audio input AC specifications92                                                                                                                                                                                                                                                                                                                                                             |

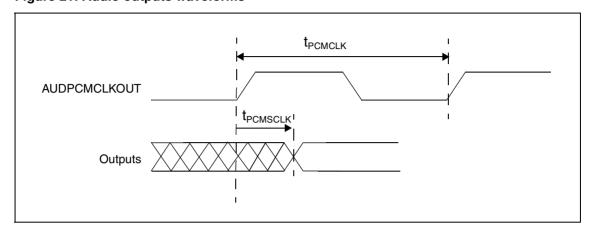

|                                                                                             | 11.2                                                                                         | Audio output AC specifications                                                                                                                                                                                                                                                                                                                                                              |

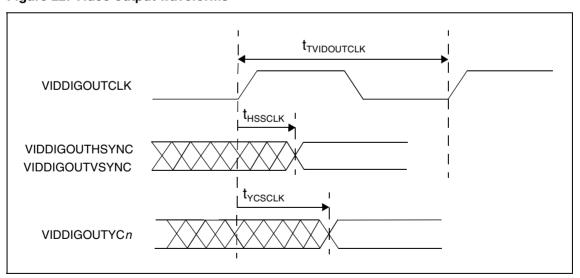

|                                                                                             | 11.3                                                                                         | Video output AC specification                                                                                                                                                                                                                                                                                                                                                               |

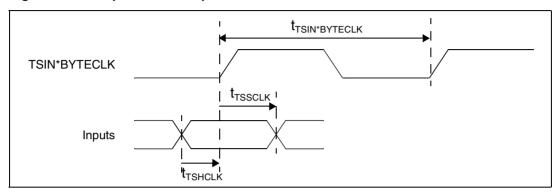

|                                                                                             | 11.4                                                                                         | Transport stream input AC specification94                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                             | 11.5                                                                                         | DVP inputs94                                                                                                                                                                                                                                                                                                                                                                                |

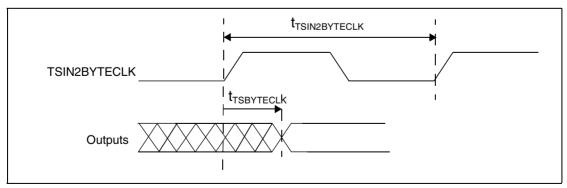

|                                                                                             | 11.6                                                                                         | Transport stream output AC specification                                                                                                                                                                                                                                                                                                                                                    |

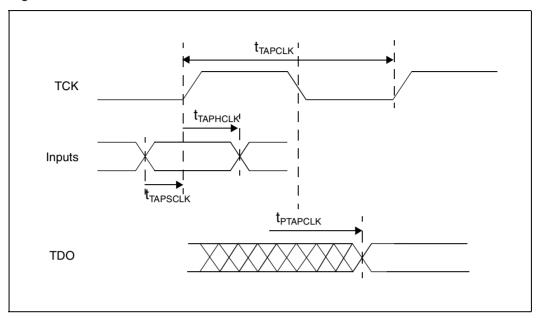

|                                                                                             | 11.7                                                                                         | JTAG interfaces AC specification95                                                                                                                                                                                                                                                                                                                                                          |

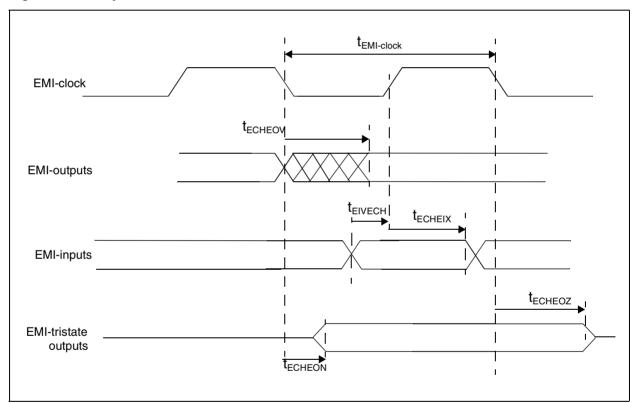

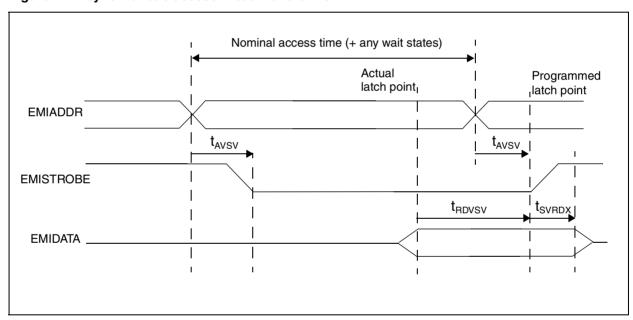

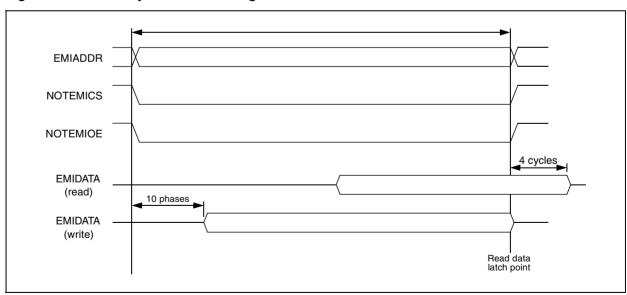

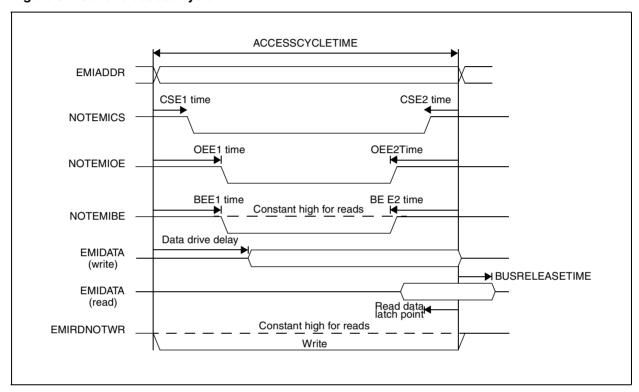

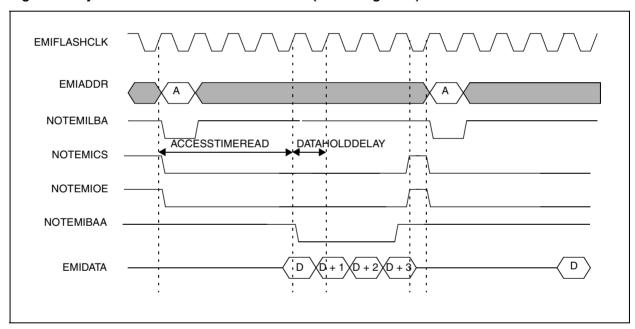

|                                                                                             | 11.8                                                                                         | EMI timings96                                                                                                                                                                                                                                                                                                                                                                               |

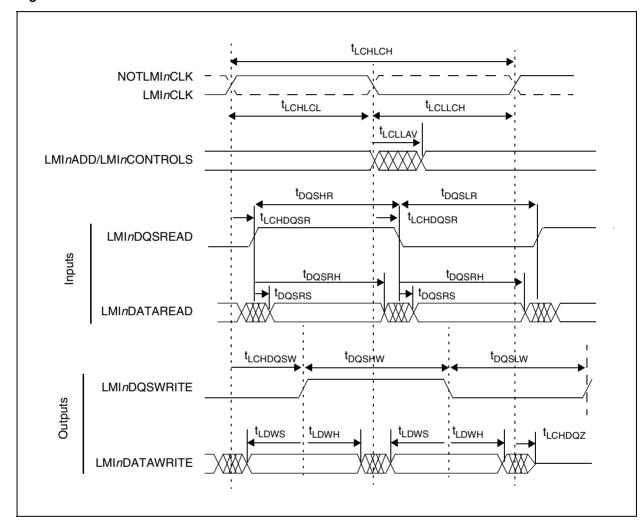

|                                                                                             | 11.9                                                                                         | LMI DDR-SDRAM timings (system and video)                                                                                                                                                                                                                                                                                                                                                    |

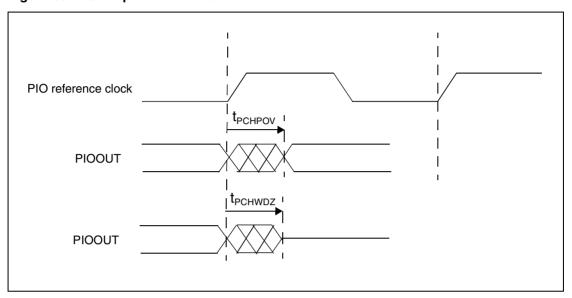

|                                                                                             | 11.10                                                                                        | PIO output AC specification                                                                                                                                                                                                                                                                                                                                                                 |

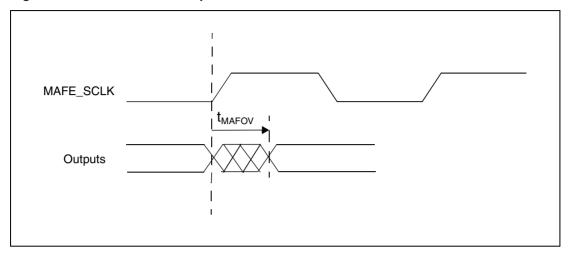

|                                                                                             | 11.11                                                                                        | MAFE interface output AC specification                                                                                                                                                                                                                                                                                                                                                      |

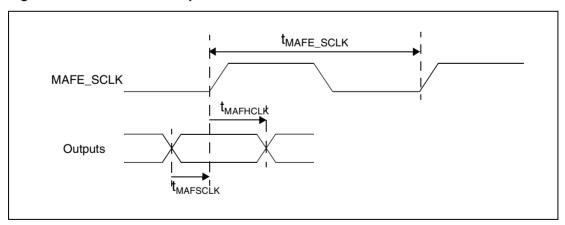

|                                                                                             | 11.12                                                                                        | MAFE interface input AC specification                                                                                                                                                                                                                                                                                                                                                       |

|                                                                                             | Chapter 12                                                                                   | HD and SD triple video DACs                                                                                                                                                                                                                                                                                                                                                                 |

| π                                                                                           | •                                                                                            | Description                                                                                                                                                                                                                                                                                                                                                                                 |

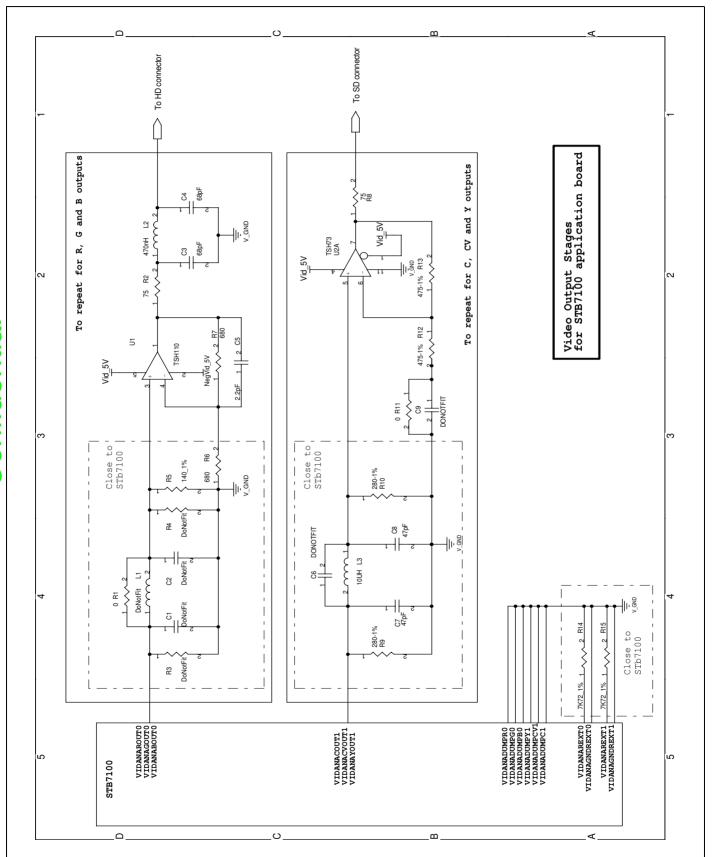

| S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S<br>S | 12.2                                                                                         | Output-stage adaptation and amplification104                                                                                                                                                                                                                                                                                                                                                |

| <u>a</u>                                                                                    |                                                                                              |                                                                                                                                                                                                                                                                                                                                                                                             |

| <u>Ö</u>                                                                                    | Chapter 13                                                                                   | Audio DAC                                                                                                                                                                                                                                                                                                                                                                                   |

|                                                                                             | Chapter 10                                                                                   | Addio DAO                                                                                                                                                                                                                                                                                                                                                                                   |

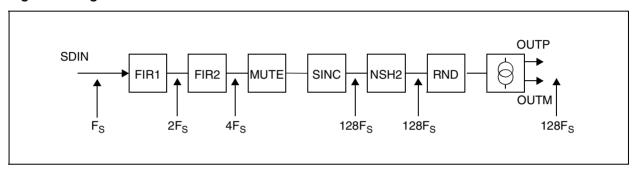

|                                                                                             | 13.1                                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                 |

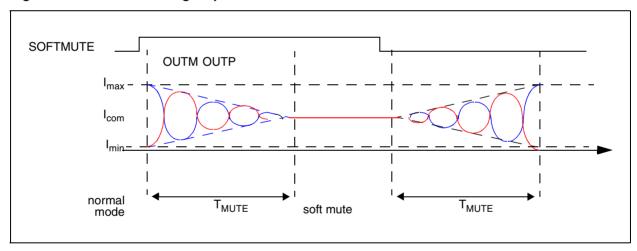

|                                                                                             | 13.1<br>13.2                                                                                 |                                                                                                                                                                                                                                                                                                                                                                                             |

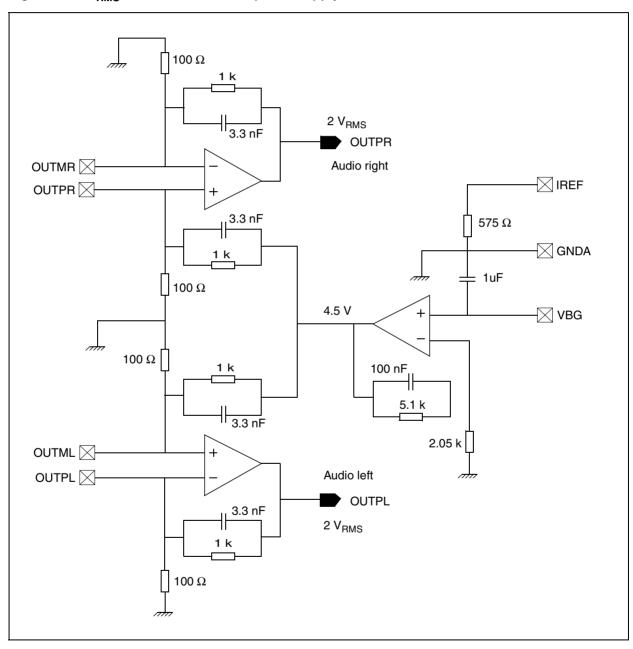

|                                                                                             | 13.1<br>13.2<br>13.3                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                             | 13.1<br>13.2<br>13.3                                                                         | Description                                                                                                                                                                                                                                                                                                                                                                                 |

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b>                                                    | Description.105Operating modes.105Output stage filtering.107PCB layout recommendations.108                                                                                                                                                                                                                                                                                                  |

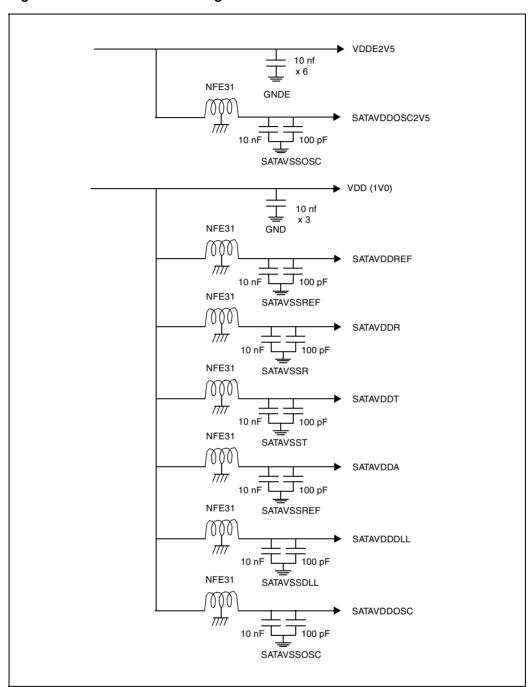

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1                                            | Description.105Operating modes.105Output stage filtering.107PCB layout recommendations.108SATA.108                                                                                                                                                                                                                                                                                          |

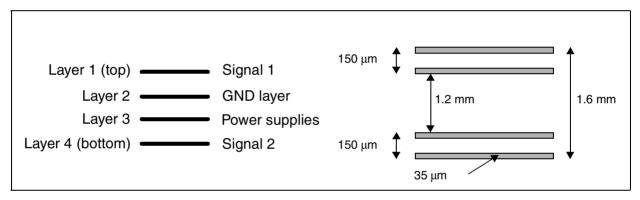

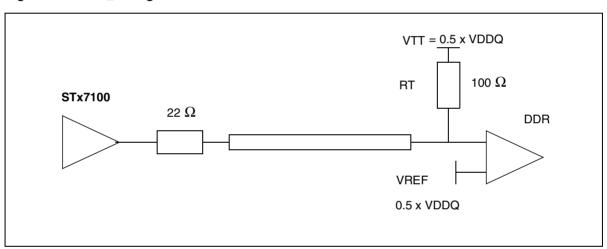

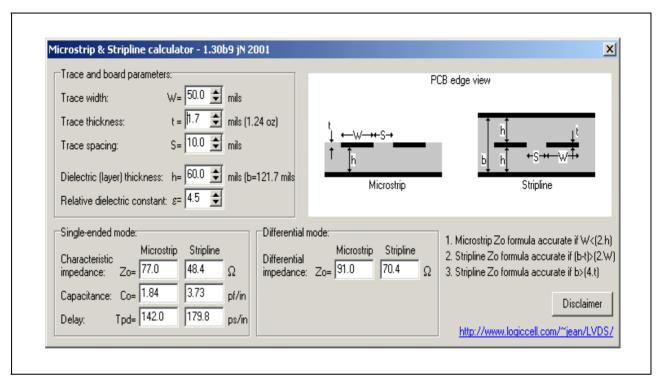

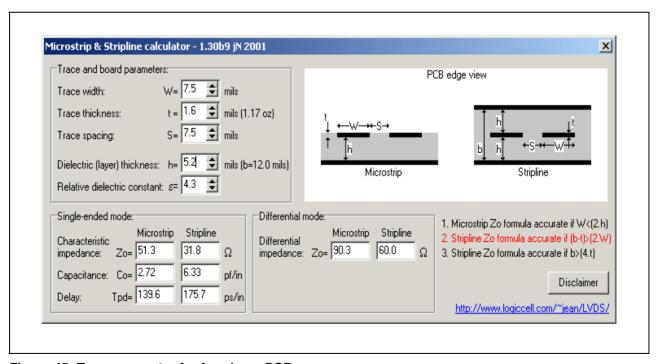

| TUC'O                                                                                       | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2                                    | Description.105Operating modes.105Output stage filtering.107PCB layout recommendations108SATA.108DDR-SDRAM interface.111                                                                                                                                                                                                                                                                    |

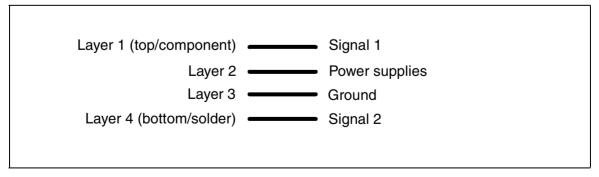

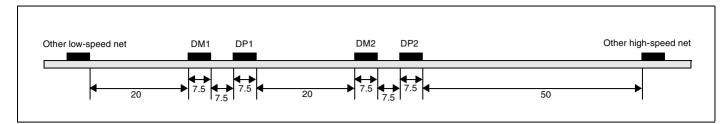

| (CODE                                                                                       | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3                            | Description       .105         Operating modes       .105         Output stage filtering       .107         PCB layout recommendations       108         SATA       .108         DDR-SDRAM interface       .111         USB2.0       .113                                                                                                                                                   |

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3<br>14.4                    | Description       105         Operating modes       105         Output stage filtering       107         PCB layout recommendations       108         SATA       108         DDR-SDRAM interface       111         USB2.0       113         Board design       113                                                                                                                          |

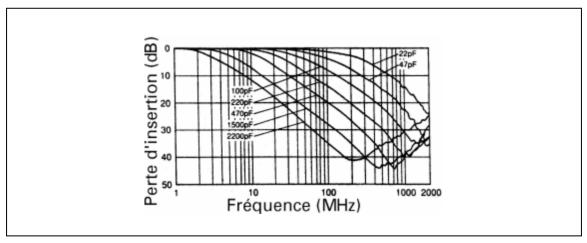

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3<br>14.4<br>14.5            | Description       .105         Operating modes       .105         Output stage filtering       .107         PCB layout recommendations       108         SATA       .108         DDR-SDRAM interface       .111         USB2.0       .113         Board design       .113         Power supplies       .117                                                                                 |

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3<br>14.4                    | Description       105         Operating modes       105         Output stage filtering       107         PCB layout recommendations       108         SATA       108         DDR-SDRAM interface       111         USB2.0       113         Board design       113                                                                                                                          |

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3<br>14.4<br>14.5            | Description       .105         Operating modes       .105         Output stage filtering       .107         PCB layout recommendations       108         SATA       .108         DDR-SDRAM interface       .111         USB2.0       .113         Board design       .113         Power supplies       .117                                                                                 |

|                                                                                             | 13.1<br>13.2<br>13.3<br><b>Chapter 14</b><br>14.1<br>14.2<br>14.3<br>14.4<br>14.5            | Description       .105         Operating modes       .105         Output stage filtering       .107         PCB layout recommendations       108         SATA       .108         DDR-SDRAM interface       .111         USB2.0       .113         Board design       .113         Power supplies       .117                                                                                 |

|                                                                                             | 13.1<br>13.2<br>13.3<br>Chapter 14<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6           | Description       105         Operating modes       105         Output stage filtering       107         PCB layout recommendations       108         SATA       108         DDR-SDRAM interface       111         USB2.0       113         Board design       113         Power supplies       117         HDMI       118         System infrastructure       119                          |

|                                                                                             | 13.1<br>13.2<br>13.3<br>Chapter 14<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6<br>Part 3 | Description       105         Operating modes       105         Output stage filtering       107         PCB layout recommendations       108         SATA       108         DDR-SDRAM interface       111         USB2.0       113         Board design       113         Power supplies       117         HDMI       118         System infrastructure       119         Clocks       120 |

|                                                                                             | 13.1<br>13.2<br>13.3<br>Chapter 14<br>14.1<br>14.2<br>14.3<br>14.4<br>14.5<br>14.6           | Description       105         Operating modes       105         Output stage filtering       107         PCB layout recommendations       108         SATA       108         DDR-SDRAM interface       111         USB2.0       113         Board design       113         Power supplies       117         HDMI       118         System infrastructure       119                          |

|   | _              |

|---|----------------|

|   | w              |

| • |                |

| - | $lue{}$        |

|   |                |

|   | $\overline{0}$ |

| _ | $\widetilde{}$ |

|   | $\cup$         |

| • |                |

| ٩ |                |

|   |                |

|   | $\overline{}$  |

|   |                |

| ( | )              |

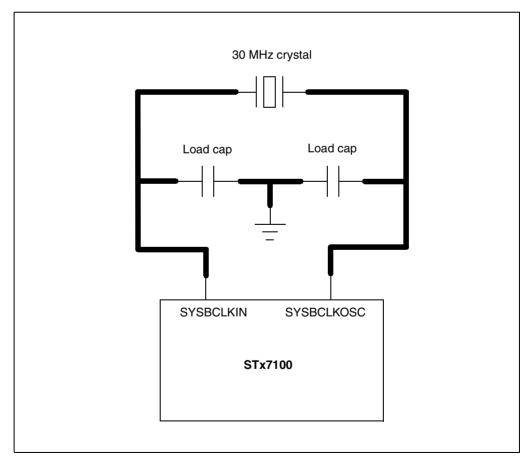

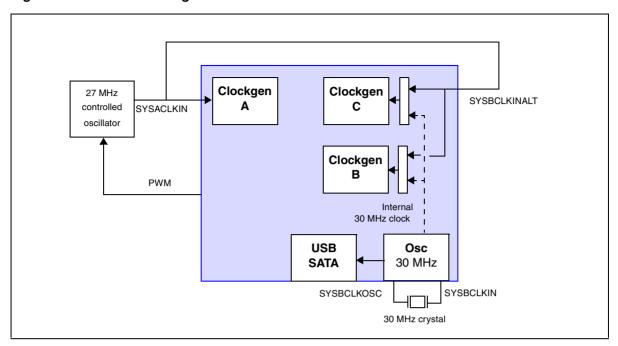

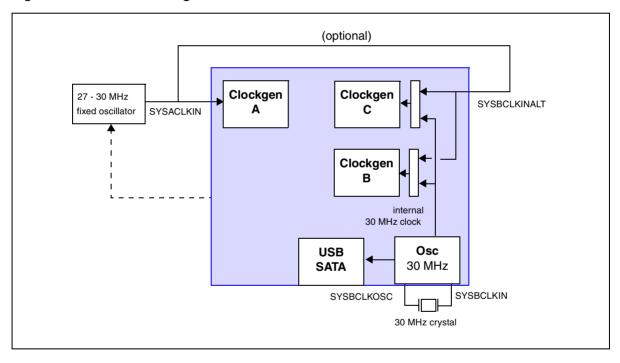

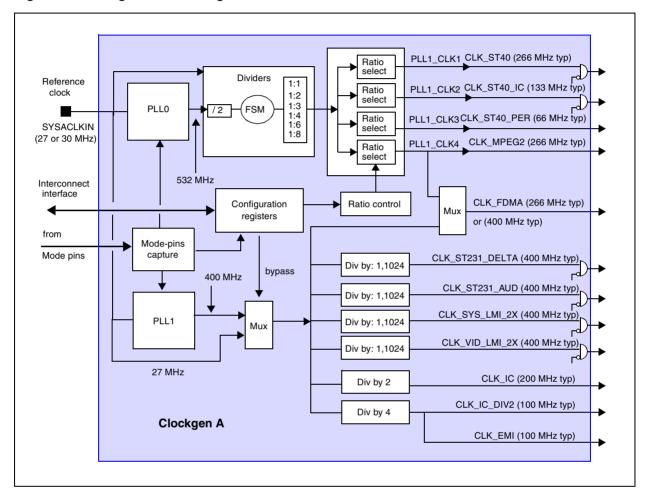

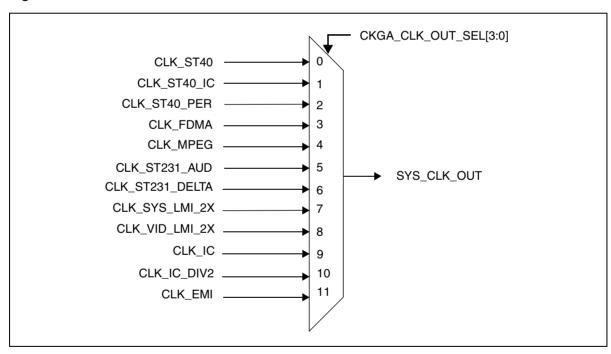

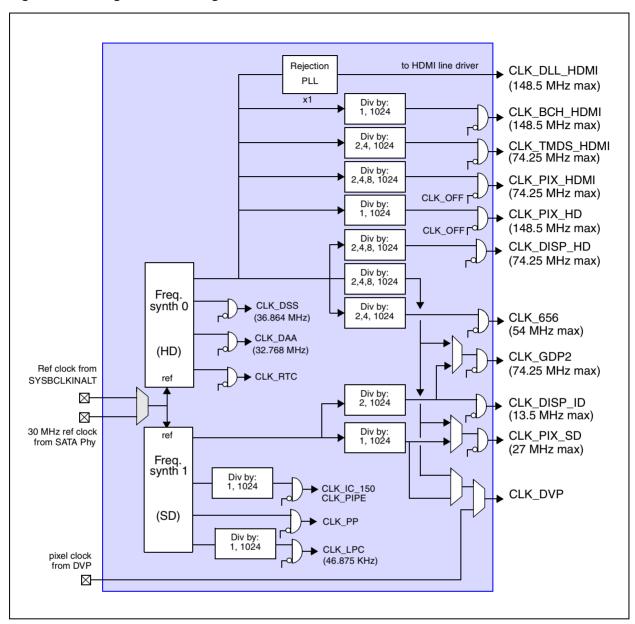

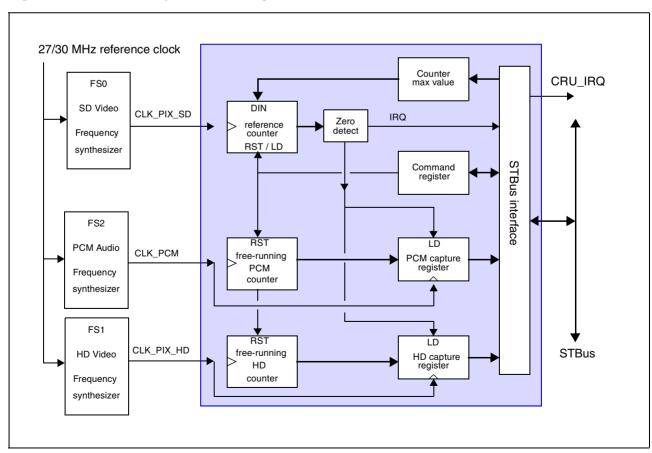

| 15.2                                                                                                                        | Clock generator A                                                                                                                                                                                                                                                                                                                                                                                                                                        |

|-----------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15.3                                                                                                                        | Clock generator B                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Chapter 16                                                                                                                  | Clock registers                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 16.1                                                                                                                        | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| 16.2                                                                                                                        | Clock generator A                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| 16.3                                                                                                                        | Clock generator B                                                                                                                                                                                                                                                                                                                                                                                                                                        |

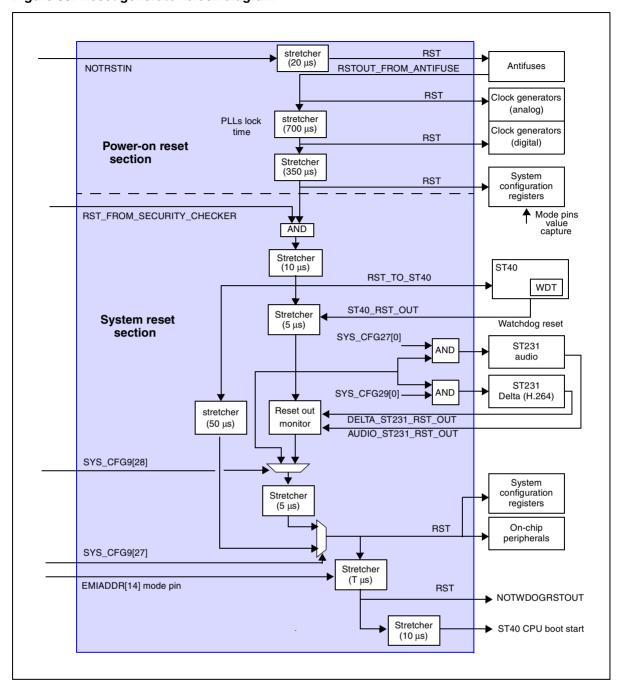

| Chapter 17                                                                                                                  | Reset                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 17.1                                                                                                                        | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17.2                                                                                                                        | Power-on reset                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17.3                                                                                                                        | System reset                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| 17.4                                                                                                                        | Reset sequence                                                                                                                                                                                                                                                                                                                                                                                                                                           |

| 17.5                                                                                                                        | CPUs reset and reset out                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 17.6                                                                                                                        | ST40 watchdog timeout reset                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 17.7                                                                                                                        | NOTWDOGRSTOUT signal length                                                                                                                                                                                                                                                                                                                                                                                                                              |

| Chapter 18                                                                                                                  | Low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                          |

|                                                                                                                             |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18.1                                                                                                                        | Overview                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 18.1<br>18.2                                                                                                                | Overview         164           ST40 low-power modes         165                                                                                                                                                                                                                                                                                                                                                                                          |

| _                                                                                                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 18.2                                                                                                                        | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3                                                                                                                | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3<br>18.4                                                                                                        | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3<br>18.4<br>18.5                                                                                                | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6                                                                                        | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br><b>Chapter 19</b>                                                                   | ST40 low-power modes                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>Chapter 19                                                                          | ST40 low-power modes165Reducing or/and stopping the clocks166ILC interrupt controller: wake-up interrupt166DDR self-refresh167Low-power mode sequence167Low power registers168Boot modes169                                                                                                                                                                                                                                                              |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br><b>Chapter 19</b><br><b>Chapter 20</b><br>20.1                                      | ST40 low-power modes165Reducing or/and stopping the clocks166ILC interrupt controller: wake-up interrupt166DDR self-refresh167Low-power mode sequence167Low power registers168Boot modes169Default mode169                                                                                                                                                                                                                                               |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br><b>Chapter 19</b><br><b>Chapter 20</b><br>20.1<br>20.2                              | ST40 low-power modes       165         Reducing or/and stopping the clocks       166         ILC interrupt controller: wake-up interrupt       166         DDR self-refresh       167         Low-power mode sequence       167         Low power registers       168         Boot modes       169         Default mode       169         Delta ST231 mode       170                                                                                     |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br><b>Chapter 19</b><br><b>Chapter 20</b><br>20.1<br>20.2<br>20.3                      | ST40 low-power modes       165         Reducing or/and stopping the clocks       166         ILC interrupt controller: wake-up interrupt       166         DDR self-refresh       167         Low-power mode sequence       167         Low power registers       168         Boot modes       169         Default mode       169         Delta ST231 mode       170         Audio ST231 mode       170                                                  |

| 18.2<br>18.3<br>18.4<br>18.5<br>18.6<br><b>Chapter 19</b><br><b>Chapter 20</b><br>20.1<br>20.2<br>20.3<br><b>Chapter 21</b> | ST40 low-power modes       165         Reducing or/and stopping the clocks       166         ILC interrupt controller: wake-up interrupt       166         DDR self-refresh       167         Low-power mode sequence       167         Low power registers       168         Boot modes       169         Default mode       169         Delta ST231 mode       170         Audio ST231 mode       170         System configuration registers       171 |

| 21.4                                | System status                         |     |

|-------------------------------------|---------------------------------------|-----|

| 21.5                                | Configuration                         |     |

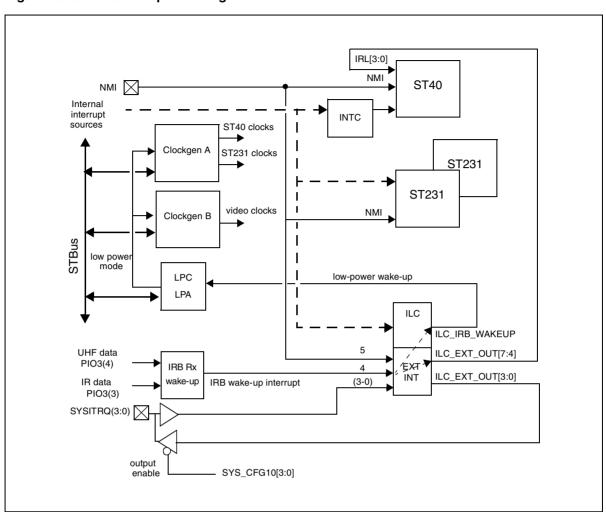

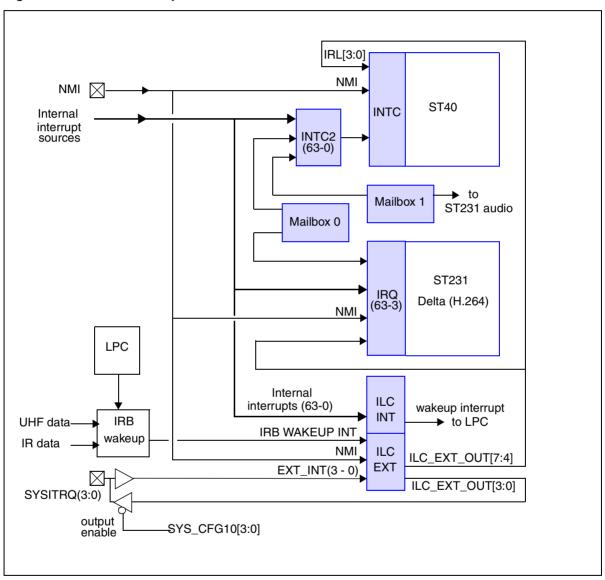

| Chapter 22                          | Interrupt system                      | 196 |

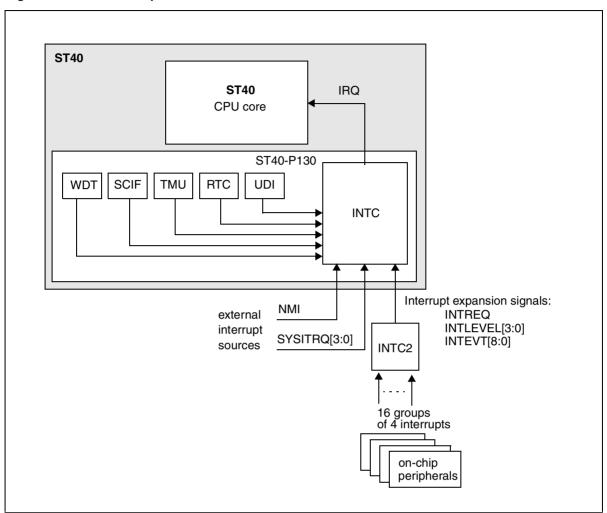

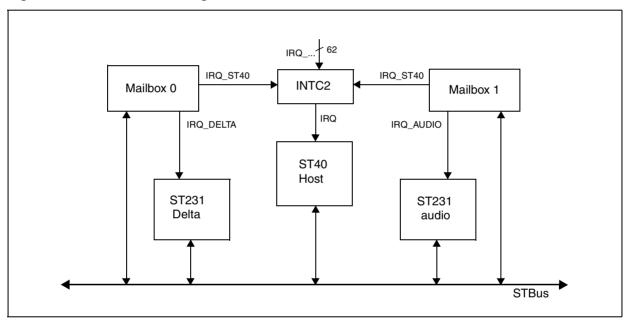

| 22.1                                | ST40 Interrupt network                | 196 |

| 22.2                                | Delta (H.264) ST231 interrupt network |     |

| 22.3                                | STx7100 interrupt network             |     |

| Chapter 23                          | Interrupt maps                        | 200 |

| 23.1                                | ST40 interrupts                       |     |

| 23.2                                | INTC2 secondary interrupt controller  |     |

| 23.3                                | Delta (H.264) ST231 interrupts        |     |

| 23.4                                | STx7100 interrupts                    |     |

| Chapter 24                          | Interrupt registers                   | 208 |

| 24.1                                | Interrupt level controler (ILC)       |     |

| 24.2                                | INTC2 interrupt controller            |     |

| 24.1<br>24.2<br><b>O</b> Chapter 25 | Programmable I/O (PIO) ports          | 216 |

| Chapter 26                          | Programmable I/O ports registers      | 217 |

| Chapter 27                          | Mailboxes                             | 223 |

| 27.1                                | Mailbox register operation            |     |

| Chapter 28                          | Mailbox registers                     | 226 |

| Part 4                              | Memory                                | 230 |

| Chapter 29                          | Local memory interface (LMI)          | 231 |

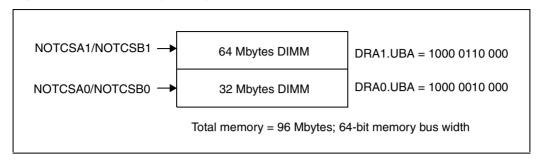

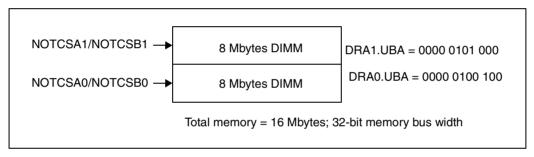

| 29.1                                | Introduction                          |     |

| 29.2                                | SDRAM interface                       |     |

| Chapter 30                          | LMI registers                         | 242 |

| Chapter 31                          | External memory interface (EMI)       | 250 |

|                                     |                                       |     |

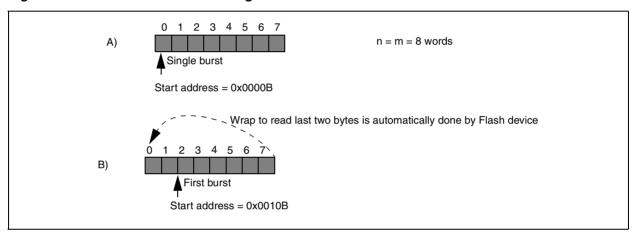

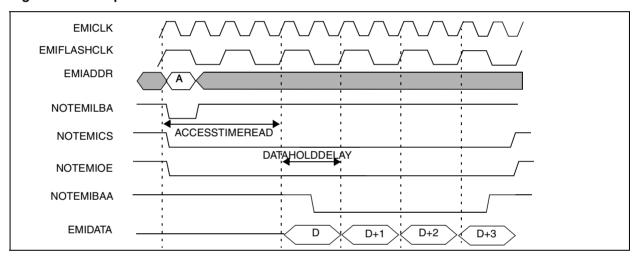

|          | 31.1                                 | Overview                                                                                                                                        | 250                     |

|----------|--------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------|

|          | 31.2                                 | Features                                                                                                                                        | 250                     |

|          | 31.3                                 | EMI interface pins                                                                                                                              | 251                     |

|          | 31.4                                 | EMI address map                                                                                                                                 | 252                     |

|          | 31.5                                 | EMI operation                                                                                                                                   | 252                     |

|          | 31.6                                 | Default/reset configuration                                                                                                                     | 253                     |

|          | 31.7                                 | Peripheral interface (with synchronous Flash memory support)                                                                                    | 254                     |

|          | 31.8                                 | Chip select allocation/bank configuration                                                                                                       | 260                     |

|          | 31.9                                 | Address bus extension to low order bits                                                                                                         | 260                     |

|          | 31.10                                | PC card interface                                                                                                                               | 261                     |

|          | 31.11                                | External bus mastering                                                                                                                          | 262                     |

|          | 31.12                                | EMI buffer                                                                                                                                      | 262                     |

|          | Chapter 32                           | EMI registers                                                                                                                                   | 263                     |

|          | 32.1                                 | Overview                                                                                                                                        | 263                     |

| <u>ಹ</u> | 32.2                                 | EMI register descriptions                                                                                                                       | 266                     |

| <u>6</u> | 32.3                                 | EMI buffer register descriptions                                                                                                                | 273                     |

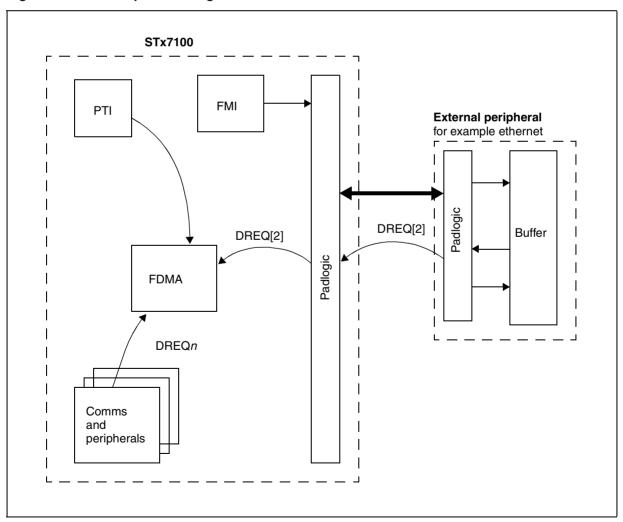

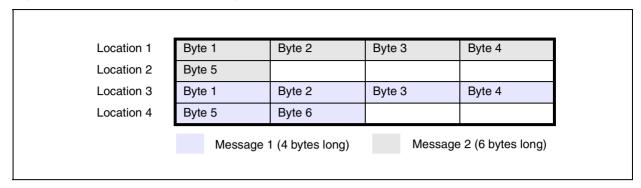

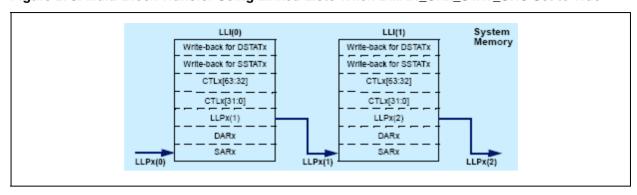

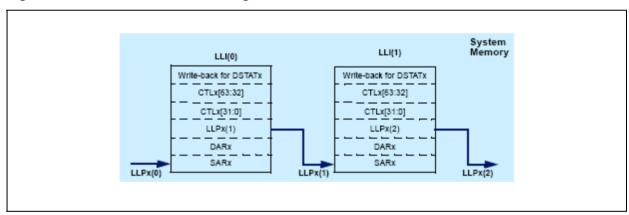

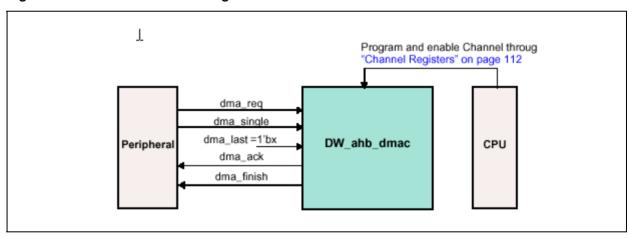

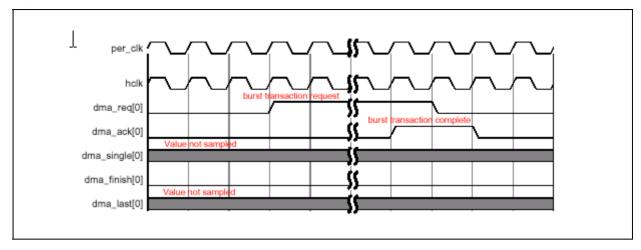

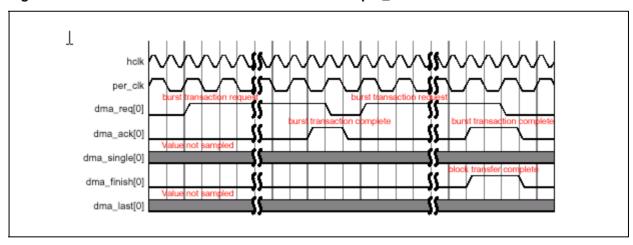

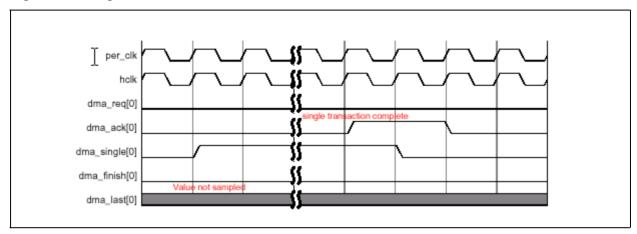

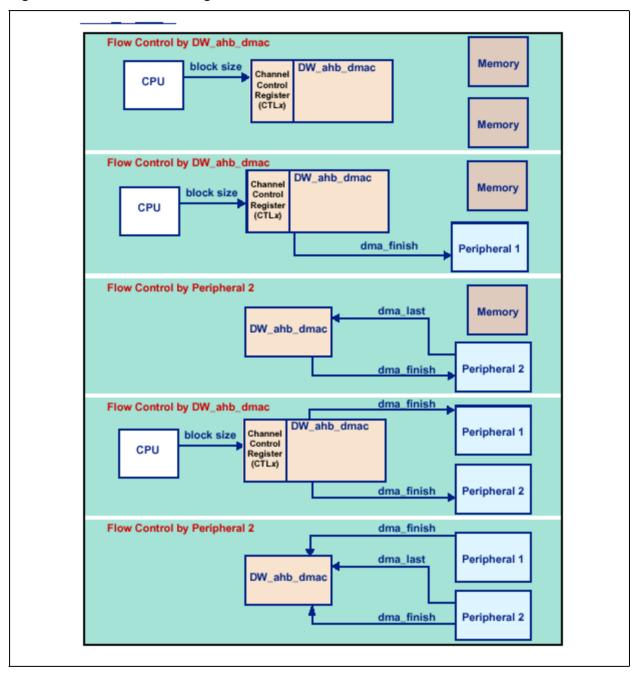

| 0        | Chapter 33                           | DMA network                                                                                                                                     | 275                     |

|          | 33.1                                 | DMA requests and channels                                                                                                                       | 275                     |

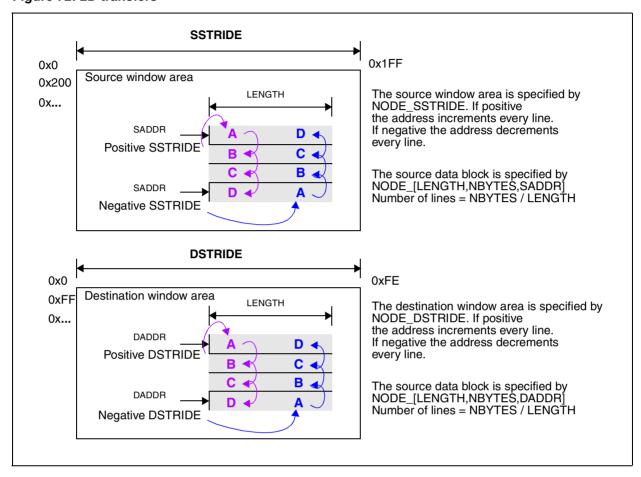

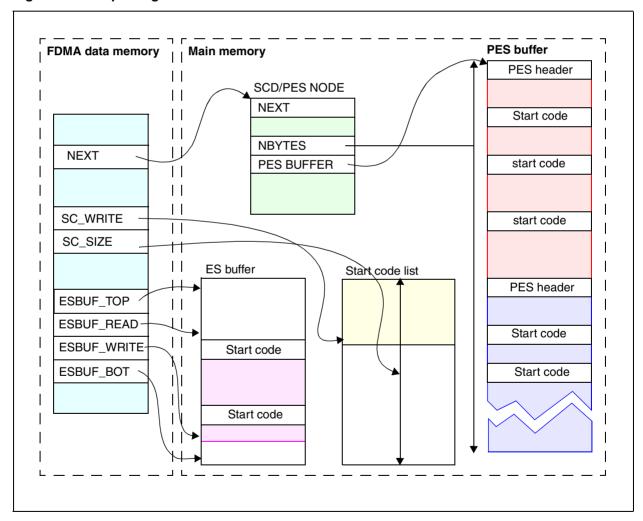

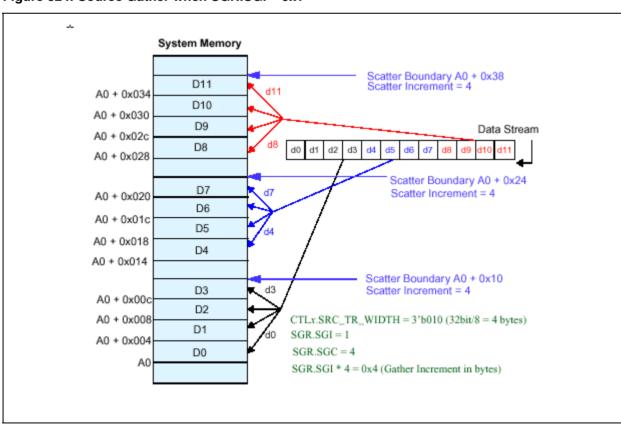

| ک        | Chapter 34                           | Flexible DMA (FDMA)                                                                                                                             | 277                     |

|          | •                                    | Channel structures                                                                                                                              |                         |

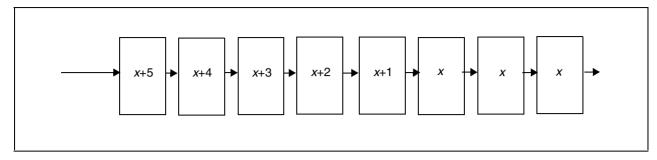

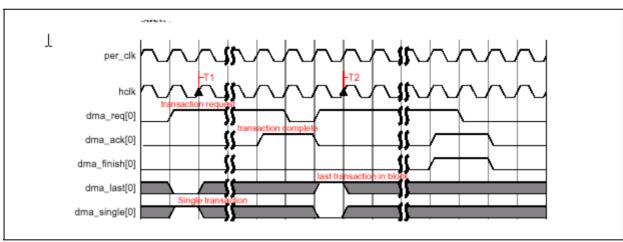

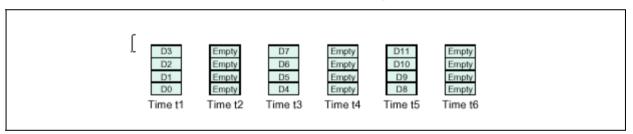

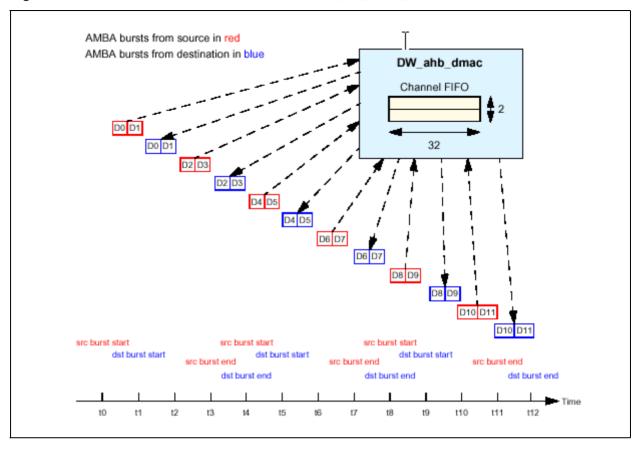

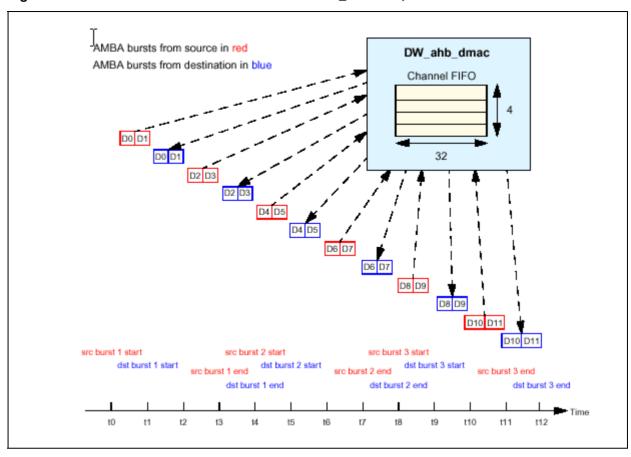

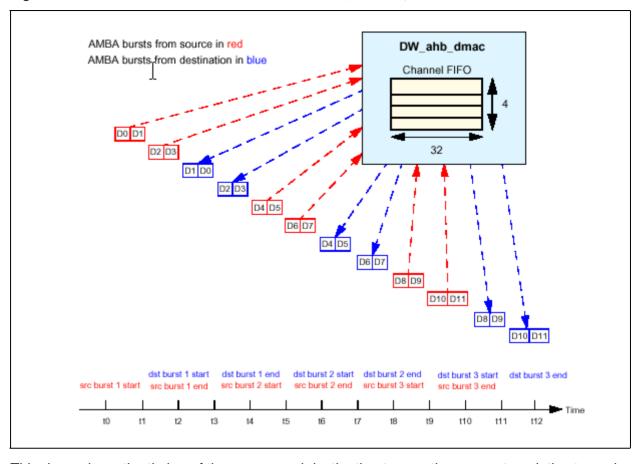

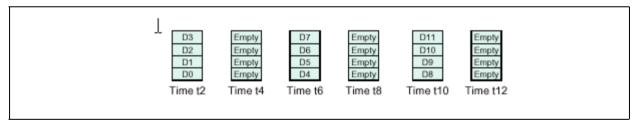

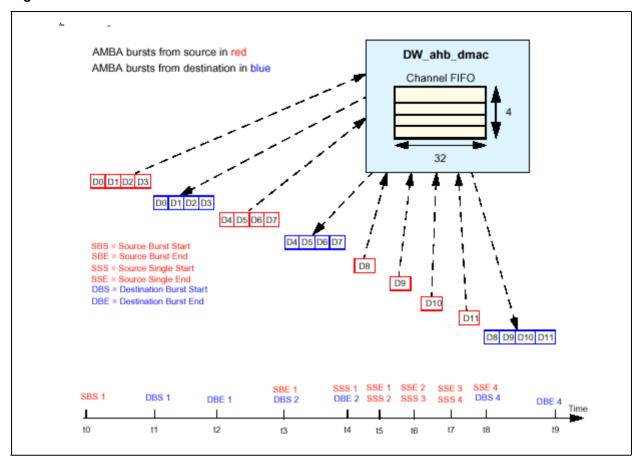

|          | 34.2                                 | FDMA timing model                                                                                                                               |                         |

|          | 34.3                                 | Operating the FDMA                                                                                                                              |                         |

|          | 0.4.4                                |                                                                                                                                                 |                         |

|          | 34.4                                 | Setting up FDMA transfers                                                                                                                       | 283                     |

|          |                                      |                                                                                                                                                 |                         |

|          | Chapter 35                           | Flexible DMA (FDMA) registers                                                                                                                   | 291                     |

|          | <b>Chapter 35</b> 35.1               | Flexible DMA (FDMA) registers                                                                                                                   | <b>291</b>              |

|          | <b>Chapter 35</b> 35.1 35.2          | Flexible DMA (FDMA) registers  FDMA interface  Channel interface                                                                                | <b>291</b><br>293       |

|          | <b>Chapter 35</b> 35.1 35.2 35.3     | Flexible DMA (FDMA) registers  FDMA interface  Channel interface  Command mailbox                                                               | 291<br>293<br>294       |

|          | 35.1<br>35.2<br>35.3<br>35.4         | Flexible DMA (FDMA) registers  FDMA interface  Channel interface  Command mailbox  Interrupt mailbox                                            | 291 293 294 297         |

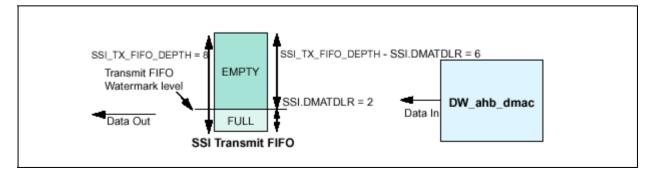

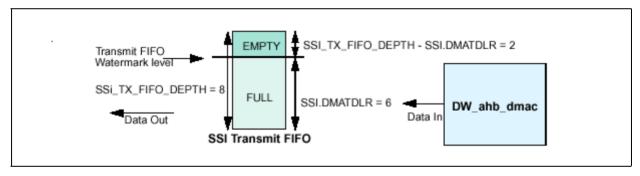

|          | 35.1<br>35.2<br>35.3<br>35.4<br>35.5 | Flexible DMA (FDMA) registers  FDMA interface  Channel interface  Command mailbox  Interrupt mailbox  Memory-to-memory moves and paced transfer | 291 293 294 297 298     |

|          | 35.1<br>35.2<br>35.3<br>35.4         | Flexible DMA (FDMA) registers  FDMA interface  Channel interface  Command mailbox  Interrupt mailbox                                            | 291 293 294 297 298 300 |

| Pa   | rt 5                 | Transport Interface                              |

|------|----------------------|--------------------------------------------------|

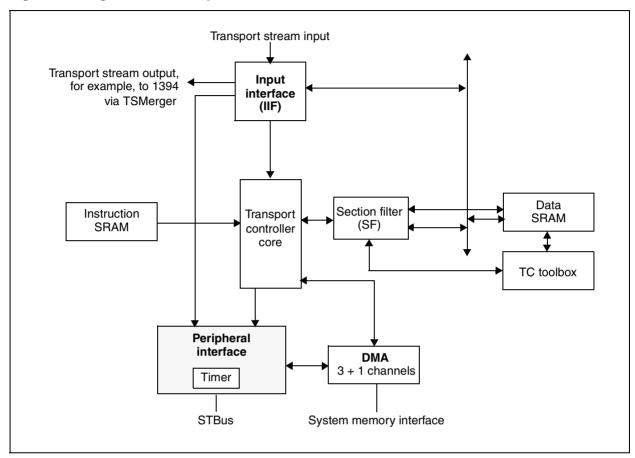

| Cha  | apter 36             | Programmable transport interface (PTI)           |

|      | 36.1                 | Overview                                         |

|      | 36.2                 | PTI functions                                    |

|      | 36.3                 | PTI architecture                                 |

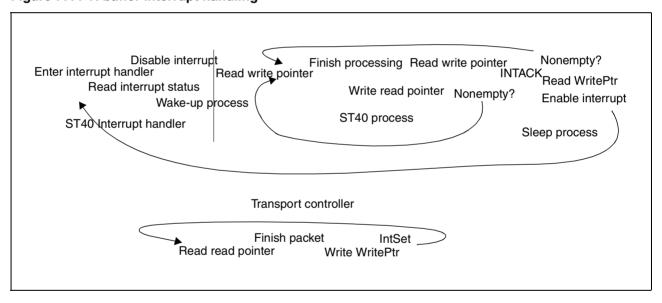

|      | 36.4                 | PTI operation                                    |

|      | 36.5                 | Interrupt handling                               |

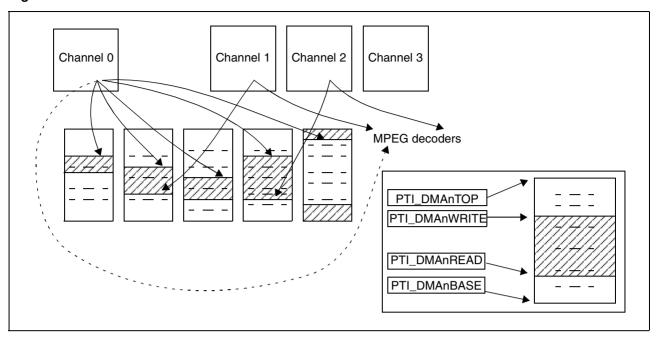

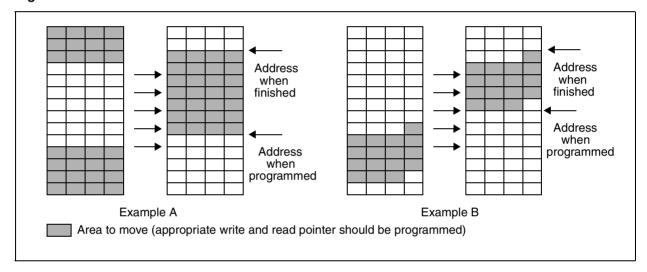

|      | 36.6                 | DMA operation                                    |

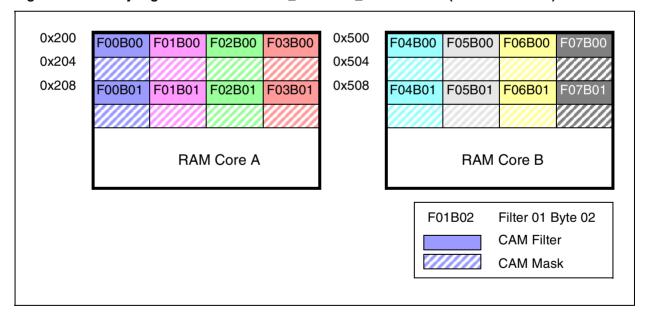

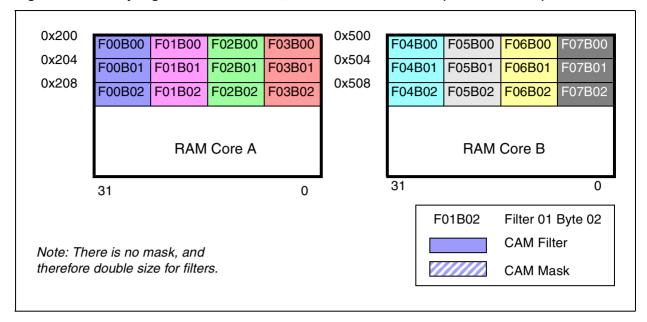

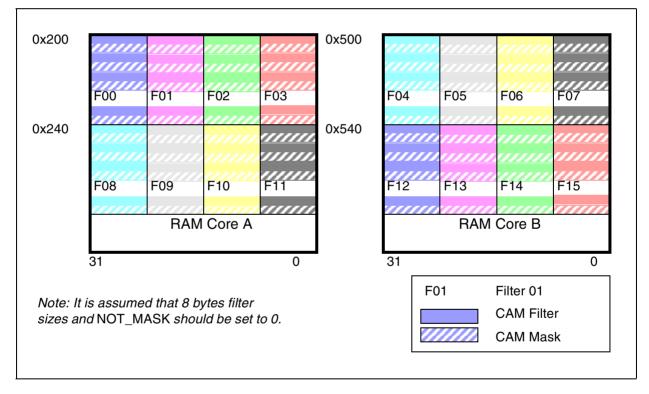

|      | 36.7                 | Section filter                                   |

| Cha  | apter 37             | Programmable transport interface (PTI) registers |

|      | 37.1                 | DMA                                              |

|      | 37.2                 | Input interface                                  |

| _    | 37.3                 | PTI configuration                                |

| ntia | 37.4                 | Transport controller mode                        |

| Cha  | 38.1<br>38.2<br>38.3 | Transport stream merger and router               |

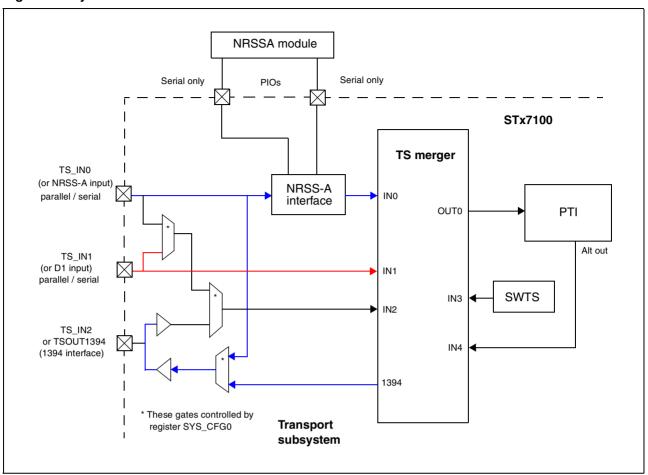

| ij   | 38.1                 | Overview                                         |

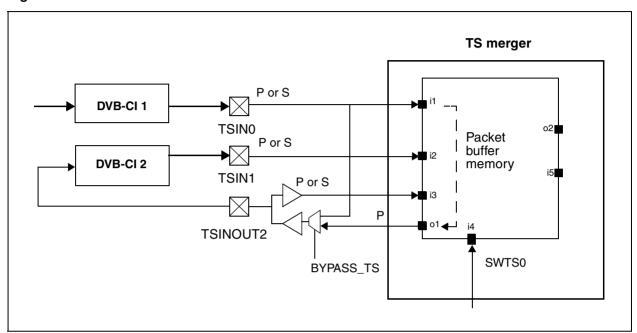

| o    | 38.2                 | DVB common interface                             |

| Ö    | 38.3                 | NRSS-A interface                                 |

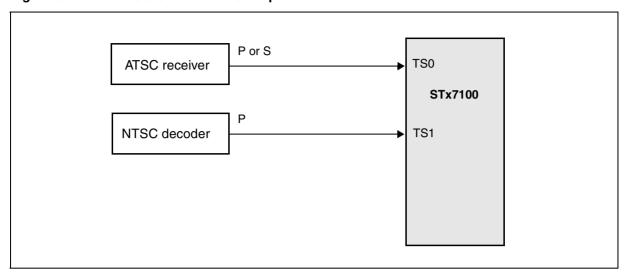

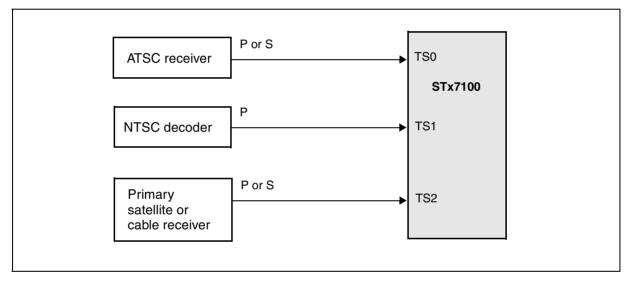

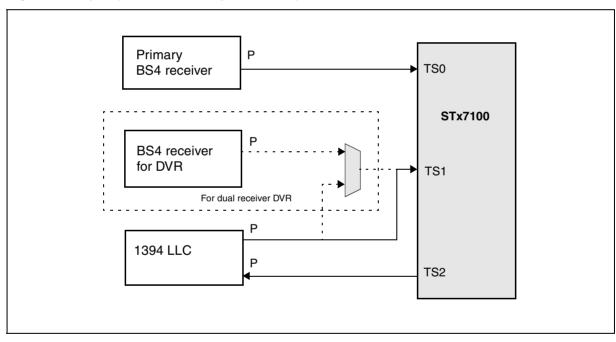

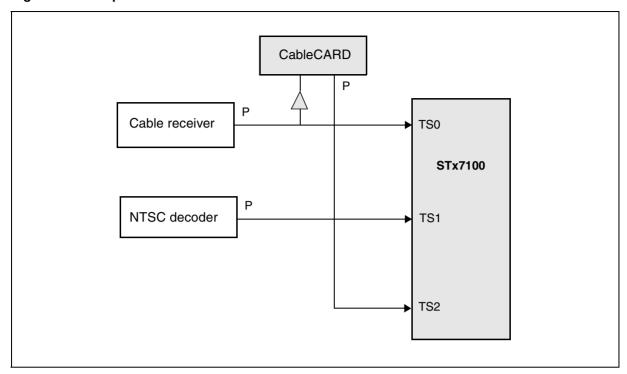

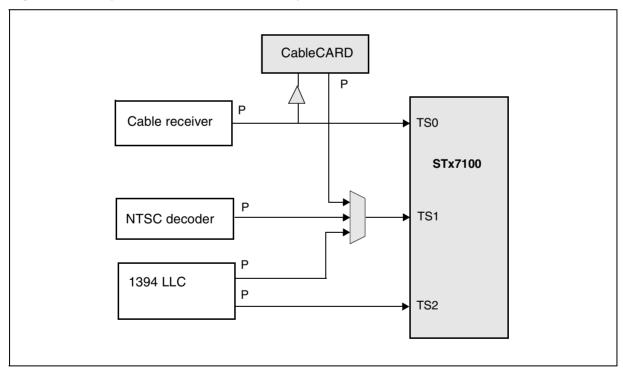

|      | 38.4                 | Input examples                                   |

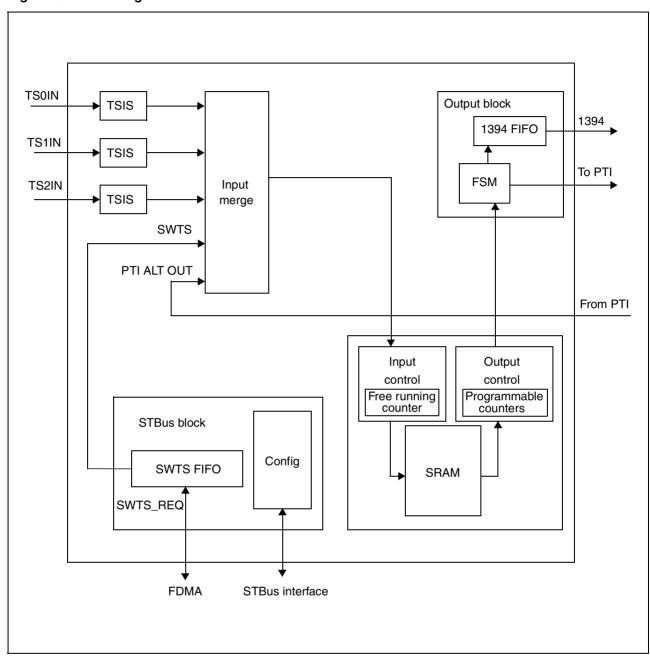

|      | 38.5                 | Architecture                                     |

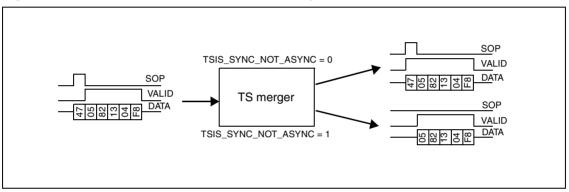

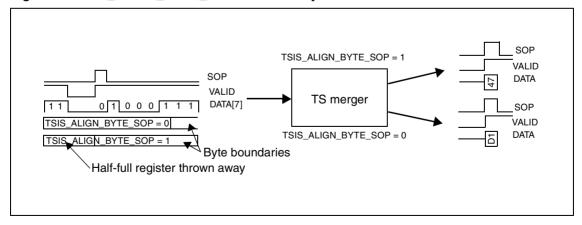

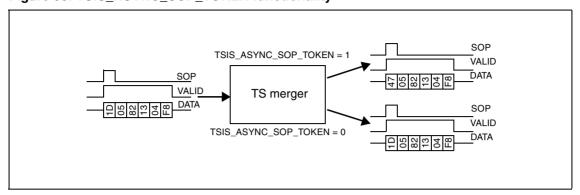

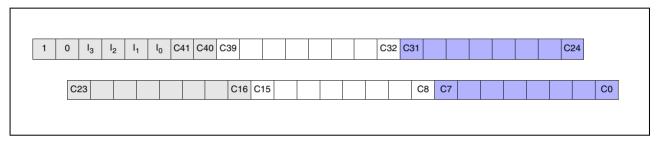

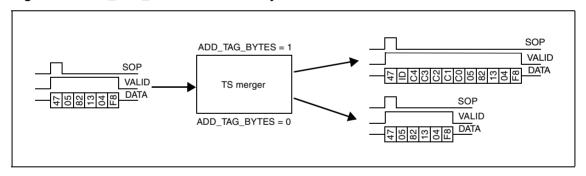

|      | 38.6                 | Transport stream formats                         |

|      | 38.7                 | Packet buffering                                 |

|      | 38.8                 | Transport stream inputs                          |

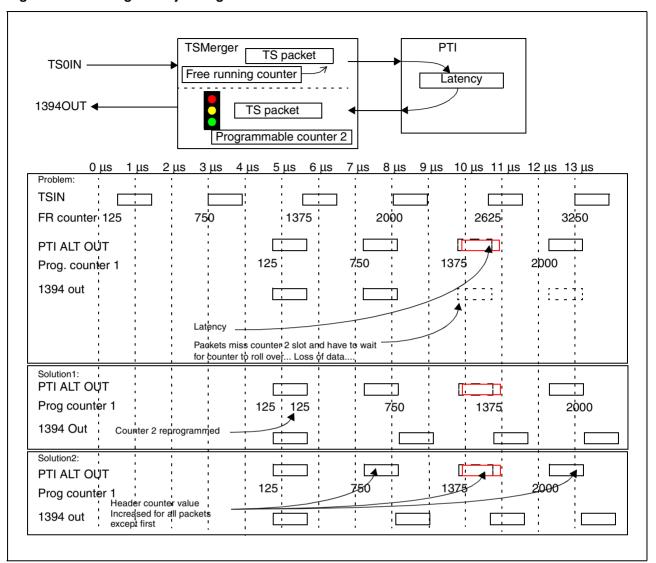

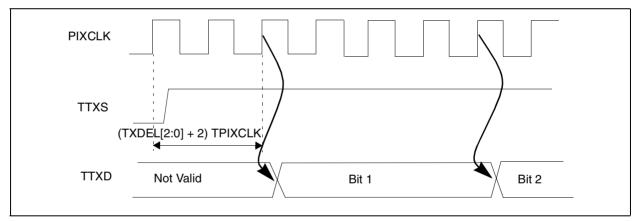

|      | 38.9                 | Transport stream output                          |

| Cha  | apter 39             | Transport stream merger and router registers     |

| Pa   | rt 6                 | Video372                                         |

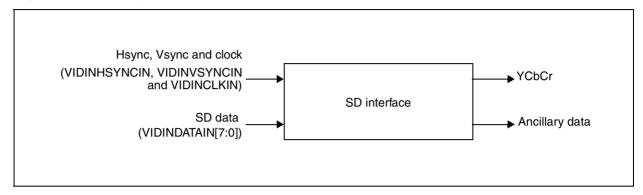

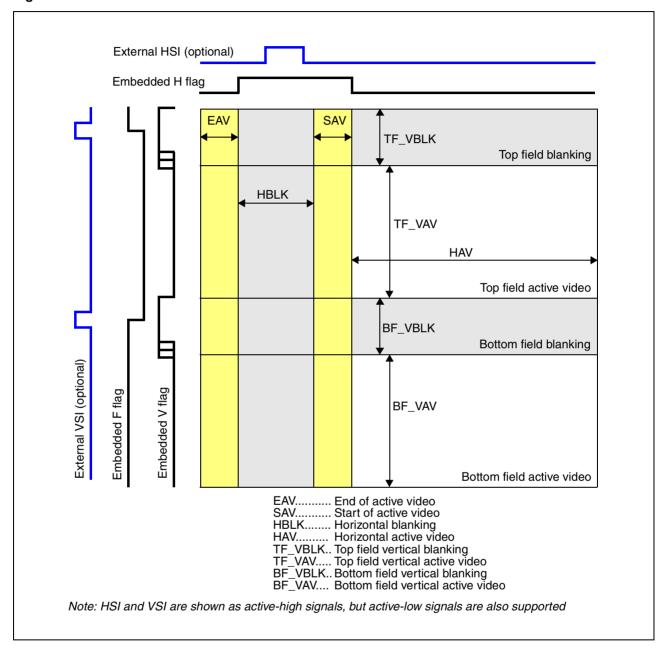

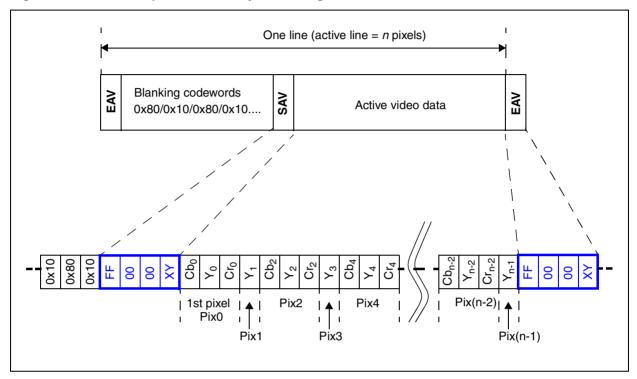

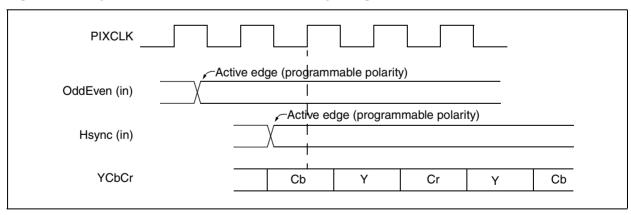

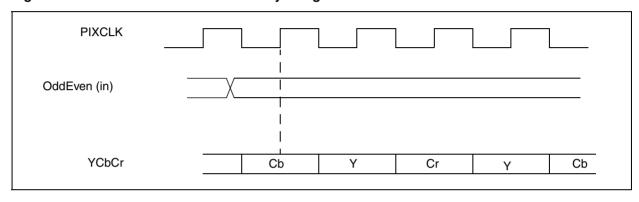

| Cha  | apter 40             | Digital video port (DVP) input                   |

|      | 40.1                 | Factoria a                                       |

|      | 40.1                 | Features                                         |

|          | 40.3       | Ancillary data decoder              |

|----------|------------|-------------------------------------|

| C        | Chapter 41 | Digital video port (DVP) registers  |

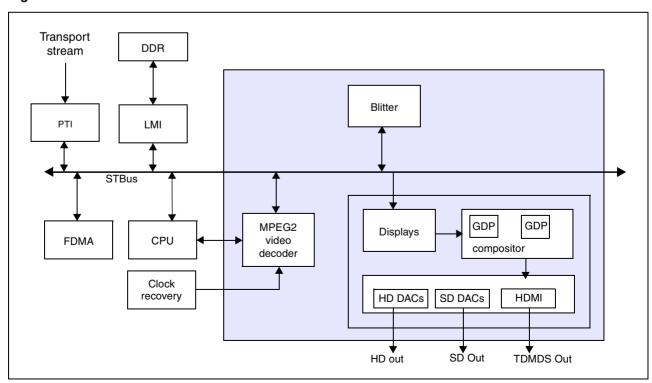

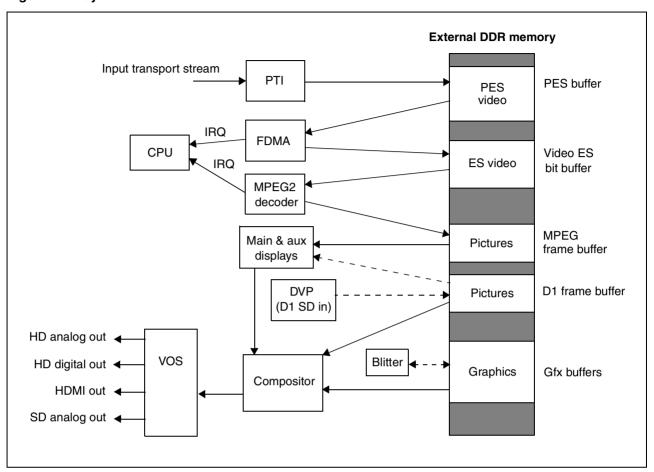

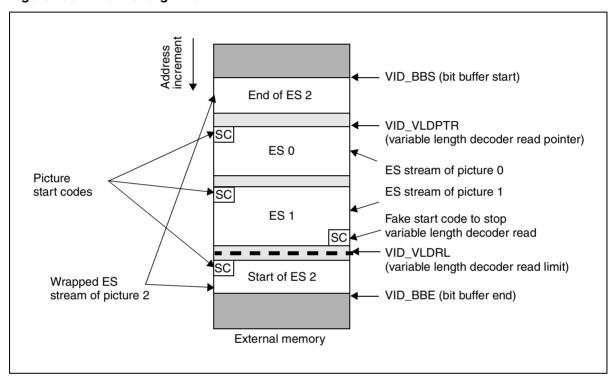

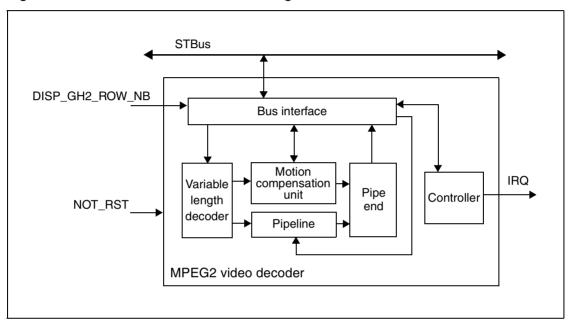

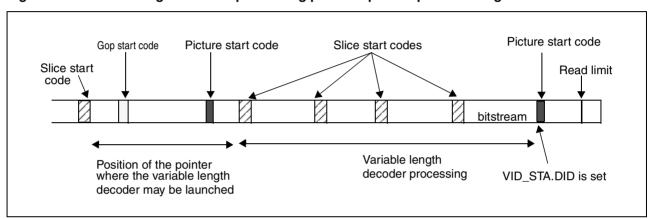

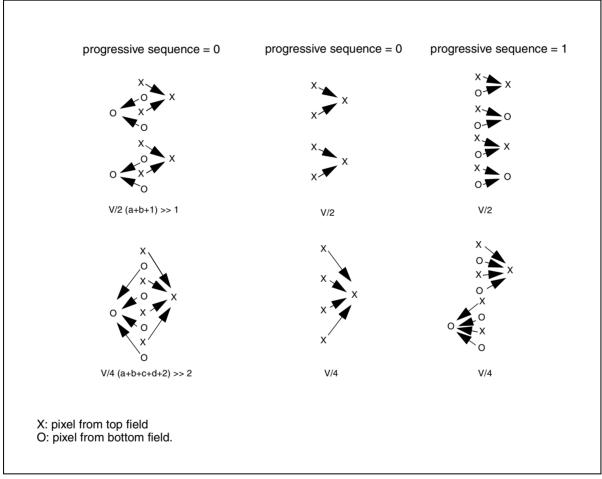

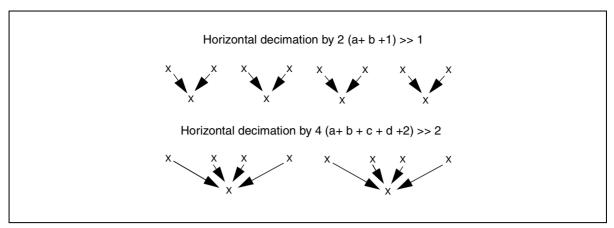

| C        | Chapter 42 | MPEG2 video decoder                 |

|          | 42.1       | Overview                            |

|          | 42.2       | Main functions                      |

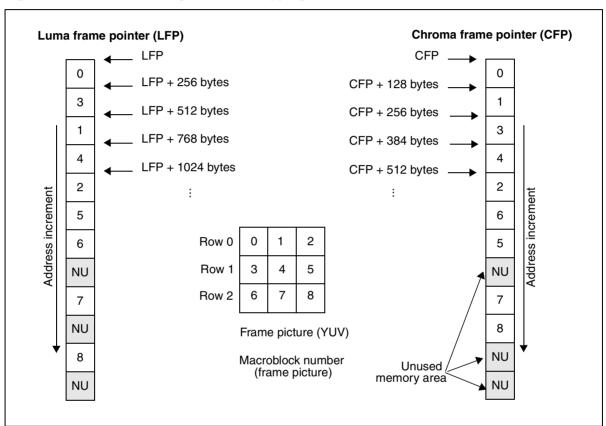

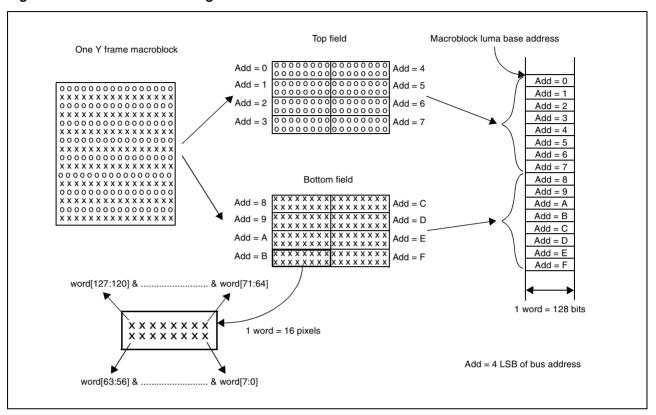

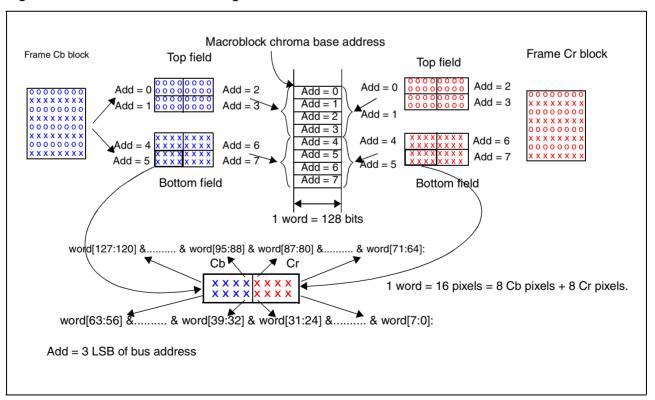

|          | 42.3       | Buffer organization                 |

|          | 42.4       | Video decoding tasks                |

|          | 42.5       | Video decoding                      |

|          | 42.6       | Resets                              |

| C        | Chapter 43 | MPEG2 video decoder registers       |

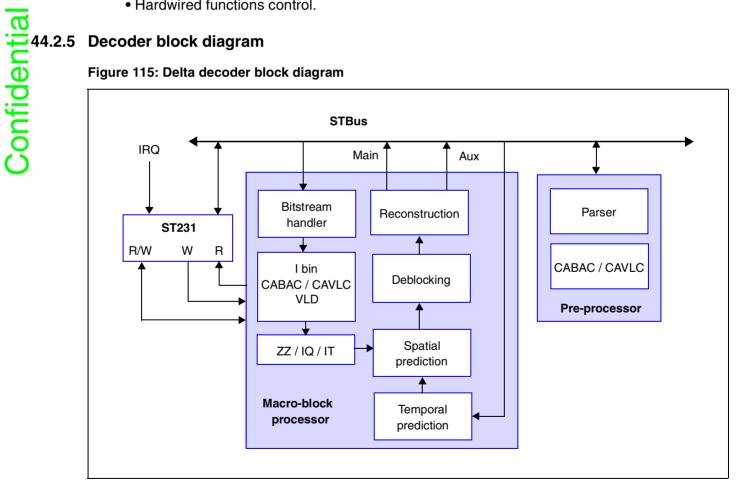

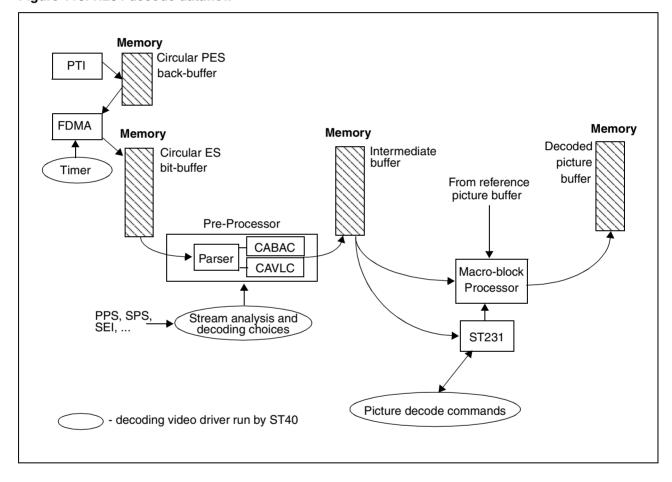

| C        | Chapter 44 | H.264 video decoder 418             |

|          | 44.1       | Introduction                        |

| ַ        | 44.2       | Decoder main features               |

| _<br>D   | 44.3       | H.264 decoder interface             |

| 5        | 44.4       | Firmware                            |

|          | 44.5       | H.264 decoder reset                 |

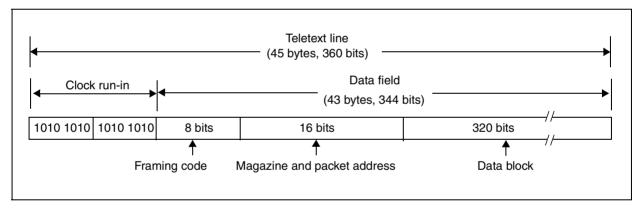

| )<br>) ( | hapter 45  | Teletext DMA 423                    |

|          | 45.1       | Teletext DMA overview423            |

|          | 45.2       | Teletext packet format              |

|          | 45.3       | Data transfer sequence              |

|          | 45.4       | Interrupt control                   |

|          | 45.5       | DENC teletext registers424          |

|          | 45.6       | Teletext external interface         |

| C        | Chapter 46 | Teletext DMA registers              |

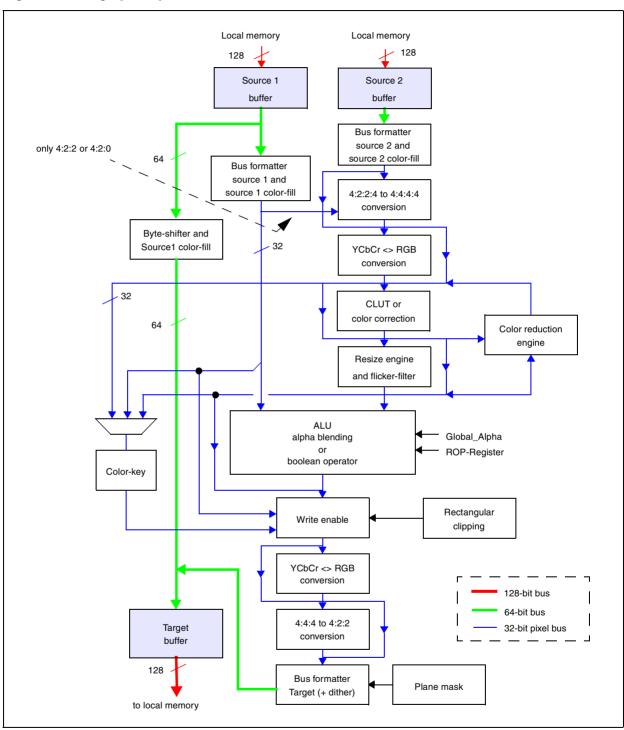

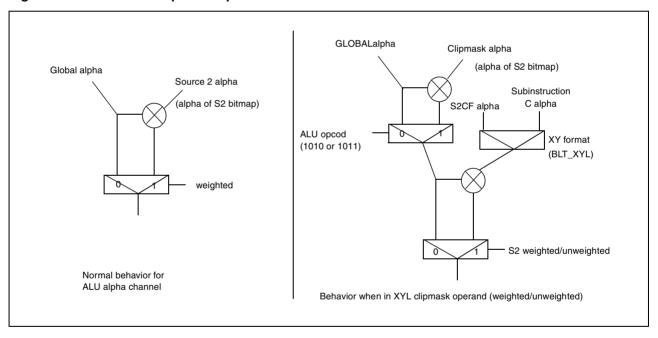

| C        | Chapter 47 | 2D graphics processor (blitter) 428 |

|          | 47.1       | Overview                            |

|          | 47.2       | Functions                           |

|          | 47.3       | Functional block diagram430         |

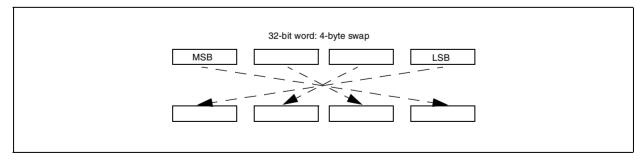

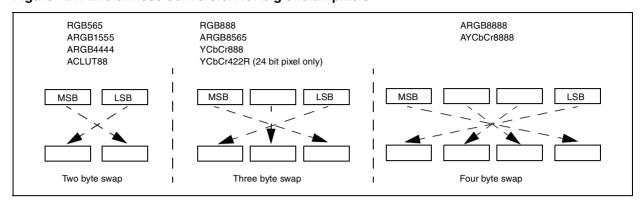

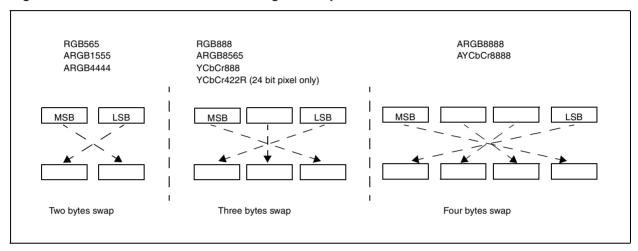

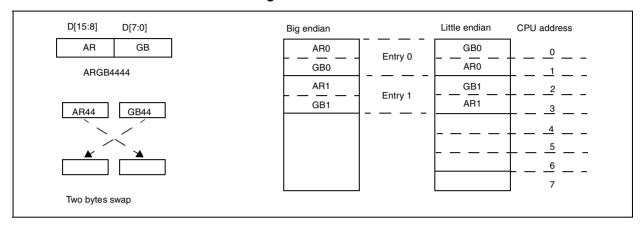

|          | 47.4       | Endianness support                  |

|               | 47.5                                                                            | Bilitter functions                                                                                                                                                                                                                                                                                             |

|---------------|---------------------------------------------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

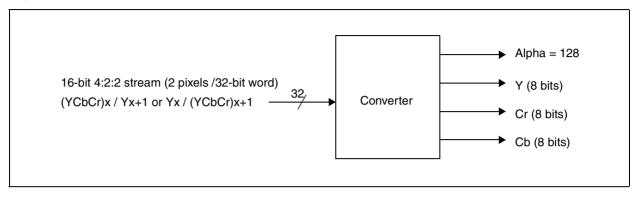

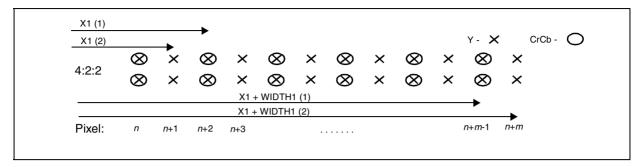

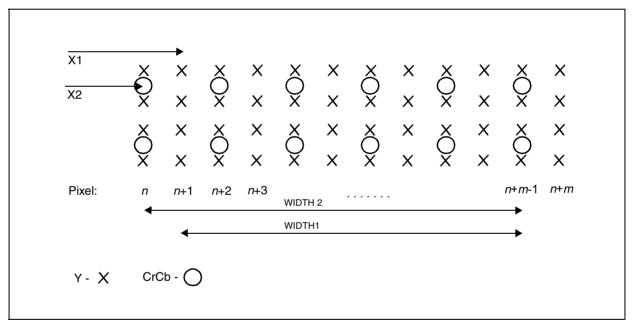

|               | 47.6                                                                            | Using the 4:2:x macroblock-based plane as a source                                                                                                                                                                                                                                                             |

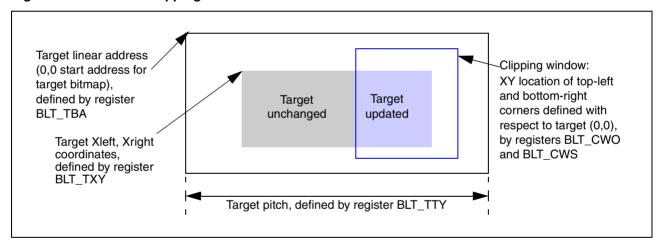

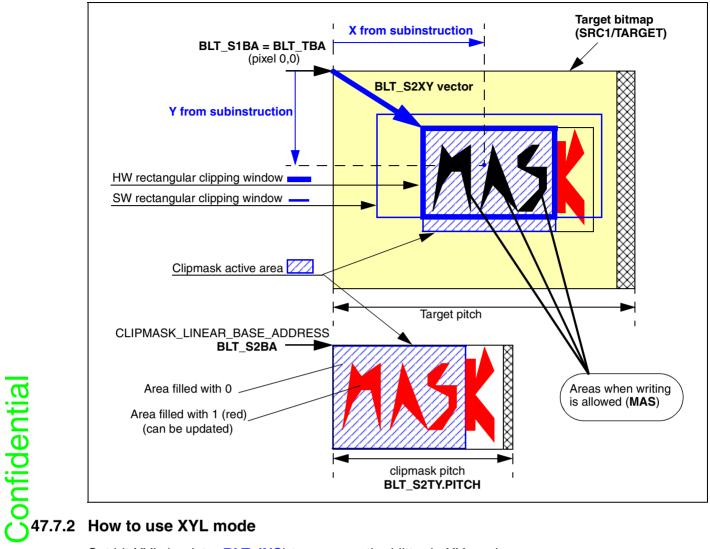

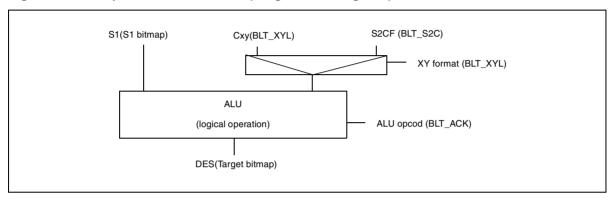

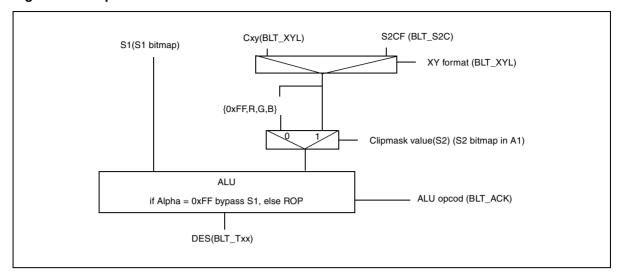

|               | 47.7                                                                            | Blitter XYL mode                                                                                                                                                                                                                                                                                               |

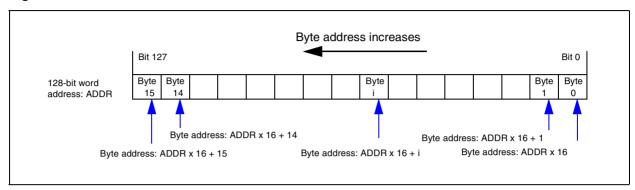

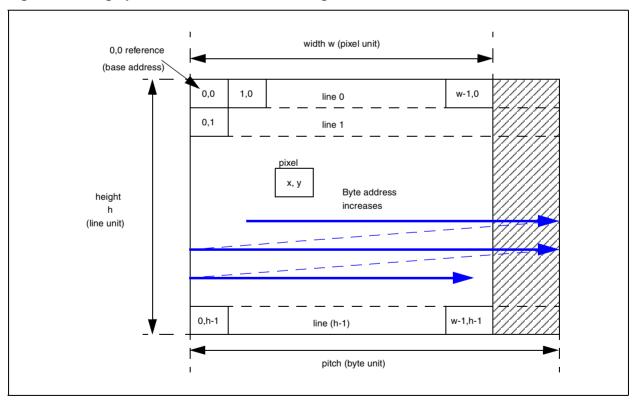

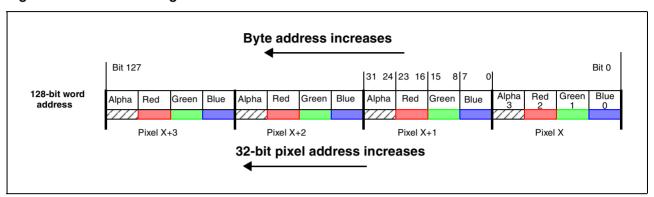

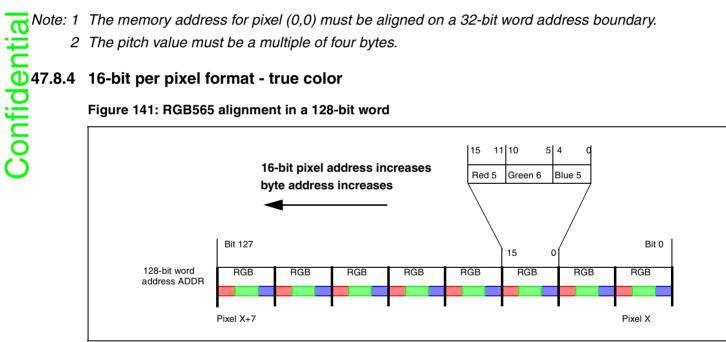

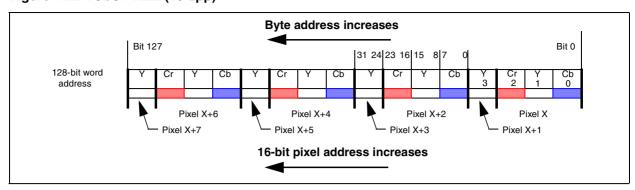

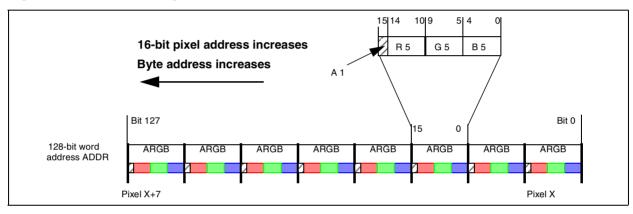

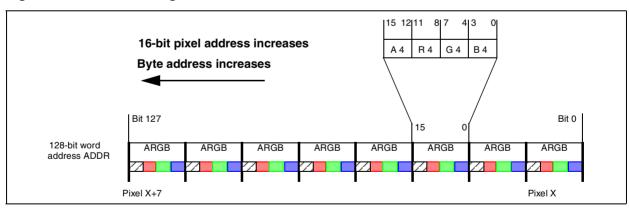

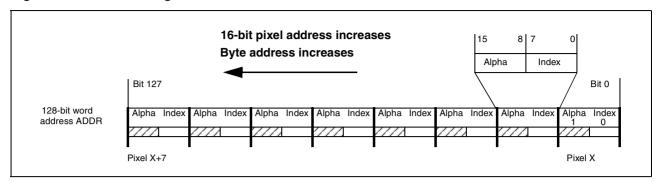

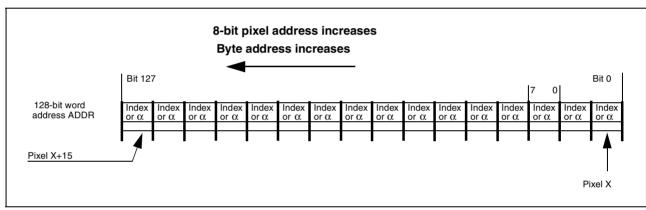

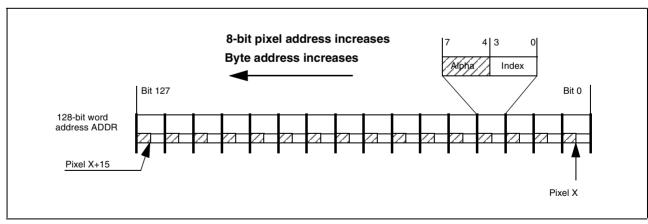

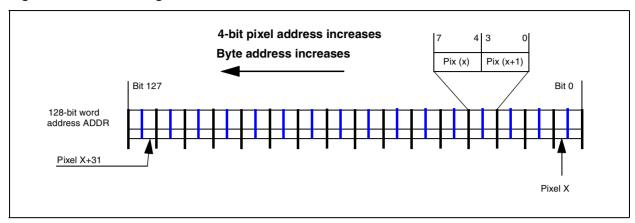

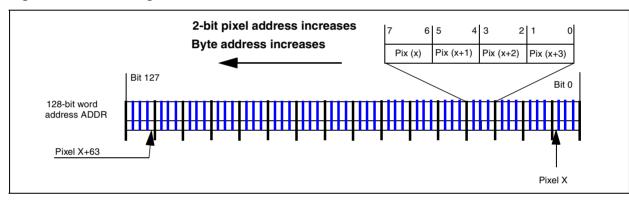

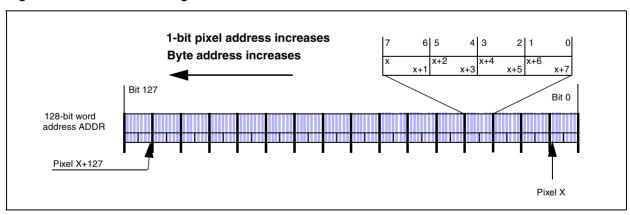

|               | 47.8                                                                            | Local memory storage of supported graphics formats                                                                                                                                                                                                                                                             |

| Ch            | apter 48                                                                        | 2D graphics processor registers                                                                                                                                                                                                                                                                                |

|               | 48.1                                                                            | Register map                                                                                                                                                                                                                                                                                                   |

|               | 48.2                                                                            | Register descriptions                                                                                                                                                                                                                                                                                          |

|               | 48.3                                                                            | Blitter 2D-filter coefficients                                                                                                                                                                                                                                                                                 |

| Ch            | apter 49                                                                        | Main and auxiliary displays                                                                                                                                                                                                                                                                                    |

|               | 49.1                                                                            | Overview                                                                                                                                                                                                                                                                                                       |

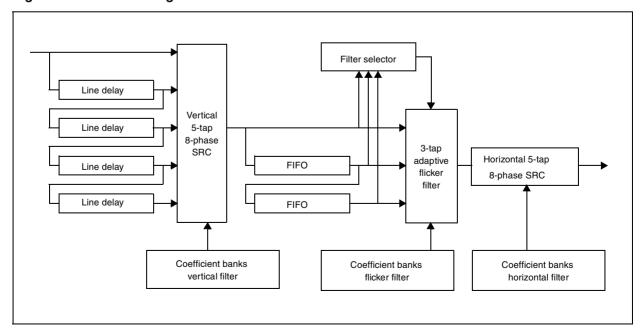

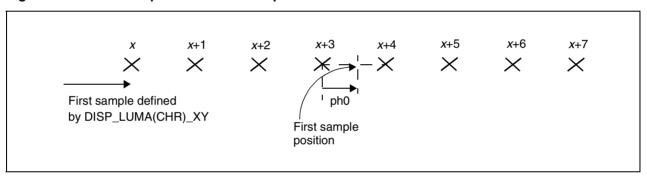

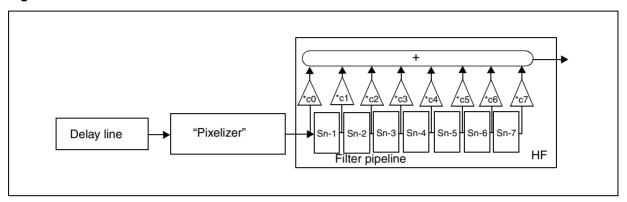

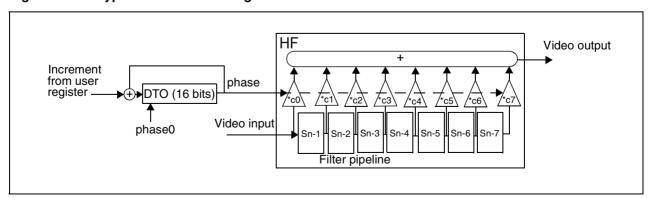

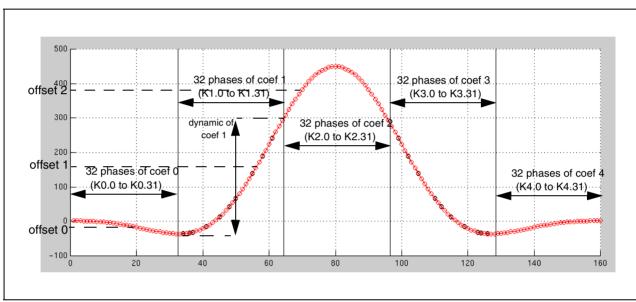

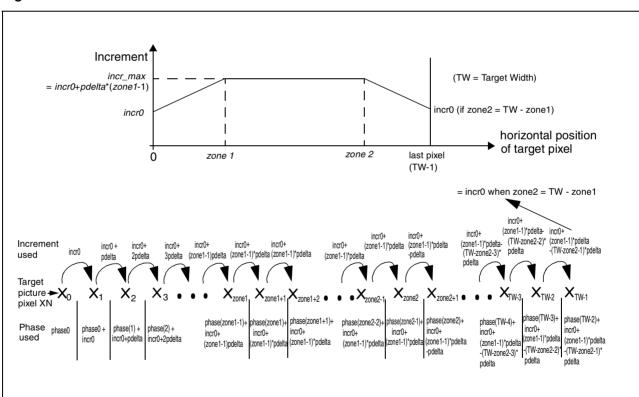

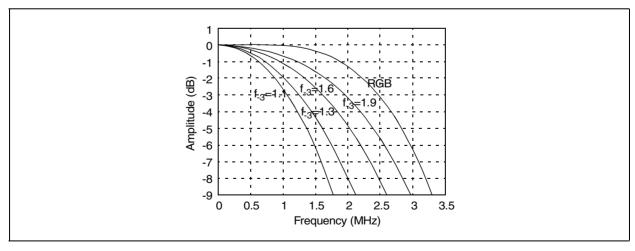

|               | 49.2                                                                            | Fully programmable horizontal sample rate converters                                                                                                                                                                                                                                                           |

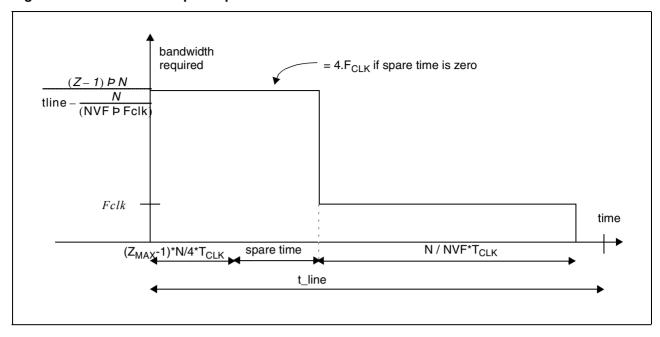

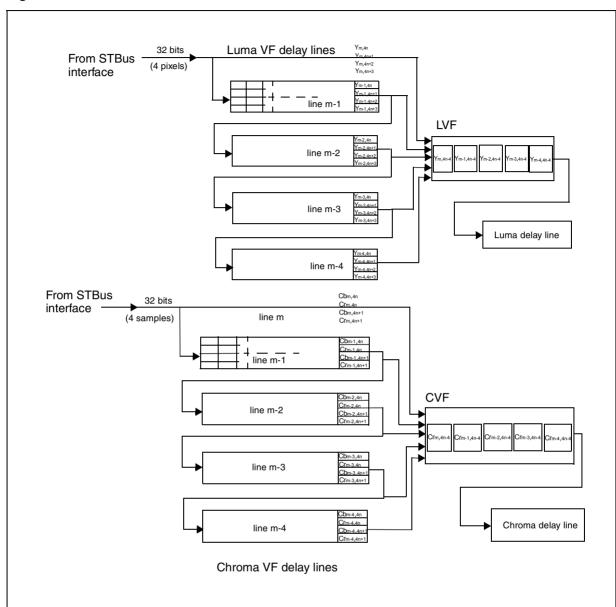

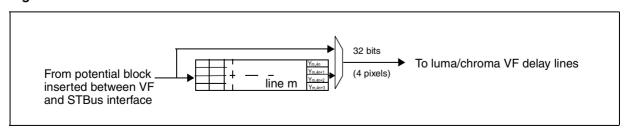

|               | 49.3                                                                            | Fully programmable vertical sample rate converters                                                                                                                                                                                                                                                             |

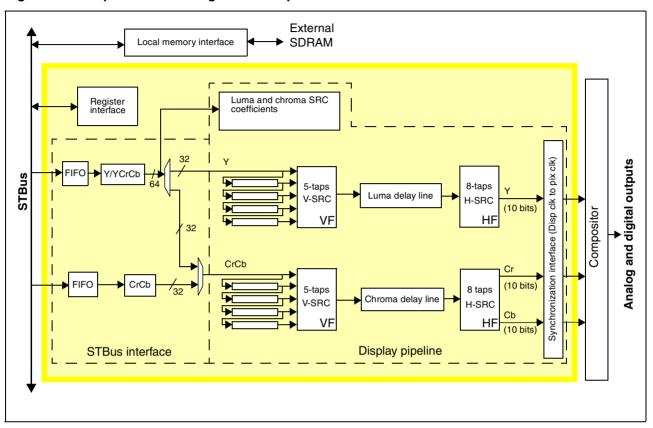

|               | 49.4                                                                            | Block diagram                                                                                                                                                                                                                                                                                                  |

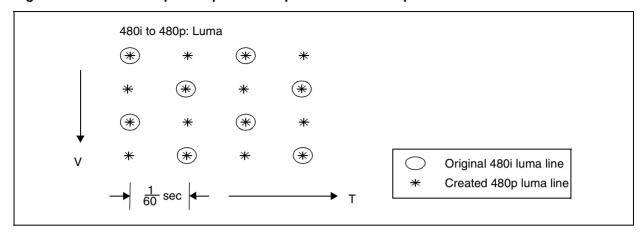

| <u>\alpha</u> | 49.5                                                                            | Linear motion upconverter (LMU)494                                                                                                                                                                                                                                                                             |

| nt            | 49.6                                                                            | Functional description                                                                                                                                                                                                                                                                                         |

| de            | 49.6<br>49.7<br><b>apter 50</b>                                                 | Soft reset                                                                                                                                                                                                                                                                                                     |

|               |                                                                                 |                                                                                                                                                                                                                                                                                                                |

| Ch            | apter 50                                                                        | Main and auxiliary display registers                                                                                                                                                                                                                                                                           |

| Ch            | <b>apter 50</b><br>50.1                                                         | Main and auxiliary display registers       506         Main and auxiliary display registers                                                                                                                                                                                                                    |

| Ch            |                                                                                 |                                                                                                                                                                                                                                                                                                                |

| Ö             | 50.1                                                                            | Main and auxiliary display registers508                                                                                                                                                                                                                                                                        |

| Ö             | 50.1<br>50.2                                                                    | Main and auxiliary display registers                                                                                                                                                                                                                                                                           |

| Ö             | 50.1<br>50.2<br><b>apter 51</b>                                                 | Main and auxiliary display registers                                                                                                                                                                                                                                                                           |

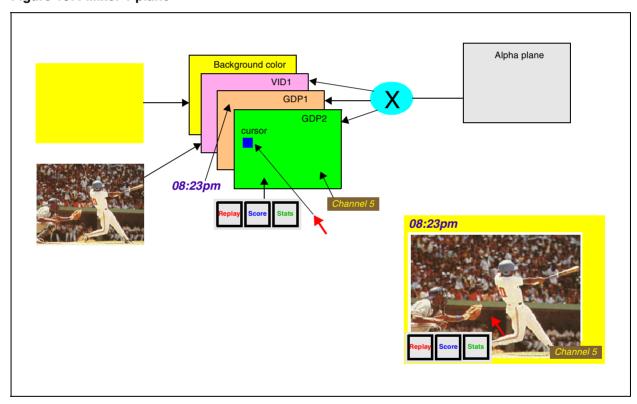

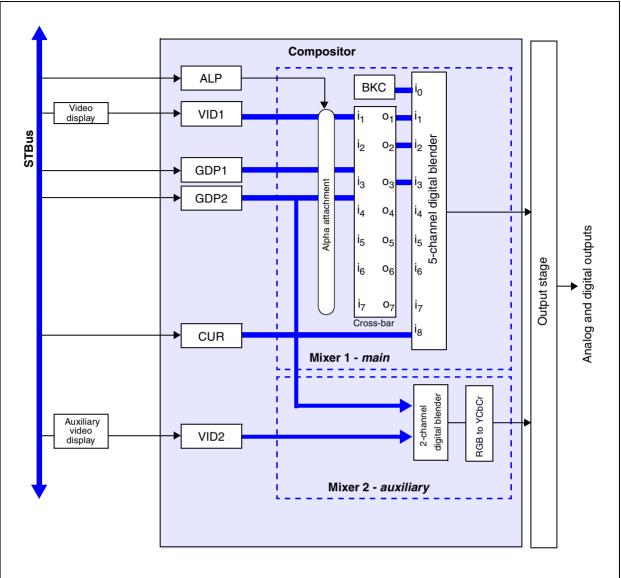

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1                                         | Main and auxiliary display registers.508LMU registers.527Compositor.533Overview.533                                                                                                                                                                                                                            |

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1<br>51.2                                 | Main and auxiliary display registers.508LMU registers.527Compositor533Overview.533Compositor layout.534                                                                                                                                                                                                        |

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1<br>51.2<br>51.3                         | Main and auxiliary display registers.508LMU registers.527Compositor533Overview.533Compositor layout.534Digital mixer 1 (MIX1) - main display output.536                                                                                                                                                        |

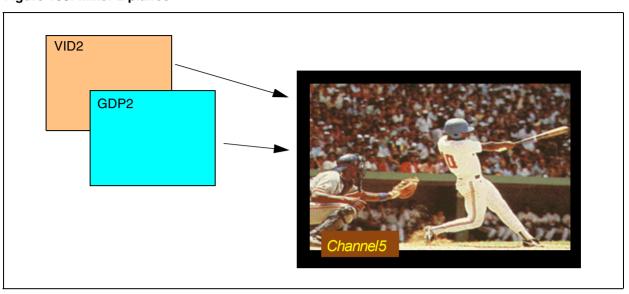

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1<br>51.2<br>51.3<br>51.4                 | Main and auxiliary display registers.508LMU registers.527Compositor.533Overview.533Compositor layout.534Digital mixer 1 (MIX1) - main display output.536Digital mixer 2 (MIX2) - auxiliary display output.537                                                                                                  |

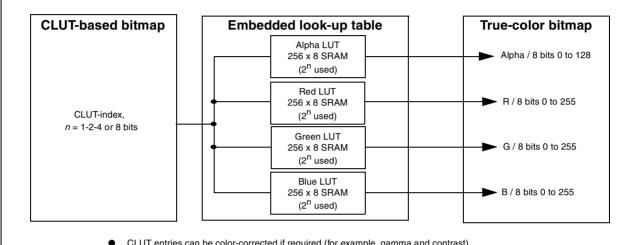

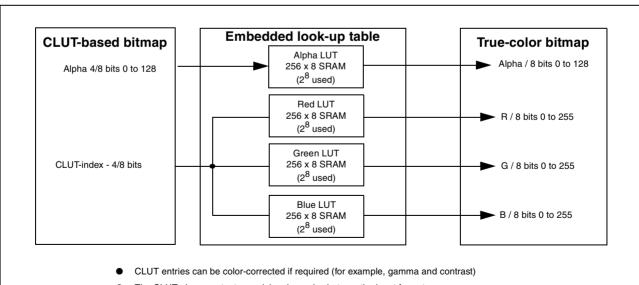

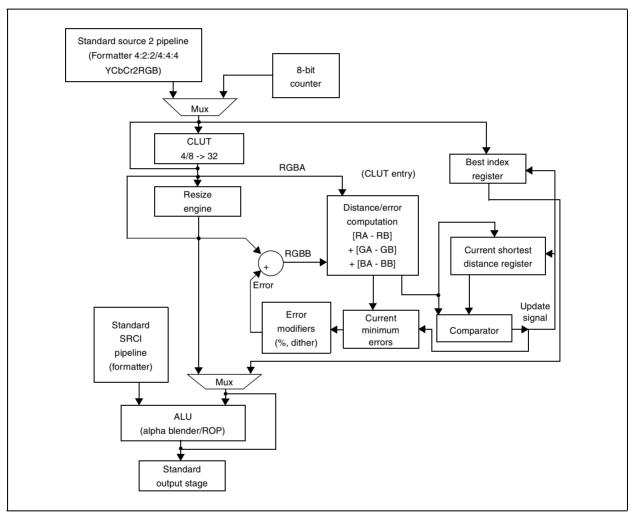

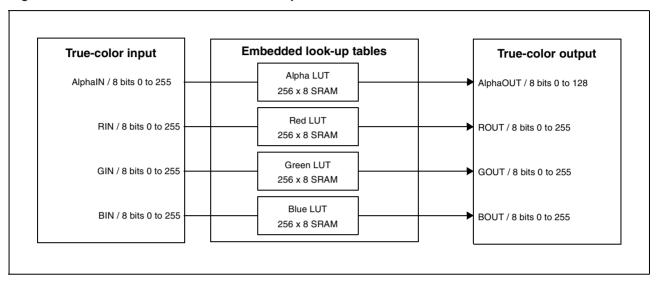

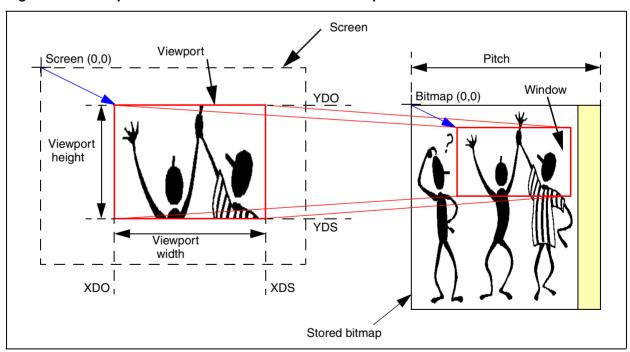

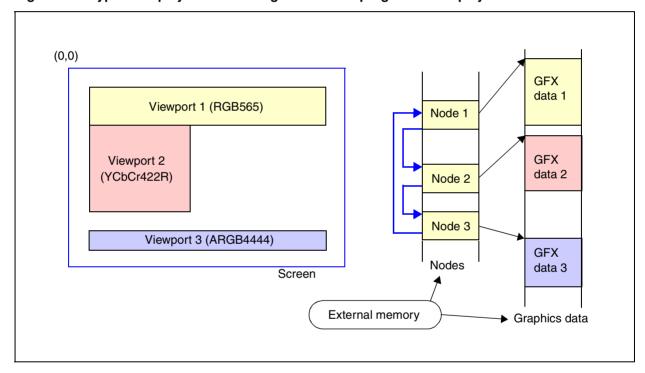

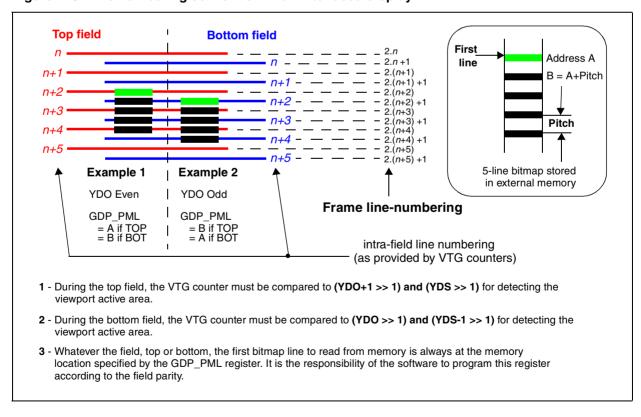

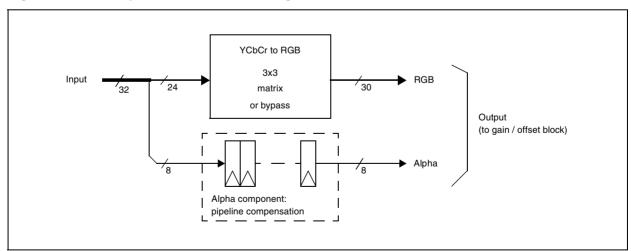

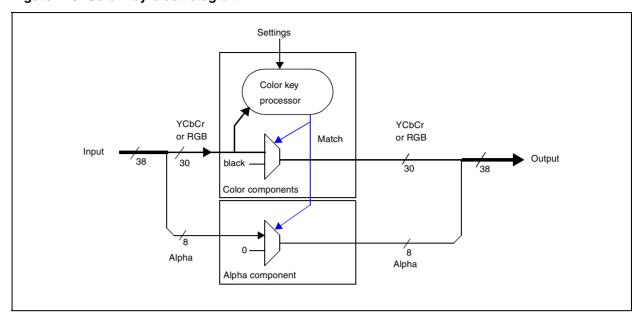

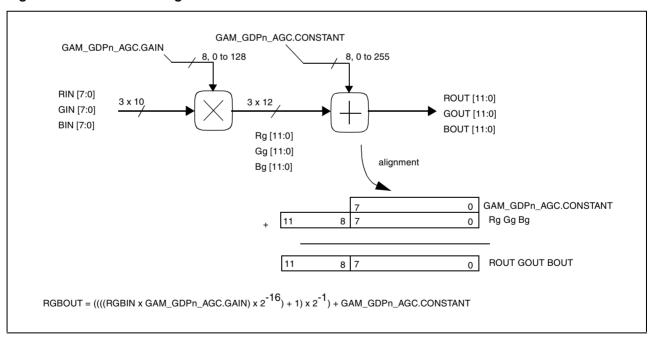

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1<br>51.2<br>51.3<br>51.4<br>51.5         | Main and auxiliary display registers.508LMU registers.527Compositor.533Overview.533Compositor layout.534Digital mixer 1 (MIX1) - main display output.536Digital mixer 2 (MIX2) - auxiliary display output.537Generic display pipelines (GDP1 and GDP2).538                                                     |

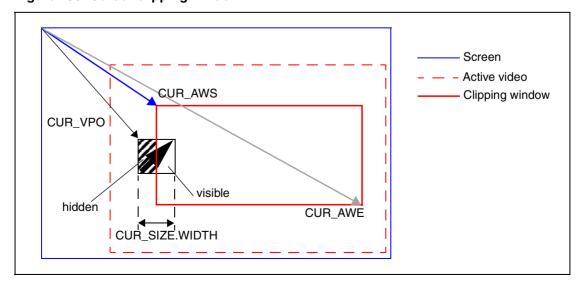

| Ö             | 50.1<br>50.2<br><b>apter 51</b><br>51.1<br>51.2<br>51.3<br>51.4<br>51.5<br>51.6 | Main and auxiliary display registers.508LMU registers.527Compositor533Overview.533Compositor layout.534Digital mixer 1 (MIX1) - main display output.536Digital mixer 2 (MIX2) - auxiliary display output.537Generic display pipelines (GDP1 and GDP2).538Cursor plane (CUR).546                                |

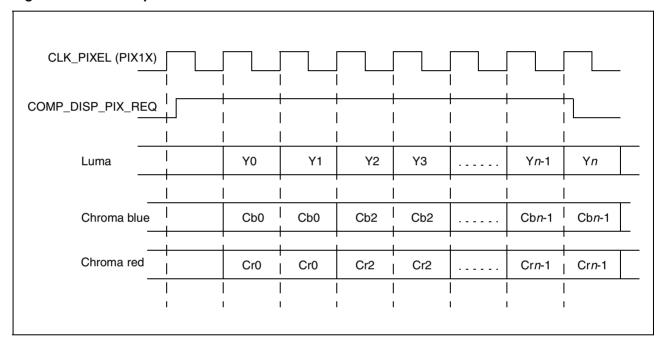

| Ch            | 50.1<br>50.2<br><b>apter 51</b> 51.1 51.2 51.3 51.4 51.5 51.6 51.7              | Main and auxiliary display registers.508LMU registers.527Compositor.533Overview.533Compositor layout.534Digital mixer 1 (MIX1) - main display output.536Digital mixer 2 (MIX2) - auxiliary display output.537Generic display pipelines (GDP1 and GDP2).538Cursor plane (CUR).546Video plug (VID).550           |

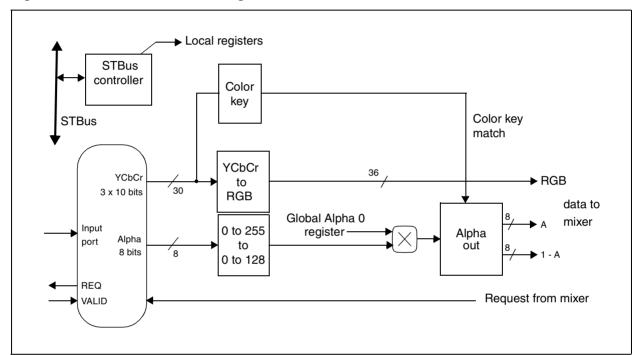

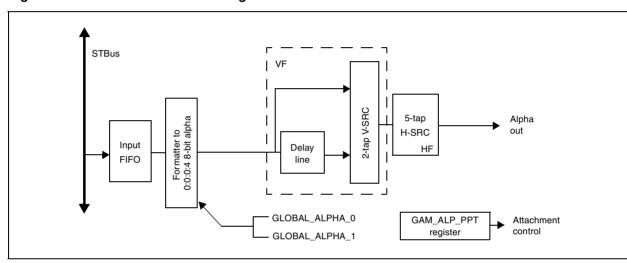

| Ch            | 50.1<br>50.2<br><b>apter 51</b> 51.1 51.2 51.3 51.4 51.5 51.6 51.7 51.8         | Main and auxiliary display registers508LMU registers527Compositor533Overview533Compositor layout534Digital mixer 1 (MIX1) - main display output536Digital mixer 2 (MIX2) - auxiliary display output537Generic display pipelines (GDP1 and GDP2)538Cursor plane (CUR)546Video plug (VID)550Alpha plane (ALP)552 |

|   | σ           | 3 |

|---|-------------|---|

| t |             | 5 |

|   | Ċ           |   |

|   | d           | 5 |

| • | C           | 5 |

| į | F           |   |

|   | $\subseteq$ | _ |

|   | C           |   |

| 1 | •           | ١ |

| 52.3       | Register descriptions559                    |

|------------|---------------------------------------------|

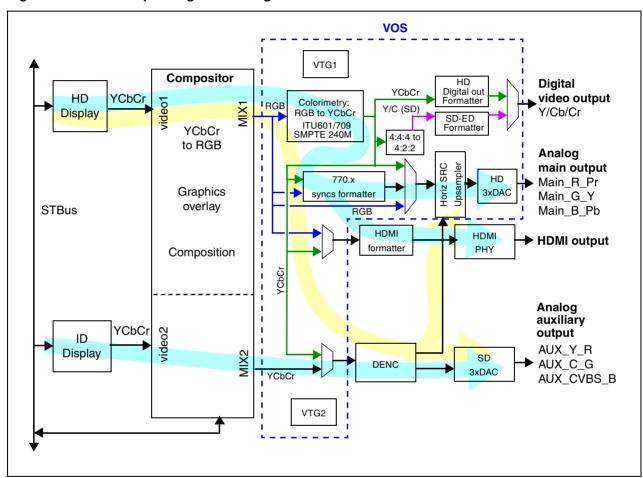

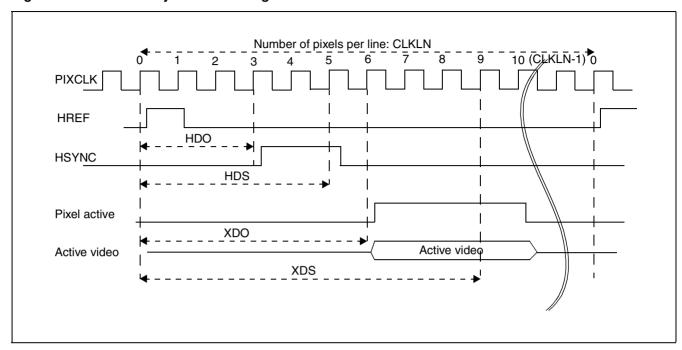

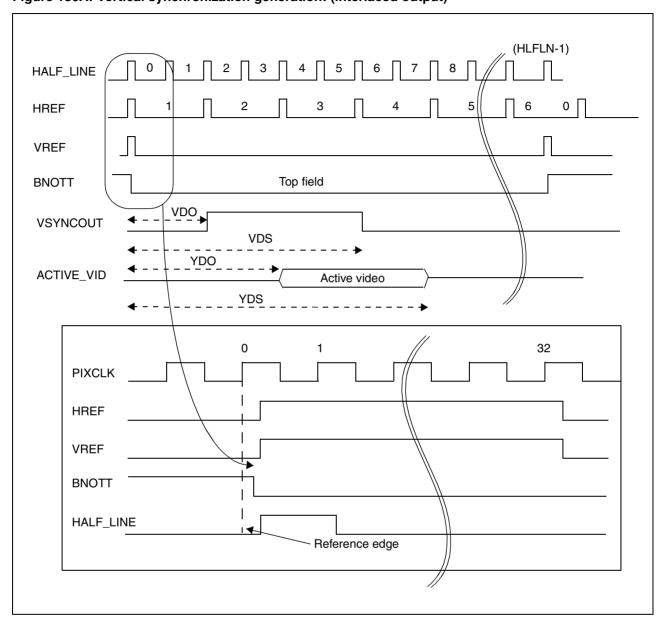

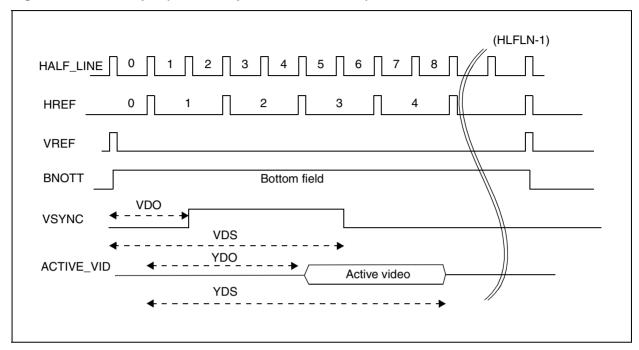

| Chapter 53 | Video output stage (VOS) 588                |

| 53.1       | Display and video output subsystem overview |

| 53.2       | HD DACs clocking                            |

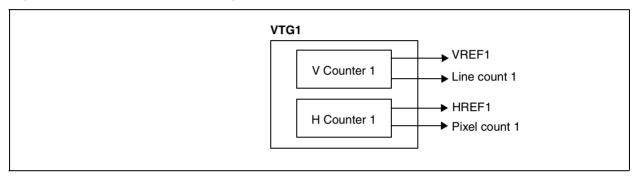

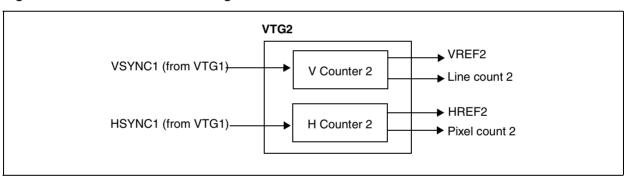

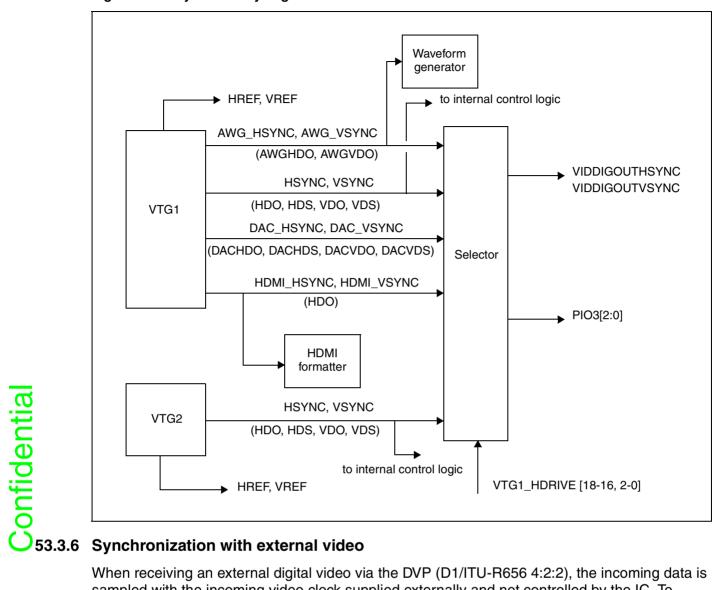

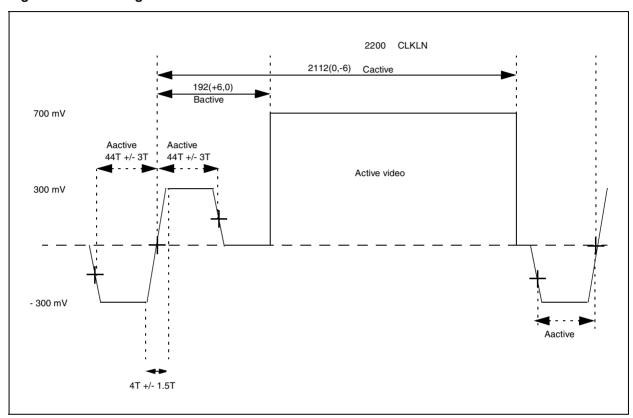

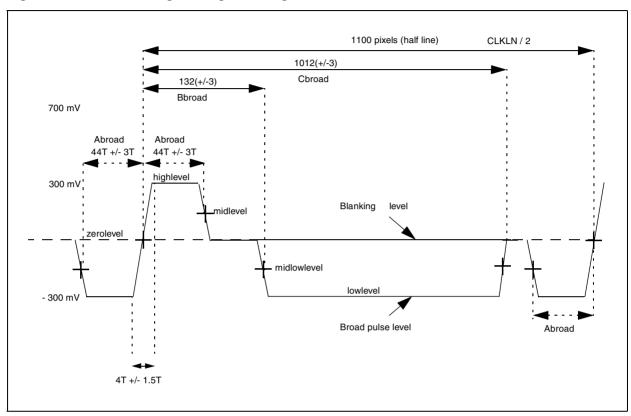

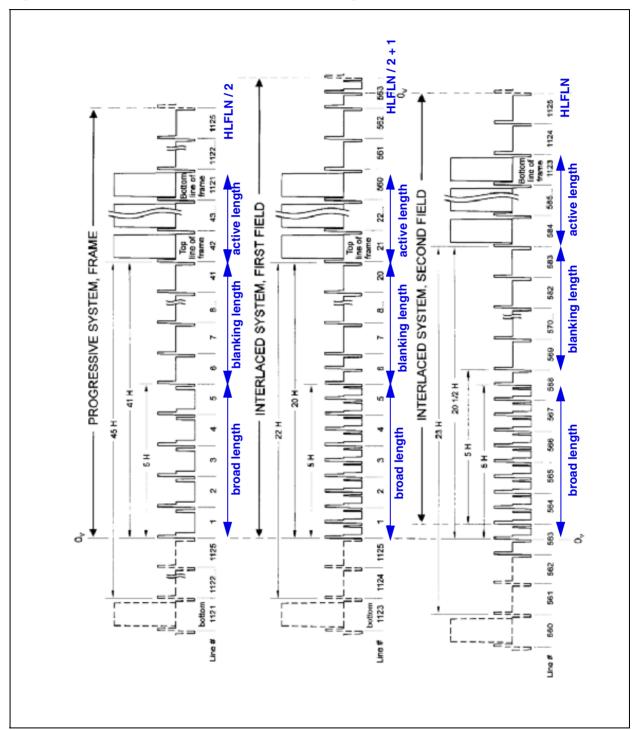

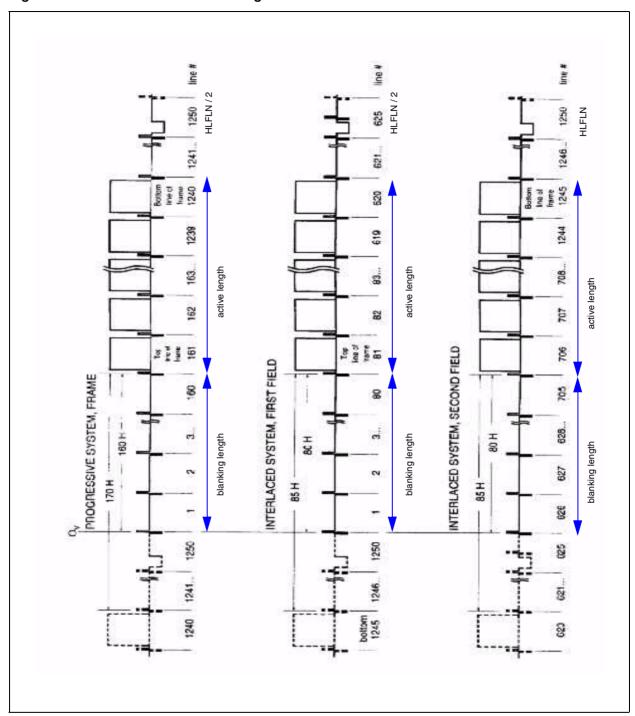

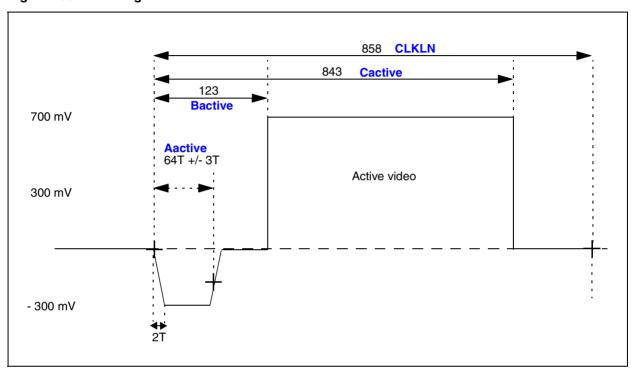

| 53.3       | Video timing generators (VTG)               |

| 53.4       | RGB to YCrCb color space conversion         |

| 53.5       | Digital video output formatter              |

| 53.6       | Analog video output                         |

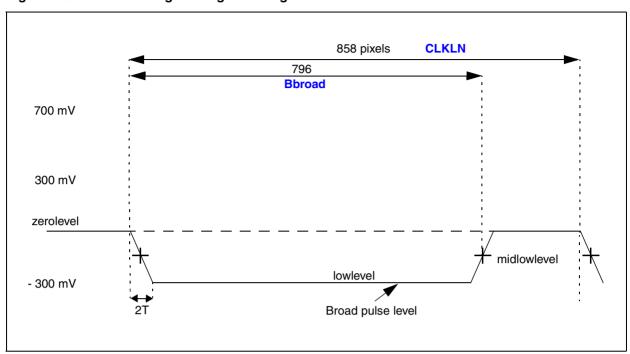

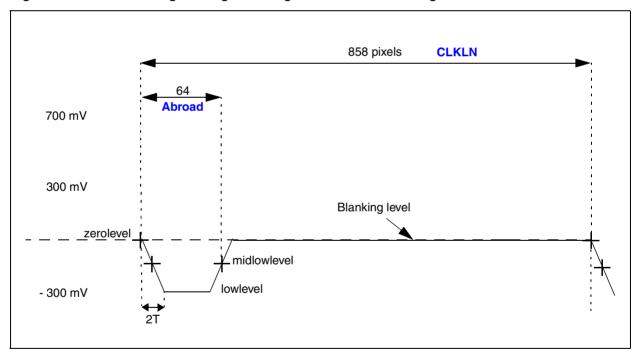

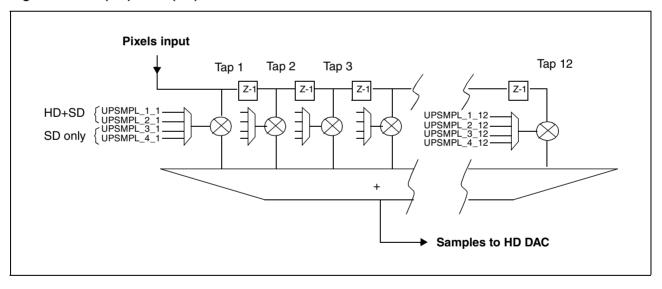

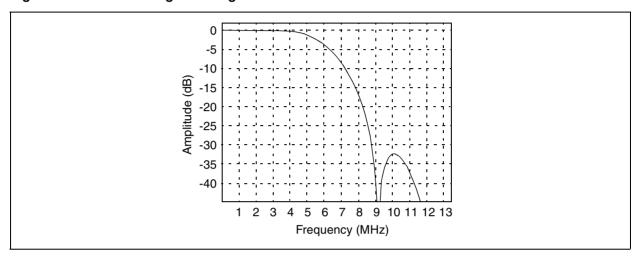

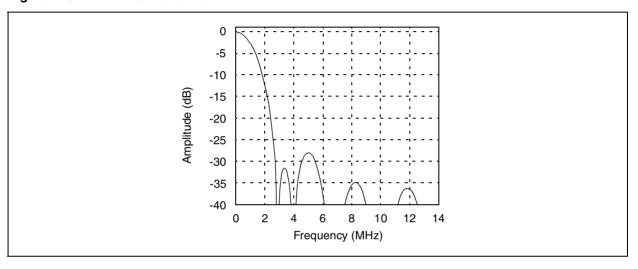

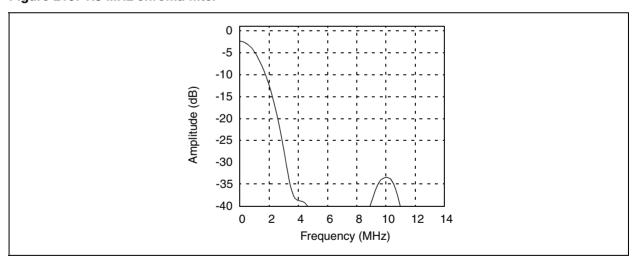

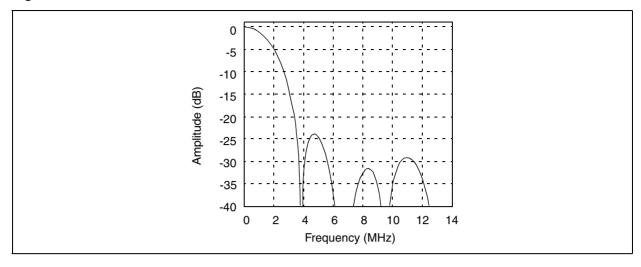

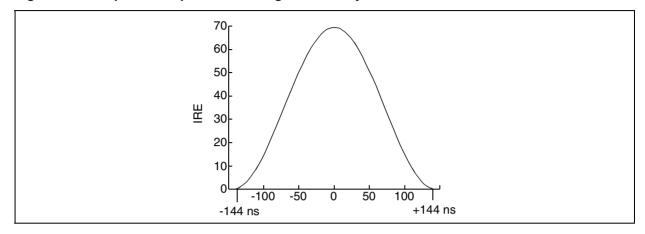

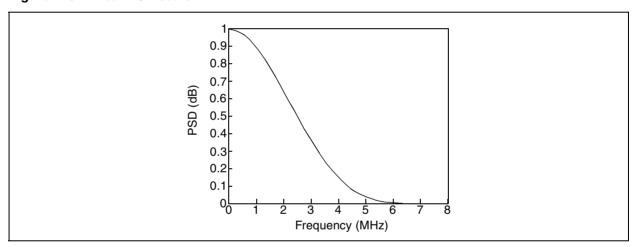

| 53.7       | Upsampler                                   |

| Chapter 54 | Video output stage (VOS) registers 607      |

| 54.1       | VTG 1610                                    |

| 54.2       | VTG 2619                                    |

| 54.3       | General VOS configuration                   |

| 54.4       | Main video output configuration628          |

| 54.5       | Digital SD video out                        |

| 54.6       | HD DAC configuration                        |

| 54.7       | Upsampler tap coefficients                  |

| 54.8       | Waveform generator configuration            |

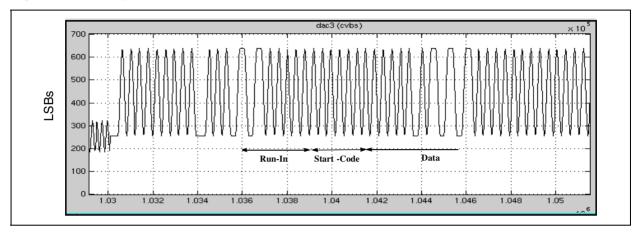

| Chapter 55 | Digital encoder (DENC) 644                  |

| 55.1       | Digital encoder overview                    |

| 55.2       | Data input format644                        |

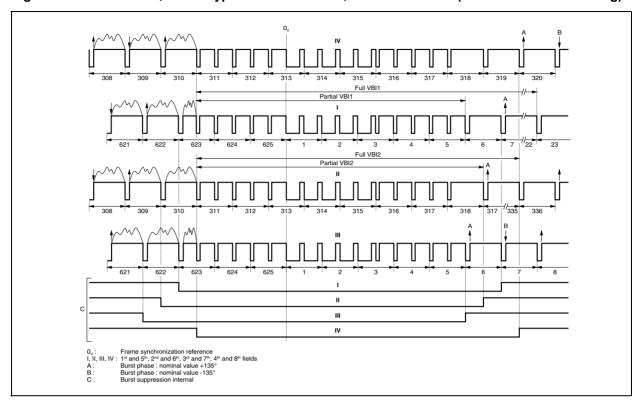

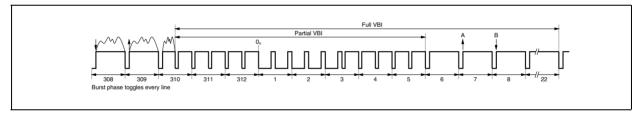

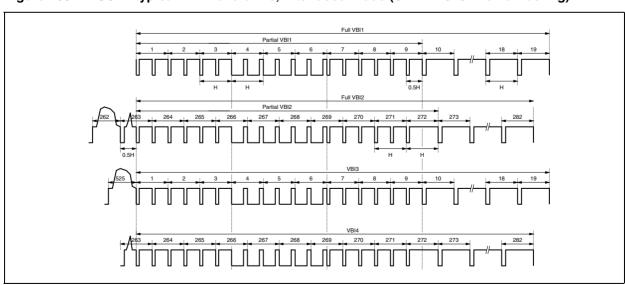

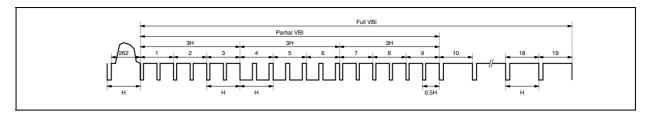

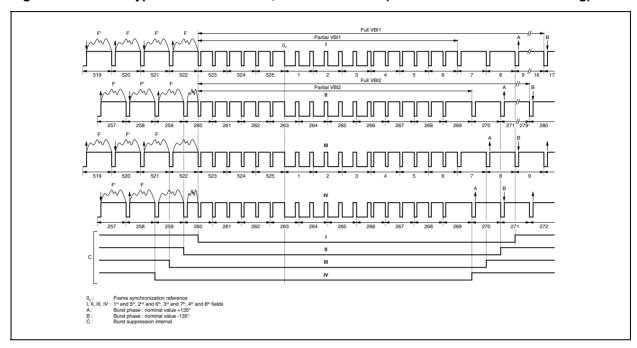

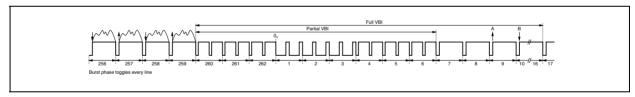

| 55.3       | Video timing                                |

| 55.4       | Reset procedure                             |

| 55.5       | Digital encoder synchronization             |

| 55.6       | Input demultiplexor                         |

| 55.7       | Subcarrier generation                       |

| 55.8       | Burst insertion (PAL and NTSC)              |

| 55.9       | Subcarrier insertion (SECAM)653             |

| 55.10      | Luminance encoding653                       |

| 55.11      | Chrominance encoding                        |

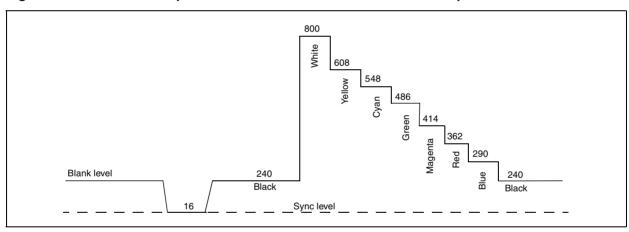

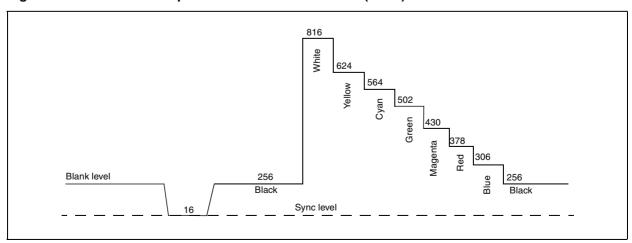

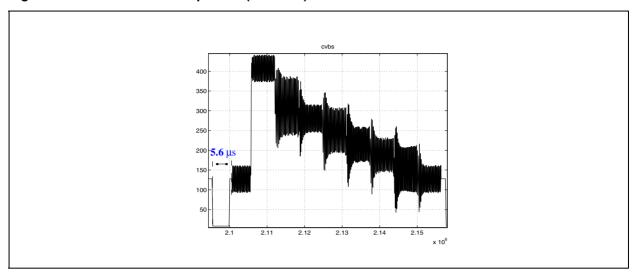

| 55.12      | Composite video signal generation657        |

| 55.13      | RGB and UV encoding                         |

|      | 55.14  | Closed captioning                           |

|------|--------|---------------------------------------------|

|      | 55.15  | CGMS encoding                               |

|      | 55.16  | WSS encoding                                |

|      | 55.17  | VPS encoding                                |

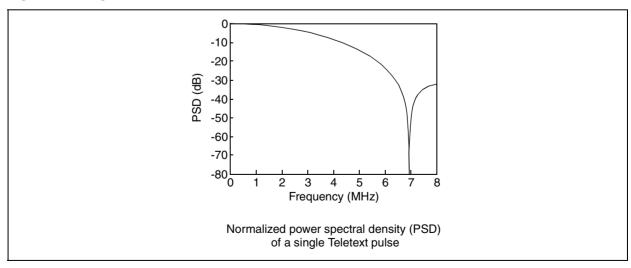

|      | 55.18  | Teletext encoding                           |

|      | 55.19  | CVBS, S-VHS, RGB and UV outputs             |

| Chap | ter 56 | Digital encoder (DENC) registers            |

|      | 56.1   | Configuration and status                    |

|      | 56.2   | Digital frequency synthesizer               |

|      | 56.3   | WSS                                         |

|      | 56.4   | DAC inputs                                  |

|      | 56.5   | Hardware ID                                 |

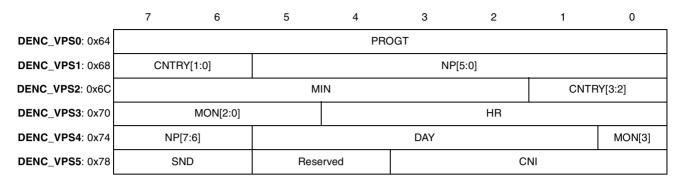

|      | 56.6   | VPS data                                    |

|      | 56.7   | CGMS data                                   |

|      | 56.8   | Teletext                                    |

|      | 56.9   | Closed caption                              |

|      | 56.10  | Input demultiplexor                         |

|      | 56.11  | Chroma coefficient                          |

|      | 56.12  | Luma coefficient                            |

|      | 56.13  | Hue control                                 |