## STi7197 Advanced STB decoder with integrated QAM demodulator

## Features

- ITU-T J83 Annex B compliant

- 256 QAM (quadrature amplitude modulation) demodulation and FEC (forward error correction) sub-system

- Advanced high-definition video decoding (H.264/VC-1/MPEG2)

- Advanced standard-definition video decoding (H.264/VC-1/MPEG2/AVS)

- Advanced multi-channel audio decoding (MPEG 1, 2, MP3, DD/DD+, AAC/AAC+, WMA9/WMA9Pro)

- DVD data decryption

- Multi-stream, DVR capable transport stream processing

- Linux, Windows CE and OS21 compatible ST40 applications CPU (450 MHz)

- 32-bit DDR1/DDR2 compatible local memory interface

- Extensive connectivity (dual USB 2.0 host ports, e-SATA, Ethernet MAC/MII/RMII, and PCI)

- Advanced security and DRM support including SVP, MS-DRM, and DTCP-IP

# Description

The STI7197 is an advanced STB decoder with an integrated QAM demodulator, suitable for cable networks conforming to the ITU-T J83-Annex B standard (for example, US cable).

The STi7197 integrates multi-stream transport demultiplexing, audio video decode, video processing, graphics and display handling, STB peripherals, audio video DACs, digital audio video outputs, PCI, e-SATA, dual USB ports, an Ethernet GMAC controller and ST40 applications CPU.

Doc ID 8265038 Rev 2

# Contents

| 1 | Relat | ted documents                        |

|---|-------|--------------------------------------|

|   | 1.1   | STi7197 programming manual           |

|   | 1.2   | CPU documentation 8                  |

| 2 | Func  | tional overview                      |

|   | 2.1   | Front end                            |

|   | 2.2   | QAM demodulator/FEC 10               |

|   | 2.3   | IF to MPEG2 TS block conversion      |

|   | 2.4   | Transport                            |

|   | 2.5   | Connectivity                         |

|   | 2.6   | Audio/video decoding 12              |

|   | 2.7   | Graphics and display 12              |

|   | 2.8   | Audio/video outputs                  |

|   | 2.9   | Processors                           |

|   | 2.10  | System interfaces                    |

|   | 2.11  | DVR 13                               |

|   | 2.12  | STB peripherals                      |

|   | 2.13  | HDMI interface                       |

|   | 2.14  | Target applications                  |

| 3 | Syste | em on chip subsystem overview16      |

|   | 3.1   | ITU-T J83 Annex B demodulator/FEC 16 |

|   | 3.2   | STBus interconnect 16                |

|   | 3.3   | Processor core                       |

|   | 3.4   | External memory interface (EMI) 17   |

|   | 3.5   | Local memory interface (LMI)         |

|   | 3.6   | STB transport subsystem 17           |

|   | 3.7   | DVD decryption                       |

|   | 3.8   | Video decoder                        |

|   | 3.9   | Main and auxiliary display 21        |

|   | 3.10  | Compositor                           |

|   |       |                                      |

| 3.11 Video output                       | 25  |

|-----------------------------------------|-----|

| 3.12 2D blitter display engine          | 27  |

| 3.13 Audio subsystem                    | 28  |

| 3.14 FDMA controllers                   | 31  |

| 3.15 Interfaces                         | 31  |

| 3.16 Clock generation                   | 32  |

| 3.17 System services                    | 32  |

| 4 Package mechanical data               | 33  |

| 4.1 27 × 27 package                     | 33  |

| 4.2 Environmentally friendly packages   |     |

| 5 Ordering information                  | 37  |

| 6 Front-end registers                   | 38  |

| 6.1 Register map                        | 38  |

| 6.2 Register descriptions               | 45  |

| 6.3 Configuration and control registers | 91  |

| 6.4 FEC-B registers                     | 98  |

| 6.5 TSMF registers                      | 107 |

| 7 BGA footprint                         | 127 |

| 7.1 Ball grid array                     |     |

|                                         | 121 |

| 8 Connections                           | 132 |

| 8.1 Ball list sorted by ball number     | 132 |

| 8.2 Power supplies                      | 153 |

| 8.3 System                              | 164 |

| 8.4 JTAG                                | 164 |

| 8.5 Transport interface                 | 165 |

| 8.6 Display analog output interface     | 167 |

| 8.7 HDMI interface                      | 168 |

| 8.8 Audio digital interface             | 168 |

| 8.9 Audio analog interface              | 169 |

| 8.10 Serial ATA interface               | 169 |

|                                         |     |

|    | 8.11  | FDMA interface                                                         |

|----|-------|------------------------------------------------------------------------|

|    | 8.12  | Programmable inputs/outputs (PIOs) 170                                 |

|    | 8.13  | External memory interface (EMI) 175                                    |

|    | 8.14  | Local memory interface 177                                             |

|    | 8.15  | Front end                                                              |

|    | 8.16  | Front-end transport stream output 182                                  |

|    | 8.17  | Ethernet                                                               |

|    | 8.18  | USB 2.0 interface                                                      |

|    | 8.19  | Peripherals                                                            |

|    | 8.20  | Pad reset conditions                                                   |

| -  |       |                                                                        |

| 9  |       | c chip operating modes and multiplexing scenarios                      |

|    | 9.1   | Transport interfaces multiplexing                                      |

|    | 9.2   | Ethernet interface multiplexing in standard mode                       |

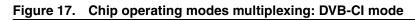

|    | 9.3   | DVB common interface (DVB-CI) transport mode                           |

|    | 9.4   | External memory interface (EMI) operating modes                        |

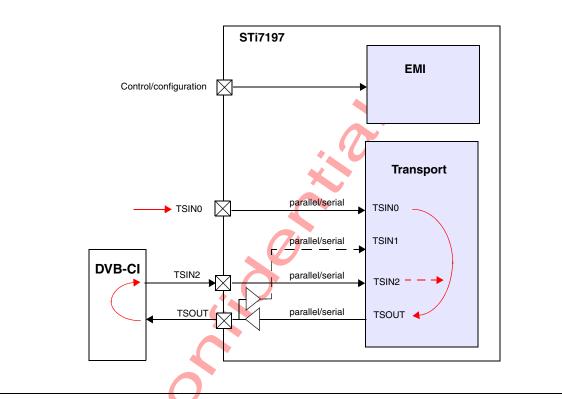

| 10 | Mem   | ory map                                                                |

|    | 10.1  | Global Mapping                                                         |

|    |       |                                                                        |

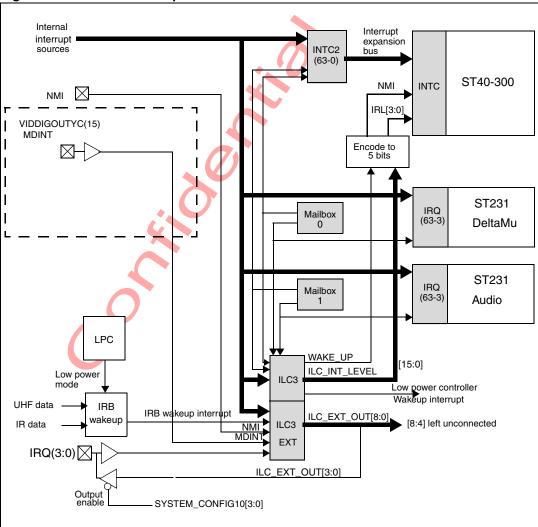

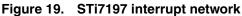

| 11 | Inter | rupt networks                                                          |

|    | 11.1  | Interrupt network organization                                         |

| 10 | FDM   |                                                                        |

| 12 | FDM   |                                                                        |

|    | 12.1  | Overview                                                               |

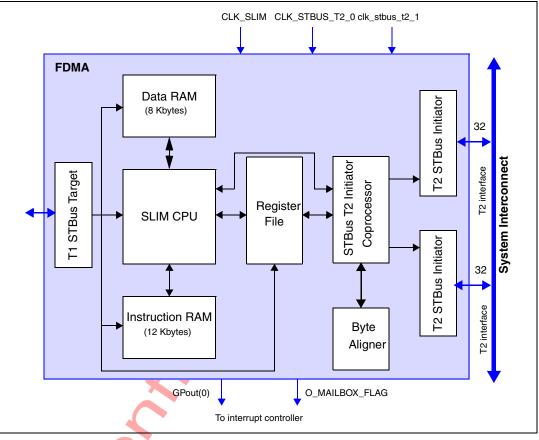

|    | 12.2  | Block diagram                                                          |

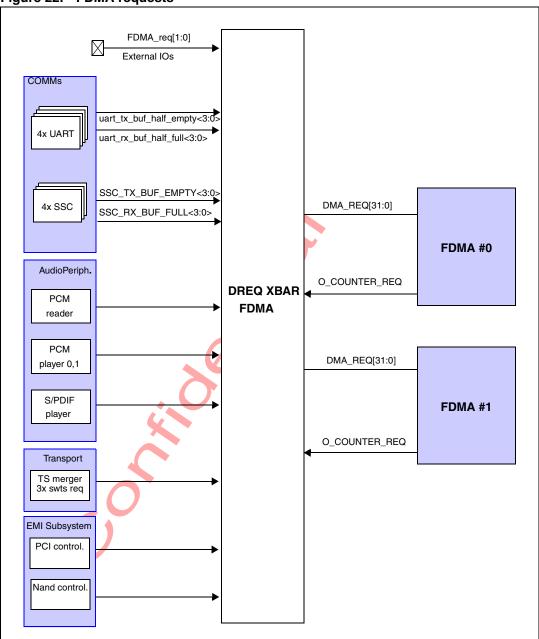

|    | 12.3  | DMA requests                                                           |

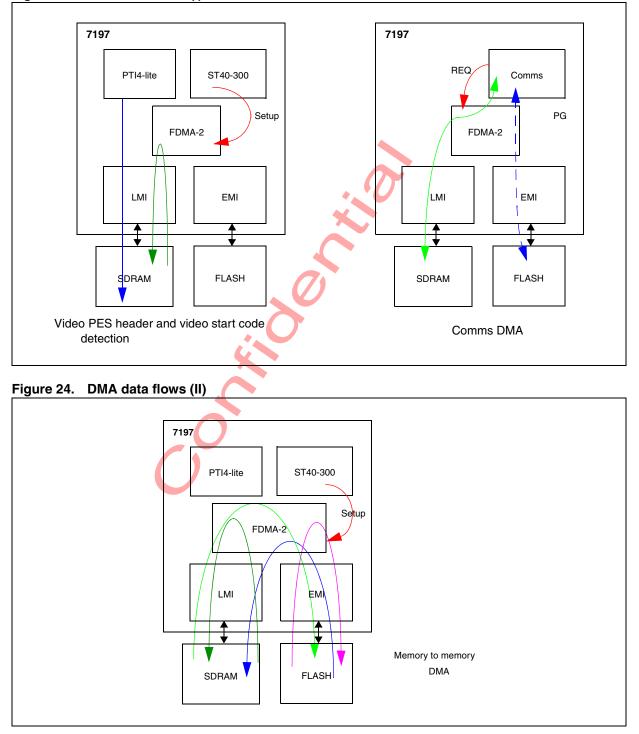

|    | 12.4  | Examples of DMA Data flow 241                                          |

| 13 | Cloc  | king                                                                   |

|    | 13.1  | Clock input/output pins 242                                            |

|    | 13.2  | Clock domains                                                          |

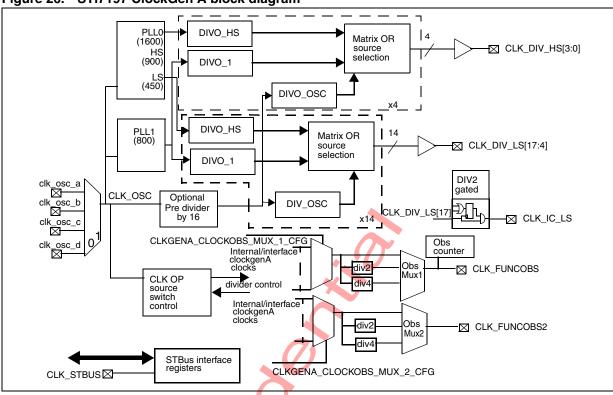

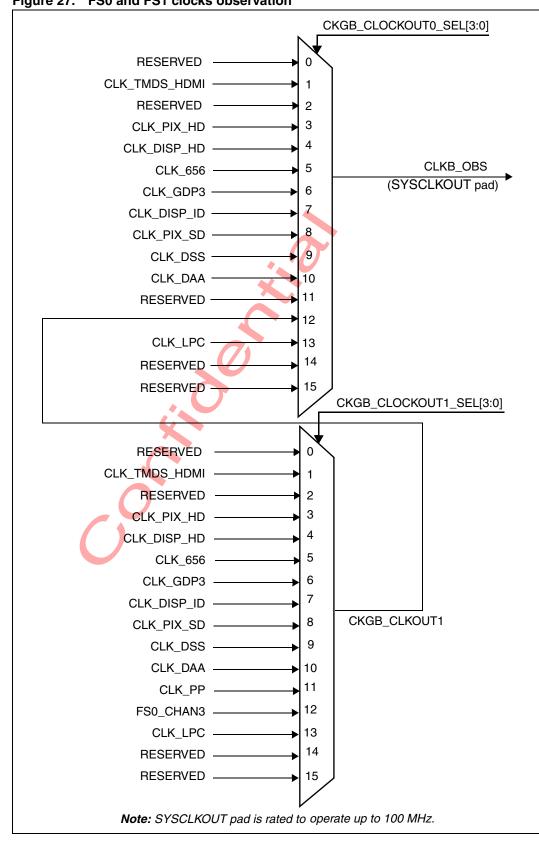

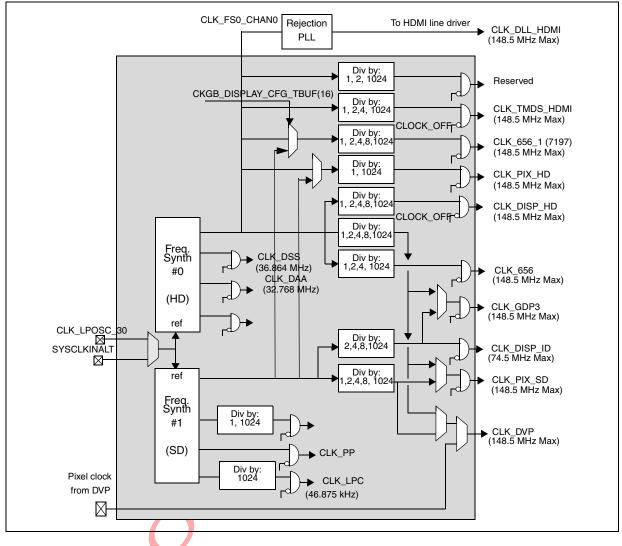

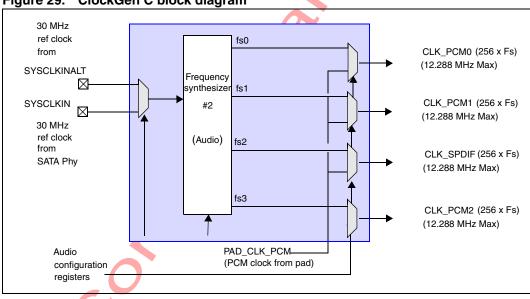

|    | 13.3  | CPUs and interconnect clock generation (ClockGen A) 249                |

|    | 13.4  | Video decoder, display, and Comms clock generation<br>(ClockGen B) 251 |

|    |       |                                                                        |

4/410

|          | 13.5                                                                                                                    | Audio clock generation (ClockGen C) 257                                                                                                                                                                                                                                                                |

|----------|-------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 13.6                                                                                                                    | LMI memory clocks (ClockGen D) 258                                                                                                                                                                                                                                                                     |

|          | 13.7                                                                                                                    | MPEG clock recovery                                                                                                                                                                                                                                                                                    |

| 14       | Powe                                                                                                                    | r-on-reset and system reset                                                                                                                                                                                                                                                                            |

|          | 14.1                                                                                                                    | Reset sources                                                                                                                                                                                                                                                                                          |

|          | 14.2                                                                                                                    | POR reset (cold reset) vs. system reset (warm reset) 26                                                                                                                                                                                                                                                |

|          | 14.3                                                                                                                    | Reset test mode                                                                                                                                                                                                                                                                                        |

| 15       | Mode                                                                                                                    | e pins                                                                                                                                                                                                                                                                                                 |

| 16       | Low                                                                                                                     | power control                                                                                                                                                                                                                                                                                          |

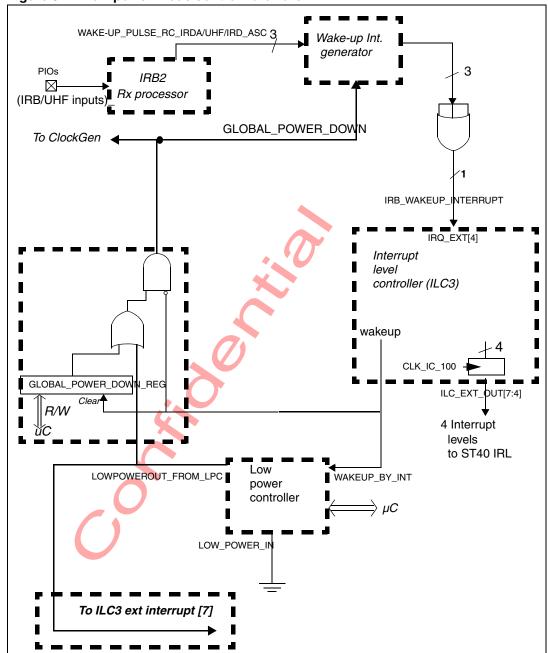

|          | 16.1                                                                                                                    | Entering low power modes 265                                                                                                                                                                                                                                                                           |

|          | 16.2                                                                                                                    | Exiting low power modes                                                                                                                                                                                                                                                                                |

|          | 16.3                                                                                                                    | DDR self-refresh                                                                                                                                                                                                                                                                                       |

|          | 16.4                                                                                                                    | EMI and PCI clocks stopping 269                                                                                                                                                                                                                                                                        |

|          | 16.5                                                                                                                    | ST40 sleep and standby modes overview                                                                                                                                                                                                                                                                  |

|          |                                                                                                                         |                                                                                                                                                                                                                                                                                                        |

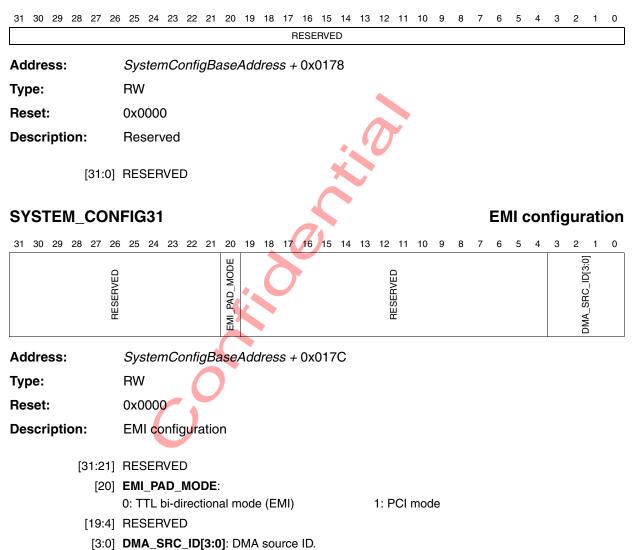

| 17       | Syste                                                                                                                   | em config module                                                                                                                                                                                                                                                                                       |

| 17       | <b>Syste</b><br>17.1                                                                                                    | em config module                                                                                                                                                                                                                                                                                       |

|          | 17.1                                                                                                                    | Brief overview                                                                                                                                                                                                                                                                                         |

| 17<br>18 | 17.1<br>Exter                                                                                                           | Brief overview                                                                                                                                                                                                                                                                                         |

|          | 17.1<br><b>Exter</b><br>18.1                                                                                            | Brief overview    271      mal circuitry recommendations    333      Power supplies    333                                                                                                                                                                                                             |

|          | 17.1<br>Exter<br>18.1<br>18.2                                                                                           | Brief overview    271      nal circuitry recommendations    333      Power supplies    333      System    333                                                                                                                                                                                          |

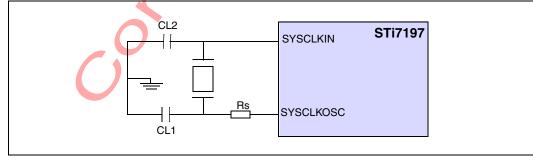

|          | 17.1<br>Exter<br>18.1<br>18.2<br>18.3                                                                                   | Brief overview    271      nal circuitry recommendations    333      Power supplies    333      System    333      JTAG    334                                                                                                                                                                         |

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4                                                                    | Brief overview    271      nal circuitry recommendations    333      Power supplies    333      System    333      JTAG    334      Display analog output interface    334                                                                                                                             |

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5                                                            | Brief overview       271         nal circuitry recommendations       333         Power supplies       333         System       333         JTAG       334         Display analog output interface       334         HDMI interface       335                                                           |

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6                                                    | Brief overview       271         nal circuitry recommendations       333         Power supplies       333         System       333         JTAG       334         Display analog output interface       334         HDMI interface       335         Audio digital interface       335                 |

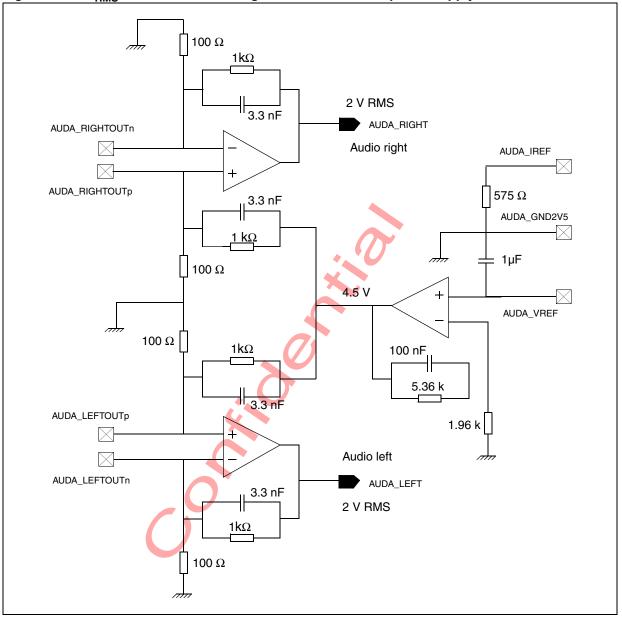

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7                                            | Brief overview271nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335                                                                                                               |

|          | 17.1<br>Exter<br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7<br>18.8                                           | Brief overview271nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335Programmable inputs/outputs337                                                                                 |

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7<br>18.8<br>18.9                            | Brief overview27nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335Programmable inputs/outputs337External memory interface (EMI)337                                                |

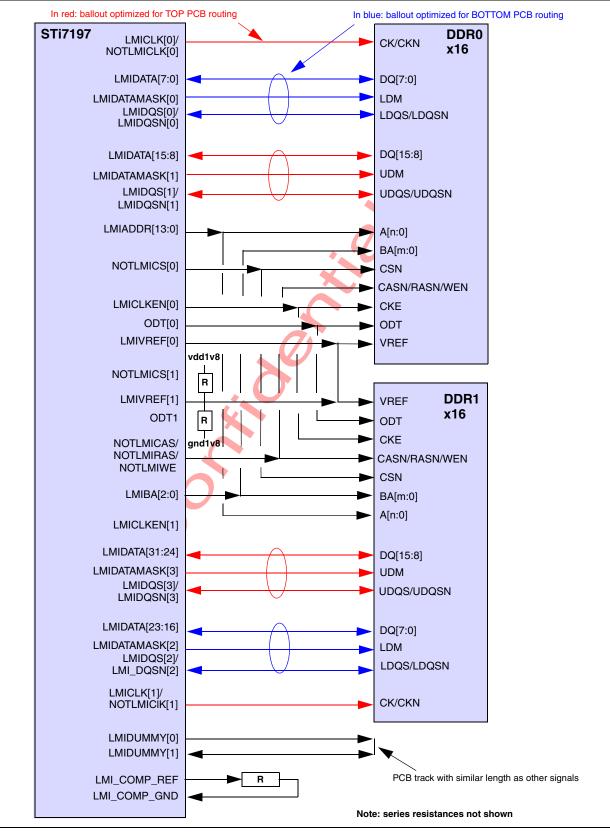

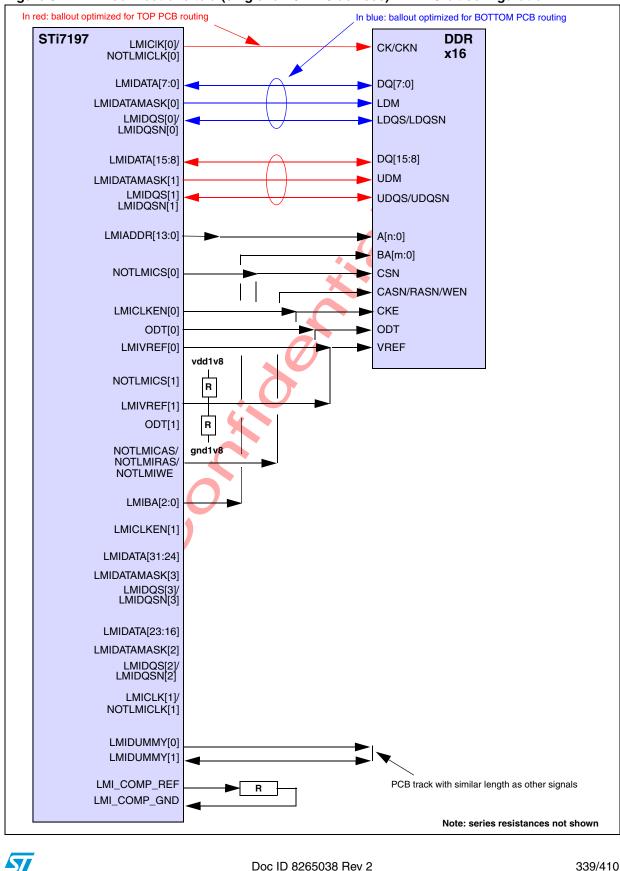

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7<br>18.8<br>18.9<br>18.10                   | Brief overview271nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335Programmable inputs/outputs337External memory interface (EMI)337Local memory interface337                      |

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7<br>18.8<br>18.9<br>18.10<br>18.11          | Brief overview271nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335Programmable inputs/outputs337External memory interface (EMI)337Local memory interface340Ethernet interface340 |

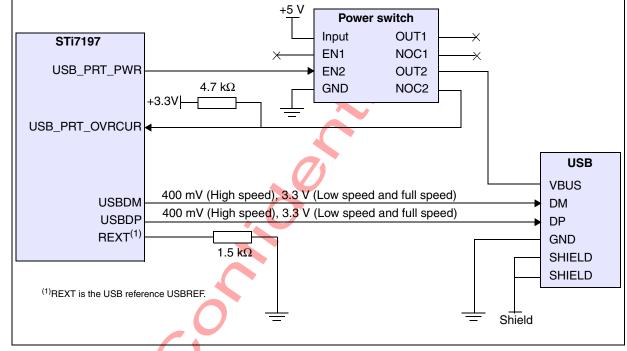

|          | 17.1<br><b>Exter</b><br>18.1<br>18.2<br>18.3<br>18.4<br>18.5<br>18.6<br>18.7<br>18.8<br>18.9<br>18.10<br>18.11<br>18.12 | Brief overview271nal circuitry recommendations333Power supplies333System333JTAG334Display analog output interface334HDMI interface335Audio digital interface335Audio analog interface335Programmable inputs/outputs337External memory interface (EMI)337Local memory interface337                      |

577

|    | 18.14  | Peripherals                              | I |

|----|--------|------------------------------------------|---|

| 19 | Electr | rical specifications                     | 2 |

|    | 19.1   | Absolute maximum ratings 342             | 2 |

|    | 19.2   | Operating conditions                     | 2 |

|    | 19.3   | Audio DAC                                | 3 |

|    | 19.4   | Triple HD video DACs                     | 1 |

|    | 19.5   | DAA electrical characteristics           | 3 |

|    | 19.6   | DDR electrical characteristics 346       | 3 |

|    | 19.7   | SATA PHY electrical characteristics      | 3 |

|    | 19.8   | External memory interface (EMI)          |   |

|    | 19.9   | USB 350                                  | ) |

|    | 19.10  | 3V3 IO pads 350                          | ) |

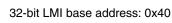

|    | 19.11  | Crystal oscillator specifications 351    | I |

| 20 | Timin  | g interfaces                             | 2 |

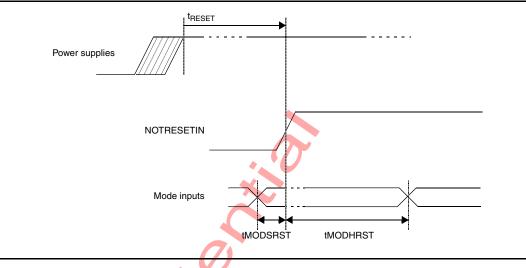

| 20 |        | System timing interface                  |   |

|    | 20.1   |                                          |   |

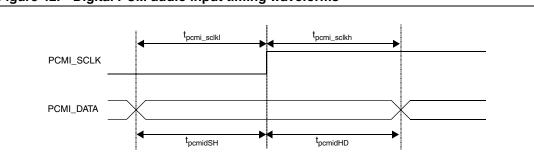

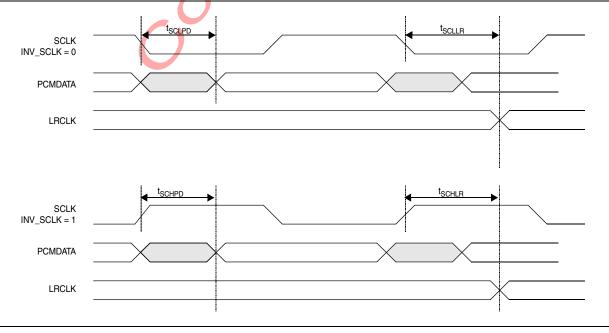

|    | 20.2   | Digital audio interface                  |   |

|    | 20.3   | Digital PCM player output interface      |   |

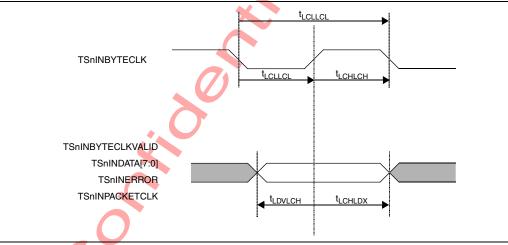

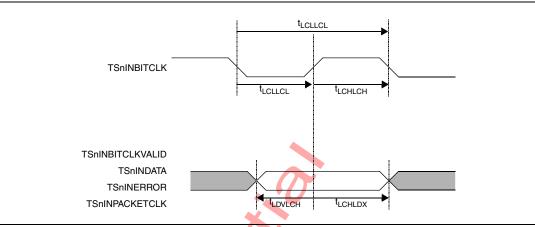

|    | 20.4   | Transport stream input AC specification  |   |

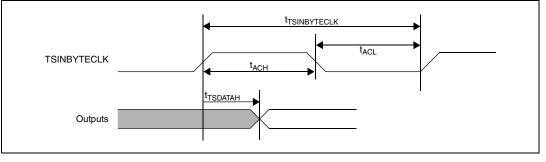

|    | 20.5   | Transport stream output AC specification |   |

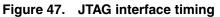

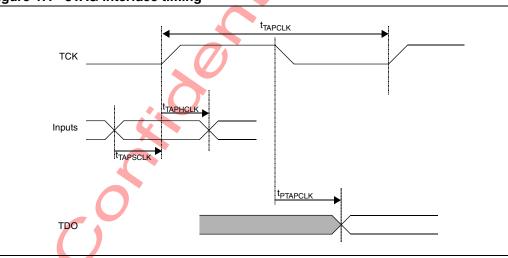

|    | 20.6   | JTAG interfaces AC specification         |   |

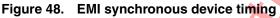

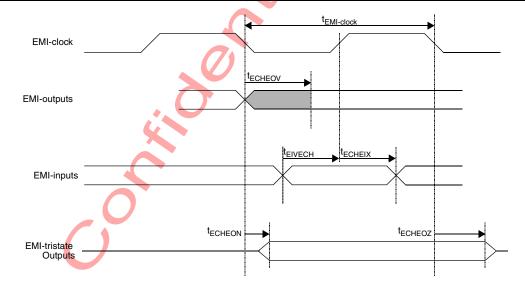

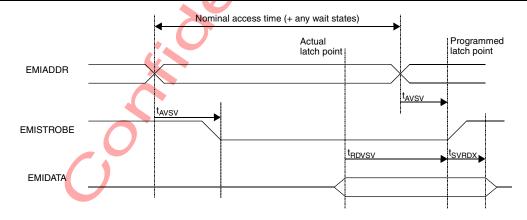

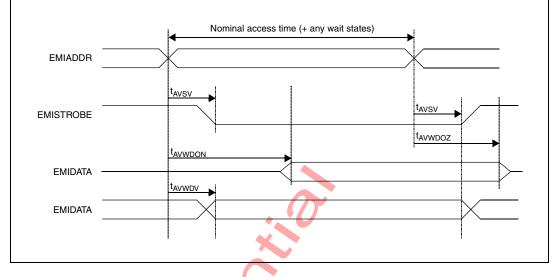

|    | 20.7   | EMI timings                              |   |

|    | 20.8   | LMI DDR2-SDRAM timings                   |   |

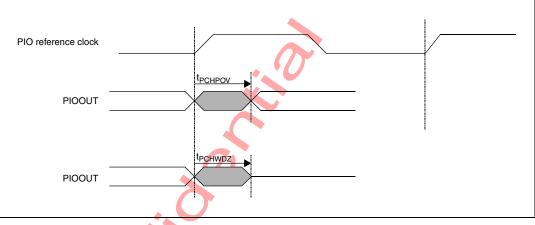

|    | 20.9   | PIO output AC specification              |   |

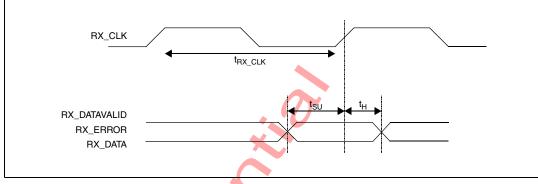

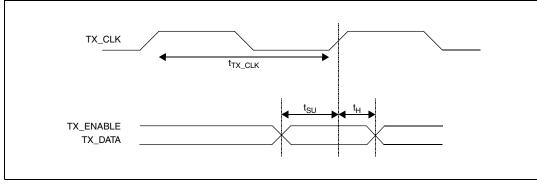

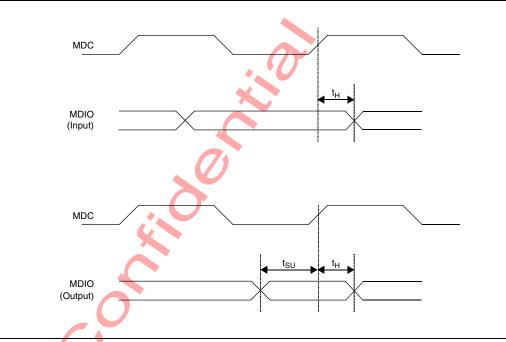

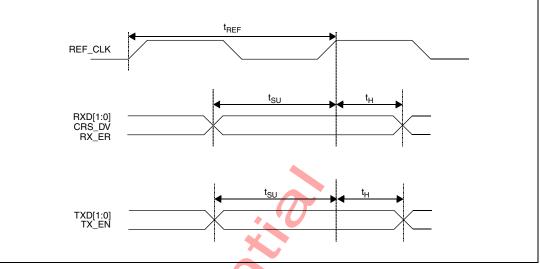

|    | 20.10  | Ethernet interface                       | ł |

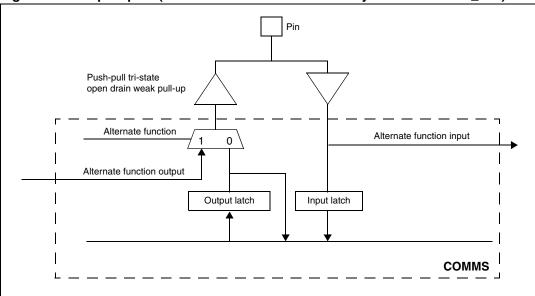

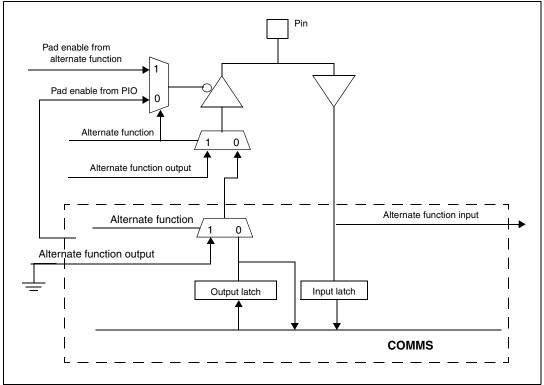

| 21 | Alterr | nate functions on PIO                    | ł |

|    | 21.1   | Alternate functions 364                  | 1 |

|    | 21.2   | PIO0 alternate functions                 | 3 |

|    | 21.3   | PIO1 alternate functions 368             | 3 |

|    | 21.4   | PIO2 alternate functions                 | ) |

|    | 21.5   | PIO3 alternate functions 373             | 3 |

|    | 21.6   | PIO4 alternate functions                 | 3 |

|    |        |                                          |   |

6/410

| 21.7  | PIO5 alternate functions 3  | 78 |

|-------|-----------------------------|----|

| 21.8  | PIO6 alternate functions 3  | 80 |

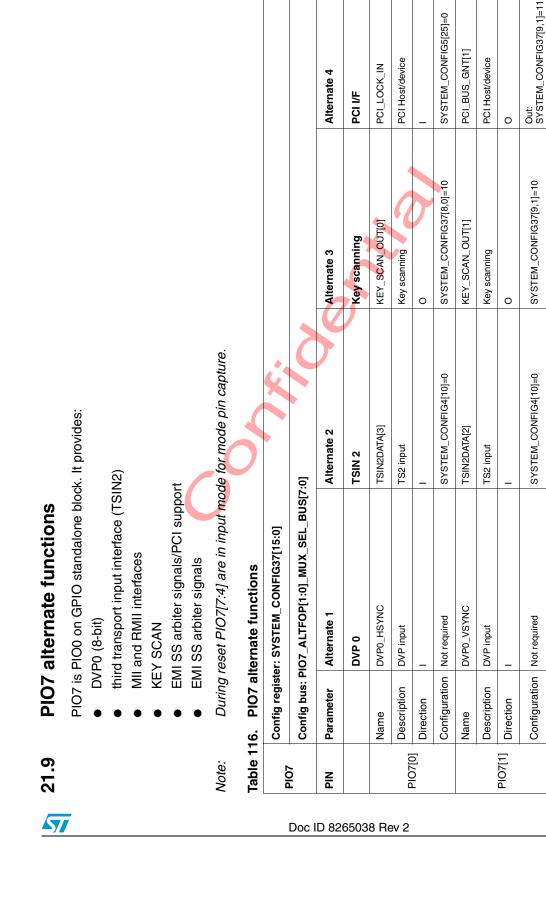

| 21.9  | PIO7 alternate functions 3  | 83 |

| 21.10 | PIO8 alternate functions 3  | 85 |

| 21.11 | PIO9 alternate functions 3  | 87 |

| 21.12 | PIO10 alternate functions 3 | 89 |

| 21.13 | PIO11 alternate functions 3 | 91 |

| 21.14 | PIO12 alternate functions 3 | 93 |

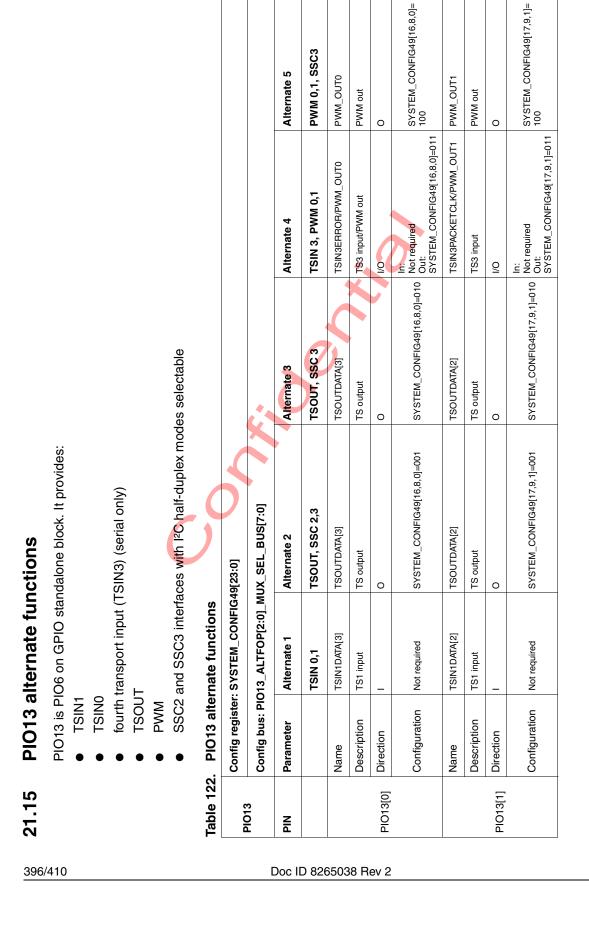

| 21.15 | PIO13 alternate functions 3 | 96 |

| 21.16 | PIO14 alternate functions 4 | 00 |

| 21.17 | PIO15 alternate functions 4 | 02 |

| 21.18 | PIO16 alternate functions 4 | 04 |

| Licon | ses                         | 06 |

| Licen | ses                         | 00 |

| Revis | sion history                | 09 |

|       |                             |    |

|       |                             |    |

22

23

## 1 Related documents

This datasheet is part of the STi7197 documentation suite which forms a complete system description and programming guide. This datasheet is intended for hardware engineers, and describes the pins, package, electrical characteristics, and timing information for the STi7197 device.

To obtain an up-to-date specification of this product, this datasheet should be read in conjunction with the latest relevant product errata sheet (buglist). If an errata sheet for this product exists, it will be obtainable from your STMicroelectronics representative.

The documents related to this datasheet are described in the following sections.

## 1.1 STi7197 programming manual

The *STi7197 programming manual* describes how to program and configure the STi7197 device. It is intended for software and system engineers.

## 1.2 CPU documentation

The ST40 core and its instruction set are documented in the *ST40 32-bit CPU Core Architecture Manual.*

The ST231 core and its instruction set are documented in the *ST231 CPU Core and Instruction Set Architecture Manual.*

## 2 Functional overview

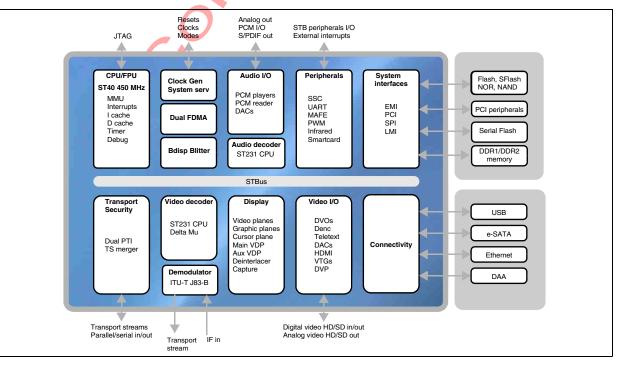

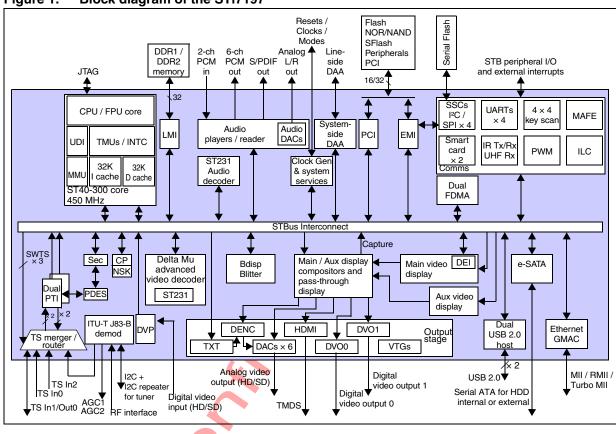

#### Figure 1. Block diagram of the STi7197

## 2.1 Front end

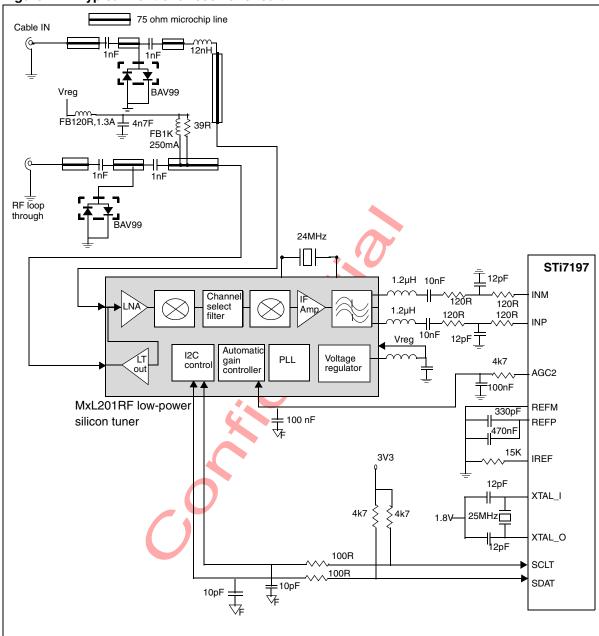

The STi7197 is designed to be optimized, both in cost and performance, with the most advanced Can and Silicon tuners available in the market and is compliant with the ITU-T J83 Annex B standard.

The STi7197 front end has one of the lowest power consumptions in the market today. This has been made possible because of technology and clock rate management. This also has the advantage of improving the channel acquisition and re-acquisition efficiency.

The *Figure 2* shows an application diagram for a typical front-end receiver circuit that can be used with the STi7197.

#### Figure 2. Typical front-end receiver circuit

## 2.2 QAM demodulator/FEC

The STi7197 front-end QAM section provides quadrature amplitude modulation (QAM) demodulation and forward error correction (FEC). The front end performs IF-to-MPEG2 block processing of QAM signals. It is intended for the digital transmission of compressed television, video, sound, and data services over cable, and is fully compliant with ITU-T J83 Annex B specification bitstreams. It can handle square (16, 64, 256-QAM) and non-square (32, 128-QAM) constellations.

Doc ID 8265038 Rev 2

57

The IF can be up to 57 MHz, and the sampling clock can be selected freely from a given range (constrained by the SAW filter and symbol rate characteristics). All further processing is fully digital, so no external feedback loop is required. The STi7197 handles a wide range of symbol rates, from the highest practical rates to rates as low as 0.87 Mbaud, even when there is a significant frequency offset.

The STi7197 provides all demodulation and FEC functions required for the recovery of QAM bitstreams with outstanding BER results. In addition, it includes several features that give simple and immediate access to various quality and status monitoring parameters.

The demodulator provides error-corrected MPEG transport stream outputs, which can be routed to the transport sub-system.

### 2.3 IF to MPEG2 TS block conversion

A high-performance 12-bit ADC samples, at sampling rates up to 60 MHz, and down-converts to baseband the intermediate frequency (IF) differential carrier signal produced by CATV tuners. The signal is then demodulated by the QAM demodulator to recover a byte stream. The FEC block then performs trellis decoding, convolutional de-interleaving, Reed–Solomon decoding, and de-randomizing to provide an MPEG2 transport stream. The QAM/FEC processing is fully compatible with ITU-T J83 Annex B streams up to 256 QAM.

## 2.4 Transport

The front-end demodulator outputs an error-corrected MPEG transport stream for routing to the transport subsystem. The STi7197 receives transport streams from broadcast networks through three parallel/serial transport stream inputs and one serial transport stream input. The fourth transport interface can be configured as a fourth input or as an output. Transport stream routing for DVB-CI+ (HD/SD profiles) modules can also be supported. One of the transport inputs is dedicated to the output of the internal QAM demodulator.

Transport streams are processed by two integrated programmable transport stream engines (PTIs). These perform demultiplexing, descrambling, and section filtering on multiple transport streams received from Broadcast, IP, and HDD sources.

### 2.5 Connectivity

The STi7197 has a wide range of options for connecting to external peripherals or IP network devices, such as wired Ethernet, xDSL, and Wi-Fi. These interfaces enable the delivery of IP streams received over broadband networks and support streaming over home networks. These interfaces include two USB host ports, a 32-bit PCI interface, and a high-speed Ethernet MAC/MII/RMII interface.

PCI uses the same physical interface as the EMI with dynamic interleaving of access types possible. Transport streams received through IP can be routed internally to the PTIs for demultiplexing and descrambling similar to the broadcast TS streams. The PTIs can concurrently process multiple TS streams from both sources.

## 2.6 Audio/video decoding

The STi7197 can decode H264, VC-1/WMV9, and MPEG2 HD and SD streams with concurrent decoding of one HD stream and one SD stream possible for PIP applications. AVS SD decoding is also supported. Multiple decoding of lower resolution streams can also be supported for Mosaic applications. The decoder is well proven in the industry and is powerful and flexible enough to decode other video formats, such as MPEG4 part2 and DivX (3.x, 4.x, and 5.x). It can also support concurrent H263 encode and decode for video conference applications.

A programmable ST231 CPU core provides the flexibility and performance for decoding multi-channel advanced audio streams. Concurrent decoding of an audio description channel is also supported.

## 2.7 Graphics and display

The STi7197 integrates a graphics and display sub-system that can deliver a high quality visual experience for applications. Graphics generation can use both the CPU and an independent multi-operator graphics accelerator that supports 2D graphics and 3D user interface effects. Graphics can be displayed on any one of three graphics planes. The graphics planes are combined, with video, using alpha blending and color keying. The graphics and video are combined by two independent display compositors, one for the Main TV and a second for output to a VCR or DVD-R. Two video planes are available for PIP on the main composition or downscaled video on the second composition. Video post-processing can be applied to resize, reformat, and de-interlace video between the encoded and intended display formats prior to composition. Advanced de-blocking and de-ringing processing can be applied to decoded MPEG2 SD video. With such capabilities, feature-rich displays can be generated including PIP, POP, Mosaics, animations, highlighting, blended overlays, scrolling subtitles, and so on.

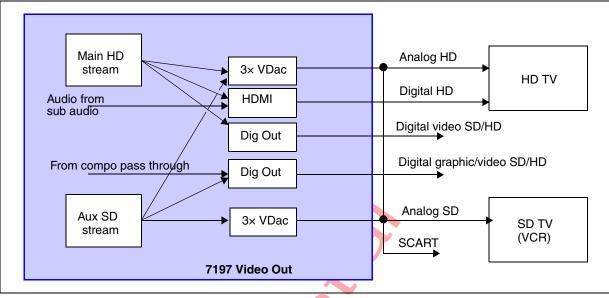

## 2.8 Audio/video outputs

The STi7197 has both HDMI and analog interfaces for outputting video to the TV/panel. In addition to the standard 720p and 1080i HD formats, the STi7197 supports 1080p60 display output on the HDMI interface. The analog interface comprises six video DACs with CGMS-A, Rovi™, and Dwight-Cavendish copy protection, whilst the HDMI interface supports the HDCP copy protection. For more information on HDMI features supported, refer to Section 2.13.

Audio is output over HDMI, S/PDIF, stereo analog DACs, and a digital PCM output interface. It is possible to output both compressed and decoded audio streams at the same time over different interfaces (for example, Dolby Digital 5.1 over S/PDIF with decoded and downmixed AAC-plus audio through the analog output). A 2-channel PCM input is also available for inputting audio from external sources such as a microphone (for example, for VOIP telephony).

### 2.9 Processors

The STi7197 embeds the latest ST40 class applications processor, the ST40-300 with 2– way, set associative caches, a 32 K instruction cache, and a 32 K data cache. At an operating frequency of 450 MHz it can deliver > 800 DMIPs performance<sup>(a)</sup>.

## 2.10 System interfaces

The STi7197 supports the latest DDR2 memory technology on its 32-bit local memory interface (LMI) providing a high bandwidth unified memory for code, data, audio and video buffers, graphics and so on. With two 2-Gbit devices in a ×16 configuration, up to 512 Mbytes capacity can be supported. The STi7197 also retains the ability to support DDR1 memory types.

A 16-bit external memory interface (EMI) is used for connecting to Flash and SRAM/peripherals supporting a standard 8/16-bit asynchronous read/write protocol. Synchronous or burst mode can also be supported. Both NOR and NAND Flash types can be used, with the ability to boot from, and perform code authentication checking from both types. Interfacing and authenticated booting from serial Flash attached through SPI is also supported.

## 2.11 DVR

Confidential

The STi7197 supports attachment of an HDD through e-SATA, USB, or EIDE (PIO mode) allowing DVR STBs to be developed. The e-SATA interface can independently support either internal or external SATA drive attachment. The STi7197 can support recording of up to four HD streams with local playback of an HD stream with trick modes, as well as playback of additional streams for export to client STBs over a home network. Streams can be encrypted to/from the HDD and to/from a home network for copy protection using AES, T-DES, or DES ciphers.

## 2.12 STB peripherals

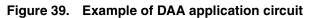

The STi7197 integrates a range of peripherals and interfaces to minimize or eliminate the external cost of implementing basic STB functions. These include UARTs and SSCs used for serial interfaces, I<sup>2</sup>C control buses, two smartcard controllers, a PWM module, IR receiver and transmitter, general-purpose programmable I/O, external interrupt inputs, and a controller for scanning/debouncing a  $4 \times 4$  key matrix. There are also two options available for implementing a software modem on the STi7197; a MAFE interface to connect to an external modem codec and integration of a system-side DAA circuit to connect to an external line-side DAA device. For HDMI interfacing, a dedicated I<sup>2</sup>C port is available, together with a hardware CEC line controller.

a. An extended mode of STi7197 can enable the operation of ST40-300 at 600 MHz that can deliver > 1100 DMIPS performance. Contact customer support for application note and guidance.

Doc ID 8265038 Rev 2

#### 2.13 **HDMI** interface

The STi7197 supports the following features compliant to HDMI 1.4a specification:

- 3D video •

- 3D video format timings Video resolution up to 1920 x 1080p @60 Hz \_

- \_ 3D over HDMI — Side-by-side (Half) and Top-and-Bottom formats

- Content Type

- Audio formats LPCM, Dolby Digital, and Dolby Digital Plus

- CEC

- HDCP

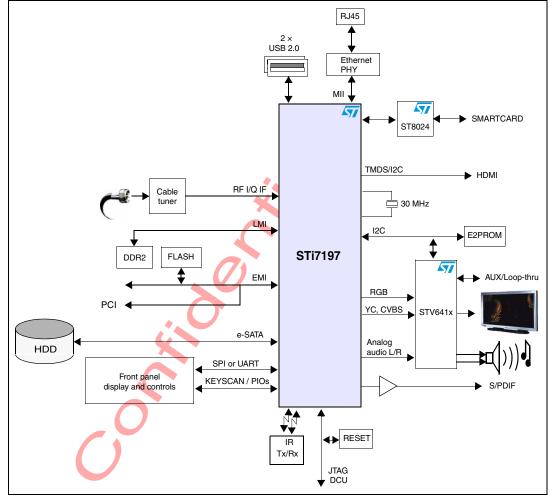

## 2.14 Target applications

#### 2.14.1 Cable applications

#### Figure 3. Typical DVR cable STB

## 3 System on chip subsystem overview

This section gives a top-level overview of the device components.

## 3.1 ITU-T J83 Annex B demodulator/FEC

- High-performance integrated 12-bit A/D converter suitable for direct IF architecture in all quadrature amplitude modulation (QAM) modes

- Decodes ITU-T J83-Annex B bit streams

- Forward error correction (FEC) compliant with ITU-T J83-Annex B with integrated deinterleaving SRAM

- Supports 16, 32, 64, 128, and 256 point constellations

- Two automatic gain control (AGC) outputs suitable for delayed AGC applications (sigma-delta outputs)

- Integrated signal quality monitors, plus lock indicator and interrupt pins

- RF signal loss detection and automatic recovery

- Easy controlling and monitoring using two-wire fast I<sup>2</sup>C bus

- Additional I<sup>2</sup>C bus (I<sup>2</sup>C repeater) dedicated to tuner control for minimum tuner disturbance

## 3.2 STBus interconnect

The STBus multipath unified interconnect provides high on-chip bandwidth and low latency accesses between modules. The interconnect operates hierarchically, with latency-critical modules placed at the top level. The multipath router allows simultaneous access paths between modules, and simultaneous read and write phases from different transactions to and from the modules. Split transactions maximize the use of the available bandwidth.

## 3.3 Processor core

The STi7197 integrates a 450 MHz ST40-300 processor core that features a 32-bit superscalar RISC CPU and IEEE-754 compliant floating point unit (FPU). The ST40-300 includes 2-way, set-associative caches and an interrupt controller with 15 user interrupt sources and an interrupt expansion port.

#### STi7197

## 3.4 External memory interface (EMI)

The EMI is a general-purpose interface for attaching Flash memory and peripherals. The EMI features are:

- Five banks

- Addressing up to at least 64 Mbytes of NOR Flash

- External bus master support through BUSREQ/BUSGNT signals

- Slave mode EMI support

- Single level cell (SLC) NAND Flash and boot from SLC NAND Flash

- Serial Flash support

- PCI interface, host and device selected on boot

- ATAPI PIO mode 4

- DVB-CI+

The STi7197 integrates one 32-bit DDR2-DDR1 interface. The interface can run up to 400 MHz when configured in DDR2 mode or up to 250 MHz when in DDR1 mode.

The LMI supports 32-bit configurations, including:

- 2 × 512 Mbits (×16) devices resulting in 128 Mbytes memory space

- 4 × 512 Mbits (×8) devices resulting in 256 Mbytes memory space

- 2 × 1 Gbits (×16) devices resulting in 256 Mbytes memory space

- 2 × 2 Gbits (×16) devices resulting in 512 Mbytes memory space

- 4 × 1 Gbits (×8) devices resulting in 512 Mbytes memory space

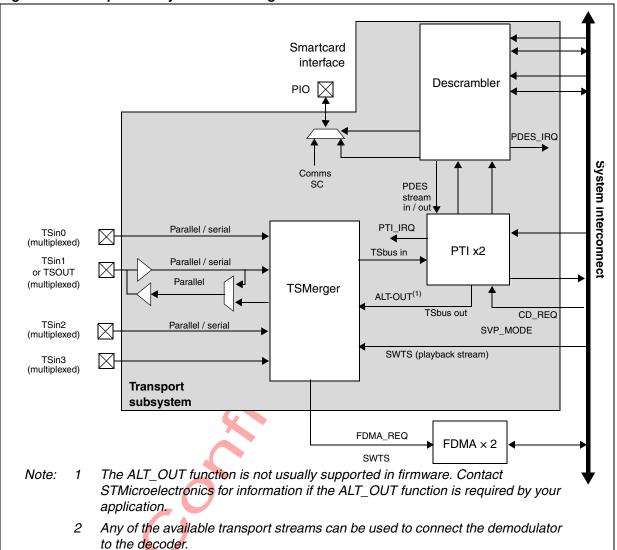

## 3.6 STB transport subsystem

### 3.6.1 Overview

The transport subsystem (TS) is able to receive ATSC, DVB, DIRECTV, DCII, OpenCable, ARIB BS4 transport streams containing high-definition (HD) and standard-definition (SD) programs. It demultiplexes and descrambles the transport streams to deliver PES packets to the video and audio decoders.

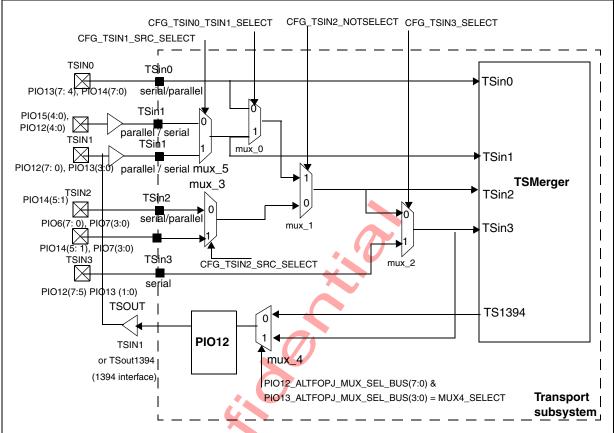

Figure 4. Transport subsystem block diagram

The STi7197 receives transport streams from broadcast networks through three parallel/serial transport stream inputs and one serial transport stream input. The fourth transport interface can be configured as a fourth input or as an output. Note that one of the transport inputs is dedicated to the output of the internal QAM demodulator/FEC.

Transport streams are processed by two integrated programmable transport stream engines (PTIs). These perform demultiplexing, descrambling, and section filtering on multiple transport streams received from Broadcast, IP, and HDD sources.

## 3.6.2 Dual programmable transport interface (PTI)

Each PTI is a dedicated transport engine and integrates its own CPU to handle the transport stream PID filtering, demultiplexing, descrambling, and data filtering. It interfaces with the programmable descrambler (PDES) for descrambling. Each PTI receives a transport stream from a dedicated input port, processes it, and outputs it either to the memory through its DMA channels or to a dedicated transport output port.

STi7197

The PTIs perform PID filtering, demultiplexing, descrambling, and data filtering on up to four transport streams. The PTIs extract PCRs with time stamps and make them available to the CPU for clock recovery and audio/video synchronization.

PES data is transferred by DMA to memory buffers. Section data is transferred by DMA to separate buffers for further processing by the CPU. The PTIs extract indexing information and transfer packets, using DMA, to an intermediate buffer for writing to HDD.

The following transport streams are supported:

- AVS video

- MPEG2 transport stream demultiplexing, and service information extraction, conforming to:

- MPEG2 systems

- MPEG4 systems

- DVB

- DirecTV DSS format

- DirecTV AMC stream format

- MPEG2 TS audio/visual formats:

- MPEG2 A/V over MPEG2 TS

- H264 video over MPEG2 TS<sup>4</sup>

- VC-1 over MPEG2 TS

- WMA9, WMA9 pro over MPEG2 TS

- AAC and AAC+ audio over MPEG2 TS

- A/V streams encapsulated in RTP packets according to these protocols (parsing):

- MPEG2 A/V in RTP

- MPEG 4 pt2 video in RTP

- MPEG 4 audio including AAC and AAC+ in RTP

- H264 video in RTP

- VC-1 video in RTP

- AVS video in RTP

- Processing of:

- WMV9/WMA9 streaming content in ASF files using client server interaction

- Parsing of MP3 or MPEG 4 AAC audio from Audio File format versions 2, 3 and 4

- A/V streams, such as DivX, delivered in AVI files

- WAV and AIFF files

Each PTI performs PID filtering to select audio, video, and data packets to be processed. It supports up to 151 PID slots, and routes streams to and from the descrambler. Streams can be descrambled using:

- DES

- TDES

- AES

- Multi-2

- DVB-CSA

- NDS ICAM

Each PTI has a  $64 \times 16$  byte section filter core. Following four filtering modes are available:

- Wide match mode: 64 × 16 byte filters

- Long match mode: 128 × 8 byte filters

- Positive/negative mode: 64 × 8 byte filters with positive/negative filtering at the bit level

- APG filtering mode

Matching sections are transferred to memory buffers for processing by software.

### 3.7 DVD decryption

CSS (DVD-video), CPRM (DVD-RW), and CPPM (DVD-audio) decryption is provided for the DVD stream.

### 3.8 Video decoder

The STi7197 video decoding subsystem includes the Delta-Rasta core capable of decoding H264/VC-1/MPEG2 HD/SD streams and AVS SD streams.

The following are Delta-Rasta features;

- Supports H264 in-loop deblocking filter, VC-1 deblocking filter and overlapped transform, AVS deblocking filter, and deblocking and deringing post-processing algorithms for MPEG2

- Supports non-real-time MPEG2 to H264 transcoding

The decoder is partially implemented in software which is executed on a dedicated ST231 CPU core. The decoder gets its data from memory and stores decoded data back into memory.

The decoder uses a mixed hardware and firmware architecture with a hardwired data path and an ST231 core engine. It provides flexibility for firmware upgrades, error concealment, or trick modes. The ST231 core can be used for other coders or decoders at lower resolution, when the VC-1, H264, AVS SD, or MPEG2 decoders are not running.

Streams are decoded picture-by-picture from an elementary stream buffer. Decoding, reconstruction, and prediction buffers are set up by the CPU. CPU control of bit-buffer pointers provides flexibility for trick modes and out-of-sequence decoding.

Semantic or syntax errors are detected by the decoder and failing slices are replaced up to the next slice or picture.

20/410

#### STi7197

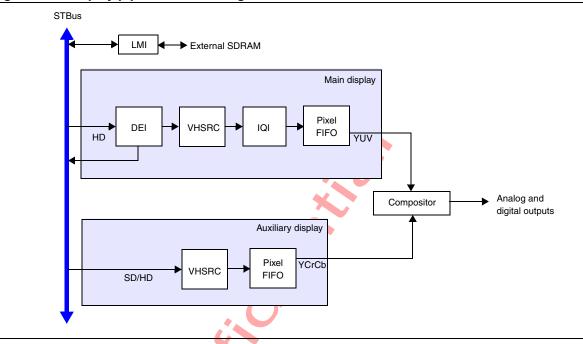

## 3.9 Main and auxiliary display

The main and auxiliary display pipelines form a high-quality scaling engine for video display processing. The two display pipelines are shown in *Figure 5*.

Figure 5. Display pipelines block diagram

The same video is displayed through both pipelines, but each display processor can be set up to format the video differently and to display video with different timing. Separate video timing generators (VTGs) are provided to support this feature. The display processors adapt the decoded video to a format suitable for display, taking into account differences in scanning method, resolution, aspect ratio, and scanning frequency.

The main-display processor receives decoded or acquired video from memory, and performs block-to-line conversion, pan and scan, and vertical and horizontal format conversion. There is also a de-interlacer (DEI) to perform interlace-to-progressive conversion using motion estimation. This is used to display 480i, 576i, or 1080i interlaced sources on a progressive display (480p, 720p, or 1080p). The main display processor has image quality improvement (IQI) that improves the subjective image quality by methods, such as high frequency peaking and edge sharpening.

The auxiliary-display processor receives decoded or acquired (and possibly decimated) video, and performs pan and scan, vertical format conversion, horizontal format conversion, and color tint and saturation control. The output line size is limited to SD on the auxiliary-display processor and is intended to output video for VCR recording.

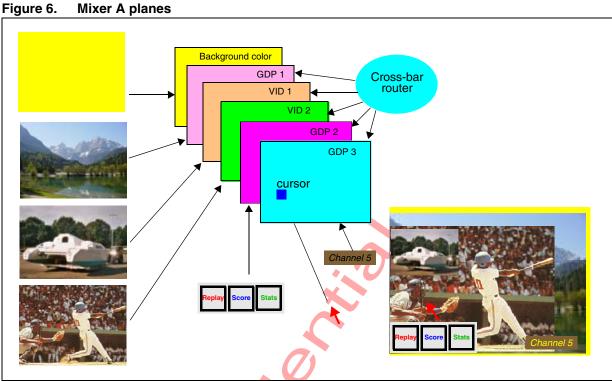

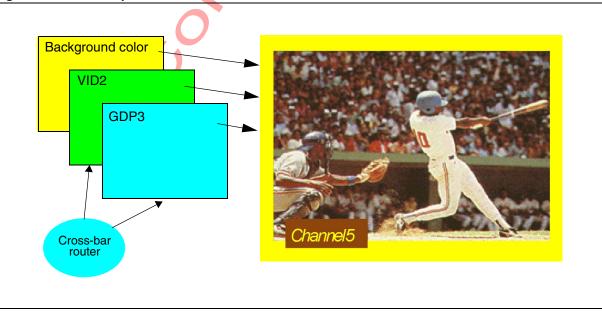

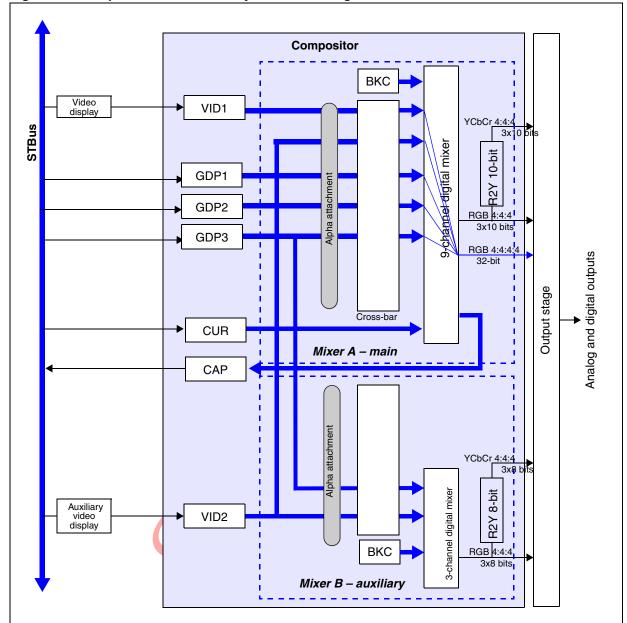

#### 3.10 Compositor

#### 3.10.1 Overview

The compositor comprises two real-time, multiplane digital mixers.

The main mixer (mixer A), which is intended for main HDTV video output, is composed of:

- one background color

- two video planes (VID1 and VID2)

- three graphics planes (GDP1, GDP2, and GDP3)

- one cursor plane

The auxiliary mixer (mixer B), which is intended for auxiliary SDTV video output, is composed of:

- one background color

- one video plane (VDP2)

- one graphics plane (GDP3)

The compositor receives the video planes from the video display processor, and the 2D graphics planes from the memory through GDP. Each mixer alpha blends graphics and video layers on a pixel basis based on alpha component values provided by each layer.

After real-time processing by the display plane pipelines, pixel data is mixed in mixer A or mixer B. The output of mixer A supports up to full HD resolutions and is intended as the main TV display (*Figure 6*). The output of mixer B (*Figure 7*) supports up to full SD resolutions and is intended as an auxiliary display for applications, including connection to a VCR. The mixer outputs are fed to the STi7197's output stage.

The mixers provide RGB and/or YCbCr digital outputs that are used by the video output subsystem to produce the HDTV video outputs (analog, digital, and composite) and the SDTV video outputs (analog and digital).

The compositor also comprises additional components that can be used to enhance the display presentation of video and graphics. These include an alpha plane attachment and a cross-bar router. A capture pipeline is also provided for capturing main video streams or mixer A or B output streams and storing them in memory.

Confidential

57

### STi7197

#### 3.10.2 Compositor layout

The *Figure 8* shows a block diagram of the compositor. It presents the dataflow and memory access of all compositor modules.

The graphics and cursor pipelines read pixel data and related control information directly from memory. The video input pipelines accept data from the main and auxiliary video display pipelines. Video and graphics data (captured for the compositor data flow by the capture pipeline) is written back to the memory with a resolution up to 32 bits/pixel. The real-time processing performed by each pipeline is controlled by the register programming.

The digital mixer A successively blends video layers (VID1, VID2), graphics layers (GDP1, GDP2, and GDP3), cursor layer (CUR), and a background color. A cross-bar router enables the hierarchy of the GDP1, GDP2, GDP3 and VID1, VID2 layers to be programmed. Each layer can be independently enabled or disabled. The blending operates in the RGB color domain, so each layer supplies an RGB signal ( $3 \times 12$  bits), with transparency information that provides the weighting coefficients for the mixing operation at a given depth.

The digital mixer B successively blends one video layer (VID2) with one graphics layer (GDP3) and a background color. A cross-bar router enables the hierarchy of the GDP3 and VID2 layers to be programmed. In the digital mixer B, each layer can be independently enabled or disabled, and blending operates in the RGB color domain.

All sub-blocks are controlled by the hardware registers. All these registers can be read but not necessarily written. The graphics planes are link-list based and have their register set written through the memory (register download is controlled directly by the hardware after initialization). All other registers can be written. Each plane block supports a specific set of bitmap formats. Each plane starts reading data from memory when it is enabled in mixer A or mixer B.

Figure 8. Graphics and video subsystem block diagram

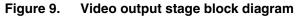

### 3.11 Video output

The Video Output subsystem is the unit responsible for reading decoded video frames and graphics data from external memory and to reformat, rasterize, and mix them for display.

The STi7197 can output video program on main HD TV Out and on aux SD TV (VCR) Out with separate timebase if required (VTG0, VTG1). It is also able to deliver the same SD video on both main and auxiliary video outputs using the capture feature. The main data paths corresponding to these typical configurations are shown in *Figure 9* as well as the principal units which constitute the Video Output stage.

#### 3.11.1 Main HDTV video output

The following are the main functional blocks included in the main video flow:

- Main VDP, including High-Definition Display Pipeline with IQI and DEI engines

- VTG0 (free running or master of the aux VTG1)

- Capture output port with vertical and horizontal resizing, shared with auxiliary video flow

- Compositor—Mixer five to four (in: video: RGB or YCbCr, 3x graphic: RGB; out: 2x video: RGB and YCbCr, pass through, capture), shared GDP3 and VDP aux with auxiliary compositor

- TV Out—receives its data from the compositor channel (video: RGB or YCbCr, graphic: RGB); the video data is then formatted and output in digital, analog and audiovideo composite to be used by external devices

- DVI-HDCP or HDMI-compliant copy-protected digital output

- Player multichannel (8-ch) and GP FIFO

- S/PDIF player and GP FIFO

- Four S/PDIF players with I<sup>2</sup>S-to-S/PDIF converters

- Triple HD/SD DAC (analog output)

- Two digital video outputs, that is, DVO0 (video) is 8-bit or 16-bit and DVO1(GFX) is 24bit

- AWG—arbitrary waveform generator (Dwight Cavendish and Rovi<sup>™</sup> copy protection support)

Note: The compositor includes a pipeline, which is able to mix one cursor, one or two video, up to three graphic layers, and one background layer. The data is then delivered to the TV Out. The capture port supports vertical and horizontal resizing output data with filtering for upsizing.

### 3.11.2 Auxiliary SDTV video flow

The following are the main functional blocks included in the auxiliary video flow:

- VTG1—free running or slave of the main HDTV VTG0

- Video Display Pipe High-definition (VDP aux)

- Capture output port with vertical and horizontal resizing, shared with main HDTV video flow

- Compositor—mixer two to three (YCbCr 8-bit and RGB 8-bit and capture), shared GDP3, and VDP aux with main HDTV compositor

- SD DENC—SDTV/VCR video encoder

- AWG—arbitrary waveform generator (Dwight Cavendish and Rovi<sup>™</sup> copy protection support)

- Triple HD/SD DAC (analog output)—The DAC outputs can be components (Y/C) or composite (PAL, SECAM, NTSC CVBS); all six DACs can output the auxiliary display in SD format for SCART output

Note:

The compositor includes a pipeline, which is able to mix one video, one graphic layer, and one background layer. The data is then delivered to the TV Out. The capture port supports vertical and horizontal resizing output data with filtering for upsizing.

## 3.12 2D blitter display engine

The 2D blitter display engine (BDisp 2 engine) is a software controlled output display generator, which can also be used as a CPU accelerator for graphics picture handling. The BDisp 2 engine, is an evolution of BDisp engine. It is a triple-source 2D DMA, with a set of powerful operators.

The 2D blitter display engine retrieves data from the local memory through three input sources, source 1, source 2, and source 3. Sources 1, 2, and 3 are used simultaneously for read/modify/write operations.

STi7197

2D blitter display engine features are as follows:

- Two composition queues

- Four application queues

- Sub-byte S1 and S2 access

- Five-tap vertical filters

- Eight-tap horizontal filters

- Flicker filter adaptive

- Matrix conversion on input and output for: rgb2ycbcr, ycbcr2rgb,bt601, and bt709

- CLUT 1/2/4/8

- Color reduction

- Logical operation

- Clipmask

- Rotation

- Plane mask

- Color key capability

- BlueRay Disc run-length decoder (BD RLD)

- High definition-DVD 2/8-bit run-length decoder (HD-DVD RLD)

2D blitter display engine functions are as follows:

- Solid color fill of rectangular window •

- Solid color shade (fill and alpha blending)

- One-source copy, with one or several operators enabled (color format conversion, 2D scaling)

- Two-source copy with alpha blending

- 4:2:2 / 4:20 capabilities, as source format

- Fully programmable matrix used for color space conversion, PSI, special effects

- Color expansion (CLUT to true color)

- Color correction (gamma, contrast, gain)

- 2D resize engine with high quality filtering

- Adaptive flicker filter from memory-to-memory

- Rectangular clipping

- VC-1 range mapping/range reduction compensation algorithm

- Programmable source/target scanning direction, both horizontally and vertically, to cope correctly with overlapping source and destination area.

#### 3.13 Audio subsystem

#### **Overview**

The main function of the STi7197 audio subsystem is to decode and play different standards of multi-channel compressed audio streams. The audio stream (encoded or decoded) is received either from an external source through the PCM input interface or an internal source, such as the transport subsystem through memory.

The audio decoder may have to decode simultaneously two different encoded audio streams when an audio description channel is provided (the main audio stream and a 2-channel audio description channel) or when recording and listening to two different audio streams.

#### **PCM** mixing

The decoded audio stream can be mixed with a PCM file stored in memory following an optional sample rate conversion to adapt the sampling rate of the two streams. PCM mixing is also used when a description channel is decoded and then mixed with the main audio stream. The PCM mixing is fully implemented in the software running on the ST231.

#### PCM output: downmixing

The multi-channel decoded PCM stream can be downmixed to generate a 2-channel PCM stream. This down mixed stream can be then output unmixed through a stereo 24-bit DAC while the PCM-mixed decoded audio stream can be delivered onto a 6-channel digital PCM output and a digital S/PDIF output.

#### Compressed data: S/PDIF output

Compressed audio data can also be delivered on the S/PDIF output to be decoded by an external decoder/amplifier.

#### **HDMI** output

The STi7197 HDMI output can deliver audio data to an HDMI sink device. The audio data is delivered by the audio subsystem to the HDMI subsystem through internal I<sup>2</sup>S-to-S/PDIF players/converters (see *Figure 10*).

#### Audio decoder features

The audio decoder features are as follows:

- Decoding of the following audio formats: MPEG1 layer I/II, MP3, MPEG2- Layer II, Dolby Digital, Dolby Digital Plus (up to 7.1), MPEG4 AAC-LC, MPEG4 AACplus (HE-AAC, AAC+SBR) v1 and v2 (up to 5.1), WMA9, WMA9pro (up to 7.1)

- PCM mixing with internal or external source with sample rate conversion (32, 44.1, 48 kHz)

- Encoded (IEC 61937) or decoded (IEC 60958) digital audio on S/PDIF output

- Multi-channel down-mixing for output over HDMI (up to eight channels), PCM output (up to six channels), and analog output (up to two channels)

- PCM audio input (I<sup>2</sup>S format)

- Audio description channel decoding

- Postprocessing (channel virtualization)—Dolby Prologic downmix, volume control, and bass redirection

#### Audio transcoding

The STi7197 supports the transcoding of advanced audio formats for output over S/PDIF as formats recognized by external audio decoders. The following two transcode operations are available:

- Dolby Digital Plus-to-Dolby Digital

- MPEG4 AACplus-to-DTS

#### Audio subsystem blocks

The audio subsystem includes the following functional units.

- One audio processor ST231 core, running at 450 MHz, which executes the decoding algorithms, the sample-rate conversion, the postprocessing, and the volume control.

- One PCM reader, which captures the data at the PCM input and stores it in memory through an FDMA channel. (This is mutually exclusive with PCM player 0 since they share the same pads.)

- Two PCM players, which receive decoded PCM data from memory through FDMA channels. One PCM player delivers the down-mixed PCM output to the audio DAC. The other PCM player produces the stereo or multi-channel decoded audio stream on a 7-wire PCM output (I<sup>2</sup>S protocol).

- Two quad-frequency synthesizers, which generate the PCM clock (oversampling clock 256 × Fs), used by the S/PDIF, PCM players, and audio DAC.

- One stereo 24-bit audio DAC with differential outputs.

- An S/PDIF player, which reads decoded PCM data or encoded data from memory through an FDMA channel, and outputs them on the S/PDIF output.

See *Figure 10* for a detailed block diagram of the audio subsystem.

Audio subsystem block diagram 2-channel Ch 0/1 PCM reader 0 2-channel PCMI 2-channel PCM player Audio DACs 2-channel PCM R multi-channel Ch 0/1 Bus PCM player 0 Ch 2/3 6-channel PCMO 8-channel PCM ST ► Ch 4/5 HDMI Audio Audio ST231 Multi-channel 4 × I<sup>2</sup>S to S/PDIF HDMI PCM (up to 8-ch) conversion audio 2-ch PCM or compressed audio Compressed audio IEC 60958 S/PDIF S/PDIF player IEC 61937

Figure 10.

30/410

Doc ID 8265038 Rev 2

The host CPU and the FDMA assist in the audio decoding process. Since the audio decoder is a frame decoder, the host CPU (ST40 core) controls the audio processor frame-by-frame. A mailbox is used for communication between the two processors.

The host CPU is also required to do the PES parsing and the frame syncword detection.

The FDMA builds the ES buffer to feed the PCM and S/PDIF players, and stores the data captured by the PCM reader in memory.

The PCM reader, PCM player, and S/PDIF player transfer data to/from memory through FDMA.

## 3.14 FDMA controllers

The STi7197 has two multichannel, burst-capable, direct memory access controllers:

- FDMA0—real-time paced channels: S/PDIF, PCM Player 0-1, and SWTS

- FDMA1—PES parsing, PCI-Master, SWTS when streaming from Ethernet or USB, UART, SSC, and free-running general-purpose DMAs

External pacing signals are available for DMA transfers with external peripherals.

### 3.15 Interfaces

Confidential

#### 3.15.1 Internal peripherals

The STi7197 has many dedicated internal peripherals, including:

- Four ASCs (UARTs), two of which are generally used by the Smartcard controllers, one to support hardware flow control signals

- Two Smartcard interfaces and clock generators

- Four external SSCs for I<sup>2</sup>C/SPI master/slave interfaces

- One four-channel PWM module with two PWM outputs and programmable frequency

- One Teletext serializer

- 17 GPIO ports (3.3 V tolerant)

- One modem analog front end (MAFE) interface

- One single infrared transmitter/receiver supporting RC5, RC6 and RECS80, RC-MM 1.5, DIRECTV and Echostar codes

- One UHF remote control digital input

- One interrupt level controller with external interrupt inputs

- Two independent USB 2.0 host controllers, each with its own integrated PHY

- One front-panel key scanning support

- One e-SATA interface

### 3.15.2 Ethernet controller

The STi7197 has an integrated Ethernet controller and MAC processor for delivery of IP-based A/V streams in hybrid IP STBs and for home network connectivity. It also includes an MII/RMII port for connection to an external PHY. Ethernet features are as follows:

- Half/full duplex, full duplex flow control

- VLAN tagging support

- MII and RMII external interface

- Direct interface with STE101P and similar PHYs through MII or RMII

- Able to accept clock from external PHY/Home network device in MII mode

- Dedicated scatter/gather link list DMA

- 100 Mbits/s sustained transfer rates to and from memory

- 32 H/W perfect match MAC address filters

The controller can also be used to interface through overclocked MII interface (up to 300 Mbits/s) to an external non-Ethernet Phy as a MoCA Phy for example.

### 3.15.3 Dual Smartcard interfaces

Both Smartcard interfaces are ISO7816, EMV2000 and NDS compliant, with the addition of a simple external power switch.

A programmable hardware power control feature allows the power control signal to be switched when card insertion or removal is detected.

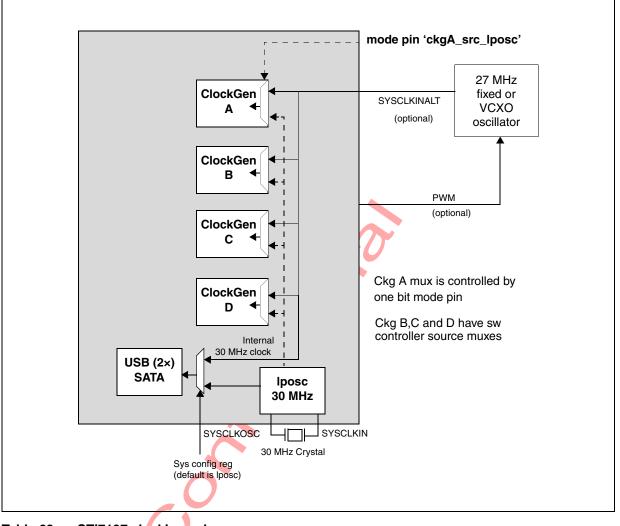

## 3.16 Clock generation

The STi7197 features five clock generation blocks:

- ClockGen A:  $2 \times PLLs$  main for CPU and interconnect clocks

- ClockGen B: 2 × FreqSynth for video, display and peripheral clocks

- ClockGen C: 1 × FreqSynth for audio clocks

- ClockGen D: 1 × PLL for memory clocks

## 3.17 System services

The STi7197 supports a number of on-chip system service functions including:

- integrated VCXOs (DCOs) for clock recovery

- debug through a single JTAG port

- reset and watchdog controller

- two power saving modes: reduced power mode and low power/standby mode

#### STi7197

## 4 Package mechanical data

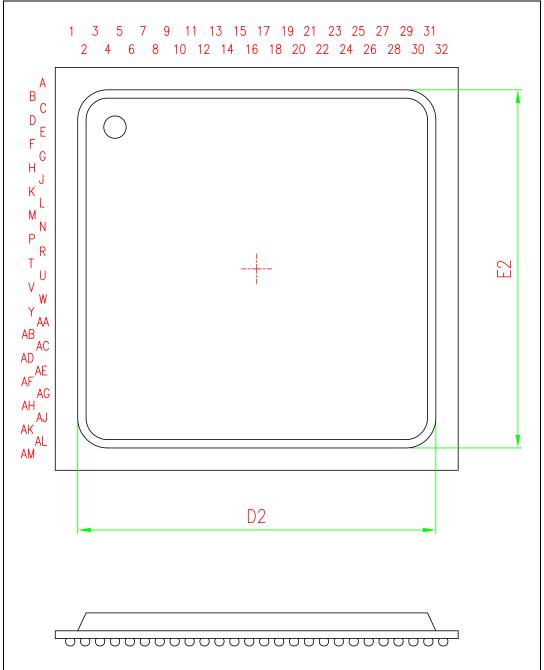

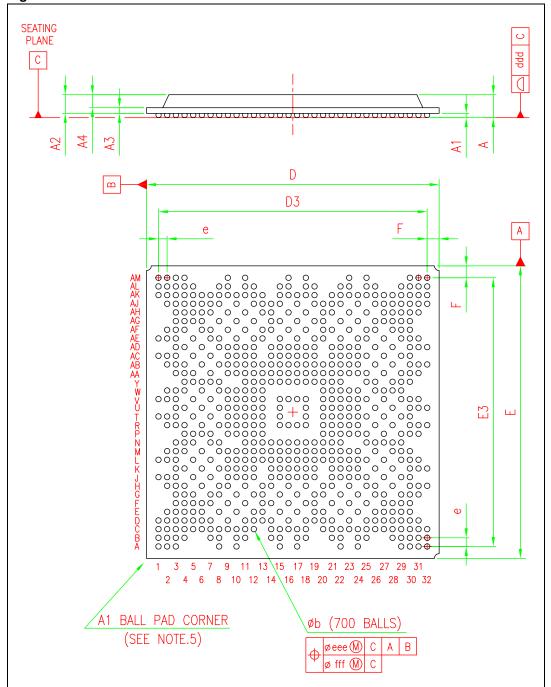

## 4.1 27 × 27 package

Package type: FPBGA 700 balls. Body: 27 × 27 mm.

Figure 11. Top view

57

Doc ID 8265038 Rev 2

Information classified Confidential - Do not copy (See last page for obligations)

Downloaded from Arrow.com.

Figure 12. Bottom view

Doc ID 8265038 Rev 2

| Dimension | Millimete | rs    |       | Inches   |        |        | - Notes |

|-----------|-----------|-------|-------|----------|--------|--------|---------|

| Dimension | Min       | Тур   | Max   | Min      | Тур    | Max    | Notes   |

| Α         | -         | -     | 2.19  |          | -      | 0.8622 | (1)     |

| A1        | 0.27      | -     | -     | 0.0106   | -      |        | -       |

| A2        | -         | 1.72  | -     | -        | 0.0677 |        | -       |

| A3        | -         | 0.52  | -     | -        | 0.0205 |        | -       |

| A4        | -         | 1.20  | -     | -        | 0.0472 |        | -       |

| b         | 0.45      | 0.50  | 0.55  | 0.0177   | 0.0197 | 0.0217 | (2)     |

| D         | 26.80     | 27.00 | 27.20 | 1.055    | 1.063  | 1.070  | -       |

| D1        | -         | 24.80 | -     |          | 0.9764 | -      | -       |

| D2        | -         | 24.00 |       |          | 0.9449 | -      | -       |

| E         | 26.80     | 27.00 | 27.20 | 1.055    | 1.063  | 1.070  | -       |

| E1        | -         | 24.80 | -     | -        | 0.9764 | -      | -       |

| E2        | -         | 24.00 | -     |          | 0.9449 | -      | -       |

| е         | -         | 0.80  | -     |          | 0.0315 | -      | -       |

| F         | -         | 1.10  | -     | <u> </u> | 0.0433 | -      | -       |

| ddd       | -         | -     | 0.20  | -        | -      | 0.0079 | -       |

| eee       | -         | -     | 0.15  | -        | -      | 0.0059 | (3)     |

| fff       | -         | -     | 0.08  | -        | -      | 0.0315 | (4)     |

| Table 1. JEDEC standard package dimensions |

|--------------------------------------------|

|--------------------------------------------|

FPBGA stands for Fine pitch Plastic Ball Grid Array.

Fine pitch: e < 1.00 mm</li>

The total profile height (Dim A) is measured from the seating plane to the top of the component.

The maximum total package height is calculated by the following methodology:

A2 Typ+A1 Typ + V (A1<sup>2</sup>+A3<sup>2</sup>+A4<sup>2</sup> tolerance values)

- 2. The typical ball diameter before mounting is 0.50 mm.

- 3. The tolerance of position that controls the location of the pattern of balls with respect to datums A and B. For each ball there is a cylindrical tolerance zone eee perpendicular to datum C and located on true position with respect to datums A and B as defined by e. The axis perpendicular to datum C of each ball must lie within this tolerance zone.

- 4. The tolerance of position that controls the location of the balls within the matrix with respect to each other. For each ball there is a cylindrical tolerance zone fff perpendicular to datum C and located on true position as defined by e. The axis perpendicular to datum C of each ball must lie within this tolerance zone. Each tolerance zone fff in the array is contained entirely in the respective zone eee above. The axis of each ball must lie simultaneously in both tolerance zones.

- The terminal A1 corner must be identified on the top surface by using a corner chamfer, ink or metallized markings, or other feature of package body or integral heatslug.

A distinguishing feature is allowable on the bottom surface of the package to identify the terminal A1 corner. Exact shape of each corner is optional.

35/410

Information classified Confidential - Do not copy (See last page for obligations)

#### STi7197

### 4.2 Environmentally friendly packages

In order to meet environmental requirements, ST offers these devices in different grades of ECOPACK<sup>®</sup> packages, depending on their level of environmental compliance. ECOPACK<sup>®</sup> specifications, grade definitions and product status are available at: *www.st.com*. ECOPACK<sup>®</sup> is an ST trademark.

# 5 Ordering information

### Table 2. Ordering information

| Order code | Package             | Description                      |  |

|------------|---------------------|----------------------------------|--|

| STI7197ZUD | FPBGA 27 mm × 27 mm | Development version, all options |  |

Confidential

# 6 Front-end registers

Registers are accessed from the processor interface. All writable register bits are reset to 0 unless otherwise stated. Read-only registers have no defined reset value. The processor should not write 1s to undefined register bits. Similarly, when reading a register, the processor should mask undefined bits.

All register addresses are hexadecimal values. Signed registers are 2's complement.

Note: Any addresses not listed in the following table is reserved and must be set to zero.

# 6.1 Register map

| Table 3. Register summary table |                |                                         |           |

|---------------------------------|----------------|-----------------------------------------|-----------|

| Address<br>offset               | Register       | Description                             | Reference |

| Demodul                         | ator registers |                                         |           |

| 0x00                            | EQU_0          | QAM mode                                | page 45   |

| 0x01                            | EQU_1          | Equalizer adaptation step               | page 46   |

| 0x03                            | EQU_3          | State machine control                   | page 46   |

| 0x04                            | EQU_4          | Corner point control                    | page 47   |

| 0x05                            | EQU_5          | Constellation corner point rate (LSBs)  | page 47   |

| 0x06                            | EQU_6          | Constellation corner point rate (MSBs)  | page 47   |

| 0x07                            | EQU_7          | Constellation corner point (MSBs)       | page 48   |

| 0x08                            | EQU_8          | Noise estimation (LSBs)                 | page 48   |

| 0x09                            | EQU_9          | Noise estimation (MSBs)                 | page 48   |

| 0x0A                            | EQU_10         | Imaginary constellation part            | page 49   |

| 0x0B                            | EQU_11         | Real constellation part                 | page 49   |

| 0x0C                            | INITDEM_0      | Demodulation frequency (LSBs)           | page 49   |

| 0x0D                            | INITDEM_1      | Demodulation frequency (MSBs)           | page 49   |

| 0x0E                            | INITDEM_2      | Scanning latency                        | page 50   |

| 0x10                            | INITDEM_3      | Demodulation scan step (LSBs)           | page 50   |

| 0x11                            | INITDEM_4      | Demodulation scan step control          | page 50   |

| 0x12                            | INITDEM_5      | Demodulator control                     | page 51   |

| 0x014                           | DELAGC_0       | Maximum PWM rate for AGC2               | page 51   |

| 0x015                           | DELAGC_1       | Minimum PWM rate for AGC2               | page 51   |

| 0x016                           | DELAGC_2       | Maximum PWM rate for AGC1               | page 52   |

| 0x017                           | DELAGC_3       | Minimum PWM rate for AGC1               | page 52   |

| 0x18                            | DELAGC_4       | Ratio between AGC1/AGC2 PWM rate slopes | page 52   |

38/410

| Address<br>offset | Register  | Description                                        | Reference |  |

|-------------------|-----------|----------------------------------------------------|-----------|--|

| 0x19              | DELAGC_5  | AGC2 PWM rate threshold                            | page 53   |  |

| 0x1A              | DELAGC_6  | AGC freeze control                                 | page 53   |  |

| 0x1C              | DELAGC_7  | ADC average magnitude (LSBs)                       | page 54   |  |

| 0x1D              | DELAGC_8  | ADC average magnitude (MSBs)                       | page 54   |  |

| 0x20              | DELAGC_10 | Analog AGC1                                        | page 55   |  |

| 0x21              | DELAGC_11 | Analog AGC1                                        | page 55   |  |

| 0x22              | DELAGC_12 | Analog AGC2                                        | page 55   |  |

| 0x23              | DELAGC_13 | Analog AGC2                                        | page 55   |  |

| 0x24              | WBAGC_0   | Analog AGCs                                        | page 56   |  |

| 0x25              | WBAGC_1   | Analog AGCs                                        | page 56   |  |

| 0x26              | WBAGC_2   | WBAGC reference                                    | page 56   |  |

| 0x27              | WBAGC_3   | WBAGC control                                      | page 57   |  |

| 0x28              | WBAGC_4   | Acquisition counter (LSBs)                         | page 57   |  |

| 0x29              | WBAGC_5   | Acquisition counter (MSBs)                         | page 58   |  |

| 0x2A              | WBAGC_6   | AGC loop response (LSBs)                           | page 58   |  |

| 0x2B              | WBAGC_7   | AGC loop response (MSBs)                           | page 58   |  |

| 0x2C              | STLOOP_1  | Symbol timing recovery loop gain (LSBs)            | page 58   |  |

| 0x2D              | STLOOP_2  | Symbol timing recovery loop gain (MSBs)            | page 59   |  |

| 0x2E              | STLOOP_3  | Symbol timing recovery loop integral gain (LSBs)   | page 59   |  |

| 0x2F              | STLOOP_4  | Symbol timing recovery loop gain scale             | page 59   |  |

| 0x30              | STLOOP_5  | Symbol rate (LSBs)                                 | page 60   |  |

| 0x31              | STLOOP_6  | Symbol rate (lower mid byte)                       | page 60   |  |

| 0x32              | STLOOP_7  | Symbol rate (upper mid byte)                       | page 61   |  |

| 0x33              | STLOOP_8  | Symbol rate (MSBs)                                 | page 61   |  |

| 0x34              | STLOOP_9  | Symbol timing recovery loop phase control          | page 61   |  |

| 0x35              | STLOOP_10 | Symbol timing recovery loop algorithm control      | page 62   |  |

| 0x38              | CRL_1     | Carrier recovery loop gain                         | page 62   |  |

| 0x39              | CRL_2     | Carrier recovery loop gain reduction factor        | page 63   |  |

| 0x3A              | CRL_3     | Carrier recovery loop control                      | page 64   |  |

| 0x3B              | CRL_4     | Carrier recovery loop capture                      | page 64   |  |

| 0x3C              | CRL_5     | Carrier recovery loop phase accumulator (LSBs)     | page 64   |  |

| 0x3D              | CRL_6     | Carrier recovery loop phase accumulator (mid byte) | page 65   |  |

| 0x3E              | CRL_7     | Carrier recovery loop phase accumulator (MSBs)     | page 65   |  |

| 0x3F              | CRL_8     | 2nd carrier recovery loop coefficient              | page 65   |  |

| Address | Register summary table<br>Register | Description                                             | Reference |

|---------|------------------------------------|---------------------------------------------------------|-----------|

|         |                                    | Corrier recovery lean frequency effect (LCDs)           | 2000 66   |

| 0x40    | CRL_9                              | Carrier recovery loop frequency offset (LSBs)           | page 66   |

| 0x41    | CRL_10                             | Carrier recovery loop frequency offset (lower mid byte) | page 66   |

| 0x42    | CRL_11                             | Carrier recovery loop frequency offset (upper mid byte) | page 66   |

| 0x43    | CRL_12                             | Carrier recovery loop frequency offset (MSBs)           | page 67   |

| 0x44    | CRL_13                             | Carrier recovery loop sweep value (LSBs)                | page 67   |

| 0x45    | CRL_14                             | Carrier recovery loop sweep value (MSBs)                | page 67   |

| 0x48    | PMFAGC_0                           | PMFAGC lock threshold (LSBs)                            | page 68   |

| 0x49    | PMFAGC_1                           | PMFAGC lock threshold (MSBs)                            | page 68   |

| 0x4A    | PMFAGC_2                           | PMFAGC control                                          | page 68   |

| 0x4C    | PMFAGC_3                           | Post-filter digital AGC (PMFAGC)                        | page 69   |

| 0x4D    | PMFAGC_4                           | Post-filter digital AGC (PMFAGC)                        | page 69   |

| 0x4E    | PMFAGC_5                           | Post-filter digital AGC (PMFAGC)                        | page 69   |

| 0x50    | INTER_0                            | Interrupt mask 1                                        | page 70   |

| 0x51    | INTER_1                            | Interrupt mask 2                                        | page 70   |

| 0x52    | INTER_2                            | Interrupt 1                                             | page 71   |

| 0x53    | INTER_3                            | Interrupt 2                                             | page 72   |

| 0x58    | SIG_FAD_0                          | Signal fading control                                   | page 72   |

| 0x59    | SIG_FAD_1                          | Signal fading magnitude                                 | page 73   |

| 0x5A    | SIG_FAD_2                          | Signal fading low threshold                             | page 73   |

| 0x5B    | SIG_FAD_3                          | Signal fading high threshold                            | page 73   |

| 0x5C    | NEW_CRL_0                          | CRL direct gain in blind mode                           | page 73   |

| 0x5D    | NEW_CRL_1                          | CRL integral gain in blind mode                         | page 74   |

| 0x5E    | NEW_CRL_2                          | CRL direct gain in LMS_1 mode                           | page 74   |

| 0x5F    | NEW_CRL_3                          | CRL integral gain in LMS_1 mode                         | page 74   |

| 0x60    | NEW_CRL_4                          | CRL direct gain in LMS_2 mode                           | page 75   |