Enhanced ST20 32-bit VL-RISC CPU

4 Kbyte data cache, 2 Kbyte SRAM

Unified memory interface

support for low-cost DVB-CI

• single transport stream input

integrated DVB, descrambler

Graphics/display

support for DVB transport streams

■ MPEG-2 MP@ML video decoder

2D paced blitter engine with fill function

blitter based display compositor

formats. Link-list control

• 200 MHz, single cycle cache, 4 Kbyte instruction cache.

• up to166 MHz,16-bit wide SDR SDRAM interface

four separately configurable banks, 8/16-bits wide

Programmable flash memory interface

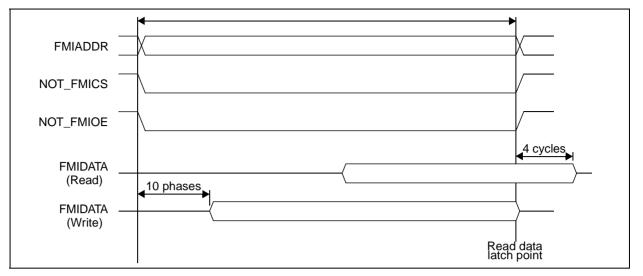

SRAM, peripheral, Flash, SFlash<sup>™</sup> support

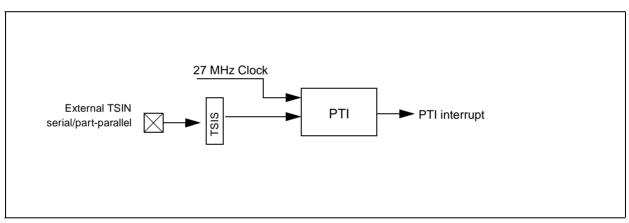

Programmable transport interface (PTI)

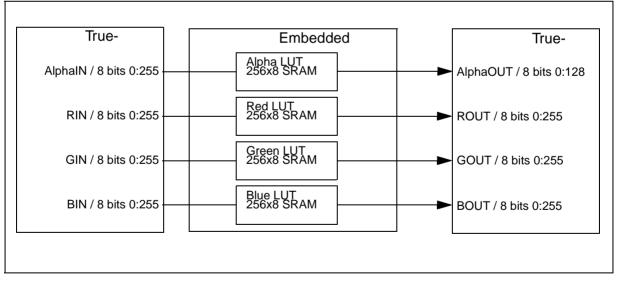

fully programmable horizontal and vertical SRCs.

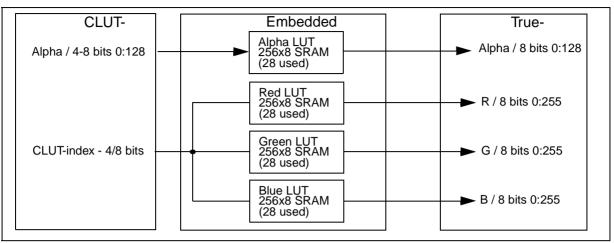

8 bpp CLUT graphics, 256 x 30 bits (AYCbCr) CLUT entries. 16 bpp true color graphics, RGB565, ARGB1555

# STx5119

# Low-cost interactive set-top box decoder

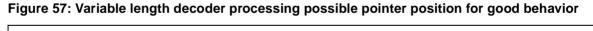

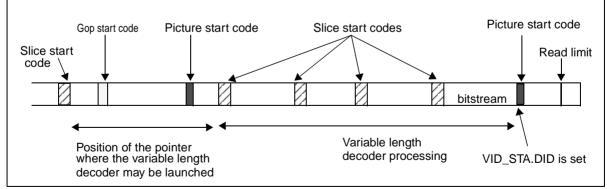

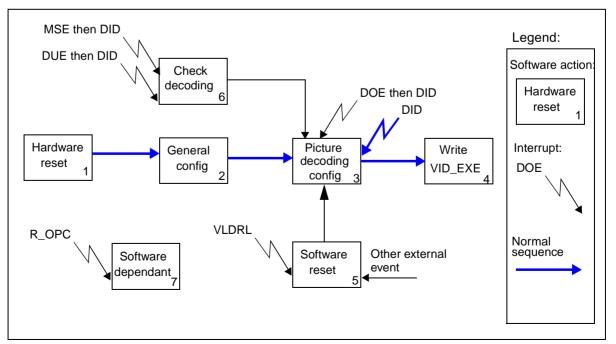

## ADVANCE DATASHEET

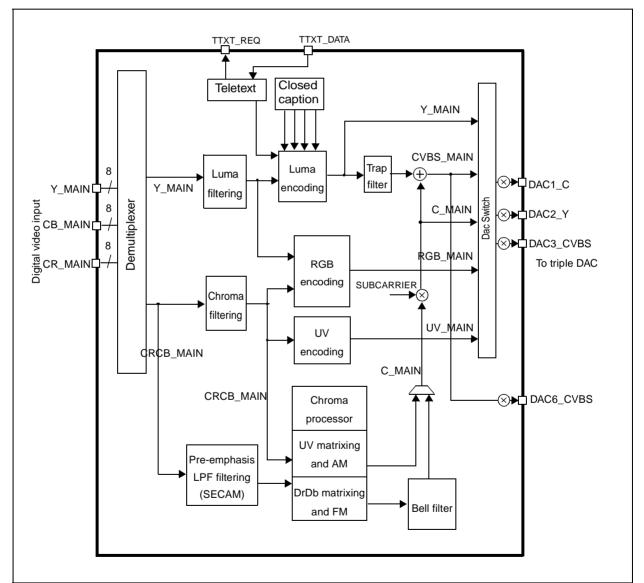

#### PAL/NTSC/SECAM encoder

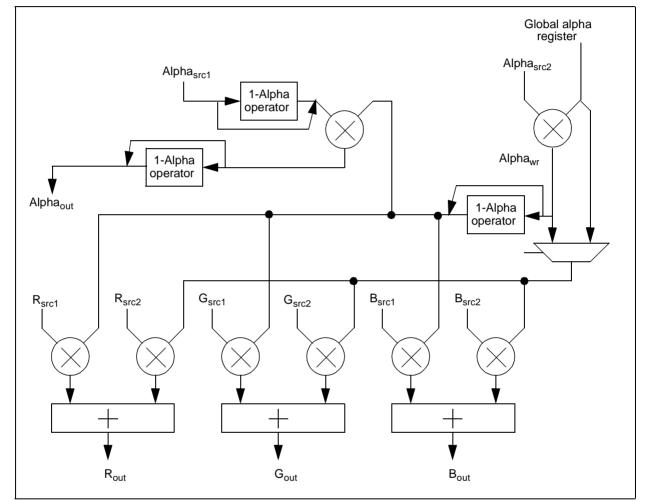

- RGB, CVBS, Y/C and YUV outputs with four 10-bit DAC outputs. RGB/CVBS or YUV/CVBS or YC/CVBS.

- encoding of CGMS, Teletext, WSS, VPS, close caption

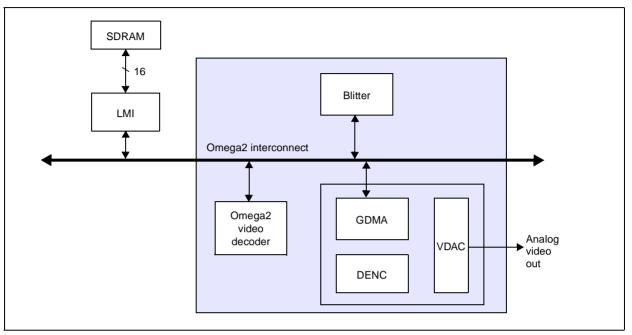

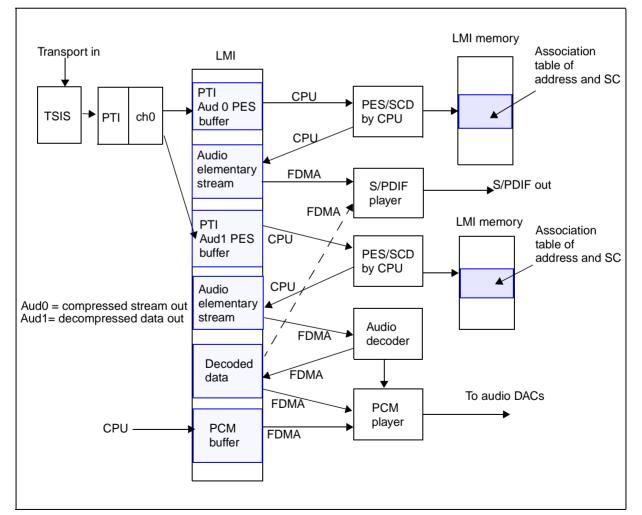

#### Audio subsystem

- MPEG-1 layers I/II

- simultaneous MPEG audio decode on audio DACs and output of Dolby streams on S/PDIF

- IEC958/IEC1937 digital audio output interface

- integrated stereo audio DAC system

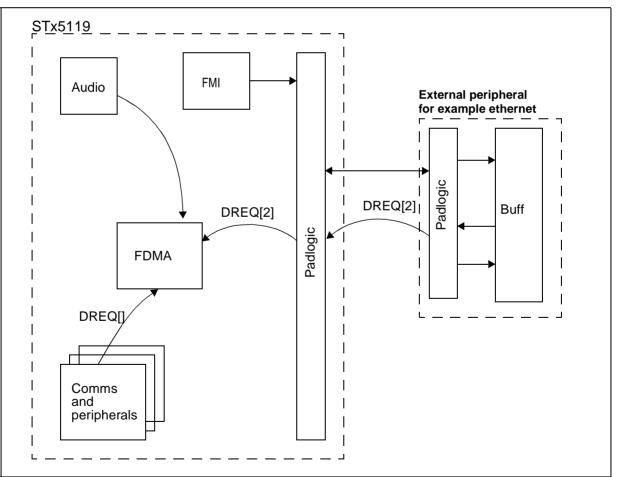

### Central DMA controller

### On-chip peripherals

- two ASCs (UARTs) with Tx and Rx FIFOs

- three 8-bit banks of parallel I/O and one 7-bit bank

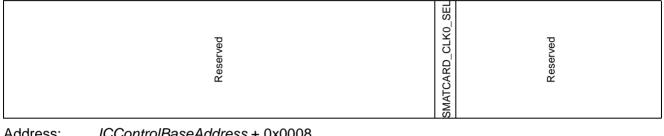

- one smartcard interface and clock generator

- two SSCs for I<sup>2</sup>C/SPI master/slave interfaces

- infrared transmitter/receiver

- integrated VCXO

- low-power / RTC / watchdog controller

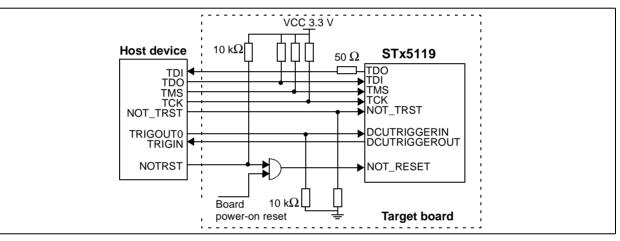

### ■ JTAG/TAP interface

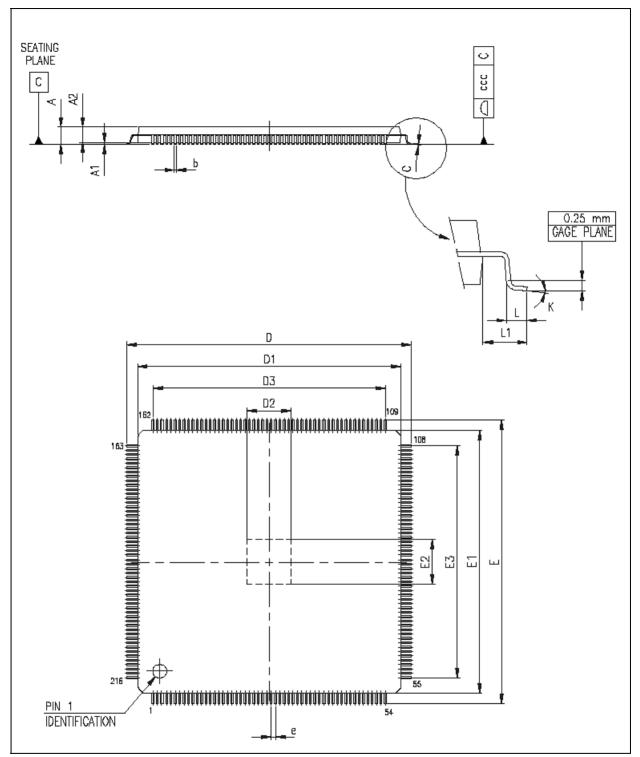

■ Package 24 mm x 24 mm LQFP216

Confidentia

## December 2005

7939391A

#### STMicroelectronics Confidential

This is preliminary information on a new product now in development or undergoing evaluation. Details are subject to change without notice.

# Contents

|            | Chapter 1 | Applications                                |

|------------|-----------|---------------------------------------------|

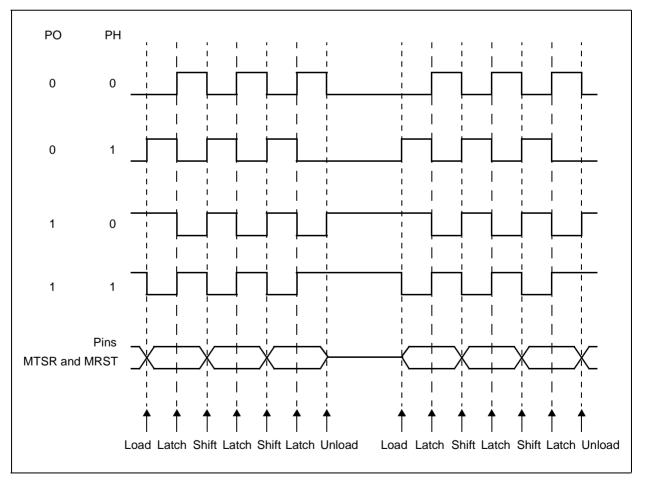

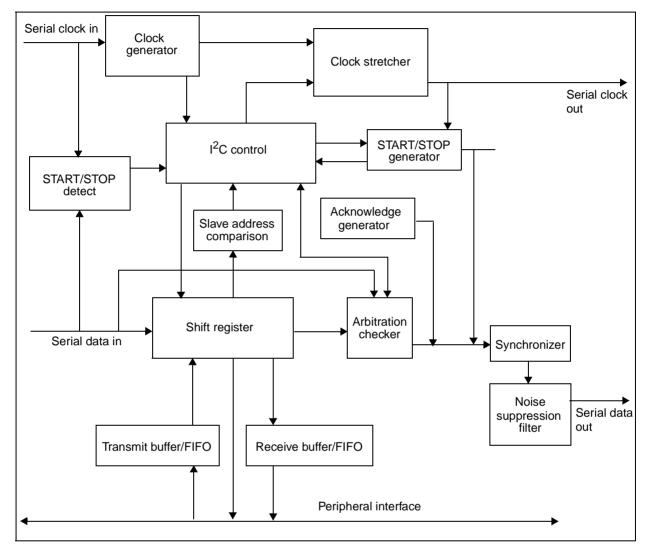

|            | Chapter 2 | Audio and video summary specification       |

|            | Chapter 3 | Architecture features                       |

|            | 3.1       | Introduction                                |

|            | 3.2       | Omega2 (STBus) interconnect14               |

|            | 3.3       | Processor core                              |

|            | 3.4       | Memory subsystem                            |

|            | 3.5       | Transport stream processing15               |

|            | 3.6       | MPEG graphics and display processing16      |

|            | 3.7       | Graphics and display16                      |

| _          | 3.8       | Digital encoder                             |

| t:         | 3.9       | Audio subsystem                             |

| Č          | 3.10      | Central DMA controller                      |

| ð          | 3.11      | Internal peripherals                        |

| onfidentia | 3.12      | Clock generation                            |

|            | Chapter 4 | Dataflow                                    |

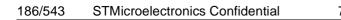

|            | 4.1       | Video decode flow                           |

|            | 4.2       | Standard audio decode flow21                |

|            | 4.3       | Real-time traffic                           |

|            | Chapter 5 | Package specifications 24                   |

|            | 5.1       | Exposed pad description25                   |

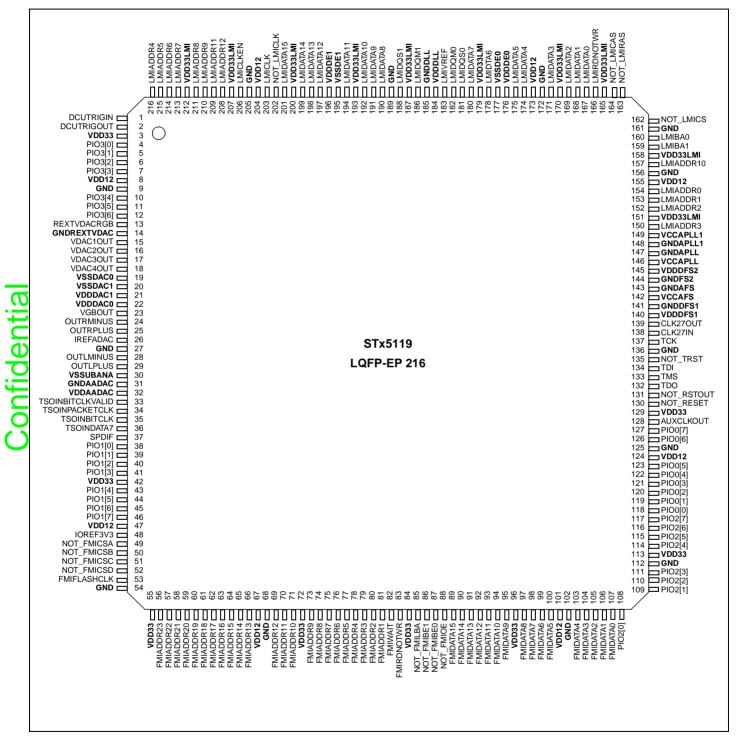

|            | Chapter 6 | Pin information                             |

|            | 6.1       | Pin data                                    |

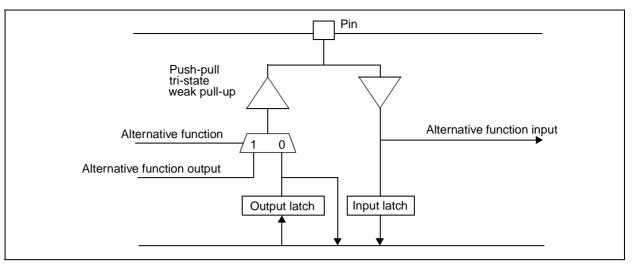

|            | 6.2       | Alternative functions (mapped to GPIO pins) |

|            | Chapter 7 | Connections                                 |

|            | 7.1       | Power supplies                              |

|            | 7.2       | System                                      |

| ST | x51 | 19 | 1 |

|----|-----|----|---|

|----|-----|----|---|

|     | 7.3                                               | Transport stream                       |

|-----|---------------------------------------------------|----------------------------------------|

|     | 7.4                                               | Flash memory interface (FMI)           |

|     | 7.5                                               | SDRAM interface for LMI41              |

|     | 7.6                                               | Audio interface                        |

|     | 7.7                                               | Video interface                        |

|     | 7.8                                               | Peripherals                            |

|     | 7.9                                               | Debug link                             |

|     | Chapter 8                                         | Configuration registers 48             |

|     | Chapter 9                                         | Register base addresses 54             |

|     | 9.1                                               | Base addresses                         |

|     | Chapter 10                                        | Interrupt system                       |

|     | 10.1                                              | Overview                               |

| Π   | 10.2                                              | Interrupt controller                   |

| ij  | 10.3                                              | Interrupt level controller             |

| der | 10.2<br>10.3<br>10.4<br><b>Chapter 11</b><br>11.1 | Interrupt assignments                  |

| j   | Chapter 11                                        | Interrupt system registers63           |

| ō   | 11.1                                              | Interrupt control registers            |

| O   | 11.2                                              | Interrupt level controller registers   |

|     | Chapter 12                                        | Memory system                          |

|     | 12.1                                              | Memory map                             |

|     | 12.2                                              | CPU cache                              |

|     | Chapter 13                                        | Cache registers                        |

|     | Chapter 14                                        | Local memory interface (LMI)85         |

|     | 14.1                                              | Introduction                           |

|     | 14.2                                              | STBus interface                        |

|     | 14.3                                              | SDRAM interface                        |

|     | Chapter 15                                        | Local memory interface (LMI) registers |

| Cha    | apter 16 | Flash and peripheral memory interface (FMI)           |

|--------|----------|-------------------------------------------------------|

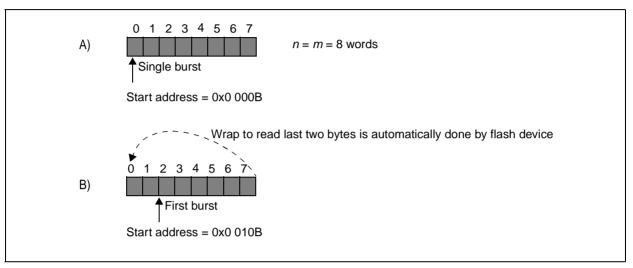

|        | 16.1     | Supported burst flash memory devices100               |

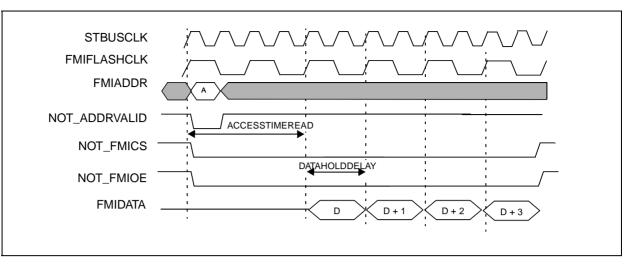

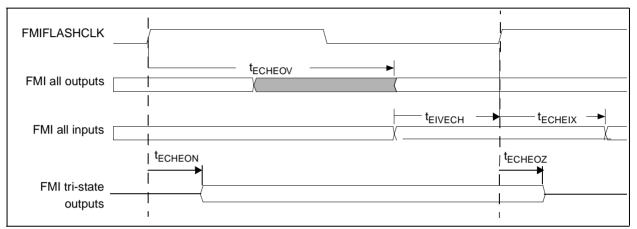

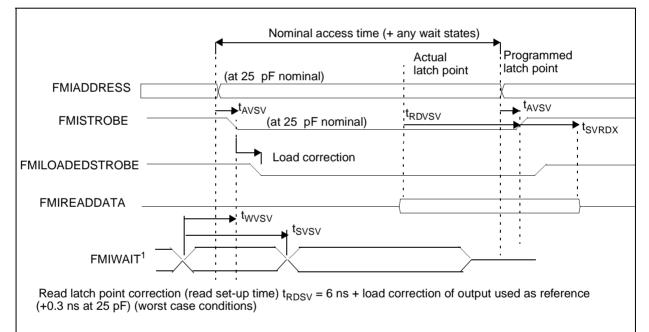

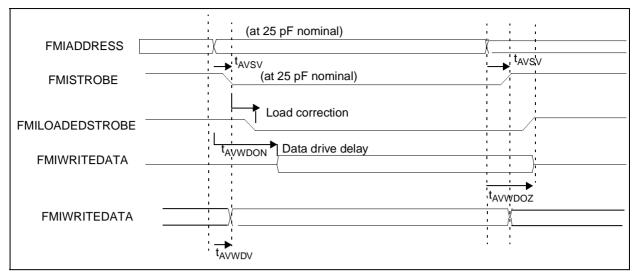

|        | 16.2     | Signal and strobe generation101                       |

|        | 16.3     | Bank position and size                                |

|        | 16.4     | Bank options                                          |

|        | 16.5     | Generic access cycle                                  |

|        | 16.6     | FMI flash interface                                   |

| Cha    | apter 17 | Flash and peripheral memory interface (FMI) registers |

|        | 17.1     | FMI bank sizing                                       |

|        | 17.2     | FMI bank control                                      |

|        | 17.3     | FMI bank options                                      |

| Cha    | apter 18 | System services                                       |

|        | 18.1     | Brief overview                                        |

| 3      | 18.2     | States of operation                                   |

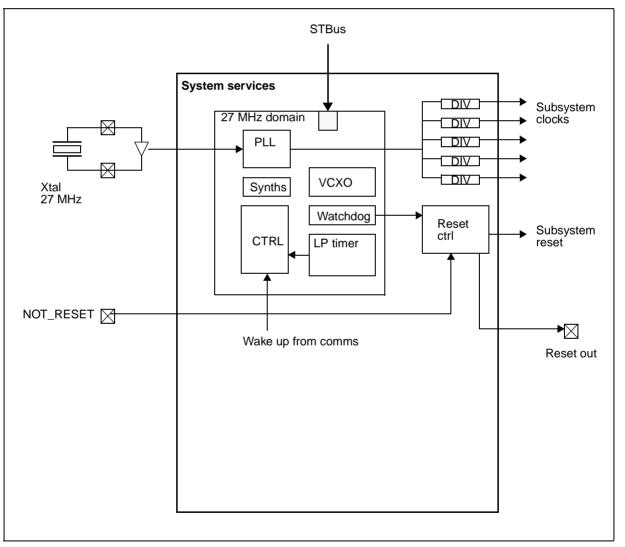

| -      | 18.3     | Clock generation and distribution125                  |

| 2<br>S | 18.4     | Reduced power mode129                                 |

|        | 18.5     | Standby mode                                          |

| 5      | 18.6     | Real-time counter (RTC)131                            |

| )      | 18.7     | Integrated clock recovery (VCXO)131                   |

|        | 18.8     | Smartcard power control                               |

|        | 18.9     | Reset control                                         |

|        | 18.10    | CPU programmable interrupt                            |

| Cha    | apter 19 | System services registers 137                         |

|        | 19.1     | System services control registers                     |

|        | 19.2     | PLL clock generation registers141                     |

|        | 19.3     | Frequency synthesizer clock generation registers      |

|        | 19.4     | Reduced power control                                 |

|        | 19.5     | Low power control registers146                        |

|        | 19.6     | Real-time counter registers148                        |

|        | 19.7     | Integrated clock recovery (DCO) registers150          |

|        | 19.8     | Smartcard power control registers152                  |

## STx5119

57

|          | 19.9                                                                             | Reset control registers                                                                                                                                                                                                                           |

|----------|----------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 19.10                                                                            | CPU programmable interrupt register155                                                                                                                                                                                                            |

|          | Ob any (any 00                                                                   |                                                                                                                                                                                                                                                   |

|          | Chapter 20                                                                       | Programmable transport interface (PTI)                                                                                                                                                                                                            |

|          | 20.1                                                                             | Overview                                                                                                                                                                                                                                          |

|          | 20.2                                                                             | PTI functions                                                                                                                                                                                                                                     |

|          | 20.3                                                                             | PTI architecture                                                                                                                                                                                                                                  |

|          | 20.4                                                                             | PTI operation                                                                                                                                                                                                                                     |

|          | 20.5                                                                             | Interrupt handling                                                                                                                                                                                                                                |

|          | 20.6                                                                             | DMA operation                                                                                                                                                                                                                                     |

|          | 20.7                                                                             | Section filter                                                                                                                                                                                                                                    |

|          | Chapter 21                                                                       | Programmable transport interface (PTI) registers                                                                                                                                                                                                  |

|          | 21.1                                                                             | DMA registers                                                                                                                                                                                                                                     |

|          | 21.2                                                                             | Input interface registers                                                                                                                                                                                                                         |

| ש        | 21.3                                                                             | PTI configuration registers                                                                                                                                                                                                                       |

| <u> </u> | 21.4                                                                             | Transport controller mode register                                                                                                                                                                                                                |

| <u></u>  |                                                                                  |                                                                                                                                                                                                                                                   |

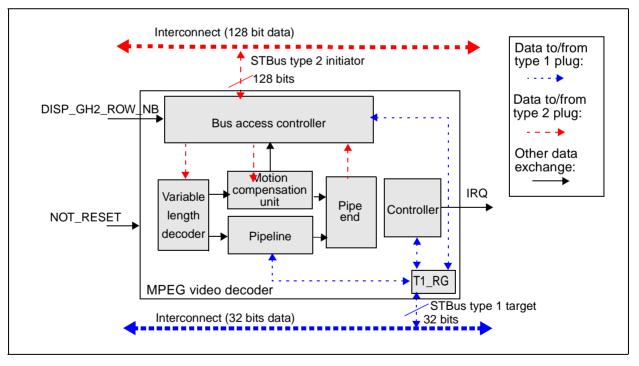

| ide      | Chapter 22                                                                       | MPEG video decoder                                                                                                                                                                                                                                |

| nfide    | Chapter 22<br>22.1                                                               | MPEG video decoder         186           Overview         .186                                                                                                                                                                                    |

| Confide  | 21.4<br>Chapter 22<br>22.1<br>22.2                                               |                                                                                                                                                                                                                                                   |

| Confide  | <b>Chapter 22</b><br>22.1<br>22.2<br>22.3                                        | Overview                                                                                                                                                                                                                                          |

| Confide  |                                                                                  | Overview                                                                                                                                                                                                                                          |

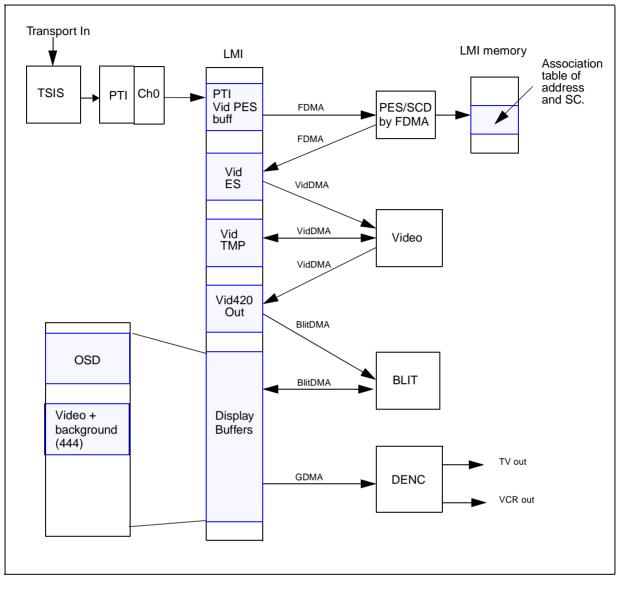

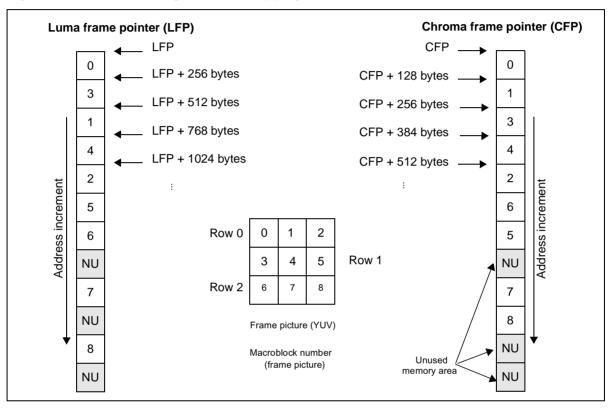

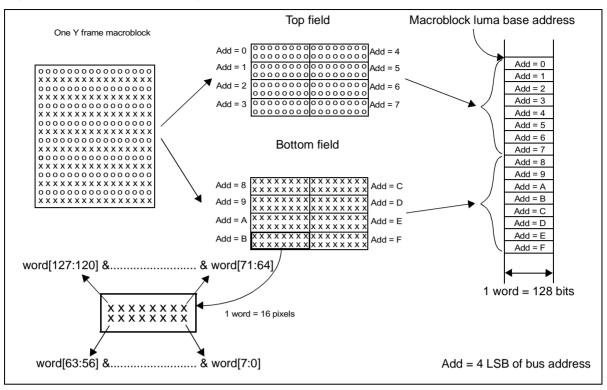

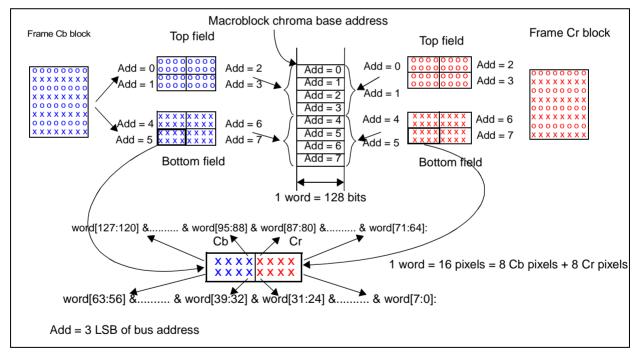

| Confide  | 22.3                                                                             | Overview.186Main functions.186Buffer organization.188                                                                                                                                                                                             |

| Confide  | 22.3<br>22.4                                                                     | Overview   .186     Main functions   .186     Buffer organization   .188     Video decoding tasks   .192                                                                                                                                          |

| O        | 22.3<br>22.4<br>22.5                                                             | Overview.186Main functions.186Buffer organization.188Video decoding tasks.192Video decoding.195                                                                                                                                                   |

| 0        | 22.3<br>22.4<br>22.5<br>22.6                                                     | Overview186Main functions186Buffer organization188Video decoding tasks192Video decoding195Resets202                                                                                                                                               |

| 0        | 22.3<br>22.4<br>22.5<br>22.6<br>Chapter 23                                       | Overview.186Main functions.186Buffer organization.188Video decoding tasks.192Video decoding.195Resets.202MPEG video decoder registers.203                                                                                                         |

| 0        | 22.3<br>22.4<br>22.5<br>22.6<br>Chapter 23<br>Chapter 24                         | Overview.186Main functions.186Buffer organization.188Video decoding tasks.192Video decoding.195Resets.202MPEG video decoder registers.2032D blitter display engine.213                                                                            |

| 0        | 22.3<br>22.4<br>22.5<br>22.6<br>Chapter 23<br>Chapter 24<br>24.1                 | Overview186Main functions186Buffer organization188Video decoding tasks192Video decoding195Resets202MPEG video decoder registers2032D blitter display engine2132D blitter display engine functions214                                              |

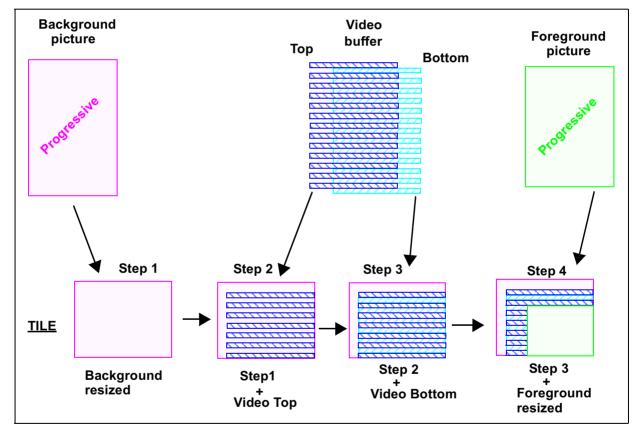

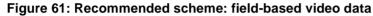

| 0        | 22.3<br>22.4<br>22.5<br>22.6<br>Chapter 23<br>Chapter 24<br>24.1<br>24.2         | Overview186Main functions186Buffer organization188Video decoding tasks192Video decoding195Resets202MPEG video decoder registers2032D blitter display engine2132D blitter display engine functions214Recommended scheme215                         |

| 0        | 22.3<br>22.4<br>22.5<br>22.6<br>Chapter 23<br>Chapter 24<br>24.1<br>24.2<br>24.3 | Overview186Main functions186Buffer organization188Video decoding tasks192Video decoding195Resets202MPEG video decoder registers2032D blitter display engine2132D blitter display engine functions214Recommended scheme215Types of source queue216 |

7939391A STMicroelectronics Confidential 5/543

|            | 24.7       | 2D resizing and filtering234            |

|------------|------------|-----------------------------------------|

|            | 24.8       | Blending operations                     |

|            | 01 ( 05    |                                         |

|            | Chapter 25 | 2D blitter display engine registers 246 |

|            | 25.1       | Linked list (node) registers            |

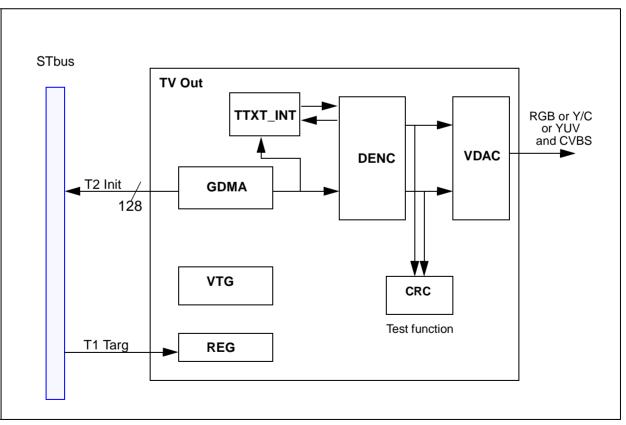

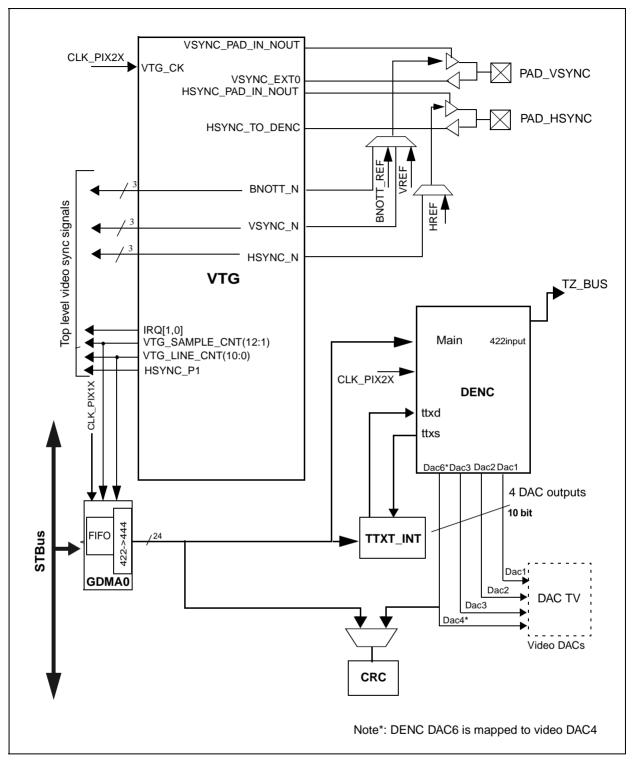

|            | Chapter 26 | TV out                                  |

|            | 26.1       | Overview                                |

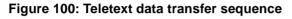

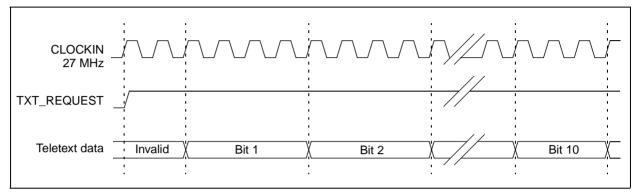

|            | 26.2       | Teletext                                |

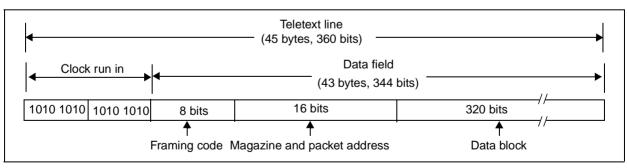

|            | 26.3       | Teletext packet format                  |

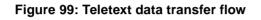

|            | 26.4       | Data transfer sequence                  |

|            | 26.5       | Interrupt control                       |

|            | Chapter 27 | TV out registers                        |

|            | Chapter 28 | Graphics DMA (GDMA)                     |

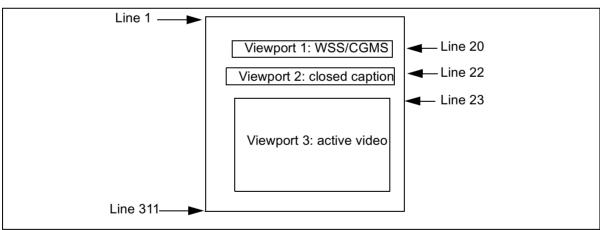

| <u>n</u>   | 28.1       | Overview                                |

| Ē          | 28.2       | Viewports                               |

| onfidentia | 28.3       | Output pixmap display                   |

| Ę          |            |                                         |

| Q          | Chapter 29 | Graphics DMA (GDMA) registers 288       |

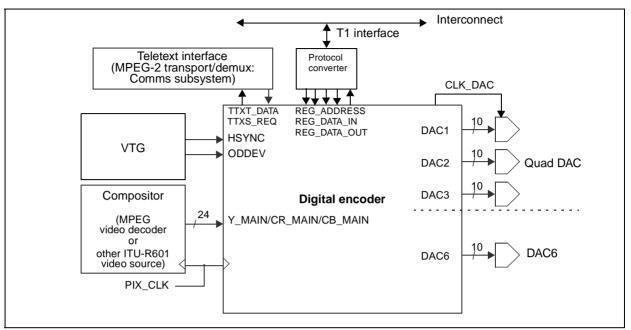

| O          | Chapter 30 | Digital encoder (DENC) 293              |

|            | 30.1       | Main features                           |

|            | 30.2       | Brief overview                          |

|            | 30.3       | Data input format                       |

|            | 30.4       | Video timing                            |

|            | 30.5       | Master Mode                             |

|            | 30.6       | Slave modes                             |

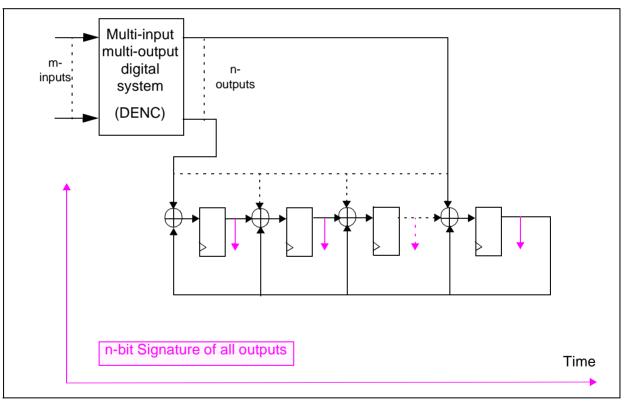

|            | 30.7       | Autotest mode                           |

|            | 30.8       | Input demultiplexor                     |

|            | 30.9       | Subcarrier generation                   |

|            | 30.10      | Burst insertion (PAL and NTSC)          |

|            | 30.11      | Subcarrier insertion (SECAM)            |

|            | 30.12      | Luminance encoding                      |

|            | 30.13      | Chrominance encoding                    |

57

|          | 30.14                                                                          | Composite video signal generation                                                                                                                                                                                                                                                                                                                                                             |

|----------|--------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | 30.15                                                                          | RGB and YPrPb (YUV) encoding                                                                                                                                                                                                                                                                                                                                                                  |

|          | 30.16                                                                          | Closed-captioning                                                                                                                                                                                                                                                                                                                                                                             |

|          | 30.17                                                                          | CGMS encoding                                                                                                                                                                                                                                                                                                                                                                                 |

|          | 30.18                                                                          | WSS encoding                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 30.19                                                                          | VPS encoding                                                                                                                                                                                                                                                                                                                                                                                  |

|          | 30.20                                                                          | Teletext encoding                                                                                                                                                                                                                                                                                                                                                                             |

|          | 30.21                                                                          | Macrovision copy protection process rev7.01/6.1                                                                                                                                                                                                                                                                                                                                               |

|          | 30.22                                                                          | CVBS, S-VHS(Y/C), RGB and UV outputs                                                                                                                                                                                                                                                                                                                                                          |

| C        | Chapter 31                                                                     | Digital encoder (DENC) registers                                                                                                                                                                                                                                                                                                                                                              |

| C        | Chapter 32                                                                     | Video timing generator (VTG)                                                                                                                                                                                                                                                                                                                                                                  |

|          | 32.1                                                                           | Signal generation                                                                                                                                                                                                                                                                                                                                                                             |

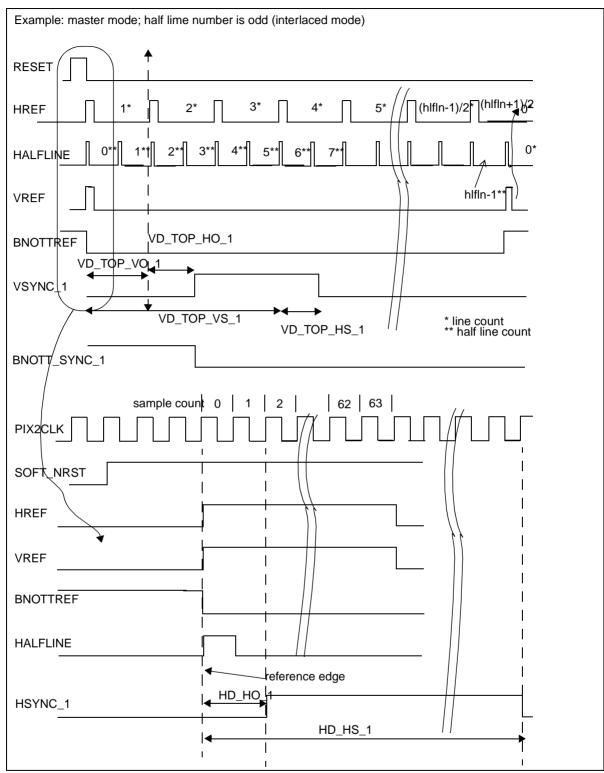

|          | 32.2                                                                           | Master mode                                                                                                                                                                                                                                                                                                                                                                                   |

| tia      | Chapter 33                                                                     | Video timing generator (VTG) registers                                                                                                                                                                                                                                                                                                                                                        |

|          |                                                                                |                                                                                                                                                                                                                                                                                                                                                                                               |

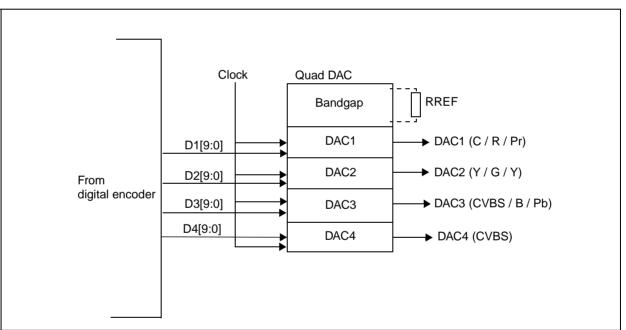

| den      | Chapter 34                                                                     | Quadruple video DAC                                                                                                                                                                                                                                                                                                                                                                           |

| ofiden   | <b>Chapter 34</b><br>34.1                                                      | Quadruple video DAC         365           Overview                                                                                                                                                                                                                                                                                                                                            |

| confiden | <b>Chapter 34</b><br>34.1<br>34.2                                              | •                                                                                                                                                                                                                                                                                                                                                                                             |

| Confiden | <b>Chapter 34</b><br>34.1<br>34.2<br>34.3                                      | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

| Confiden |                                                                                | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

| Confiden | 34.3                                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

| Confid   | 34.3<br>34.4                                                                   | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

| Confid   | 34.3<br>34.4<br>34.5                                                           | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

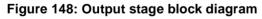

| Confid   | 34.3<br>34.4<br>34.5<br>Chapter 35                                             | Overview       .365         Input codes for video application       .366         Video output voltage level       .366         Video specifications and DAC set up       .367         Output stage adaptation and amplification       .367         Audio decoder       .369                                                                                                                   |

| Confid   | 34.3<br>34.4<br>34.5<br><b>Chapter 35</b><br>35.1                              | Overview                                                                                                                                                                                                                                                                                                                                                                                      |

| Confid   | 34.3<br>34.4<br>34.5<br>Chapter 35<br>35.1<br>Chapter 36                       | Overview.365Input codes for video application.366Video output voltage level.366Video specifications and DAC set up.367Output stage adaptation and amplification.367Audio decoder.369Overview.369Audio decoder registers.373                                                                                                                                                                   |

| Confid   | 34.3<br>34.4<br>34.5<br><b>Chapter 35</b><br>35.1<br><b>Chapter 36</b><br>36.1 | Overview       .365         Input codes for video application       .366         Video output voltage level       .366         Video specifications and DAC set up       .367         Output stage adaptation and amplification       .367         Audio decoder       .369         Overview       .369         Audio decoder registers       .373         Audio decoder registers       .373 |

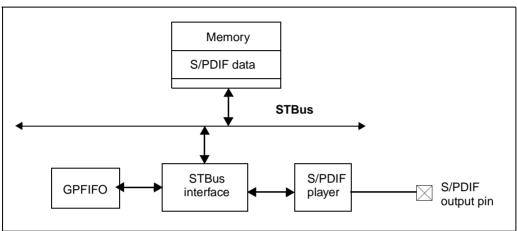

|            | Chapter 39 | S/PDIF player                                       | 3  |

|------------|------------|-----------------------------------------------------|----|

|            | 39.1       | Overview                                            | 3  |

|            | 39.2       | Audio data mode or encoded mode                     | Э  |

|            | 39.3       | Data                                                | 2  |

|            | 39.4       | Interrupts                                          | 3  |

|            | 39.5       | Soft reset                                          | 3  |

|            | Chapter 40 | S/PDIF player and GPFIFO registers                  | 1  |

|            | 40.1       | S/PDIF player registers                             | 5  |

|            | 40.2       | GPFIFO registers                                    | Э  |

|            | Chapter 41 | Audio DAC                                           | 3  |

|            | 41.1       | Description                                         | 3  |

|            | 41.2       | Input signals and output pins403                    | 3  |

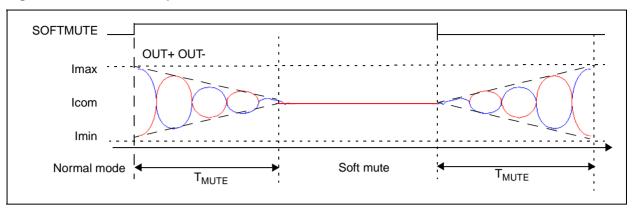

|            | 41.3       | Soft mute                                           | 4  |

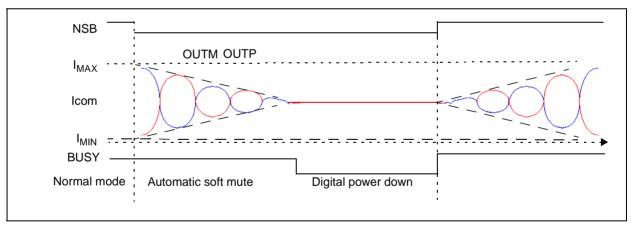

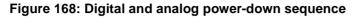

| ש          | 41.4       | Digital and analog power down405                    | 5  |

| ent.       | 41.5       | Output stage filtering                              | 6  |

| onfidentia | Chapter 42 | Flexible DMA (FDMA) 407                             | 7  |

| Ę          | 42.1       | Channel structures                                  | 3  |

| 0          | 42.2       | FDMA timing model                                   | Э  |

| U          | 42.3       | Operating the FDMA                                  | С  |

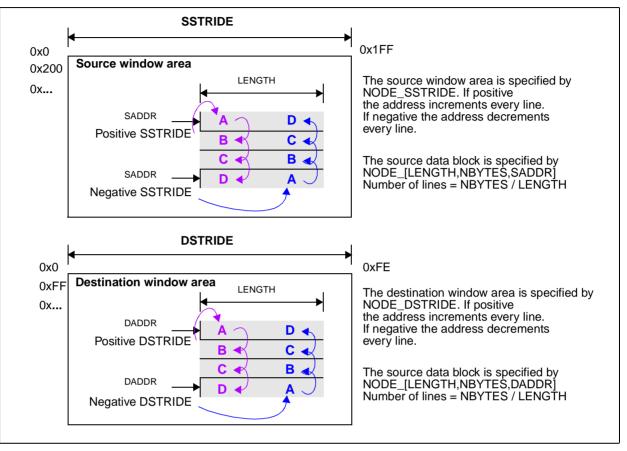

|            | 42.4       | Setting up FDMA transfers                           | 3  |

|            | Chapter 43 | Flexible DMA (FDMA) registers 420                   | )  |

|            | 43.1       | FDMA interface                                      | 3  |

|            | 43.2       | Channel interface                                   | 4  |

|            | 43.3       | Command mailbox                                     | 3  |

|            | 43.4       | Interrupt mailbox                                   | 9  |

|            | 43.5       | Memory-to-memory moves and paced transfer registers | 1  |

|            | 43.6       | S/PDIF registers                                    | 3  |

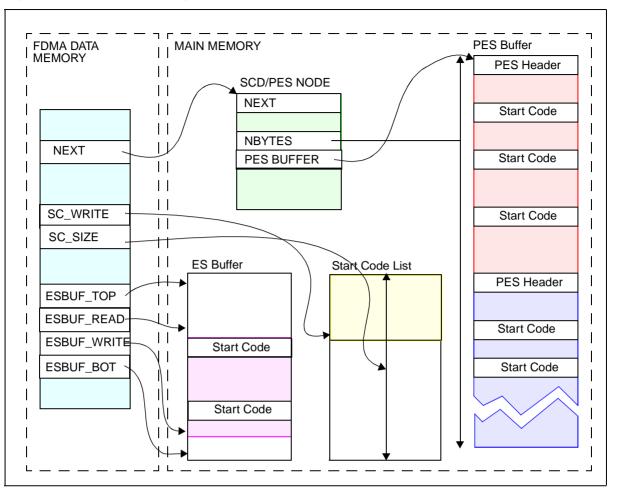

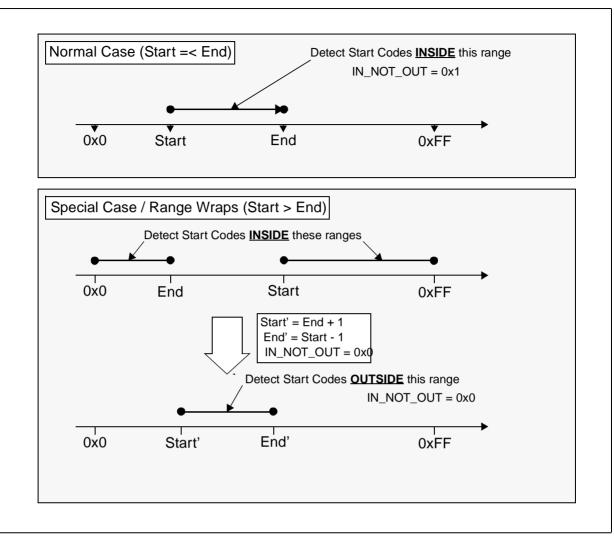

|            | 43.7       | SCD/PES parsing registers                           | 7  |

|            | Chapter 44 | Infrared transmitter/receiver 444                   | 1  |

|            | 44.1       | Overview                                            | 4  |

|            | 44.2       | Functional description                              | 5  |

|            | 8/543 ST   | Microelectronics Confidential 7939391A              | 5/ |

## STx5119

**A7/**

| C         | Chapter 45                                                                        | Infrared transmitter/receiver registers                                                                                                                                                                                                              | 9                                                |

|-----------|-----------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------|

|           | 45.1                                                                              | RC transmitter registers                                                                                                                                                                                                                             | 0                                                |

|           | 45.2                                                                              | RC receiver registers                                                                                                                                                                                                                                | 4                                                |

|           | 45.3                                                                              | RC and UHF receiver control45                                                                                                                                                                                                                        | 8                                                |

|           | 45.4                                                                              | Clock selection                                                                                                                                                                                                                                      | 9                                                |

|           | 45.5                                                                              | Noise suppression register                                                                                                                                                                                                                           | 0                                                |

|           | 45.6                                                                              | Reverse polarity registers                                                                                                                                                                                                                           | 0                                                |

| c         | Chapter 46                                                                        | Smartcard interface                                                                                                                                                                                                                                  | 1                                                |

|           | 46.1                                                                              | Overview                                                                                                                                                                                                                                             | 1                                                |

|           | 46.2                                                                              | External interface                                                                                                                                                                                                                                   | 2                                                |

|           | 46.3                                                                              | Smartcard clock generator                                                                                                                                                                                                                            | 2                                                |

|           | 46.4                                                                              | Smartcard removal                                                                                                                                                                                                                                    | 3                                                |

|           | 46.5                                                                              | Smartcard detection                                                                                                                                                                                                                                  | 3                                                |

| <u>a</u>  | Chapter 47                                                                        | Smartcard interface registers 464                                                                                                                                                                                                                    | 4                                                |

| 7         |                                                                                   |                                                                                                                                                                                                                                                      |                                                  |

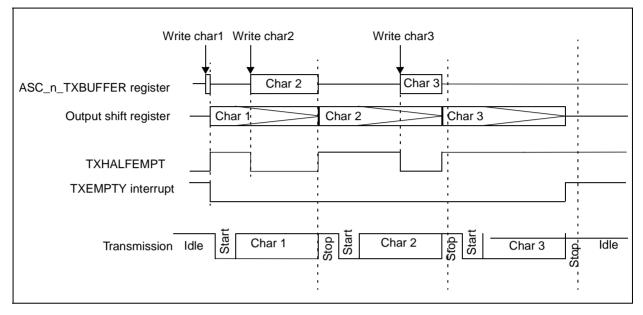

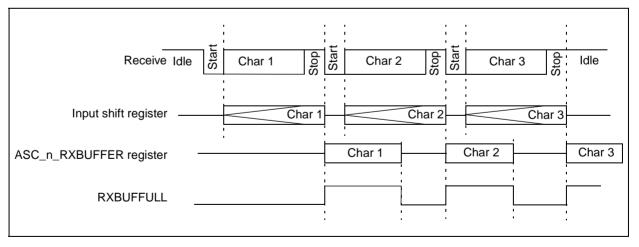

|           | Chapter 48                                                                        | Asynchronous serial controller (ASC) 46                                                                                                                                                                                                              | 5                                                |

|           | <b>Chapter 48</b><br>48.1                                                         | Asynchronous serial controller (ASC)                                                                                                                                                                                                                 |                                                  |

|           |                                                                                   |                                                                                                                                                                                                                                                      | 5                                                |

| Confident | 48.1                                                                              | Overview                                                                                                                                                                                                                                             | 5<br>5                                           |

|           | 48.1<br>48.2                                                                      | Overview                                                                                                                                                                                                                                             | 5<br>5<br>6                                      |

|           | 48.1<br>48.2<br>48.3                                                              | Overview                                                                                                                                                                                                                                             | 5<br>5<br>6<br>8                                 |

|           | 48.1<br>48.2<br>48.3<br>48.4                                                      | Overview                                                                                                                                                                                                                                             | 5<br>5<br>6<br>8<br>9                            |

|           | 48.1<br>48.2<br>48.3<br>48.4<br>48.5                                              | Overview         .46           Control         .46           Data frames         .46           Transmission         .46           Reception         .46                                                                                              | 5<br>5<br>6<br>8<br>9                            |

|           | 48.1<br>48.2<br>48.3<br>48.4<br>48.5<br>48.6                                      | Overview                                                                                                                                                                                                                                             | 5<br>5<br>6<br>9<br>1<br>3                       |

| Confid    | 48.1<br>48.2<br>48.3<br>48.4<br>48.5<br>48.6<br>48.7                              | Overview                                                                                                                                                                                                                                             | 5<br>6<br>8<br>9<br>1<br>3<br>6                  |

| Confid    | 48.1<br>48.2<br>48.3<br>48.4<br>48.5<br>48.6<br>48.7<br>48.8                      | Overview.46Control.46Data frames.46Transmission.46Reception.46Baudrate generation.47Interrupt control.47Smartcard operation.47                                                                                                                       | 5<br>5<br>6<br>8<br>9<br>1<br>3<br>6<br><b>8</b> |

| Confid    | 48.1<br>48.2<br>48.3<br>48.4<br>48.5<br>48.6<br>48.7<br>48.8<br><b>Chapter 49</b> | Overview.460Control.460Data frames.460Transmission.460Reception.460Baudrate generation.460Baudrate generation.470Interrupt control.470Smartcard operation.470Asynchronous serial controller (ASC) registers.470                                      | 5<br>5<br>8<br>9<br>1<br>3<br>6<br><b>8</b><br>7 |

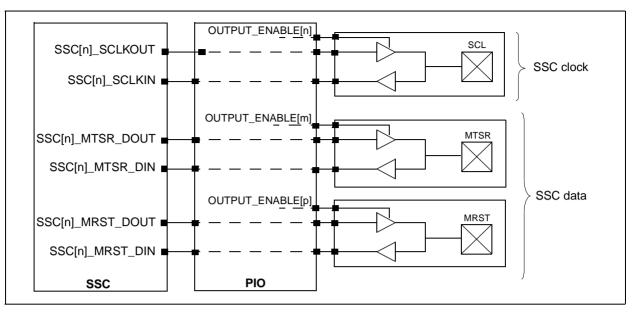

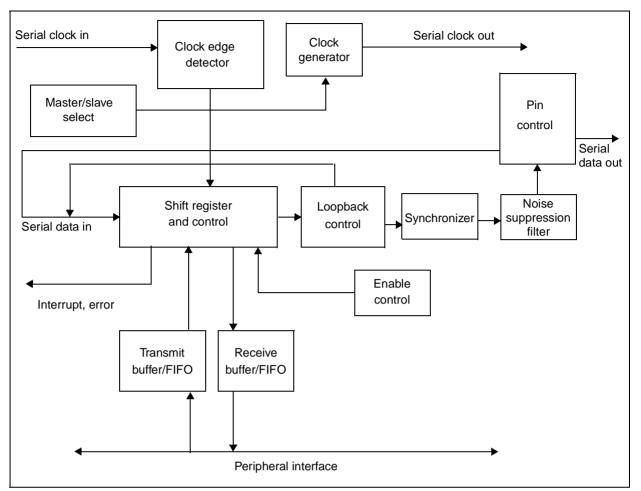

| Confid    | 48.1<br>48.2<br>48.3<br>48.4<br>48.5<br>48.6<br>48.7<br>48.8<br>Chapter 49        | Overview.460Control.460Data frames.460Transmission.460Reception.460Baudrate generation.460Interrupt control.470Interrupt control.470Smartcard operation.470Asynchronous serial controller (ASC) registers.470Synchronous serial controller (SSC).480 | 5<br>5<br>6<br>8<br>7<br>7                       |

|              | Chapter 51 | Synchronous serial controller (SSC) registers       |

|--------------|------------|-----------------------------------------------------|

|              | 51.1       | Control and configuration registers                 |

|              | 51.2       | SSC status and interrupt registers508               |

|              | 51.3       | I2C registers                                       |

|              | 51.4       | Buffer and FIFO registers                           |

|              | 51.5       | Noise suppression filter registers514               |

|              | 51.6       | Prescaler registers                                 |

|              | Chapter 52 | Programmable I/O port 516                           |

|              | 52.1       | Overview                                            |

|              | Chapter 53 | Programmable I/O port registers 517                 |

|              | Chapter 54 | Electrical specifications                           |

|              | 54.1       | Absolute maximum ratings                            |

| σ            | 54.2       | Operating conditions                                |

| onfidentia   | 54.3       | Standard pads DC specifications                     |

| Ð            | 54.4       | LMI pads DC/AC specifications for SDR-based systems |

| E            | 54.5       | Targeted power consumption525                       |

| <sup>i</sup> | 54.6       | Audio DAC specifications                            |

| Ö            | 54.7       | Video DAC parameters                                |

|              | Chapter 55 | Timing specification                                |

|              | 55.1       | System                                              |

|              | 55.2       | LMI (SDRAM) interface specifications529             |

|              | 55.3       | FMI                                                 |

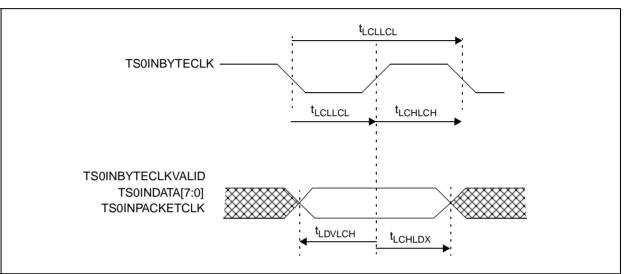

|              | 55.4       | Transport stream timings                            |

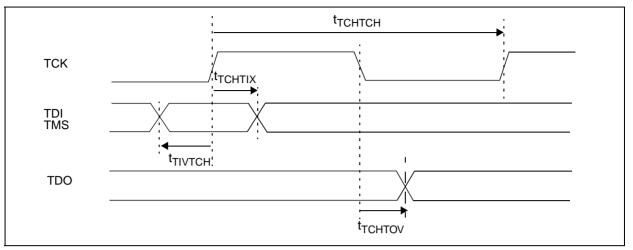

|              | 55.5       | TAP timings                                         |

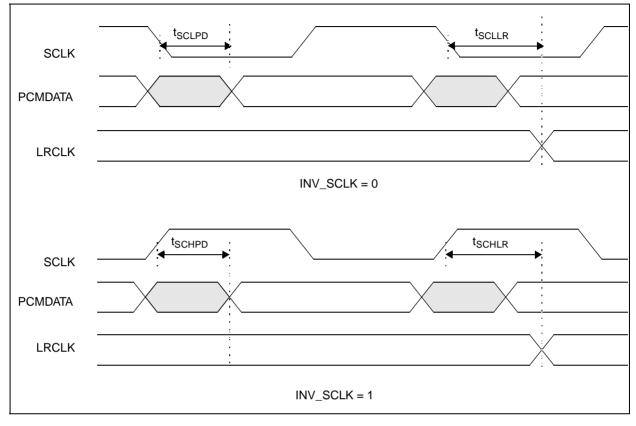

|              | 55.6       | Audio                                               |

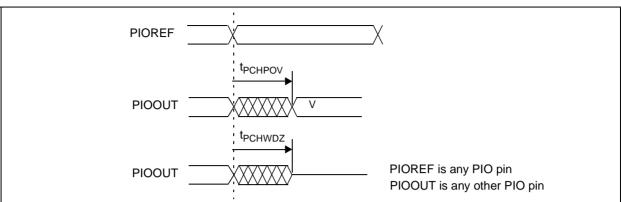

|              | 55.7       | General PIO                                         |

|              | 55.8       | Digital I/O                                         |

|              | 55.9       | General power supplies                              |

|              | Chapter 56 | Index of registers 543                              |

57

# **1** Applications

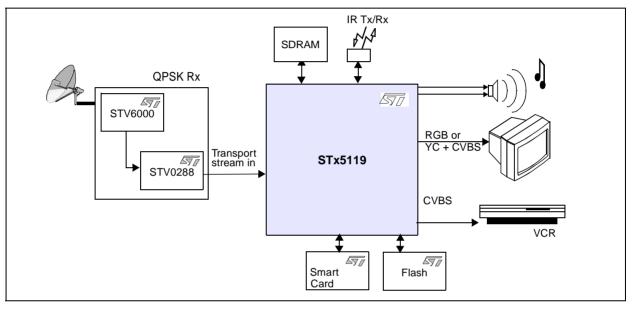

The STx5119 is the latest in the family of Omega2 set-top box ICs providing a high performance, low cost system on a chip for MPEG processing in cable, satellite or digital terrestrial STBs.

The STx5119 delivers enhanced performance with respect to previous generation devices. Main memory is based upon a single 16-bit external SDRAM.

The display architecture of the device is based on a high performance blitter engine which supports CLUT8 and RGB16 formats for video and OSD/graphics displays.

The STx5119 can be used for basic set-top boxes. A typical application is shown in Figure 1.

### Figure 1: Free to air satellite

# 2 Audio and video summary specification

### Table 1: Summary specification

| Video decoder                       |                                                                                                                                                                                                                                                                                      |  |

|-------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

| Feature                             | Description                                                                                                                                                                                                                                                                          |  |

| Video decode display                | Based on the Omega2, provides a memory to memory decode into YC 4:2:0 macroblock format, provides simple resizing based on x2 and x0.5.                                                                                                                                              |  |

| Bit streams accepted                | MPEG-1 video (ISO/IEC 11172-2), MPEG-2 video (ISO/IEC 13818-2)<br>MPEG-2 Packetized elementary stream (PES) format as defined by ISO/IEC 13818-1<br>MPEG-1 ISO/IEC 11172-1 packets                                                                                                   |  |

| MPEG-2 profiles/levels<br>supported | Main profile at main level (MP@ML), main profile at low level (MP@LL)<br>Simple profile at main level (SP@ML)                                                                                                                                                                        |  |

| Maximum picture size                | Width: 720 x 576 pixels = 45 x 36<br>Number of macroblocks: 45 x 36 = 1620                                                                                                                                                                                                           |  |

| Motion vector range                 | MPEG-1: -1024 to 1023 (full pel), -512 to 511.5 (half pel) horizontal and vertical MPEG-2: -1024 to 1023.5 horizontal and -128 to 127.5 vertical                                                                                                                                     |  |

| PTI compressed data input           | Serial peak input rate: 100 Mbit/s                                                                                                                                                                                                                                                   |  |

| SDRAM LMI interface                 | 16-bit wide SDRAM interface. Peak bandwidth 532 Mbyte/s (133 MHz).<br>Supports 64-Mbit, 64-Mbit, 64-Mbit, 128-Mbit, 256-Mbit, or 512-Mbit SDRAM. Fully<br>cacheable address space for data and instructions, with cacheability controlled in<br>512 Kbyte blocks for up to 8 Mbytes. |  |

| Start code detection                | Automatic detection of start codes (of picture layer and above) to enable the microcontroller to access header data<br>Counters provided for time-stamp tracking                                                                                                                     |  |

| Decoding pipeline                   | Instruction register sets up each picture and defines pipeline operation<br>Double-buffered quantization matrices enable loading of new tables concurrently with<br>decoding                                                                                                         |  |

| Error concealment                   | Automatic concealment of errors detected by VLD and decoding pipeline by macroblock copy                                                                                                                                                                                             |  |

### Table 1: Summary specification

| Display                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

|----------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Feature                    | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |

| Video clock                | 27 MHz nominal                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| Video output               | External pel clock<br>Horizontal/vertical synchronization provided by internal digital encoder or external<br>source<br>Interlaced output<br>3:2 pull-down operation supported<br>On-chip up-/down-sampling with anti-aliasing filter<br>Vertical chroma reconstruction or luma filtering up to 5-tap filter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| Pan and scan vectors       | Horizontal: maximum vector size: 2047 pels, resolution: 1/8 pel<br>Vertical: maximum vector size: 1022 lines, resolution: 1 line                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| On-screen display<br>(OSD) | Blitter-based composition<br>The OSD plane is managed as a set of horizontal bands with a specification<br>comprising configuration, bitmap and, for CLUT formats, palette information for each<br>region. The OSD operates in one of two modes, palette mode or true color mode.<br><b>Palette mode</b> : Each region can be independently specified with a resolution of 8 bpp.<br>Regions are frame based. Each region palette can support up to 256 colors with up to<br>24 bits resolution per color entry.<br><b>True color mode</b> : Each region can be independently specified with a 16 bpp resolution<br>in one of the following direct color formats: RGB565 and ARGB1555.<br>A vertical interfield, antiflicker filter is provided to reduce flicker on interlace displays. It<br>is available for both palette and true color modes. |

| Audio decoder              |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Bit streams accepted       | MPEG-1, layers I and II elementary streams                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| Performance                | ISO/IEC 11172-3 Layers I and II<br>All MPEG input bit rates supported with sampling rates of 32 kHz, 44.1 kHz and<br>48 kHz, free format at 32 kHz and 48 kHz sampling rates<br>Decodes in single channel, dual channel, stereo, or joint stereo modes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |

| Error concealment          | Automatic error concealment on CRC or synchronization error detection                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| General                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Support for A/V sync       | PTS/DTS extraction from MPEG packet layers with automatic association                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

# 3 Architecture features

## 3.1 Introduction

The STx5119 is a low-cost Omega2 MPEG device that delivers highly integrated features that provide an overall system cost reduction. The device implements a fully unified SDRAM based memory architecture and integrates the Omega2 video decoder cell together with a blitter engine and a multichannel DMA controller to provide enhanced performance for graphics and real-time stream transfers.

Transfer of data such as pixmaps, audio streams, stills and PES can be performed efficiently using the STx5119's DMA.

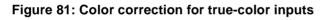

A true-color mode provides OSD graphics allowing the display of RGB16 formats: RGB565 and ARGB1555. This directly supports up to 65,536 colors in a region.

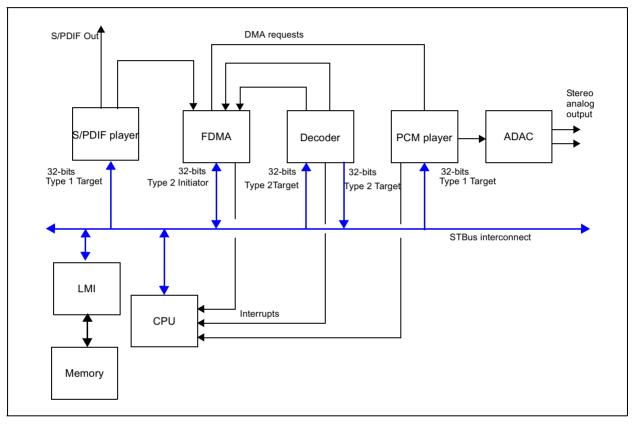

# 3.2 Omega2 (STBus) interconnect

The Omega2 multipath unified interconnect provides high on-chip bandwidth and low latency accesses between modules. The interconnect operates hierarchically, with latency-critical modules placed at the top level. The multipath router allows simultaneous access paths between modules, and simultaneous read and write phases from different transactions to and from the modules. Split transactions maximize the use of the available bandwidth.

## 3 Processor core

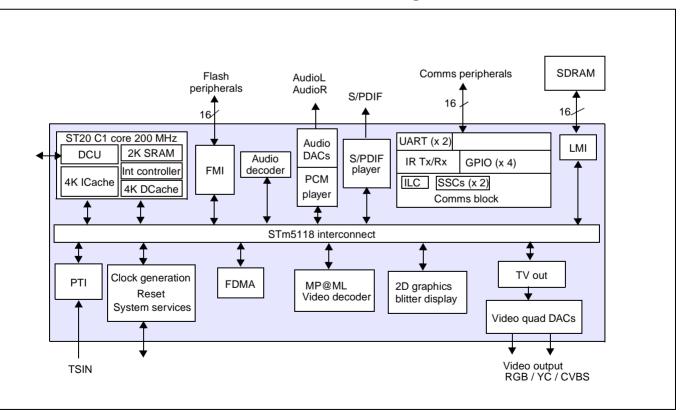

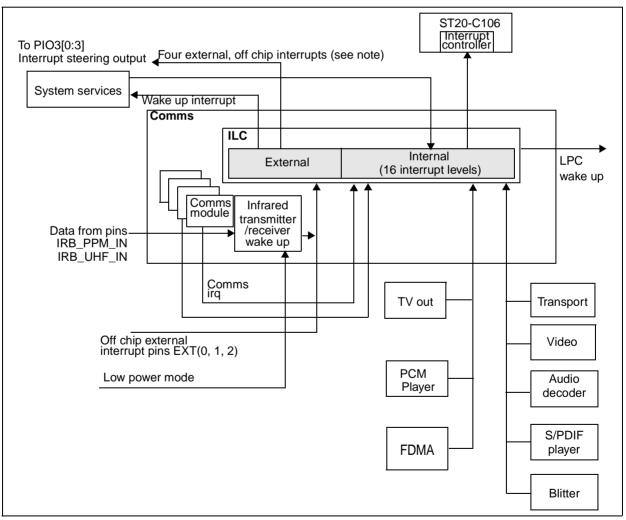

The ST20-C106 processor core is composed of the ST20C1+ CPU running at 200 MHz, a diagnostic controller unit (for low intrusion, real-time debugging), memory (4 Kbyte instruction cache, 4 Kbyte data cache and 2 Kbyte SRAM) and a 16 priority-level interrupt controller.

## Memory subsystem

The STx5119 has a memory interface and a peripheral/flash interface.

The STx5119's local memory interface is used for all data requirements in unified memory applications including graphics, video and audio buffers. It provides 16-bit wide SDRAM support at up to 166 MHz.

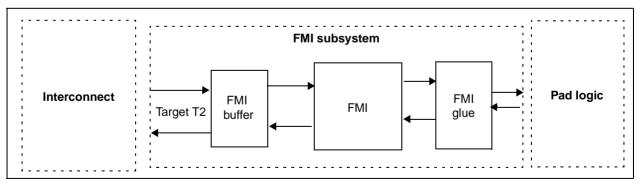

The FMI provides support for 16-bit wide peripherals, flash and synchronous flash.

Instructions can execute in place from flash/SFlash<sup>™</sup> on the FMI or can be copied to SDRAM on the LMI. The following sections provide an overview of the different memory interfaces.

## Local memory interface (LMI)

The LMI is a 16-bit wide SDRAM interface operating at up to 166 MHz. It supports 64-Mbit or 128-Mbit SDRAM. The LMI provides a fully cacheable address space for data and instructions, with data cacheability controlled in 512 Kbyte blocks for up to 8 Mbytes.

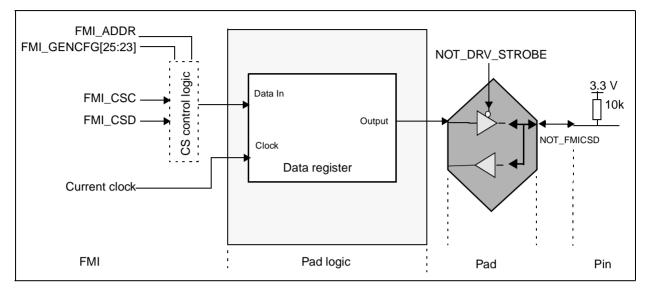

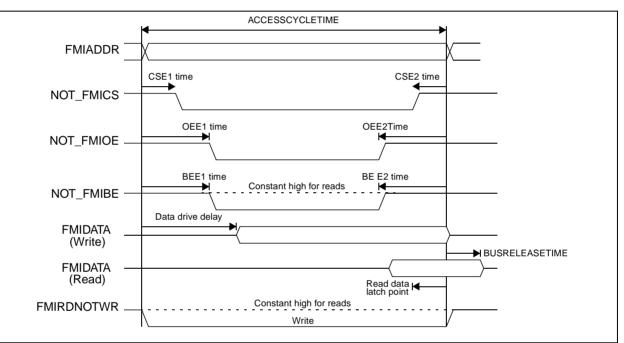

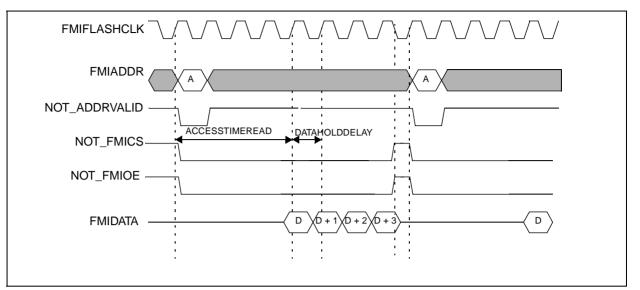

## Flash memory interface (FMI)

The FMI provides a glueless interface to SRAM, flash, SFlash and peripherals, in up to four configurable banks over a 16-bit wide interface. Bus cycle strobe timings can be programmed from 0 to 15 phases for slower peripherals. Support is provided for control of DVB-CI.

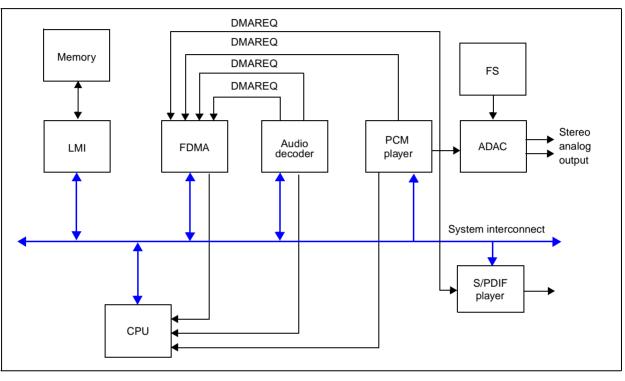

# 3.5 Transport stream processing

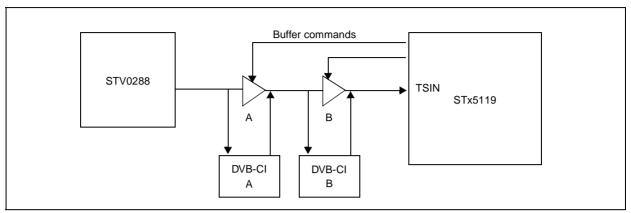

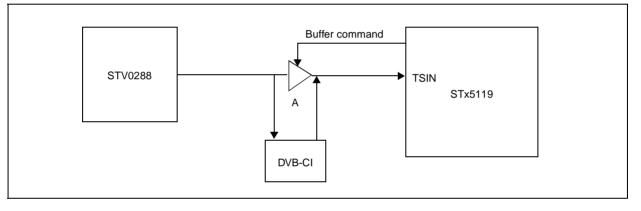

The STx5119 supports single transport stream input. It is possible to support DVB-CI configurations as shown in Figure 2 and Figure 3.

## Figure 2: Dual DVB-CI support

## Figure 3: Single DVB-CI support

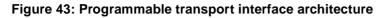

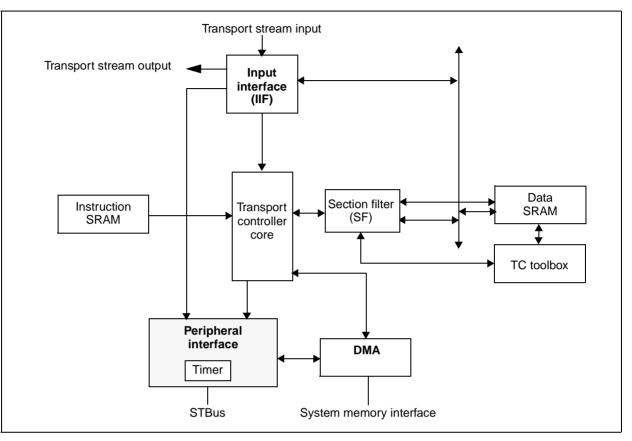

## Programmable transport interface (PTI)

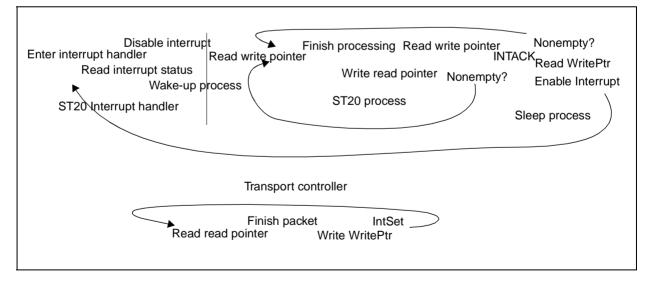

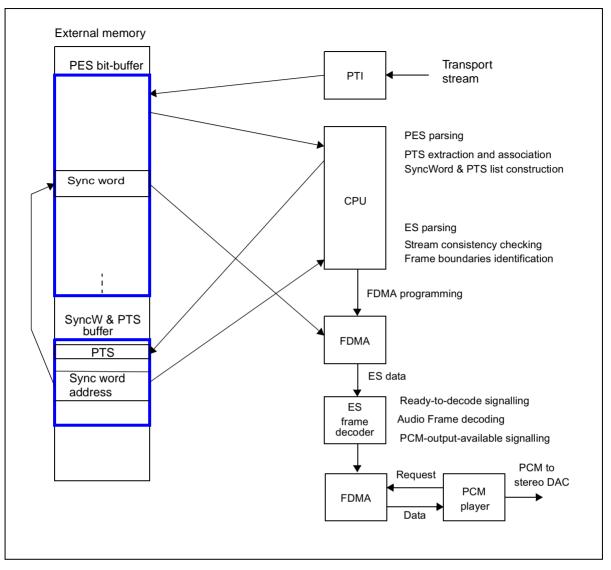

The PTI performs transport-stream descrambling, demultiplexing and data filtering. PES data is transferred by DMA to audio and video decoders via circular buffers. Section data is transferred by DMA to separate buffers for further processing by the CPU.

DVB transport streams can be handled by the PTI with data rates up to 100 Mbit/s.

The PTI performs PID filtering to select audio, video and data packets to be processed. 48 PID slots can be supported by the PTI.

The PTI cipher descrambles DVB-CSA streams.

The PTI has a section filter core that filters DVB standard sections using 32 x 8-byte filters.

# 3.6 MPEG graphics and display processing

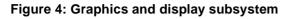

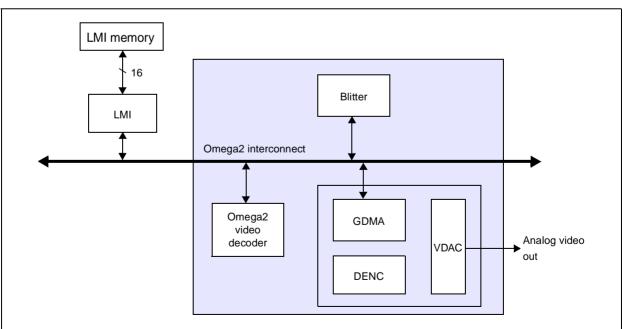

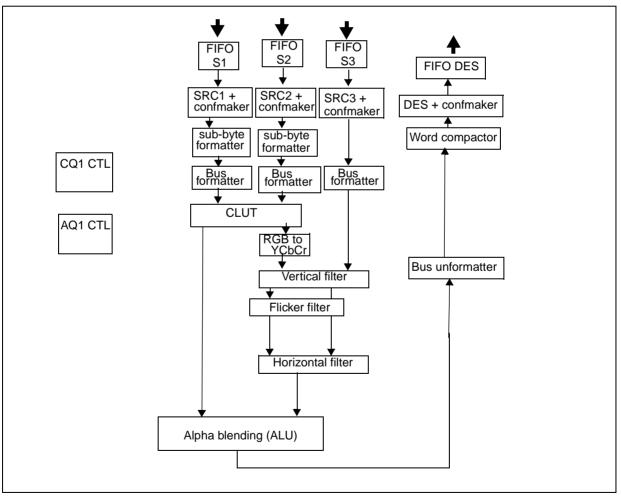

The MPEG graphics and display architecture shown in Figure 4 provides the graphics, videostream processing and display capabilities of the STx5119.

## Video decode

The video decoder is based on the Omega2 cell and provides a memory to memory decode into YC 4:2:0 macroblock format. It is also able to provide simple resizing based on x2 and x0.5.

# Graphics and display

## Display

The STx5119 uses a blitter based display architecture, providing improved graphics and increased flexibility for building applications as illustrated in Figure 5

The following features are supported:

- SMART GUI,

- Picture in Graphic,

- mosaic channels presentation.

The composition is assisted by the 2D graphic hardware accelerator.

#### Figure 5: Supported applications

| Start: 21:30 - 26Jan05       Start: 21:30 - 26Jan05         End: 22:00 - 26Jan05       Start: | End: 22:00 - 26JanO5<br>26JanO5 20:30 21:00 21:30 22:00 22:30<br>1. Digital 5 Charmed VI News 5 Ton The Amazing Race VI<br>2. Digital 8 Trivia Trov My Lucky Charm News 8 At The Prou-> | Title: New<br>Channel: 1. |           | t                            |             | En la compañía de la compañía |               |

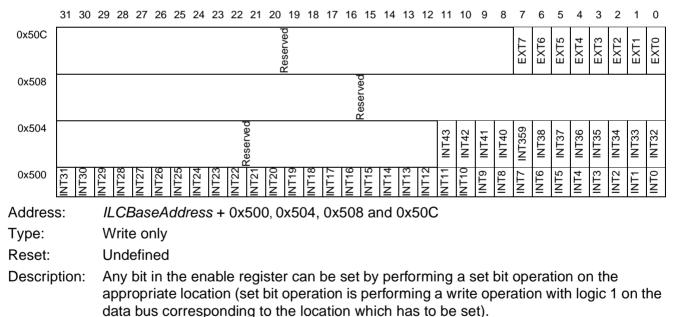

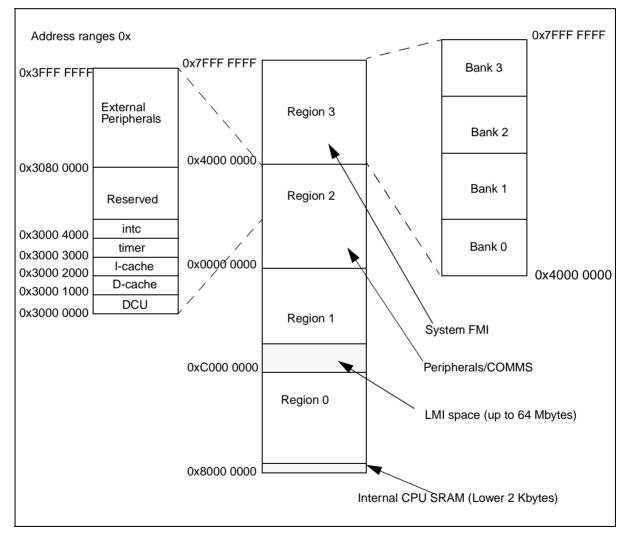

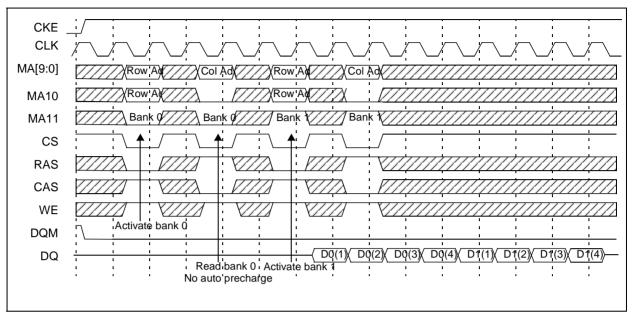

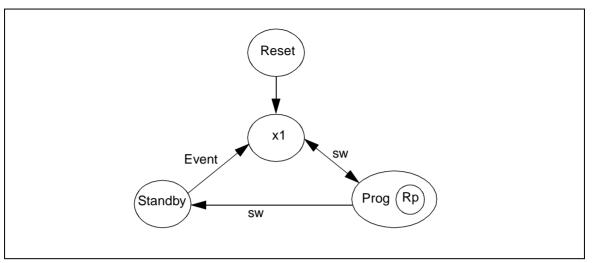

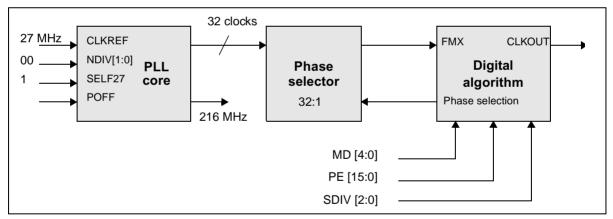

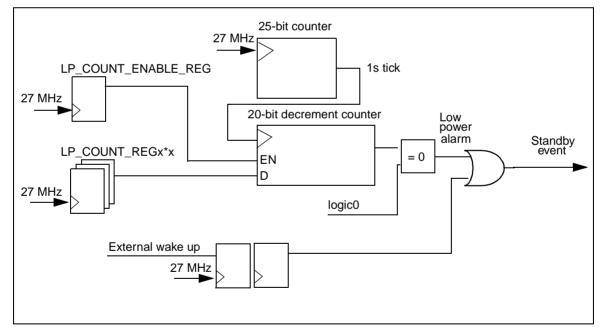

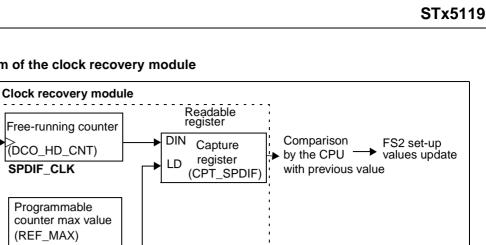

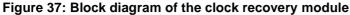

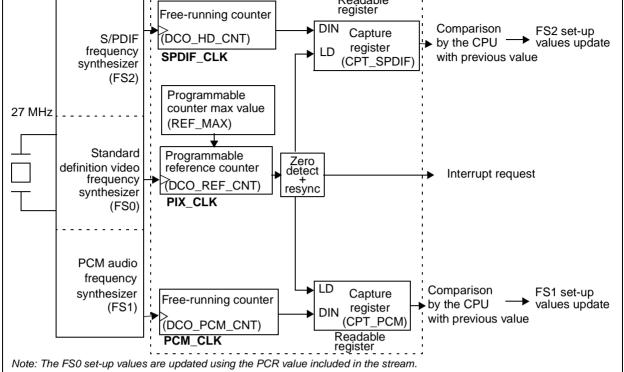

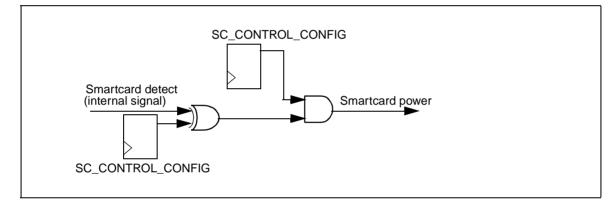

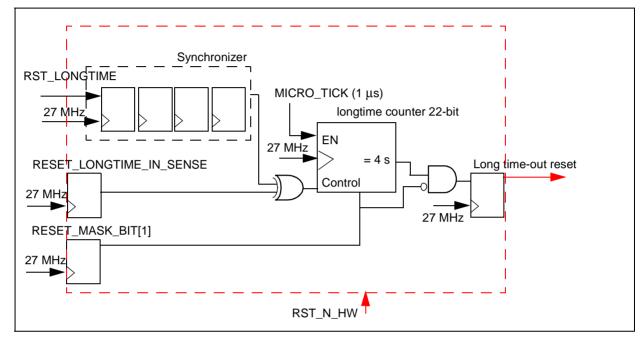

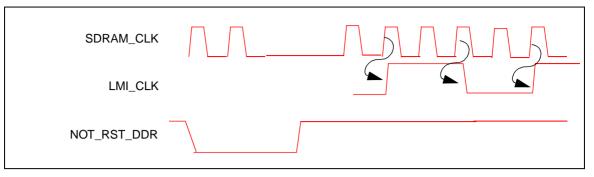

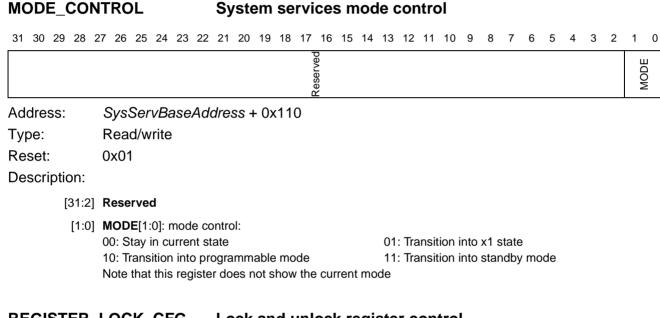

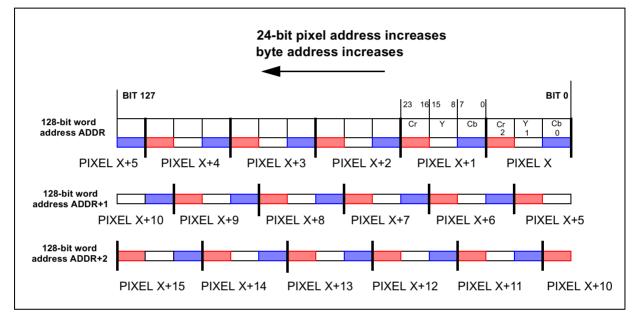

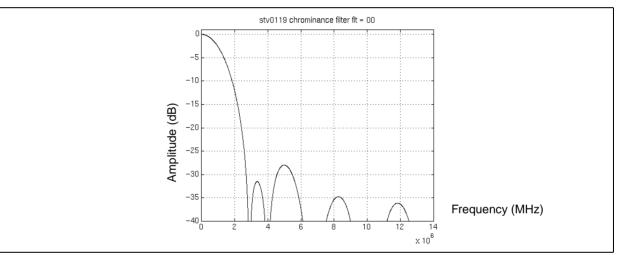

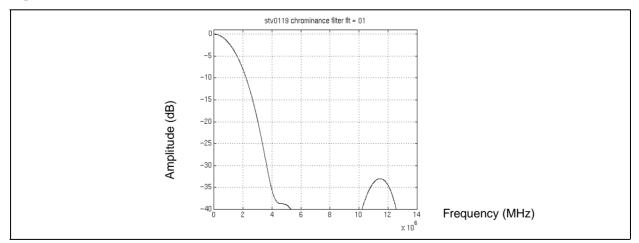

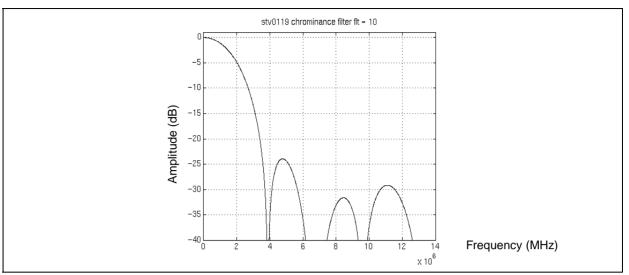

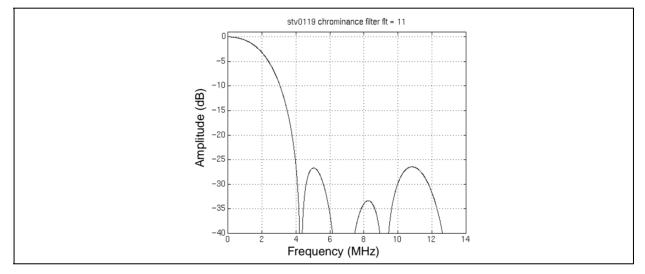

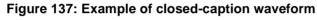

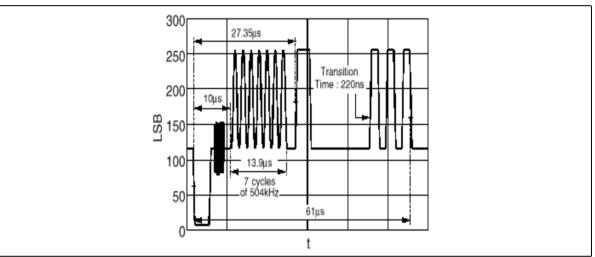

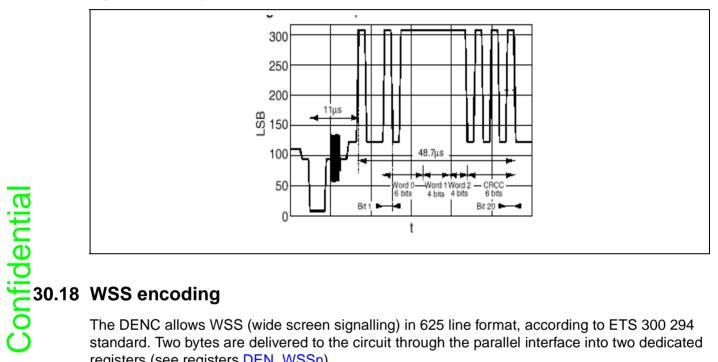

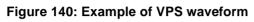

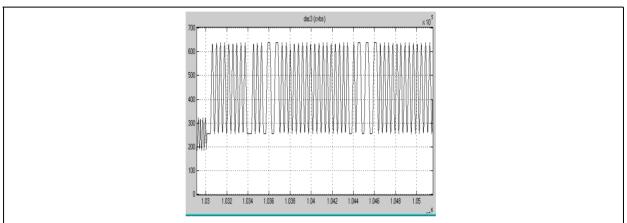

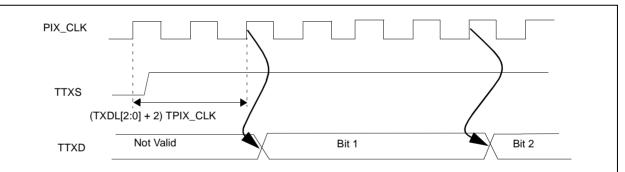

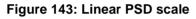

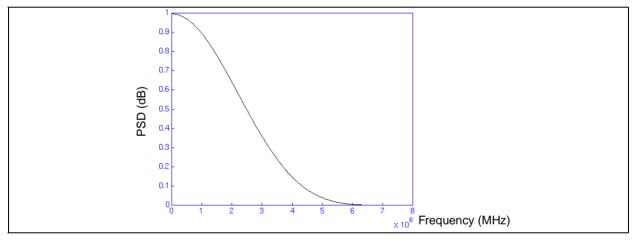

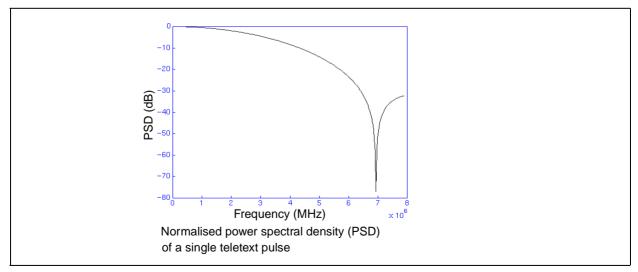

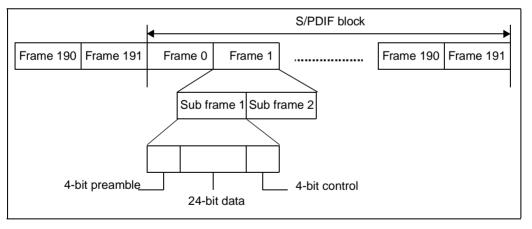

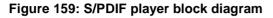

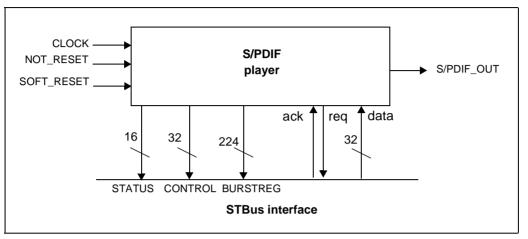

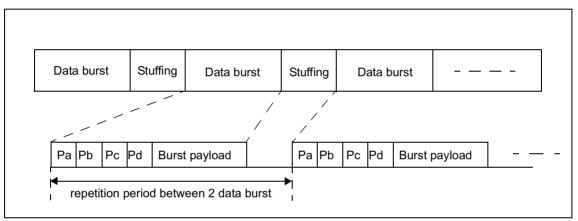

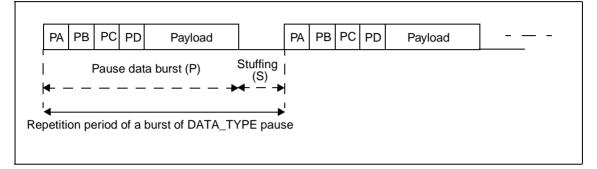

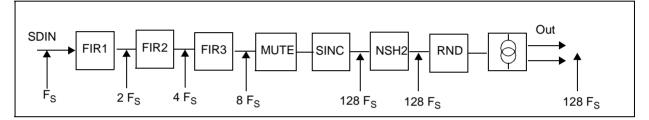

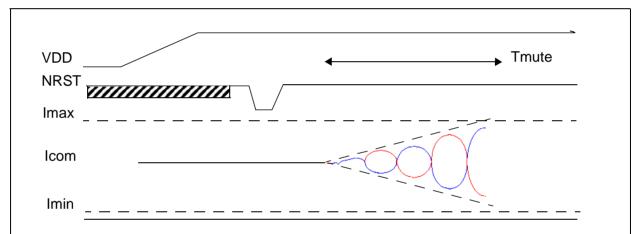

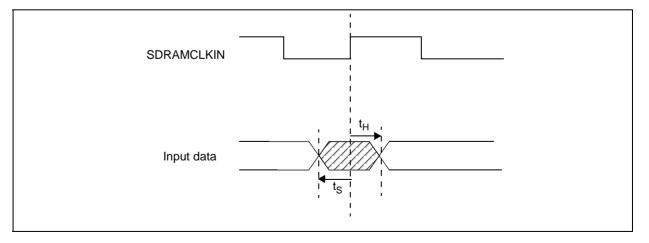

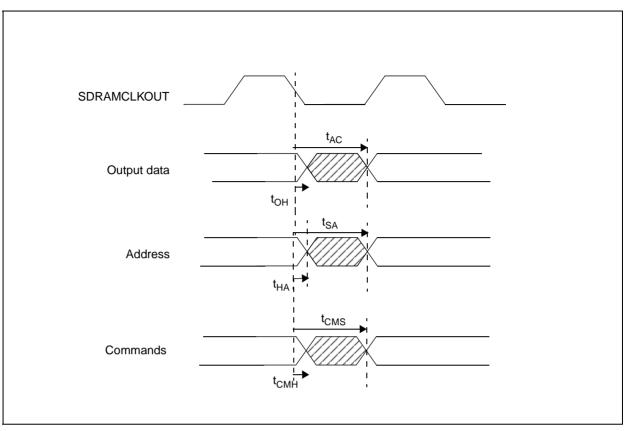

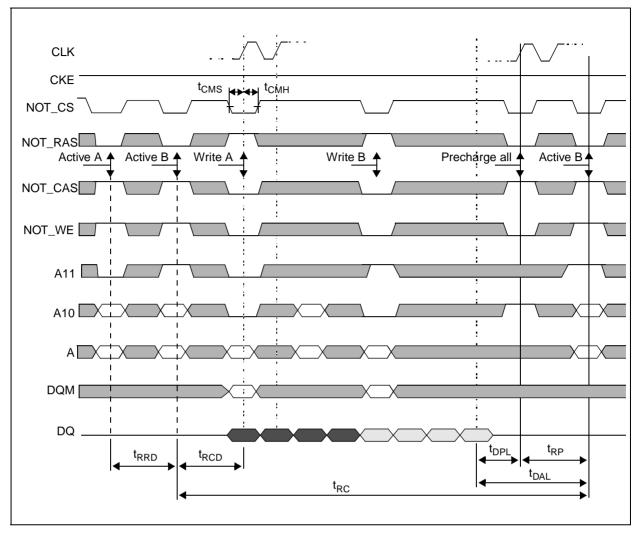

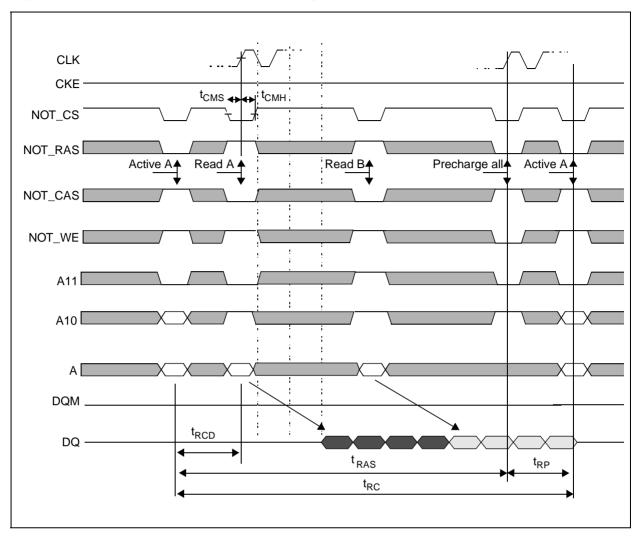

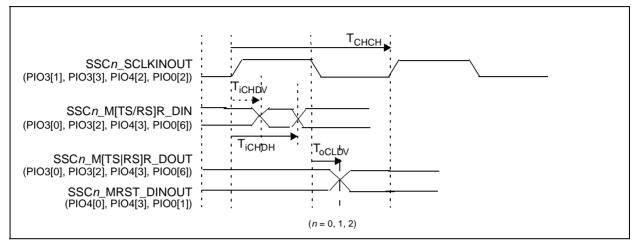

|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------|-----------|------------------------------|-------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|