### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### **GENERAL DESCRIPTION**

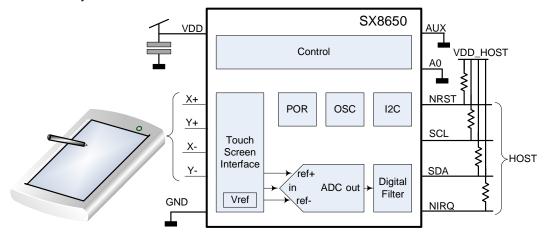

The SX8650 is an ultra low power 4-wire resistive touchscreen controller optimized for portable equipment where power and board-space are at a premium.

It incorporates a highly accurate 12-bit ADC for data conversion and operates from a single 1.65 to 3.7V supply voltage.

The SX8650 features a built-in preprocessing algorithm for data measurements, which greatly reduces the host processing overhead and bus activity. This complete touchscreen solution includes four user-selectable operation modes which offer programmability on different configurations such as conversion rate and settling time, thus enable optimization in throughput and power consumption for a wide range of touch sensing applications.

The touch screen inputs have been specially designed to provide robust on-chip ESD protection of up to ±15kV in both HBM and Contact Discharge, and eliminates the need for external protection devices.

The SX8650 supports the Fast-mode I<sup>2</sup>C (400kbit/s) serial bus data protocol and includes 2 user-selectable slave addresses. A custom I<sup>2</sup>C address is possible on request.

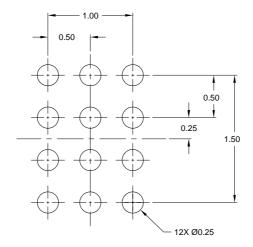

The SX8650 is offered in two tiny packages: 3.0 mm x 3.0 mm DFN and a 1.5 mm x 2.0 mm wafer-level chip-scale package (WLCSP).

#### **APPLICATIONS**

- Portable Equipment

- Mobile Communication Devices

- ◆ Cell phone, PDA, MP3, GPS, DSC

- Touch Screen Monitors

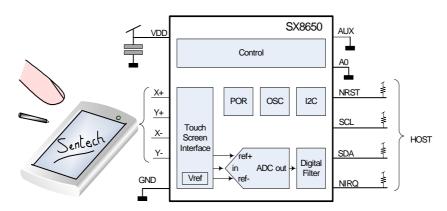

### **Block Diagram**

### **KEY PRODUCT FEATURES**

- Extremely Low Power Consumption: 23uA@1.8V 8kSPS

- Superior On-chip ESD Protection

- ⇒±15kV HBM (X+,X-,Y+,Y-)

- ⇒±2kV CDM

- ⇒±25kV Air Gap Discharge

- ⇒±15kV Contact Discharge

- ⇒±300V MM

- ◆ Single 1.65V to 3.7V Supply/Reference

- Integrated Preprocessing Block to Reduce Host Loading and Bus Activity

- Four User Programmable Operation Modes provides Flexibility to address Different Application Needs

⇒Manual, Automatic, Pen Detect, Pen Trigger

- High Precision 12-bit Resolution

- Low Noise Ratiometric Conversion

- Selectable Polling or Interrupt Modes

- ◆ Touch Pressure Measurement

- ◆ 400kHz Fast-Mode I<sup>2</sup>C Interface

- ◆ Hardware Reset & I<sup>2</sup>C Software Reset

- ◆ -40℃ to 85℃ Operation

- ◆ 12-LD (3.0 mm x 3.0 mm) DFN Package

- ◆ 12-Ball (1.5 mm x 2.0 mm) WLCSP Package

- Pin-compatible with SX8651

- ◆ Pb-Free, Halogen Free, RoHS/WEEE compliant product

- Windows CE 6.0, Linux Driver Support Available

#### **ORDERING INFORMATION**

| Part Number               | Package                           |

|---------------------------|-----------------------------------|

| SX8650ICSTRT <sup>1</sup> | 12 - Ball WLCSP (1.5 mm x 2.0 mm) |

| SX8650IWLTRT <sup>1</sup> | 12 - Lead DFN (3.0 mm x 3.0 mm)   |

1. 3000 Units / reel

### **ADVANCED COMMUNICATIONS & SENSING**

### DATASHEET

### Table of contents

| Se | Section                                                                         | Page |

|----|---------------------------------------------------------------------------------|------|

| 1. | Conoral Description                                                             | 4    |

| ١. | General Description  1.1. DFN Pinout Diagram and Marking Information (Top View) |      |

|    |                                                                                 |      |

|    | 3                                                                               |      |

|    | 1.3. Pin Description                                                            |      |

| _  | 1.4. Simplified Block Diagram                                                   |      |

| 2. | 2. Electrical Characteristics                                                   |      |

|    | 2.1. Recommended Operating Conditions                                           |      |

|    | 2.2. Thermal Characteristics                                                    |      |

|    | 2.3. Electrical Specifications                                                  |      |

|    | 2.4. Host Interface Specifications                                              |      |

|    | 2.5. Host Interface Timing Waveforms                                            |      |

|    | 2.6. Typical Operating Characteristics                                          | 11   |

| 3. | B. Functional Description                                                       |      |

|    | 3.1. General Introduction                                                       | 13   |

|    | 3.2. Channel Pins                                                               | 13   |

|    | 3.2.1. X+, X-, Y+. Y                                                            | 13   |

|    | 3.2.2. AUX                                                                      | 13   |

|    | 3.3. Host Interface and Control Pins                                            | 14   |

|    | 3.3.1. NIRQ                                                                     | 14   |

|    | 3.3.2. SCL                                                                      | 14   |

|    | 3.3.3. SDA                                                                      | 14   |

|    | 3.3.4. A0                                                                       | 15   |

|    | 3.3.5. NRST                                                                     | 15   |

|    | 3.4. Power Management Pins                                                      | 15   |

|    | 3.4.1. VDD                                                                      | 15   |

|    | 3.4.2. GND                                                                      | 15   |

| 4. |                                                                                 |      |

|    | 4.1. Touch Screen Operation                                                     |      |

|    | 4.2. Coordinates Measurement                                                    |      |

|    | 4.3. Pressure Measurement                                                       |      |

|    | 4.4. Pen Detection                                                              |      |

| 5. |                                                                                 |      |

| ٠. | 5.1. Host Interface and Control                                                 |      |

|    | 5.1.1. I2C Address                                                              |      |

|    | 5.1.2. I2C Write Registers                                                      |      |

|    | 5.1.3. I2C Read Registers                                                       |      |

|    | 5.1.4. I2C Host Commands                                                        |      |

|    | 5.1.5. I2C Read Channels                                                        |      |

|    | 5.1.6. Data Channel Format                                                      |      |

|    | J. I.O. Dala Chainei Millat                                                     |      |

### **ADVANCED COMMUNICATIONS & SENSING**

### DATASHEET

### Table of contents

| Section | n        |                          | Page |

|---------|----------|--------------------------|------|

|         | 5.1.7.   | Invalid Qualified Data   | 23   |

| 5.2     |          | C Register Map           |      |

| 5.3     |          | est Control Writing      |      |

| 5.4     |          | ost Commands             |      |

| 5.5     |          | wer-Up                   |      |

| 5.6     |          | eset                     |      |

|         |          | of Operation             |      |

| 6.1     |          | anual Mode               |      |

| 6.2     |          | itomatic mode            |      |

| 6.3     |          | NDET Mode                |      |

| 6.4     |          | NTRIG Mode               |      |

| 7. A    |          | tion Information         |      |

| 7.1     | <br>. Ас | quisition Setup          | 31   |

| 7.2     | . Ch     | nannel Selection         | 31   |

| 7.3     | . No     | sise Reduction           | 31   |

|         | 7.3.1.   | POWDLY                   | 31   |

|         | 7.3.2.   | SETDLY                   | 32   |

|         | 7.3.3.   | AUX Input                | 32   |

| 7.4     | . Inte   | errupt Generation        |      |

| 7.5     | . Co     | ordinate Throughput Rate |      |

|         | 7.5.1.   | I2C Communication Time   |      |

|         | 7.5.2.   | Conversion Time          |      |

|         | 7.5.3.   | AUTO MODE                |      |

| 7.6     | . ES     | SD event                 |      |

| 7.7     | . Ар     | plication Schematic      |      |

| 7.8     |          | plication Examples       |      |

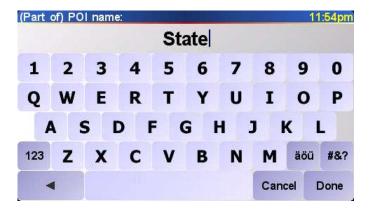

|         | 7.8.1.   | Soft Keyboard            |      |

|         | 7.8.2.   | Slider Controls          |      |

|         | 7.8.3.   | Game                     | 35   |

|         | 7.8.4.   | Handwriting Application  | 35   |

| 8. F    | •        | ing Information          |      |

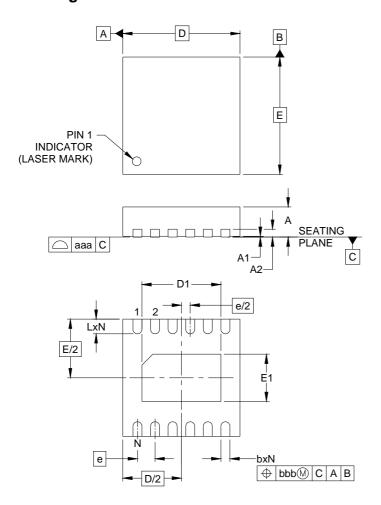

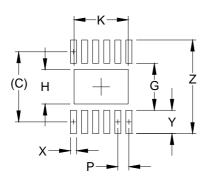

| 8.1     |          | N Package                |      |

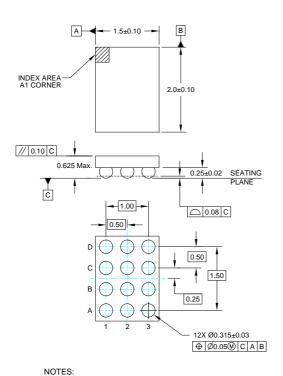

| 8.2     | . WL     | LCSP Package             | 38   |

### **ADVANCED COMMUNICATIONS & SENSING**

**DATASHEET**

### 1. General Description

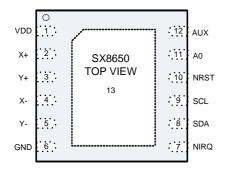

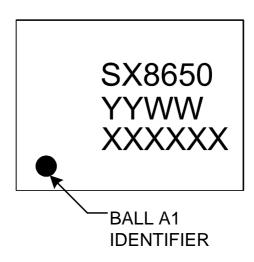

#### 1.1. DFN Pinout Diagram and Marking Information (Top View)

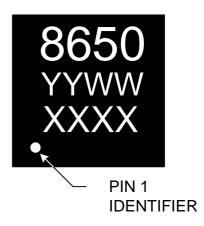

Figure 1. SX8650SX8650 DFN Top View, Pad on Bottom Side

YYWW : date code XXXXX: Lot Number

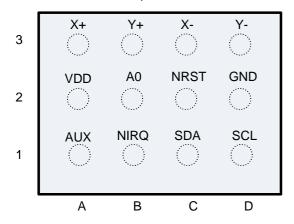

### 1.2. WLCSP Pinout Diagram and Marking Information (Top View)

#### SX8650 TOP VIEW

solder bumps on bottom side

Figure 2. SX8650 WLCSP Top View, Solder Bumps on Bottom Side

YYWW : date code XXXXX: Lot Number

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 1.3. Pin Description

| Pin Nu | Pin Number # |      | Pin Number # Name                  |                                                              | n Number # Name Type |  | Туре | Description |

|--------|--------------|------|------------------------------------|--------------------------------------------------------------|----------------------|--|------|-------------|

| DFN    | WLCSP        |      |                                    |                                                              |                      |  |      |             |

| 1      | A2           | VDD  | Power                              | Input power supply connect to a 0.1uF capacitor to GND       |                      |  |      |             |

| 2      | A3           | X+   | Analog                             | X+ channel input                                             |                      |  |      |             |

| 3      | В3           | Y+   | Analog                             | Y+ channel input                                             |                      |  |      |             |

| 4      | C3           | X-   | Analog                             | X- channel input                                             |                      |  |      |             |

| 5      | D3           | Y-   | Analog                             | Y- channel input                                             |                      |  |      |             |

| 6      | D2           | GND  | Ground                             | Ground                                                       |                      |  |      |             |

| 7      | B1           | NIRQ | Digital Output / Open Drain Output | Interrupt output, active low. Need external pull-up resistor |                      |  |      |             |

| 8      | C1           | SDA  | Digital Input / Open Drain Output  | I2C data input/output                                        |                      |  |      |             |

| 9      | D1           | SCL  | Digital Input / Open Drain Output  | I2C clock, input/output                                      |                      |  |      |             |

| 10     | C2           | NRST | Digital Input / Output             | Reset Input, active low. Need external 50k pull-up resistor  |                      |  |      |             |

| 11     | B2           | A0   | Digital Input                      | I2C slave address selection input                            |                      |  |      |             |

| 12     | A1           | AUX  | Digital Input/Analog Input         | Analog auxiliary input or conversion synchronization         |                      |  |      |             |

| 13     |              | GND  | Ground                             | Die attach paddle, connect to Ground                         |                      |  |      |             |

Table 1 Pin description

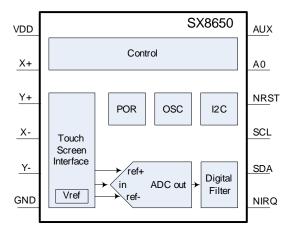

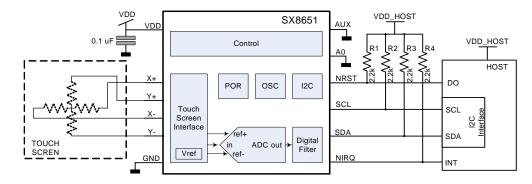

### 1.4. Simplified Block Diagram

The SX8650 simplified block diagram is shown in Figure 3.

Figure 3. Simplified block diagram of the SX8650

### **ADVANCED COMMUNICATIONS & SENSING**

**DATASHEET**

#### 2. Electrical Characteristics

Stresses above the values listed in "Absolute Maximum Ratings" may cause permanent damage to the device.

This is a stress rating only and functional operation of the device at these, or any other conditions beyond the "Recommended Operating Conditions", is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

| Parameter                                                                   |                             | Symbol                 | Min.                | Max. | Unit |

|-----------------------------------------------------------------------------|-----------------------------|------------------------|---------------------|------|------|

| Supply Voltage                                                              |                             | V <sub>DDABS</sub>     | -0.5                | 3.9  | V    |

| Input voltage (non-supply pins)                                             |                             | V <sub>IN</sub>        | -0.5                | 3.9  | V    |

| Input current (non-supply pins)                                             |                             | I <sub>IN</sub>        |                     | 10   | mA   |

| Operating Junction Temperature                                              | е                           | T <sub>JCT</sub>       |                     | 125  | .C   |

| Reflow temperature                                                          | T <sub>RE</sub>             |                        | 260                 | .C   |      |

| Storage temperature                                                         |                             | T <sub>STOR</sub>      | -50                 | 150  | .C   |

|                                                                             | High ECD piper V. V. V. V   | ESD <sub>HBM1</sub>    | ± 15 <sup>(i)</sup> |      | kV   |

| ESD HBM                                                                     | High ESD pins: X+, X-,Y+,Y- | LODHBM1                | ± 8 <sup>(ii)</sup> |      | kV   |

| (Human Body Model)  All pins except high ESD pins: AUX,A0,NRST,NIRQ,SDA,SCI |                             | ESD <sub>HBM2</sub>    | ± 2                 |      | kV   |

| ESD (Contact Discharge) High ESD pins: X+, X-,Y+,Y-                         |                             | ESD <sub>CD</sub>      | ± 15                |      | kV   |

| Latchup                                                                     | I <sub>LU</sub>             | ± 100 <sup>(iii)</sup> |                     | mA   |      |

Table 2. Absolute Maximum Ratings

- (i) Tested to TLP (10A)

- (ii) Tested to JEDEC standard JESD22-A114

- (iii) Tested to JEDEC standard JESD78

#### 2.1. Recommended Operating Conditions

| Parameter                 | Symbol          | Min.  | Max | Unit |

|---------------------------|-----------------|-------|-----|------|

| Supply Voltage            | V <sub>DD</sub> | 1.65V | 3.7 | V    |

| Ambient Temperature Range | T <sub>A</sub>  | -40   | 85  | C    |

#### 2.2. Thermal Characteristics

| Parameter                                                       | Symbol        | Min. | Max | Unit |

|-----------------------------------------------------------------|---------------|------|-----|------|

| Thermal Resistance with DFN package - Junction to Ambient (i)   | $\theta_{JA}$ |      | 39  | €\M  |

| Thermal Resistance with WLCSP package - Junction to Ambient (i) | $\theta_{JA}$ |      | 65  | €\M  |

(iii)  $\theta_{JA}$  is calculated from a package in still air, mounted to 3" x 4.5", 4 layer FR4 PCB with thermal vias under exposed pad (if applicable) per JESD51 standards.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 2.3. Electrical Specifications

| Parameter                                                                   | Symbol                                                                 | Conditions                                                                                                                                | Min.                                      | Тур | Max                       | Unit |

|-----------------------------------------------------------------------------|------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------|-----|---------------------------|------|

| Current consumption                                                         |                                                                        |                                                                                                                                           |                                           |     |                           |      |

| Manual                                                                      | I <sub>pwd</sub>                                                       | Manual (converter stopped, pen detection off, I2C listening, OSC stopped)                                                                 |                                           | 0.4 | 0.75                      | uA   |

| Pen Detect                                                                  | Ipndt                                                                  | Pen detect mode (converter stopped, pen detection activated, device will generate interrupt upon detection, I2C listening, OSC stopped).  |                                           | 0.4 | 0.75                      | uA   |

| Pen Trigger                                                                 | I <sub>pntr</sub>                                                      | Pen trigger mode (converter stopped, pen detection activated, device will start conversion upon pen detection. I2C listening, OSC stopped |                                           | 0.4 | 0.75                      | uA   |

| Automatic                                                                   | I <sub>wt</sub>                                                        | Automatic (converter stopped, pen detection off, I2C listening, OSC and timer on, device is waiting for timer expiry)                     |                                           | 1.5 |                           | uA   |

| Operation @8kSPS, VDD=1.8V                                                  | I <sub>opl</sub>                                                       | X,Y Conv. RATE=4kSPS, N <sub>filt</sub> =1<br>PowDly=0.5us, SetDly=0.5us                                                                  |                                           | 23  | 50                        | uA   |

| Operation @42kSPS, VDD=3.3V                                                 | l <sub>oph</sub>                                                       | X,Y Conv. RATE=3kSPS, N <sub>filt</sub> =7<br>PowDly=0.5us, SetDly=0.5us                                                                  |                                           | 105 | 140                       | uA   |

| Digital I/O                                                                 |                                                                        |                                                                                                                                           |                                           |     |                           |      |

| High-level input voltage <sup>1</sup>                                       | V <sub>IH</sub>                                                        |                                                                                                                                           | 0.7V <sub>DD</sub>                        |     | V <sub>DD</sub> +0.5      | V    |

| Low-level input voltage                                                     | V <sub>IL</sub>                                                        |                                                                                                                                           | V <sub>SS</sub> -0.3                      |     | 0.3V <sub>DD</sub>        | V    |

| SDA / SCL Hysteresis of Schmitt<br>trigger inputs<br>VDD > 2 V<br>VDD < 2 V | V <sub>hys</sub>                                                       |                                                                                                                                           | 0.05V <sub>DD</sub><br>0.1V <sub>DD</sub> |     |                           | V    |

| Low-level output voltage                                                    | V <sub>OL</sub>                                                        | I <sub>OL</sub> =3mA, V <sub>DD</sub> >2V<br>I <sub>OL</sub> =3mA, V <sub>DD</sub> <2V                                                    | 0<br>0                                    |     | 0.4<br>0.2V <sub>DD</sub> | V    |

| Input leakage current                                                       | L <sub>l</sub>                                                         | CMOS input                                                                                                                                |                                           |     | ±1                        | uA   |

| AUX                                                                         |                                                                        |                                                                                                                                           |                                           |     |                           |      |

| Input voltage range                                                         | V <sub>IAUX</sub>                                                      |                                                                                                                                           | 0                                         |     | V <sub>DD</sub>           | V    |

| Input capacitance                                                           | C <sub>X+</sub> ,C <sub>X-</sub> ,C <sub>Y+</sub> ,<br>C <sub>Y-</sub> |                                                                                                                                           |                                           | 50  |                           | pF   |

|                                                                             | C <sub>AUX</sub>                                                       |                                                                                                                                           |                                           | 5   |                           | pF   |

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

| Parameter                  | Symbol               | Conditions                                   | Min. | Тур  | Max | Unit |

|----------------------------|----------------------|----------------------------------------------|------|------|-----|------|

| Input leakage current      | I <sub>IAUX</sub>    |                                              | -1   |      | 1   | uA   |

| Startup                    |                      |                                              |      |      |     |      |

| Power-up time<br>(Delay    | t <sub>POR</sub>     | Time between rising edge VDD and rising NIRQ |      |      | 1   | ms   |

| Reset                      |                      |                                              |      |      |     |      |

| Reset low time             | t <sub>NRST</sub>    |                                              | 50   |      |     | ns   |

| ADC                        |                      |                                              |      |      |     |      |

| Resolution                 | A <sub>res</sub>     |                                              | 12   |      |     | bits |

| Offset                     | A <sub>off</sub>     |                                              |      | ±1   |     | LSB  |

| Gain error                 | A <sub>ge</sub>      | At full scale                                |      | 0.5  |     | LSB  |

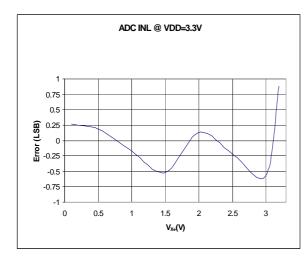

| Differential nonlinearity  | A <sub>dnI</sub>     |                                              |      | ±1   |     | LSB  |

| Integral nonlinearity      | A <sub>inl</sub>     |                                              |      | ±1.5 |     | LSB  |

| Resistors                  |                      |                                              |      |      |     |      |

| X+, X-, Y+, Y- resistance  | R <sub>chn</sub>     | Touch Pad Biasing Resistance                 |      | 5    |     | Ohm  |

| Pen detect resistance      | R <sub>PNDT_00</sub> | R <sub>PNDT</sub> = 0                        |      | 100  |     | kOhm |

|                            | R <sub>PNDT_01</sub> | R <sub>PNDT</sub> = 1                        |      | 200  |     | kOhm |

|                            | R <sub>PNDT_10</sub> | R <sub>PNDT</sub> = 2                        |      | 50   |     | kOhm |

|                            | R <sub>PNDT_11</sub> | R <sub>PNDT</sub> = 3                        |      | 25   |     | kOhm |

| External components        |                      | recommendations                              |      |      |     |      |

| Capacitor between VDD, GND | C <sub>vdd</sub>     | Type 0402, tolerance +/-50%                  |      | 0.1  |     | uF   |

<sup>1.</sup> SCL, SDA, NRST and NIRQ can be pulled up to a potential higher than the chip VDD but must not exceed the maximun voltage of 3.7V.

All values are valid within the recommended operating conditions unless otherwise specified.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

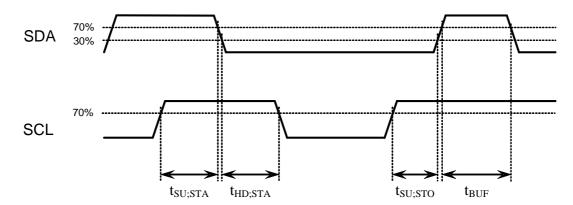

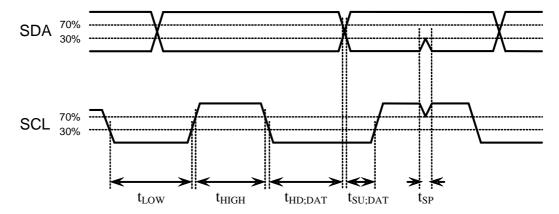

### 2.4. Host Interface Specifications

| Parameter                                                         | Symbol              | Condition | Min | Тур | Max | Unit |  |  |

|-------------------------------------------------------------------|---------------------|-----------|-----|-----|-----|------|--|--|

| 2C TIMING SPECIFICATIONS <sup>(i)</sup>                           |                     |           |     |     |     |      |  |  |

| SCL clock frequency                                               | f <sub>SCL</sub>    |           | 0   |     | 400 | kHz  |  |  |

| SCL low period                                                    | t <sub>LOW</sub>    |           | 1.3 |     |     | us   |  |  |

| SCL high period                                                   | tHIGH               |           | 0.6 |     |     | us   |  |  |

| Data setup time                                                   | t <sub>SU;DAT</sub> |           | 100 |     |     | ns   |  |  |

| Data hold time                                                    | t <sub>HD;DAT</sub> |           | 0   |     |     | ns   |  |  |

| Repeated start setup time                                         | t <sub>SU;STA</sub> |           | 0.6 |     |     | us   |  |  |

| Start condition hold time                                         | t <sub>HD;STA</sub> |           | 0.6 |     |     | us   |  |  |

| Stop condition setup time                                         | t <sub>SU;STO</sub> |           | 0.6 |     |     | us   |  |  |

| Bus free time between stop and start                              | t <sub>BUF</sub>    |           | 1.3 |     |     | us   |  |  |

| Data valid time                                                   | t <sub>VD;DAT</sub> |           |     |     | 0.9 | us   |  |  |

| Data valid ack time                                               | t <sub>VD;ACK</sub> |           |     |     | 0.9 | us   |  |  |

| Pulse width of spikes that must be suppressed by the input filter | t <sub>SP</sub>     |           |     |     | 50  | ns   |  |  |

| I2C BUS SPECIFICATIONS                                            |                     | 1         | 1   | ı   | 1   | I    |  |  |

| Capacitive Load on each bus line SCL, SD/                         | A C <sub>b</sub>    |           |     |     | 400 | pF   |  |  |

### Table 3 Host Interface Specifications **Notes:**

(i) All timing specifications refer to voltage levels (V<sub>IL</sub>, V<sub>IH</sub>, V<sub>OL</sub>) defined in Table 3 unless otherwise mentioned.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 2.5. Host Interface Timing Waveforms

Figure 4. I2C Start and Stop timing

Figure 5. I2C Data timing

> **SUPPLY CURRENT in MANUAL MODE** vs TEMPERATURE

> > $V_{DD}=3.3V$

V<sub>DD</sub>=1.85\

60

Conversion Rate (kCPS)

80

### **ADVANCED COMMUNICATIONS & SENSING**

**DATASHEET**

100

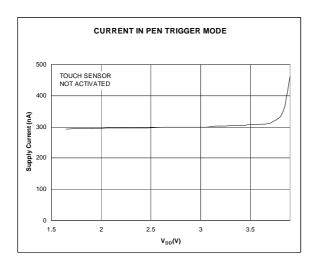

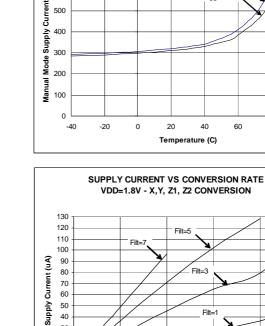

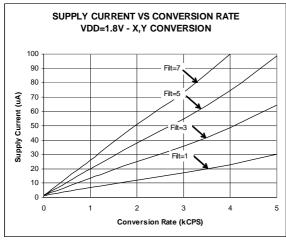

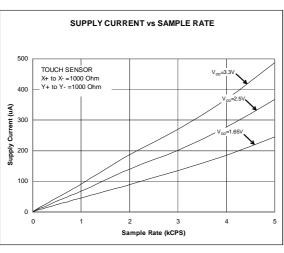

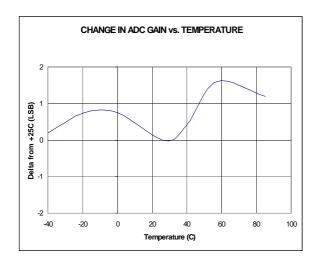

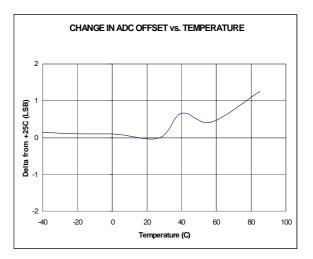

### 2.6. Typical Operating Characteristics

At Ta= -40℃ to +85℃, VDD=1.7V to 3.7V, PowDly=0.5 us, SetDly=0.5us, Filt=1, Resistive touch screen sensor current not taking in account, unless otherwise noted.

700

600

500

40

30

20

10

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

Typical Operating Characteristics (continued)

At Ta= -40°C to +85°C, VDD=1.7V to 3.7V, PowDly=0.5 us, SetDly=0.5us, Filt=1, Resistive touch screen sensor current not taking in account, unless otherwise noted.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 3. Functional Description

#### 3.1. General Introduction

This section provides an overview of the SX8650 architecture, device pinout and a typical application.

The SX8650 is designed for 4-wire resistive touch screen applications (Figure 6). The touch screen or touch panel is the resistive sensor and can be activated by either a finger or stylus. The touch screen coordinates and touch pressure are converted into I2C format by the SX8650 for transfer to the host.

Figure 6. SX8650 with screen

#### 3.2. Channel Pins

#### 3.2.1. X+, X-, Y+. Y-

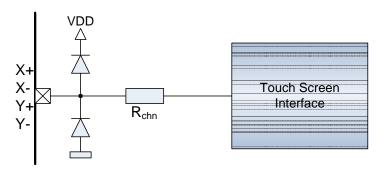

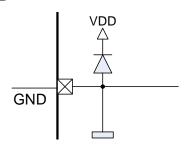

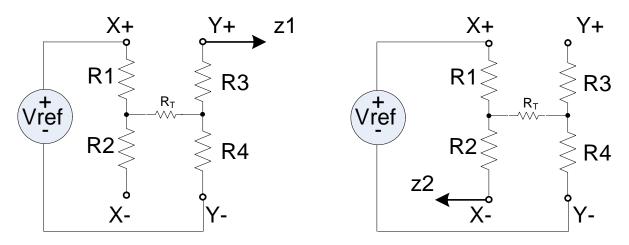

Figure 7. Simplified diagram of X+, X-, Y+, Y- pins

# The SX8650's channel pins (X+, X-, Y+, Y-) directly connect to standard touch screen X and Y resistive layers. The SX8650 separately biases each of these layers and converts the resistive values into (X,Y) coordinates.

The channel pins are protected to VDD and GROUND.

Figure 7 shows the simplified diagram of the X+, X-, Y+, Y- pins.

#### 3.2.2. AUX

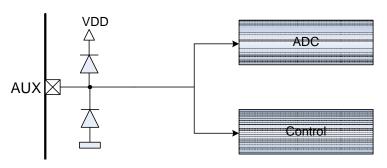

The SX8650 interface includes an AUX pin that serves two functions: an ADC input; and a start of conversion trigger. When used as an ADC, the single ended input range is from GND to VDD, referred to GND. When the AUX input is configured to start conversions, the AUX input can be further configured as a rising and / or falling edge trigger.

The AUX is protected to VDD and GROUND.

Figure 8 shows a simplified diagram of the AUX pin.

Figure 8. Simplified diagram of AUX

### **ADVANCED COMMUNICATIONS & SENSING**

**DATASHEET**

#### 3.3. Host Interface and Control Pins

The SX8650 host and control interface consists of: NIRQ, I2C pins SCL and SDA, A0, and NRST.

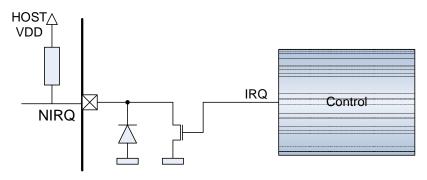

#### 3.3.1. NIRQ

The NIRQ pin is an active low, open drain output to facilitate interfacing to different supply voltages and thus requires an external pull-up resistor (1-10 kOhm). The NIRQ pin does not have protection to VDD.

The NIRQ function is designed to provide an interrupt to the host processor. Interrupts may occur when a pen is detected, or when channel data is available.

Figure 9 shows a simplified diagram of the NIRQ pin.

Figure 9. Simplified diagram of NIRQ

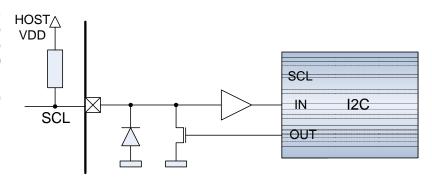

#### 3.3.2. SCL

The SCL pin is a high-impedance input and opendrain output pin. The SCL pin does not have protection to VDD to conform to I2C slave specifications. An external pull-up resistor (1-10 kOhm) is required.

Figure 10 shows the simplified diagram of the SCL pin.

Figure 10. Simplified diagram of SCL

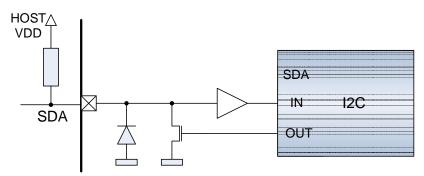

#### 3.3.3. SDA

Figure 11. Simplified diagram of SDA

SDA is an I/O pin. It can be used as an open-drain output (with external pull-up resistor) or as an input. An external pull-up resistor (1-10 kOhm) is required.

The SDA I/O pin does not have protection to VDD to conform to I2C slave specifications.

Figure 11 shows a simplified diagram of the SDA pin.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

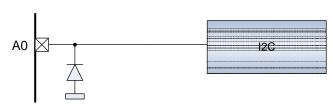

#### 3.3.4. A0

The A0 pin is connected to the I2C address select control circuitry and is used to modify the device I2C address. The A0 pin is protected to GROUND.

Figure 12 shows a simplified diagram of the A0 pin.

Figure 12. Simplified diagram of A0

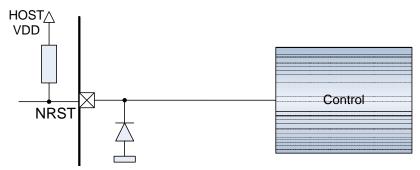

#### 3.3.5. NRST

The NRST pin is an active low input that provides a hardware reset of the SX8650's control circuitry.

The NRST pin is protected GROUND to enable interfacing with devices at a different supply voltages.

Figure 13 shows a simplified diagram of the NRST pin.

Figure 13. Simplified diagram of NRST

#### 3.4. Power Management Pins

The SX8650's power management input consists of the following Power and Ground pins.

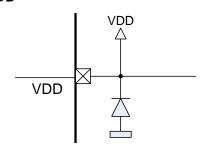

#### 3.4.1. VDD

The VDD is a power pin and is the power supply for the SX8650. The VDD has ESD protection to GROUND.

Figure 14 shows a simplified diagram of the VDD pin.

Figure 14. Simplified diagram of VDD

#### 3.4.2. GND

Figure 15. Simplified diagram of GND

The SX8650 has one power management ground pin, GND. (The die attach paddle on DFN is also connected to GND.) The GND has ESD protection to VDD.

Figure 15 shows a simplified diagram of the GND pin.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 4. Detailed Description

#### 4.1. Touch Screen Operation

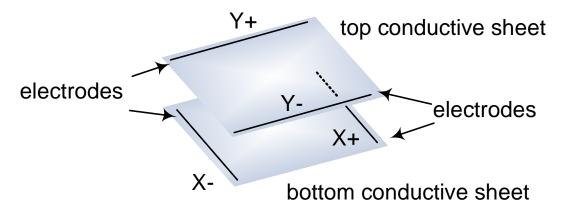

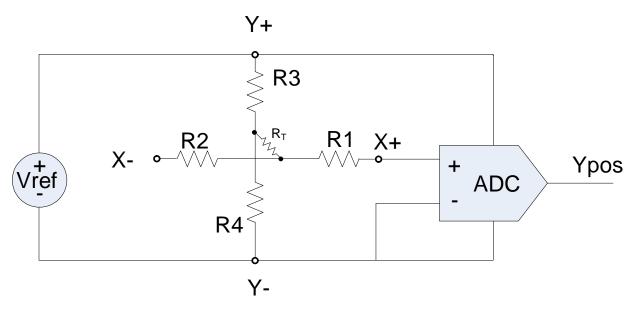

A resistive touch screen consists of two (resistive) conductive sheets separated by an insulator when not pressed. Each sheet is connected through 2 electrodes at the border of the sheet (Figure 16). When a pressure is applied on the top sheet, a connection with the lower sheet is established. Figure 17 shows how the Y coordinate can be measured. The electrode plates are connected through terminals X+, X- and Y+, Y- to an analog to digital converter (ADC) and a reference voltage. The resistance between the terminals X+ and X- is defined by Rxtot. Rxtot will be split in 2 resistors, R1 and R2, in case the screen is touched. The resistance between the terminals Y+ and Y- is represented by R3 and R4. The connection between the top and bottom sheet is represented by the touch resistance ( $R_T$ ).

Figure 16. 4-wire Touch Screen

Figure 17. Touch Screen Operation ordinate measurement (Y)

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

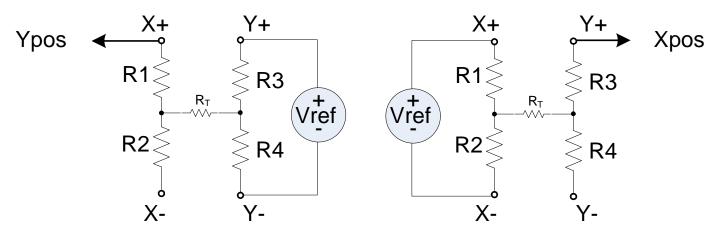

#### 4.2. Coordinates Measurement

The top resistive sheet (Y) is biased with a voltage source. Resistors R3 and R4 determine a voltage divider proportional to the Y position of the contact point. Since the converter has a high input impedance, no current flows through R1 so that the voltage X+ at the converter input is given by the voltage divider created by R3 and R4.

The X coordinate is measured in a similar fashion with the bottom resistive sheet (X) biased to create a voltage divider by R1 and R2, while the voltage on the top sheet is measured through R3. Figure 18 shows the coordinates measurement setup. The resistance  $R_T$  is the resistance obtained when a pressure is applied on the screen.  $R_T$  is created by the contact area of the X and Y resistive sheet and varies with the applied pressure.

Figure 18. Ordinate (Y) and abscissa (X) coordinates measurement setup

The X and Y position are found by:  $Xpos = 4095 \cdot \frac{R2}{R1 + R2}$   $Ypos = 4095 \cdot \frac{R4}{R3 + R4}$

#### 4.3. Pressure Measurement

The pressure measurement consists of two additional setups: z1 and z2 (see Figure 19).

Figure 19. z1 and z2 pressure measurement setup

The corresponding equations for the pressure:  $z1 = 4095 \cdot \frac{R4}{R1 + R4 + R_T}$   $z2 = 4095 \cdot \frac{R4 + Rt}{R1 + R4 + R_T}$

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

The X and Y total sheet resistance (Rxtot, Rytot) are known from the touch screen supplier.

R4 is proportional to the Y coordinate.

The R4 value is given by the total Y plate resistance multiplied by the fraction of the Y position over the full coordinate range.

By re-arranging z1 and z2 one obtains

$R_T = R4 \cdot \left[ \frac{z2}{z1} - 1 \right]$

$R4 = Rytot \cdot \frac{Ypos}{4005}$

Rxtot = R1 + R2

Rytot = R3 + R4

$$R_T = Rytot \cdot \frac{Ypos}{4095} \cdot \left[ \frac{z^2}{z^1} - 1 \right]$$

Which results in:

The touch resistance calculation above requires three channel measurements (Ypos, z2 and z1) and one specification data (Rytot). An alternative calculation method is using Xpos, Ypos, one z channel and both Rxtot and Rytot shown in the next calculations

R1 is inverse proportional to the X coordinate.

$$R1 = Rxtot \cdot \left[ 1 - \frac{Xpos}{4095} \right]$$

Substituting R1 and R4 into z1 and rearranging terms gives:

$$R_T = \frac{Rytot \cdot Ypos}{4095} \cdot \left[ \frac{4095}{z1} - 1 \right] - Rxtot \cdot \left[ 1 - \frac{Xpos}{4095} \right]$$

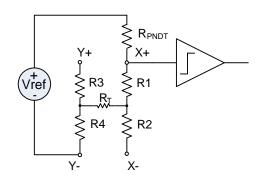

#### 4.4. Pen Detection

The pen detection circuitry is used both to detect a user action and generate an interrupt or start an acquisition in PENDET and PENTRG mode respectively. Doing a pen detection prior to conversion avoids feeding the host with dummy data and saves power.

If the touchscreen is powered between X+ and Y- through a resistor  $R_{PNDT}$ , no current will flow so long as pressure is not applied to the surface (see Figure 20). When some pressure is applied, a current path is created and brings X+ to the level defined by the resistive divider determined by  $R_{PNDT}$  and the sum of R1,  $R_{T}$  and R4.

The level is detected by a comparator.

Figure 20. Pen detection

R<sub>PNDT</sub> should be set to the greatest value 200 kOhm for optimal detection (see Table 6). Increasing PowDly settings can also improve the detection on panel with high resistance.

The pen detection will set the PENIRQ bit of the RegStat register.

In PENDET mode, the pen detection will set NIRQ low. The PENIRQ bit will be cleared and the NIRQ will be de-asserted as soon as the host reads the status register.

### **ADVANCED COMMUNICATIONS & SENSING**

**DATASHEET**

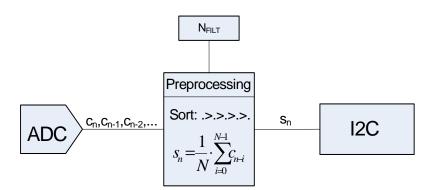

### 5. Data Processing

The SX8650 offers 4 types of data processing which allows the user to make trade-offs between data throughput, power consumption and noise rejection.

The parameter FILT is used to select the filter order  $N_{\text{filt}}$ . The noise rejection will be improved with a high order to the detriment of the power consumption. The K coefficient in Table 4 is a filter constant. Its value is K=4079/4095.

Figure 21. Filter structure

| FILT | N <sub>filt</sub> | Processing                                                                                                                                                                                                                                          |

|------|-------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0    | 1                 | $s_n = c_n$<br>No average.                                                                                                                                                                                                                          |

| 1    | 3                 | $= \frac{1}{3} \cdot \frac{4079}{4095} (c_n + c_{n-1} + c_{n-2})$ 3 ADC samples are averaged                                                                                                                                                        |

| 2    | 5                 | $= \frac{1}{5} \cdot \frac{4079}{4095} (c_n + c_{n-1} + c_{n-2} + c_{n-3} + c_{n-4})$ 5 ADC samples are averaged                                                                                                                                    |

| 3    |                   | $\begin{aligned} c_{max1} &\geq c_{max2} \geq c_a \geq c_b \geq c_c \geq c_{min1} \geq c_{min2} \\ &= \frac{1}{3} \cdot \frac{4079}{4095} (c_a + c_b + c_c) \\ \text{7 ADC samples are sorted and the 3 center samples are averaged} \end{aligned}$ |

Table 4. Filter order

#### 5.1. Host Interface and Control

The host interface consists of I2C (SCL and SDA) and the NIRQ, A0, NRST signals.

The I2C implemented on the SX8650 is compliant with:

- Standard Mode (100 kbit/s) & Fast Mode (400 kbit/s)

- Slave mode

- 7 bit slave address

#### 5.1.1. I2C Address

Pin A0 defines the LSB of the I2C address. It is shown on Figure 22.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

SX8650 Slave Address(7:1) =  $\begin{cases} 1 & 0 & 0 & 1 & 0 & 0 \\ \hline 1 & 0 & 0 & 1 & 0 & 0 \\ \hline 1 & 0 & 0 & 1 & 0 & 0 & 1 \\ \hline \end{array}$  with pin A0 connected to yDD

Figure 22. I2C slave address

Upon request of the customer, a custom I2C address can be burned in the NVM.

The host uses the I2C to read and write data and commands to the configuration and status registers. During a conversion, the I2C clock can be stretched until the end of the processing.

Channel data read is done by I2C throughput optimized formats.

The supported I2C access formats are described in the next sections:

- I2C Write Registers

- I2C Read Registers

- I2C Host Commands

- I2C Read Channels

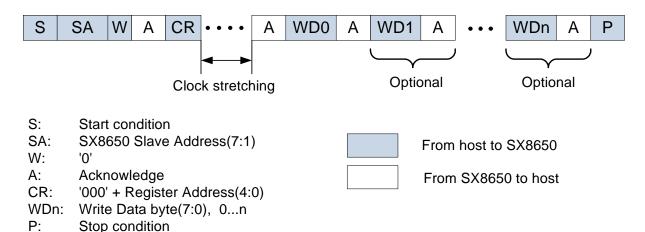

#### 5.1.2. I2C Write Registers

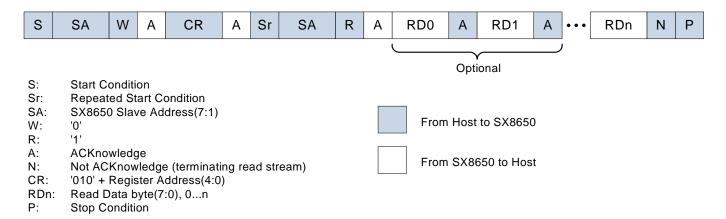

The format for I2C write is given in Figure 23.

After the start condition [S], the SX8650 slave address (SA) is sent, followed by an eighth bit (W='0') indicating a Write.

The SX8650 then Acknowledges [A] that it is being addressed, and the host sends 8-bit Command and Register address consisting of the command bits '000' followed by the SX8650 Register Address (RA).

The SX8650 Acknowledges [A] and the host sends the appropriate 8-bit Data Byte (WD0) to be written.

Again the SX8650 Acknowledges [A].

In case the host needs to write more data, a succeeding 8-bit Data Byte will follow (WD1), acknowledged by the slave [A]. This sequence will be repeated until the host terminates the transfer with the Stop condition [P].

Figure 23. I2C write register

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

The register address increments automatically when successive register data (WD1...WDn) is supplied by the host. This automatic increment can be used for the first 4 register addresses (see Table 6).

The correct sampling of the screen by the SX8650 and the host I2C bus traffic are events that might occur simultaneously. The SX8650 will synchronize these events by the use of clock stretching if that is required. The stretching occurs directly after the last received command bit (see Figure 23).

#### 5.1.3. I2C Read Registers

The format for incremental I2C read for registers is given in Figure 24. The read has to start with a write of the read address.

After the start condition [S], the SX8650 Slave Address (SA) is sent, followed by an eighth bit (W='0') indicating a Write. The SX8650 then Acknowledges [A] that it is being addressed, and the host responds with a 8-bit CR Data consisting of '010' followed by the Register Address (RA). The SX8650 responds with an Acknowledge [A] and the host sends the Repeated Start Condition [Sr]. Once again, the SX8650 Slave Address (SA) is sent, followed by an eighth bit (R='1') indicating a Read.

The SX8650 responds with an Acknowledge [A] and the read Data byte (RD0). If the host needs to read more data it will acknowledge [A] and the SX8650 will send the next read byte (RD1). This sequence can be repeated until the host terminates with a NACK [N] followed by a stop [P].

Figure 24. I2C read registers

The I2C read register format of Figure 24 is maintained until the Stop Condition. After the Stop Condition the SX8650 is performing succeeding reads by the compact read format of the I2C read channels described in the next section. No clock stretching will occur for the I2C read registers.

#### 5.1.4. I2C Host Commands

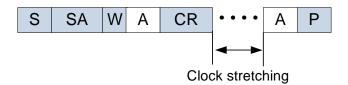

The format for I2C commands is given in Figure 25.

After the start condition [S], the SX8650 Slave Address (SA) is sent, followed by an eighth bit (W='0') indicating a Write. The SX8650 then Acknowledges [A] that it is being addressed, and the host responds with an 8-bit Data consisting of a '1' + command(6:0). The SX8650 Acknowledges [A] and the host sends a stop [P].

The exact definition of command(6:0) can be found in Table 8.

#### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

S: Start condition

SA: SX8650 Slave Address(7:1)

W: '0'

A: Acknowledge CR: '1' + Command(6:0)

P: Stop condition

From host to SX8650

From SX8650 to host

Figure 25. I2C host command

The sampling of the screen by the SX8650 and the host I2C bus traffic are events that might occur simultaneously. The SX8650 will synchronize these events by the use of clock stretching if that is required. The stretching occurs directly after the last received command bit (see Figure 25).

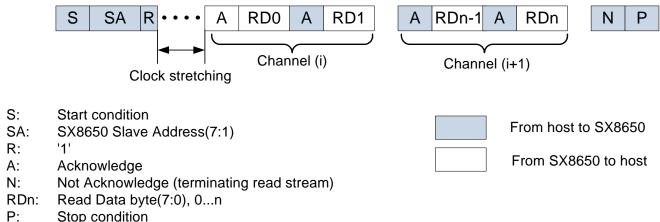

#### 5.1.5. I2C Read Channels

The host is able to read the channels with a high throughput, by the format shown in Figure 26.

After the start condition [S], the SX8650 Slave Address (SA) is sent, followed by an eighth bit (R='1') indicating a read. The SX8650 responds with an Acknowledge [A] and the Read Data byte (RD0). The host sends an Acknowledge [A] and the SX8650 responds with the Read Data byte (RD1). If the host needs to read more data, it will acknowledge [A] and the SX8650 will send the next read bytes. This sequence can be repeated until the host terminates with a NACK [N] followed immediately by a stop [P]. The NACK [N] releases the NIRQ line. The stop [P] must occur before the end of the conversion. The channel data that can be read is defined by the last conversion sequence.

A maximum number of 10 data bytes is passed when all channels (X, Y, z1, z2 and AUX) are activated in the "I2CRegChanMsk".

The channel data is sent with the following order: X, Y, Z1, Z2, AUX. The first byte of the data contains the channel information as shown in Figure 27.

Typical applications require only X and Y coordinates, thus only 4 bytes of data will be read.

Figure 26. I2C read channels

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

The sampling of the screen by the SX8650 and the host I2C bus traffic are events that might occur simultaneously. The SX8650 will synchronize these events by the use of clock stretching if that is required. The stretching occurs directly after the address and read bit have been sent for the I2C read channels command (see Figure 26).

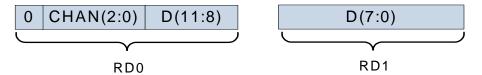

#### 5.1.6. Data Channel Format

Channel data is coded on 16 bits as shown in Figure 27

Figure 27. data channel format

The 3 bits CHAN(2:0) are defined in Table 9 and show which channel data is referenced. The channel data D(11:0) is of unsigned format and corresponds to a value between 0 and 4095.

#### 5.1.7. Invalid Qualified Data

The SX8650 will return 0xFFFF data in case of invalid qualified data.

This occurs:

- when the SX8650 converted channels and the host channel readings do not correspond. E.g. the host converts X and Y and the host tries to read X, Y and z1 and z2.

- when a conversion is done without a pen being detected.

#### 5.2. I2C Register Map

| I2C register address RA(4:0) | Register        | Description |

|------------------------------|-----------------|-------------|

| 0 0000                       | I2CRegCtrl0     | Write, Read |

| 0 0001                       | I2CRegCtrl1     | Write, Read |

| 0 0010                       | I2CRegCtrl2     | Write, Read |

| 0 0100                       | I2CRegChanMsk   | Write, Read |

| 0 0101                       | I2CRegStat      | Read        |

| 1 1111                       | I2CRegSoftReset | Write       |

Table 5. I2C Register address

The details of the registers are described in the next sections.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

### 5.3. Host Control Writing

The host control writing allows the host to change SX8650 settings. The control data goes from the host towards the SX8650 and may be read back for verification.

| register    | bits     | default | description                                                                                                                                 |                                                                                                                                                     |                                                                                                                                               |  |  |  |

|-------------|----------|---------|---------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|             |          |         |                                                                                                                                             | Set rate in coordinates per sec (cps) (± 20%) If RATE equals zero then Manual mode. if RATE is larger than zero then Automatic mode                 |                                                                                                                                               |  |  |  |

| I2CRegCtrl0 | 7:4      | 0000    | RATE                                                                                                                                        | 0000: Timer disabled -Manual mode<br>0001: 10 cps<br>0010: 20 cps<br>0011: 40 cps<br>0100: 60 cps<br>0101: 80 cps<br>0110: 100 cps<br>0111: 200 cps | 1000: 300 cps<br>1001: 400 cps<br>1010: 500 cps<br>1011: 1k cps<br>1100: 2k cps<br>1101: 3k cps<br>1110: 4k cps<br>1111: 5k cps               |  |  |  |

|             |          |         |                                                                                                                                             | Settling time (± 10%): The channel w before each channel conversion                                                                                 | rill be biased for a time of POWDLY                                                                                                           |  |  |  |

|             | 3:0 0000 | POWDLY  | 0000: Immediate (0.5 us)<br>0001: 1.1 us<br>0010: 2.2 us<br>0011: 4.4 us<br>0100: 8.9 us<br>0101: 17.8 us<br>0110: 35.5 us<br>0111: 71.0 us | 1000: 0.14 ms<br>1001: 0.28 ms<br>1010: 0.57 ms<br>1011: 1.14 ms<br>1100: 2.27 ms<br>1101: 4.55 ms<br>1110: 9.09 ms<br>1111: 18.19 ms               |                                                                                                                                               |  |  |  |

|             | 7:6 0    | 00      | AUXAQC                                                                                                                                      | 00: AUX is used as an analog input 01: On rising AUX edge, wait POWDLY and start acquisition                                                        | 10: On falling AUX edge, wait<br>POWDLY and start acquisition<br>11: On rising and falling AUX<br>edges, wait POWDLY and start<br>acquisition |  |  |  |

|             |          |         |                                                                                                                                             | The AUX trigger requires the manual mode.                                                                                                           |                                                                                                                                               |  |  |  |

|             | 5        | 1       | CONDIRQ                                                                                                                                     | Enable conditional interrupts 0: interrupt always generated at end detected the data is set to 'invalid qu 1: interrupt generated when pen dete     | alified'.                                                                                                                                     |  |  |  |

| I2CRegCtrl1 | 4        | 0       | reserved                                                                                                                                    |                                                                                                                                                     |                                                                                                                                               |  |  |  |

|             | 3:2      | 00      | RPDNT                                                                                                                                       | Select the Pen Detect Resistor<br>00: 100 KOhm<br>01: 200 KOhm<br>10: 50 KOhm<br>11: 25 KOhm                                                        |                                                                                                                                               |  |  |  |

|             | 1:0      | 00      | FILT                                                                                                                                        | Digital filter control 00: Disable 01: 3 sample averaging 10: 5 sample averaging 11: 7 sample acquisition, sort, average                            | ge 3 middle samples                                                                                                                           |  |  |  |

Table 6. I2C registers

### **ADVANCED COMMUNICATIONS & SENSING**

### DATASHEET

| register        | bits | default | description |                                                                                                                                                         |                                                                                                                                       |  |  |

|-----------------|------|---------|-------------|---------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------|--|--|

|                 | 7:4  | 0       | reserved    |                                                                                                                                                         |                                                                                                                                       |  |  |

|                 |      |         |             | Settling time while filtering (± 10%) When filtering is enabled, the channe POWDLY for the first conversion, and subsequent conversion in a filter set. | d for a time of SETDLY for each                                                                                                       |  |  |

| I2CRegCtrl2     | 3:0  | 0000    | SETDLY      | 0000: Immediate (0.5 us)<br>0001: 1.1 us<br>0010: 2.2 us<br>0011: 4.4 us<br>0100: 8.9 us<br>0101: 17.8 us<br>0110: 35.5 us<br>0111: 71.0 us             | 1000: 0.14 ms<br>1001: 0.28 ms<br>1010: 0.57 ms<br>1011: 1.14 ms<br>1100: 2.27 ms<br>1101: 4.55 ms<br>1110: 9.09 ms<br>1111: 18.19 ms |  |  |

|                 | 7    | 1       | XCONV       | 0: no sample<br>1: sample, report X channel                                                                                                             |                                                                                                                                       |  |  |

|                 | 6    | 1       | YCONV       | 0: no sample<br>1: sample, report Y channel                                                                                                             |                                                                                                                                       |  |  |

|                 | 5    | 0       | Z1CONV      | 0: no sample<br>1: sample, report Z1 channel                                                                                                            |                                                                                                                                       |  |  |

| I2CRegChanMsk   | 4    | 0       | Z2CONV      | 0: no sample<br>1:sample, report Z2 channel                                                                                                             |                                                                                                                                       |  |  |

|                 | 3    | 0       | AUXCONV     | 0: no sample<br>1: sample, report AUX channel                                                                                                           |                                                                                                                                       |  |  |

|                 | 0    | 0       | reserved    |                                                                                                                                                         |                                                                                                                                       |  |  |

|                 | 0    | 0       | reserved    |                                                                                                                                                         |                                                                                                                                       |  |  |

|                 | 0    | 0       | reserved    |                                                                                                                                                         |                                                                                                                                       |  |  |

|                 |      |         |             | host to read the status of the SX86 is register is ignored.                                                                                             | 50. The data goes from the SX8650                                                                                                     |  |  |

| IOCD a a Ctat   | 7    | 0       | CONVIRQ     | 0: no IRQ pending 1: End of conversion sequence IRQ   IRQ is cleared by the I2C channel re-                                                             | •                                                                                                                                     |  |  |

| I2CRegStat      | 6    | 0       | PENIRQ      | operational in pen detect mode 0: no IRQ pending 1: Pen detected IRQ pending IRQ is cleared by the I2C status reading                                   |                                                                                                                                       |  |  |

|                 | 5:0  | 000000  | reserved    |                                                                                                                                                         |                                                                                                                                       |  |  |

| I2CRegSoftReset | 7:0  | 0x00    |             | If the host writes the value 0xDE to this register, then the SX8650 will be reset.  Any other data will not affect the SX8650                           |                                                                                                                                       |  |  |

Table 6. I2C registers

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### 5.4. Host Commands

The host can write to and read from registers of the SX8650 by the write and read commands as defined in Table 7.

| W/R command name |   |   |   | CR | Function |   |   |   |                                     |

|------------------|---|---|---|----|----------|---|---|---|-------------------------------------|

|                  | 7 | 6 | 5 | 4  | 3        | 2 | 1 | 0 |                                     |

| WRITE(RA)        | 0 | 0 | 0 |    | RA(4:0)  |   |   |   | Write register (see Table 5 for RA) |

| READ(RA)         | 0 | 1 | 0 |    | RA(4:0)  |   |   |   | Read register (see Table 5 for RA)  |

Table 7. I2C W/R commands

.The host can issue commands to change the operation mode or perform manual actions as defined in Table 8.

| command name  |   |   |   | CR | Function |   |           |   |                                                                              |

|---------------|---|---|---|----|----------|---|-----------|---|------------------------------------------------------------------------------|

|               | 7 | 6 | 5 | 4  | 3        | 2 | 1         | 0 |                                                                              |

| SELECT(CHAN)  | 1 | 0 | 0 | 0  | х        | С | CHAN(2:0) |   | Bias channel (see Table 9 for CHAN)                                          |

| CONVERT(CHAN) | 1 | 0 | 0 | 1  | х        | С | CHAN(2:0) |   | Bias channel (see Table 9 for CHAN) Wait POWDLY settling time Run conversion |

| MANAUTO       | 1 | 0 | 1 | 1  | х        | х | х         | х | Enter manual or automatic mode.                                              |

| PENDET        | 1 | 1 | 0 | 0  | х        | х | х         | х | Enter pen detect mode.                                                       |

| PENTRG        | 1 | 1 | 1 | 0  | х        | х | х         | х | Enter pen trigger mode.                                                      |

Table 8. I2C commands

The channels are defined as in Table 9.

| Channel  | CHAN(2:0) |   |   | Function                                                                 |

|----------|-----------|---|---|--------------------------------------------------------------------------|

|          | 2         | 1 | 0 |                                                                          |

| Х        | 0         | 0 | 0 | X channel                                                                |

| Y        | 0         | 0 | 1 | Y channel                                                                |

| Z1       | 0         | 1 | 0 | First channel for pressure measurement                                   |

| Z2       | 0         | 1 | 1 | Second channel for pressure measurement                                  |

| AUX      | 1         | 0 | 0 | Auxiliary channel                                                        |

| reserved | 1         | 0 | 1 |                                                                          |

| reserved | 1         | 1 | 0 |                                                                          |

| SEQ      | 1         | 1 | 1 | Channel sequentially selected from I2CRegChanMsk register, (see Table 8) |

Table 9. channel definition

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

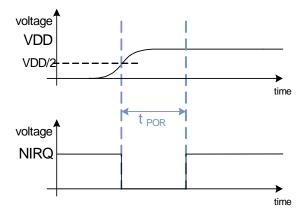

#### 5.5. Power-Up

The NIRQ pin is kept low during SX8650 power-up.

During power-up, the SX8650 is not accessible and I2C communications are ignored.

As soon as NIRQ rises, the SX8650 is ready for I2C communication.

After startup, the host must wait t<sub>por</sub> before any communication with the SX8650.

The POR of the SX8650 will reset all registers and states of the SX8650 at power-up.

Figure 28. Power-up, NIRQ

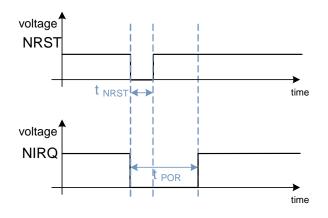

#### 5.6. Reset

Additionally the host can reset the SX8650 by asserting the NRST pin (active low) and also via the I2C bus.

If NRST is driven LOW, then NIRQ will be driven low by the SX8650. When NRST is released (or set to high) then NIRQ will be released by the SX8650.

The circuit has also a soft reset capability. When writing the code 0xDE to the register RegSoftReset, the circuit will be reset.

Figure 29. Reset

### 6. Modes of Operation

The SX8650 has four operation modes that are configured using the I2C commands as defined in Table 8 and Table 6. These 4 modes are:

- manual (command 'MANAUTO' and RATE=0),

- automatic (command 'MANAUTO' and RATE>0),

- pen detect (command 'PENDET'),

- pen trigger mode (command 'PENTRG').

At startup the SX8650 is set in manual mode.

In the manual mode the SX8650 is entirely stopped except for the I2C peripheral which accepts host commands. This mode requires RATE equal to be zero (RATE = 0, see Table 6).

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

In the automatic mode the SX8650 will sequence automatic channel conversions. This mode requires RATE to be larger than zero (RATE > 0, see Table 6).

In the PENDET mode the pen detection is activated. The SX8650 will generate an interrupt (NIRQ) upon pen detection and set the PENIRQ bit in the I2C status register. To quit the PENDET mode the host needs to configure the manual mode.

In the PENTRG mode the pen detection is activated and a channel conversion will start after the detection of a pen. The SX8650 will generate an interrupt (NIRQ) upon pen detection and set the CONVIRQ bit in the I2C status register. To quit the PENTRIG mode the host needs to configure the manual mode. The PENTRG mode offers the best compromise between power consumption and coordinate throughput.

#### 6.1. Manual Mode

In manual mode (RATE=0) single actions are triggered by the I2C commands described in Table 10.

When a command is received, the SX8650 executes the associated task and waits for the next command. It is up to the host to sequence all actions.

| Command       | Action                                                                                    |

|---------------|-------------------------------------------------------------------------------------------|

| CONVERT(CHAN) | Select and bias a channel Wait for the programmed settling time (POWDLY) Start conversion |

| SELECT(CHAN)  | Select and bias a channel                                                                 |

Table 10 CONVERT and SELECT command

The channel can be biased for an arbitrary amount of time by first sending a SELECT command and then a CONVERT command once the settling time requirement is met.

The SELECT command can be omitted if the large range of POWDLY settings cover the requirements. In the latter case, the CONVERT command alone is enough to perform an acquisition.

With CHAN=SEQ, multiple channels are sampled. This requires programming the POWDLY field in register RegCTRL0. The selected channel will be powered during POWDLY before a conversion is started. The channel bias is automatically removed after the conversion has completed.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

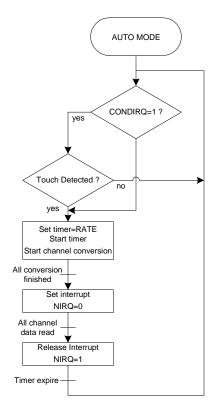

#### 6.2. Automatic mode

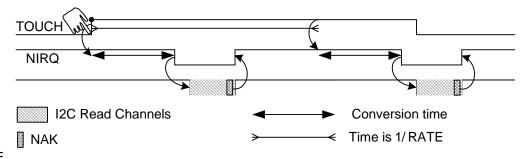

In automatic mode (RATE > 0), SX8650 will automatically decide when to start acquisition, sequence all the acquisitions and alerts the host if data is available for download with a NIRQ. The host will read the channels and the SX8650 will start again with the next conversion cycle.

The fastest coordinate rate is obtained if the host reads the channels immediately after the NIRQ.

To not loose data, the SX8650 will not begin conversion before the host read the channels. If after the NIRQ a delay superior to the sampling period is made by the host to read the channels a slower coordinate rate is obtained.

When the control CONDIRQ bit (see register I2CRegStat Table 6) is set to '1' then the interrupts will only be generated if the pen detect occurred. This result in a regular interrupt stream, as long as the host performs the read channel commands, and the screen is touched. When the screen is not touched, interrupts does not occur.

If the control CONDIRQ bit is cleared to '0', the interrupts will always be generated. In case there is no pen detected on the screen then the coordinate data will be qualified as invalid, see section [5.1.7]. This result in a regular interrupt stream, as long as the host performs the read channel commands, independent of the screen being touched or not.

This working is illustrated in Figure 30.

Figure 30. AUTO Mode Flowchart

Figure 31 shows the I2C working in automatic mode. After the first sentence send throught the I2C to make the initialization, traffic is reduced as only reads are required.

The processing time is the necessary time for the SX8650 to makes the pendetection, the settling time (POWDLY) and the conversion. This time increases with the number of channel selected and the filter used. All succeeding conversions notifies the host by an interrupt signal and the host only needs to issue the I2C read command.

The reads occur at the RATE interval.

Figure 31. I2C working in AUTO mode

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### 6.3. PENDET Mode

The PENDET mode can be used if the host only needs to know if the screen has been touched or not and take from that information further actions. When pen detect circuitry is triggered the interrupt signal NIRQ will be generated and the status register bit 'PENIRQ' will be set. The bit is cleared by reading the status register RegStat.

Figure 32. PENDET Mode Flowchart

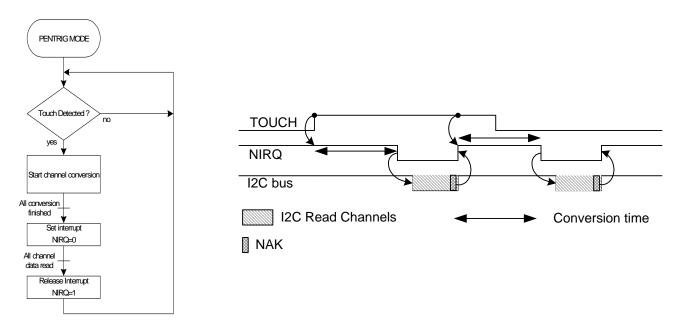

#### 6.4. PENTRIG Mode

The PENTRIG mode offers the best compromise between power consumption and coordinate throughput.

In this mode the SX8650 will wait until a pen is detected on the screen and then starts the coordinate conversions. The host will be signalled only when the screen is touched and coordinates are available.

The coordinate rate in pen trigger mode is determined by the speed of the host reading the channels and the conversion times of the channels. The host performs the minimum number of I2C commands in this mode.

The host has to wait for the NIRQ interrupt to make the acquisition of the datas.

The flowchart and the I2C working is illustrated in Figure 33.

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

Figure 33. PENTRIG Mode Flowchart and I2C working in PENTRIG mode

### 7. Application Information

This section describes in more detail application oriented data.

#### 7.1. Acquisition Setup

Prior to an acquisition, the SX8650 can be setup by writing the control registers. Registers are written by issuing the register write command. They can be read by issuing the read command. Please refer to the section [5.3].

If no registers are written, the circuit will start in manual mode.

#### 7.2. Channel Selection

The SX8650 can be setup to start a single channel conversion or to convert several channels in sequence. For a single conversion, the channel to be converted is determined from the CHAN(2:0) field in the command word (defined in Table 9).

Several channels can be acquired sequentially by setting the CHAN(2:0) field to SEQ. The channels will be sampled in the order defined by register RegChanMsk from MSB to LSB.

If a "one" is written in a channel mask, the corresponding channel will be sampled, in the opposite case, it is ignored and the next selected channel is chosen.

#### 7.3. Noise Reduction

A noisy environment can decrease the performance of the controller. For example, an LCD display located just under the touch screen can adds a lot of noise on the high impedance A/D converter inputs.

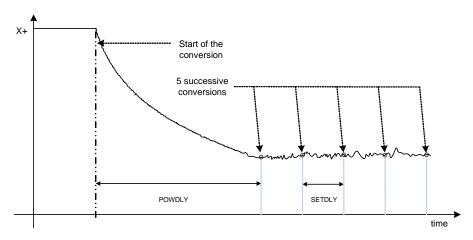

#### 7.3.1. **POWDLY**

In order to perform correct coordinates acquisition properly, some time must be given for the touch screen to reach a proper level. It is a function of the PCB trace resistance connecting the SX8650 to the touchscreen and also the capacitance of the touchscreen. If tau is this RC time constant then POWDLY duration must be programmed to 10 tau to reach 12 bit accuracy.

Adding a capacitor from the touch screen drivers to ground is a solution to minimize external noise. A low-pass filter created by the capacitor may increase settling time. Therefore, use POWDLY to stretch the acquisition period. POWDLY can be estimated by the following formula:  $PowDly = 10 \times Rtouch \times Ctouch$

#### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

Rtouch is the sum of the panel resistances plus any significant series input resistance, Rxtot + Rytot + Ri. Ctouch is the sum of the touch panel capacitance plus any noise filtering and routing capacitances.

#### 7.3.2. **SETDLY**

A second method of noise filtering uses an averaging filter as described in section [5] (Data processing). In this case, the chip will sequence up to 7 conversions on each channel. The parameter SETDLY sets the settling time between the consecutive conversions.

In most applications, SETDLY can be set to 0. In some particular applications, where accuracy of 1LSB is required and Ctouch is less than 100nF a specific value should be determined.

Figure 34. POWDLY and SETDLY timing with FILT=2

#### 7.3.3. AUX Input

An alternate conversion trigger method can be used if the host system provides additional digital signals that indicate noisy or noise-free periods. The SX8650 can be set up to start conversions triggered by the AUX pin. A rising edge, a falling edge or both can trigger the conversion. To enter this mode, AUXACQ must be set to a different value than '00' as defined in Table 6. The AUX edge will first trigger the bias delay (POWDLY). Following the programmed delay, the channel acquisition takes place.

#### 7.4. Interrupt Generation

An interrupt (NIRQ=0) will be generated:

- During the power-up phase or after a reset

- After completion of a conversion in MANUAL, PENTRIG or AUTO mode. CONVIRQ (bit [7] of RegStat) will be set at the same time.

- After a touch on the panel is detected in PENDET mode. PENIRQ (bit [6] of RegStat) will be set at the same time.

The NIRQ will be released and pulled high(NIRQ=1) by the external pull-up resistor:

- When the power-up phase is finished

- When the host read all channels data that were previously converted by the SX8650 in MANUAL, PENTRIG or AUTO

mode. CONVIRQ will be cleared at the same time.

- When the host read the status register in PENDET mode. PENIRQ, will be cleared at the same time.

An active NIRQ (low) needs to be cleared before any new conversions will occur.

#### 7.5. Coordinate Throughput Rate

The coordinate throughput rate depends on the following factors:

- The I2C communication time: T<sub>com</sub>

- The conversion time : T<sub>conv</sub>

The coordinate rate is the frequency to get the X, Y, Z1 and Z2 coordinate:  $CoordRate = \frac{1}{T_{com} + T_{conv}}$

### **ADVANCED COMMUNICATIONS & SENSING**

DATASHEET

#### 7.5.1. I2C Communication Time

The minimun time to read the channel data in PENTRIG mode is :  $T_{com} = (8 + 16 \times N_{chan}) \times T_{SPI}$

The highest throughput will be obtained with a I2C frequency of 5MHz when the host read the channel data as quickly as possible after the NIRQ falling edge.

#### 7.5.2. Conversion Time

The maximum possible throughput can be estimated with the following equation

$$Tconv(us) = 47 \cdot Tosc + N_{chan} \cdot (POWDLY + (N_{filt} - 1) \cdot SETDLY + (21N_{filt} + 1) \cdot Tosc)$$

with:

- N<sub>filt</sub> = {1,3,5,7} based on the order defined for the filter FILT (see Figure 4).

- N<sub>chan</sub> = {1,2,3,4,5} based on the number of channels defined in RegChanMsk