# **Application Note: SY5955**

PFC+LLC Combo Controller

# **General Description**

The SY5955 is a PFC+LLC combo controller, which integrates a Boost PFC controller and a resonant half-bridge controller.

The Boost converter works in CrM/DCM mode to minimize switching losses and get better EMI performance. Proprietary control is adopted to get unity PF and lowest THD. Burst function increases efficiency at low load. Reliable input BO/BI protection, Boost output OVP/UVP, over current protection, Boost feedback protection guarantees safety work.

The LLC converter with proprietary control achieves fast dynamic response and easy loop compensation parameters design. The peripheral devices count is greatly reduced to save BOM cost. The SY5955 also has Output OVP, OTP and OLP for safety operation.

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY5955FFP       | SOP16        |      |

## **Features**

- PF>0.95, THD<5%

- Boost Quasi Resonant (QR) Operation

- Boost Burst Operation at Light Load

- LLC Fast Dynamic Response

- LLC Integrated Half Bridge Driver

- Input BO/BI Protection

- Boost Output, LLC Output OVP Protection

- Cycle by Cycle Peak Current Protection

- Over Temperature Protection

- LLC Capacitive Mode Protection

## **Applications**

- LCD Television

- Desktop, all in one PC

- Adapter, Charger

- Printer

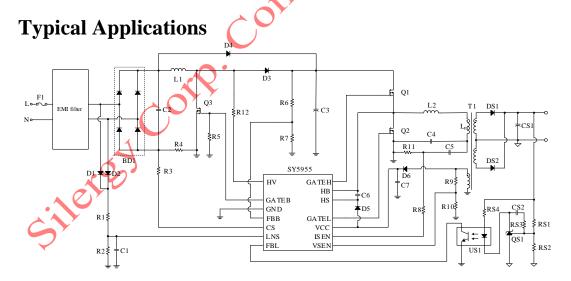

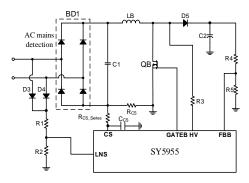

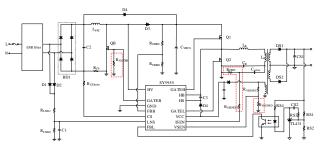

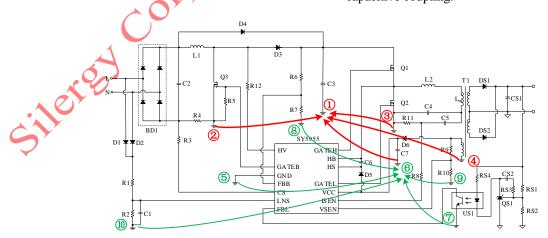

**Figure Typical Applications**

## Pinout (top view)

Top Mark: DCYxyz (device code: DCY, x=year code, y=week code, z= lot number code)

| Pin number | Pin Name | Pin Description                                                    |

|------------|----------|--------------------------------------------------------------------|

| 1          | GATEH    | Half bridge controller high side drive pin.                        |

| 2          | НВ       | Half bridge controller high side ground pin.                       |

| 3          | HS       | Half bridge controller high side bias supply pin.                  |

| 4          | NC       | Not connected.                                                     |

| 5          | VCC      | Bias supply pin.                                                   |

| 6          | ISEN     | Half bridge controller resonant current sense pin.                 |

| 7          | VSEN     | Half bridge controller output voltage sense pin.                   |

| 8          | FBL      | Half bridge controller feedback pin.                               |

| 9          | LNS      | PFC controller input voltage sense pin.                            |

| 10         | CS       | PFC controller input current sense pin.                            |

| 11         | FBB      | PFC controller output feedback pin.                                |

| 12         | GATEB    | PFC controller gate drive pin.                                     |

| 13         | GND      | Ground pin.                                                        |

| 14         | GATEL    | Half bridge controller low side drive pin.                         |

| 15         | NC       | Not connected.                                                     |

| 16         | HV       | High voltage Start-up pin. combined with Boost QR detect function. |

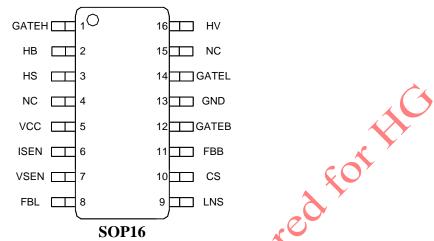

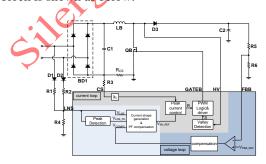

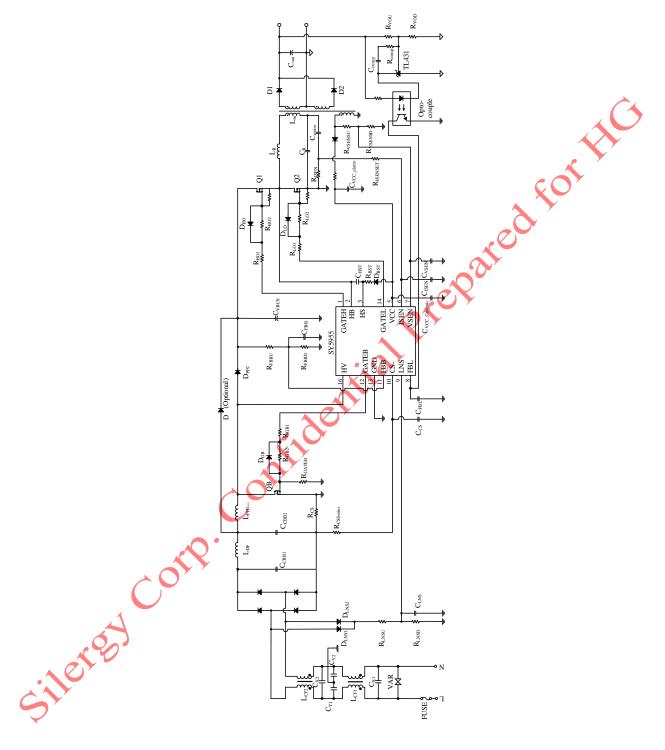

# **Block Diagram**

Figure. Block Diagram

# **Absolute Maximum Ratings** (Note 1)

| 8 . , ,                                          |                    |

|--------------------------------------------------|--------------------|

| HV, HS                                           |                    |

| HV, HS                                           |                    |

| GATEH                                            | HB-0.3V ~ HB+15V   |

| GATEHVCC                                         |                    |

| I <sub>CS</sub> (Note2)                          | $-10mA \sim +20mA$ |

| CS, ISEN                                         |                    |

| FBB, LNS, FBL, VSEN                              |                    |

| GATEB, GATED                                     |                    |

| Power Dissipation, @ T <sub>A</sub> = 25°C SOP16 | 1.02W              |

| Package Thermal Resistance (Note 3)              |                    |

| SOP16, θ <sub>JA</sub>                           | 122°C/W            |

| SOP16, θ <sub>JC</sub>                           |                    |

| Maximum Junction Temperature                     |                    |

| Lead Temperature (Soldering, 10 sec.)            | 260°C              |

| Storage Temperature Range                        |                    |

## **Electrical Characteristics**

$(V_{VCC} = 15V \text{ (Note 4), } T_A = 25^{\circ}\text{C unless otherwise specified)}$

| Parameter                                  | Symbol                 | Test Conditions                                                                       | Min              | Тур              | Max              | Unit |

|--------------------------------------------|------------------------|---------------------------------------------------------------------------------------|------------------|------------------|------------------|------|

| VCC Pin Section                            |                        |                                                                                       |                  |                  |                  |      |

| VCC Turn-on Threshold                      | V <sub>VCC_ON</sub>    |                                                                                       | 23               | 24               | 25               | Y.   |

| VCC Turn-off Threshold                     | V <sub>VCC_OFF</sub>   |                                                                                       | 8.5              | 9                | 9.5              | V    |

| VCC Low for HV Start<br>Threshold          | V <sub>VCC_LO</sub>    |                                                                                       | 8.9              | 9.5              | 10               | V    |

| VCC Short Circuit<br>Protection            | V <sub>VCC_SCP</sub>   |                                                                                       | 0.3              | 0.7              | (13)             | V    |

| VCC Shunt Voltage<br>Protection            | V <sub>VCC_Shunt</sub> |                                                                                       | 25.4             | 26               | 27.5             | V    |

| VCC OVP Threshold                          | $V_{VCC\_OVP}$         |                                                                                       | VCC<br>Shunt+0.4 | VCC<br>Shunt+0.7 | VCC<br>Shunt+1.2 | V    |

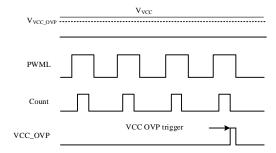

| VCC OVP Trigger Number of Switching Cycles | N <sub>VCC_OVP</sub>   |                                                                                       |                  | 4                |                  |      |

| Quiescent Current                          | $I_Q$                  |                                                                                       | 1,3              | 1.7              | 2.1              | mA   |

| Standby Current                            | $I_{SDY}$              |                                                                                       | 380              | 600              | 820              | μΑ   |

| Enable Off Current                         | I <sub>ENOFF</sub>     |                                                                                       | ,                |                  | 270              | μΑ   |

| VCC Max Shunt Current                      | $I_{Shunt}$            |                                                                                       | 8                | 12               | 16               | mA   |

| VCC Fault Restart Timer                    | $T_{VCC\_timeout}$     |                                                                                       | 0.69             | 1                | 1.11             | s    |

| HV Pin Section                             |                        | Yes                                                                                   |                  |                  |                  |      |

| HV Startup Current at VCC SCP              | I <sub>ST_L</sub>      |                                                                                       | 0.36             | 0.5              | 0.6              | mA   |

| HV Startup Current at<br>Normal State      | I <sub>ST_N</sub>      |                                                                                       | 5.4              | 6                | 6.6              | mA   |

| QR dV/dt Sense Threshold                   | $V_{\mathrm{HV\_TH}}$  |                                                                                       | 28               | 40               | 52               | V/µs |

| QR Time Out Time                           | $T_{ZCS}$              |                                                                                       | 2.3              | 3.3              | 3.9              | μs   |

| FBB Pin Section                            | N .                    |                                                                                       |                  |                  |                  |      |

| Boost Output Regulation<br>Reference       | $V_{FBB\_REF}$         |                                                                                       | 1.18             | 1.2              | 1.22             | V    |

| Boost Output UVP Threshold                 | $V_{FBB\_UVP}$         | 20%                                                                                   | 175              | 200              | 225              | mV   |

| Boost Output OVP                           | $V_{FBB\_OVP}$         | 107.5%                                                                                | 1.25             | 1.29             | 1.33             | V    |

| Threshold                                  | $V_{FBB\_OVP}$         | Vcompv <vcompv_d< td=""><td>1.21</td><td>1.25</td><td>1.29</td><td>V</td></vcompv_d<> | 1.21             | 1.25             | 1.29             | V    |

| Boost & LLC Disable Threshold              | V <sub>FBB_ENB</sub>   |                                                                                       | 2                | 2.3              | 2.5              | V    |

| LLC Input BO Threshold                     | $V_{FBB\_BO}$          |                                                                                       | 700              | 750              | 800              | mV   |

| LLC Input BI Threshold                     | $V_{FBB\_BI}$          |                                                                                       | 880              | 950              | 1000             | mV   |

| Pin Open Detection Source<br>Current       | I <sub>FBB_OPEN</sub>  |                                                                                       | 50               | 100              | 200              | nA   |

| CS Pin Section                             |                        |                                                                                       |                  |                  |                  |      |

| Boost Peak Current Limit                   | V <sub>CS_LIMIT</sub>  |                                                                                       | -665             | -700             | -735             | mV   |

|                                   | I                         |                         |                                                   |                      |                      |     |

|-----------------------------------|---------------------------|-------------------------|---------------------------------------------------|----------------------|----------------------|-----|

| Inductor Saturation or            | **                        |                         | <b>5</b> 0.5                                      | 0.50                 | 00.7                 | **  |

| Short-circuit Protection          | V <sub>LS_LIMIT</sub>     |                         | -795                                              | -850                 | -895                 | mV  |

| Limit                             |                           |                         |                                                   |                      |                      |     |

| Inductor Saturation or            |                           |                         |                                                   |                      |                      |     |

| Short-circuit Protection          | N <sub>LStimer</sub>      |                         |                                                   | 4                    |                      |     |

| Trigger Number                    |                           |                         |                                                   |                      |                      |     |

| Boost Current Sense               |                           |                         |                                                   |                      |                      |     |

| Resistor Short Circuit            | $V_{CS\_RSCP}$            |                         | -65                                               | -50                  | -35                  | mV  |

| Protection Threshold              |                           |                         |                                                   |                      | 4                    |     |

| Boost Current Sense               |                           |                         |                                                   |                      | 40                   |     |

| Resistor Short Circuit            | T <sub>CS_RSCP</sub>      |                         | 2.8                                               | 4                    | 5.2                  | μs  |

| Protection Timer                  |                           |                         |                                                   |                      | A /                  |     |

| LNS Pin Section                   |                           |                         |                                                   |                      | COY                  |     |

| Boost Input Brown Out             |                           |                         |                                                   |                      |                      |     |

| Timer                             | T <sub>PROT_LNS_BO</sub>  |                         | 44                                                | 64                   | 75                   | ms  |

| Boost Input Brown Out             |                           |                         |                                                   | 0                    |                      |     |

| Threshold                         | $V_{LNS\_BO}$             |                         | 370                                               | 400                  | 430                  | mV  |

| Boost Input Brown in              |                           |                         |                                                   |                      |                      |     |

| Threshold                         | $V_{LNS\_BI}$             |                         | 440 🔏                                             | 470                  | 500                  | mV  |

| Pin Open Detection Source         |                           |                         |                                                   |                      |                      |     |

|                                   | I <sub>LNS_OPEN</sub>     |                         | 50                                                | 100                  | 200                  | nA  |

| CATERD B: G 4                     |                           |                         | <del>\ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ \ </del> |                      |                      |     |

| GATEB Pin Section                 |                           |                         |                                                   |                      |                      |     |

| Drive Limit Voltage               | $V_{GATEB\_DRV}$          | • 0                     | 10.2                                              | 11                   | 11.8                 | V   |

| Drive Voltage within              | V                         |                         | (                                                 | 0                    | 10                   | 17  |

| $T_{ m on,min.B}$                 | $V_{GATEB\_TH}$           |                         | 6                                                 | 8                    | 10                   | V   |

| Source Current                    | I <sub>SOURCE_GATEB</sub> | V <sub>GATEB</sub> =8V  | -800                                              | -600                 | -400                 | mA  |

|                                   |                           | V <sub>GATEB</sub> =2V  | 0.6                                               |                      |                      | Α   |

| Sink Current                      | I <sub>SINK_GATEB</sub>   | * *                     |                                                   |                      |                      | 7.1 |

|                                   | _                         | V <sub>GATEB</sub> =11V | 0.98                                              | 1.4                  | 1.82                 | Α   |

| Boost Minimum ON Time             | Ton_min_b                 | <b>Y</b>                | 200                                               | 300                  | 420                  | ns  |

| Boost Maximum ON Time             | T <sub>ON_MAX_B</sub>     |                         | 20                                                | 30                   | 40                   | μs  |

| Boost Minimum OFF Time            | Toff_MIN_B                |                         | 0.75                                              | 1                    | 1.25                 | μs  |

| Boost Maximum OFF                 |                           |                         | *****                                             | =                    |                      |     |

| Time                              | Toff_max_b                |                         | 21                                                | 30                   | 40                   | μs  |

| Toffmax if CS<-850mV              | ,                         |                         |                                                   |                      |                      |     |

|                                   | $T_{offmax}$              |                         | 70                                                | 100                  | 142                  | μs  |

| and within T <sub>LLC,delay</sub> |                           |                         |                                                   |                      |                      |     |

| Boost Minimum Switching           | T <sub>SW_MIN_B</sub>     |                         | 2                                                 | 2.9                  | 3.8                  | μs  |

| Period Period                     |                           |                         |                                                   |                      |                      |     |

| FBL Pin Section                   | ı                         | l                       |                                                   |                      | 1                    |     |

| Open Loop Protection              | I <sub>FBL_200%</sub>     |                         | 14                                                | 22                   | 29                   | μA  |

| Threshold Current                 | ≠FDL_2UU%                 |                         | 17                                                |                      | 2)                   | μιι |

| Open Loop Protection              |                           |                         |                                                   |                      |                      |     |

| Trigger Time                      | $T_{OLP}$                 |                         | 44                                                | 64                   | 75                   | ms  |

| 111gget 11ttle                    |                           |                         |                                                   |                      |                      |     |

| ISEN Pin Section                  | ISEN Pin Section          |                         |                                                   |                      |                      |     |

| Resonant Current Sample           |                           |                         |                                                   |                      |                      |     |

| Resistor Calculate                | k                         |                         | $3.1 \times 10^{-7}$                              | 4.1×10 <sup>-7</sup> | 5.1×10 <sup>-7</sup> |     |

| Coefficient                       |                           |                         |                                                   |                      |                      |     |

| <u> </u>                          | L                         |                         |                                                   |                      | I.                   |     |

| ISEN Zero Current Sense                                             |                           | Detect as≥0             | -55      | -40  | -30  | mV   |

|---------------------------------------------------------------------|---------------------------|-------------------------|----------|------|------|------|

| Threshold                                                           |                           | Detect as≤0             | 30       | 40   | 55   | mV   |

| LLC Current Sense<br>Resistor Short Circuit<br>Protection Threshold | V <sub>ISEN_RSCP</sub>    |                         | 35       | 50   | 65   | mV   |

| LLC Current Sense<br>Resistor Short Circuit<br>Protection Timer     | T <sub>ISEN_RSCP</sub>    |                         | 2.8      | 4    | 5.2  | μs   |

|                                                                     |                           | R <sub>GATEB</sub> =30k | ±610     | ±650 | ±700 | mV   |

| ISEN Max Current Limit                                              | V <sub>ISEN_L2</sub>      | R <sub>GATEB</sub> =20k | ±700     | ±750 | ±800 | mV   |

|                                                                     |                           | R <sub>GATEB</sub> =10k | ±800     | ±850 | ±900 | mV   |

|                                                                     |                           | R <sub>GATEB</sub> =30k | ±510     | ±550 | ±580 | mV   |

| ISEN Soft Current Limit                                             | V <sub>ISEN_L1</sub>      | R <sub>GATEB</sub> =20k | ±610     | ±650 | ±680 | mV   |

|                                                                     |                           | R <sub>GATEB</sub> =10k | ±710     | ±750 | ±790 | mV   |

| ISEN Max Current Limit Protection Timer                             | T <sub>ILL2_protect</sub> |                         | 22       | 32   | 36   | ms   |

| ISEN Soft Current Limit Protection Timer                            | T <sub>ILL1_protect</sub> |                         | 179      | 256  | 282  | ms   |

| VSEN Pin Section                                                    |                           | _                       | -        |      |      |      |

| LLC Output OVP Counter                                              | Novp_count                | . 0                     | <b>Y</b> | 4    |      |      |

| LLC Output OVP<br>Reference                                         | V <sub>VSEN_OVP</sub>     |                         | 1.42     | 1.5  | 1.54 | V    |

| LLC Disable Threshold                                               | V <sub>VSEN_ENB</sub>     | 207                     | 1.84     | 2.3  | 2.46 | V    |

| LLC Output UVP<br>Reference                                         | V <sub>VSEN_UVP</sub>     | I <sub>FBL</sub> <30μA  | 370      | 400  | 425  | mV   |

| LLC Output UVP Timer                                                | T <sub>VSEN_UVP</sub>     |                         | 11       | 16   | 21   | ms   |

| Pin Open Detection Source<br>Current                                | Ivsen_open                |                         | 50       | 100  | 200  | nA   |

| <b>GATEL Pin Section</b>                                            |                           |                         |          |      |      |      |

| Drive Limit Voltage                                                 | V <sub>GATEL_DRV</sub>    |                         | 10.2     | 11   | 12.5 | V    |

| Source Current                                                      | I <sub>SOURCE_GATEL</sub> | V <sub>GATEL</sub> =4V  | -460     | -350 | -240 | mA   |

| Sink Current                                                        | Ĭ                         | V <sub>GATEL</sub> =2V  | 0.4      | 0.6  | 0.8  | A    |

| Sink Current                                                        | I <sub>SINK_GATEL</sub>   | V <sub>GATEL</sub> =11V | 0.98     | 1.4  | 1.82 | A    |

| LLC Minimum on Time                                                 | T <sub>ON_MIN_L</sub>     |                         | 280      | 400  | 520  | ns   |

| LLC Maximum on Time                                                 | T <sub>ON_MAX_L</sub>     |                         | 14       | 20   | 26   | μs   |

| Bootstrap Charge Time                                               | $T_{BST}$                 |                         | 3.5      | 5    | 6.5  | μs   |

| HB Pin Section                                                      |                           |                         |          |      |      |      |

| dV/dt Threshold for HB<br>ZVS                                       | dV/dt <sub>zvs</sub>      |                         | 56       | 80   | 104  | V/µs |

| Minimum Dead Time for ZVS                                           | T <sub>D_MIN</sub>        |                         | 126      | 180  | 234  | ns   |

| Maximum Dead Time for ZVS                                           | T <sub>D_MAX</sub>        |                         | 0.85     | 1.05 | 1.25 | μs   |

| HS Pin Section (Signal Refer to HB)      |                                        |                                         |      |      |      |    |  |

|------------------------------------------|----------------------------------------|-----------------------------------------|------|------|------|----|--|

| HS Turn-on Threshold                     | V <sub>HS_ON</sub>                     |                                         | 7    | 7.5  | 8    | V  |  |

| HS Turn-off Threshold                    | V <sub>HS_OFF</sub>                    |                                         | 5.8  | 6.5  | 7.2  | V  |  |

| HS Quiescent Current                     | $I_{Q\_HS}$                            |                                         | 14   | 20   | 26   | μA |  |

| <b>GATEH Pin Section (Signa</b>          | GATEH Pin Section (Signal Refer to HB) |                                         |      |      |      |    |  |

| Drive Limit Voltage                      | V <sub>GATEH_DRV</sub>                 |                                         | 10.2 | 11   | 12.5 | V  |  |

| Source Current                           | I <sub>SOURCE_GATEH</sub>              | V <sub>GATEH</sub> -V <sub>HB</sub> =4V | -460 | -350 | -240 | mA |  |

| Sinh Comment                             | т                                      | $V_{GATEH}$ - $V_{HB}$ =2 $V$           | 0.4  | 0.6  | 0.8  | A  |  |

| Sink Current                             | I <sub>SINK_GATEH</sub>                | $V_{GATEH}$ - $V_{HB}$ =11 $V$          | 0.98 | 1.4  | 1.82 | A  |  |

| Thermal Section                          |                                        |                                         |      |      |      |    |  |

| Thermal Shut Down Temperature            | $T_{SD}$                               |                                         | 130  | 150  | 170  | °C |  |

| Thermal Shut Down Hysteresis Temperature | T <sub>TSD_HYST</sub>                  |                                         |      | 25   |      | °C |  |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2: IC Internal diode will clamp the voltage of CS pin. During IC operating, Ics should not exceed -10mA if Vcs reaches -1.1V.

Note 3:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25$  C on a low effective single layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard.

Note 4: Increase VCC pin voltage gradually higher than  $V_{VCC\ ON}$  voltage then turn down to 15V.

## Introduction

The SY5955 is a PFC+LLC combo controller; it integrates a Boost PFC controller and a resonant halfbridge LLC controller.

The Boost converter works in CrM/DCM mode to minimize switching losses and get better EMI performance. Average current control is adopted to get unity PF and the lowest THD. Burst function increases efficiency at low load. Reliable input BO/BI protection, Boost output OVP/UVP, over current protection, Boost feedback protection guarantees safety work.

The LLC converter adopts integrated current mode control to get fast dynamic response and easy loop compensation parameters design, also peripheral capacitor sense circuit is eliminated. Four level Burst point can be set simply and Burst period can be well regulated. Within the whole load range, from full load to no load, high efficiency and low audio noise can be achieved.

## **Function Description**

### **PFC Section**

#### **PFC Operation Overview**

The PFC operates in Quasi-Resonant (QR) or Discontinuous Conduction Mode (DCM) using valle detection to reduce the switch-on losses. The PEC is designed as a Boost converter with a fixed output voltage. An advantage of a fixed Boost converter is that the LLC can be designed to a high input voltage, making the LLC design easier. Another advantage of the fixed Boost converter is the option to use a smaller Boost capacitor value or to have a significant longer hold-up time. To improve efficiency at low output load, the system can be operated in Burst mode.

#### **Boost PFC Basic Control Principle**

The average current mode is adopted which can automatically compensate parasitic parameters to achieve the best PF/THD. The average current control block is shown as below:

Fig. 1 PFC Control Block

In the block, voltage loop generates compensation signal V<sub>COMPV</sub>. Current shape circuit generates current reference with PF compensation. The current loop regulates the input current to sine reference.

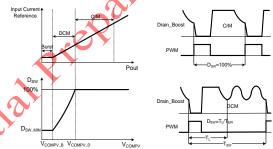

#### **Power Curve and Modes of Operation**

At heavy load, the PFC works at CrM. The duty cycle D<sub>SW</sub> is 100%. In order to increase efficiency at light load, the Boost works in DCM mode. When PFC output power decreases, the V<sub>COMPV</sub> which is generated by PFC output voltage control loop will drop. When it drops to below V<sub>COMPV D</sub>, DCM time increases with the decrease of V<sub>COMPV</sub>. The circuit controls the time that inductor with current (T<sub>L</sub>) to be a partial of switching period (T<sub>SW</sub>). If Rcs is designed in typical value which is shown in peak current control section. The duty cycle D<sub>SW</sub> drops from 100% to 1% with PFC output power Pout drops from 25% to 1%.

Fig. 2 Power Curve and Modes of Operation

At extremely low load, IC work in max toff 120us, if load continuous decline, IC will trigger V<sub>FFB\_OVP</sub> 1.25V, enter Burst mode.

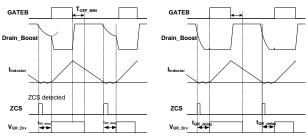

#### **Valley Detection**

The Boost stage works in quasi resonant mode to decrease switching power loss. The power MOSFET QB will turn on at resonant valley which is detected by sensing Drain voltage via HV pin. To prevent SY5955 damaged when surge energy input, a resistor is connected in series between HV pin and MOSFET Drain. The resistance value is recommended from  $1k\Omega$ to  $5k\Omega$ ;  $V_{Drain}$  slope detection circuit is integrated inside the IC. When zero crossing of PFC inductor current (ZCS) is detected, then after a fixed delay time t<sub>OR delay</sub>(300ns), MOSFET QB turns on.

Fig.3 Valley Detection

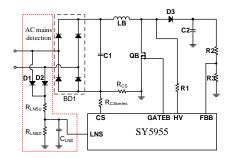

#### **AC Mains Sensing**

AC mains sensing is through LNS pin. The LNS pin both sensing the constant value of the AC mains and the peak value of the AC mains. The AC mains peak value is worked as feed forward to change input current reference. Normally, the AC mains peak value is detected every half line cycle.

Typically, 100us filter time should be added to LNS pin considering noise immunity.

The AC mains sensing circuit is shown as below:

Fig.4 AC Mains Sensing Circuit

#### **PFC Output Voltage Regulation**

A resistive divider between the PFC output voltage, the FBB and GND pin sets the Boost output voltage value. When in regulation, the voltage on the FBB pin is regulated at 1.2V.

The regulated Boost PFC output voltage can be calculated as followed:

calculated as followed:

$$V_{\text{PFC}} = \frac{R_{\text{FBBU}} + R_{\text{FBBD}}}{R_{\text{FBBD}}} \times V_{\text{FBB\_REF}}$$

Typically, the system values are:

$R_{FBBU}=6M\Omega\sim12M\Omega$

$V_{FBB\_REF}=1.2V$

200us filter time is suggested to add to FBB pin for noise immunity consideration.

For example, to obtain a nominal PFC output at 390V and  $R_{FBBU}$  is set at  $6M\Omega$ , the  $R_{FBBD}$  should be  $18.5k\Omega$ , and the  $C_{FBB}$  is suggested to be  $10nF\sim22nF$  and the  $C_{FBB}$  should be close to FBB pin.

## **PFC Current Sensing**

To get a unity PF, the input current should follow the input voltage shape. To minimize the input current distortion due to  $V_{\text{COMPV}}$  ripple under high line input, the peak input voltage information ( $V_{\text{LNS\_PK}}$ ) is fed forward to current reference. The input voltage is sensed via the resistor divider as  $V_{\text{LNS}}$ , the peak input voltage  $V_{\text{LNS\_PK}}$  detection is also integrated, Ki is an internal transfer coefficient, so the input current reference  $V_{\text{IIN\_REF}}$  is:

$$V_{IIN\_REF} = \frac{V_{COMPV} \times V_{LNS}}{Ki \times V_{LNS}^2}$$

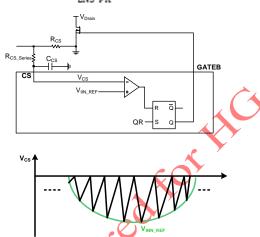

Fig.5 Peak Current Control

$V_{CS}$  is compared with  $V_{IIN\_REF}$ , when the peak current is touched, then MOSFET will be turned off. After inductor current decreases to 0, QR signal begins next switching cycle.

To design the lowest AC input and full load, the PFC works at CrM mode, the R<sub>CS</sub> can be decided by:

$$R_{CS} \approx \frac{V_{CS\_LIMIT} \times V_{AC\_MIN}}{2\sqrt{2} \times P_{IN}}$$

Where the  $V_{CS\ LIMIT}$  is the current limit point of PFC.

If there is no NTC in the AC input loop, during the start-up stage, there is usually a large surge current above 100A, which may cause a large voltage drop on the  $R_{CS\_Series}$  is used to protect the CS pin from the surge current. The circuit is shown as below:

Fig.6 VR<sub>CS</sub> Limit Circuit

CS series resistor  $R_{\text{CS\_Series}}$  is suggested within the range of  $100\Omega{\sim}300\Omega.$

For noise immunity consideration and signal delay trade off, a 100pF~470pF capacitor C<sub>CS</sub> is suggested to use and close to the CS pin.

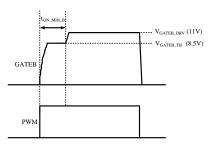

#### **PFC Driver**

In order to have good EMI performance, an optimized two-section gate driver method is adopted. In the first section, the GATEB rises to  $V_{\rm GATEB\_TH}$  (8.5V), and in the second section, after the minimum on time  $t_{\rm ON\_MIN\_B}$  has arrived, GATEB rises from  $V_{\rm GATEB\_TH}$  to  $V_{\rm GATEB\_DRV}(11V)$ , The gate voltage is shown in the figure below.

Fig.7 GATEB Waveform

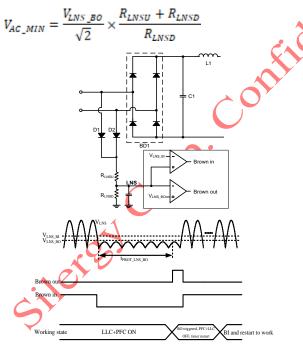

#### **Brown In and Brown Out**

To prevent the Boost working in a very low input voltage (which cause too much heat and very low efficiency), the input brown out (BO) is sensed by LNS pin. When  $V_{LNS\_PK} < V_{LNS\_BO}$  continuously for  $t_{PROT\_LNS\_BO}$ , input BO is detected. So, the protected minimum input voltage  $V_{AC\_MIN(RMS)}$  is,

Fig.8 Brown Out Protection

After the input BO protection triggered, both two stages will stop switching and enter error timer restart. After the BO is triggered, HV will start to draw current to prevent LNS from floating high. After error timer

restart is done and if  $V_{LNS\_PK} > V_{LNS\_BI}$ , the Boost will work with soft start again.

Typically, the  $R_{LNSU}$  is recommended within the range of  $5M\Omega$  to  $12M\Omega$ .

For example, if the Brown out point is set at 70V (AC RMS), the  $R_{LNSU}$  is set at  $6M\Omega$ , then the  $R_{LNSD}$  can be calculated as  $24.3k\Omega$ . A 1nF capacitor is suggested to be added between LNS pin and GND for the noise immunity consideration.

#### PFC Output UVP and OVP

PFC output under voltage protection (UVP) protects output under voltage, FBB low side resistor or FBB pin short-circuit.

If  $V_{FBB}$ < $V_{FBB\_UVP}$ , Boost stage stops switching unless  $V_{FBB}$ > $V_{FBB\_UVP}$  plus a hysteresis voltage.

Fig.9 FBB UVP

PFC output over voltage protection (FBB OVP) protects (1) output voltage overshot due to slow loop response or fast load step, (2) input over voltage due to line voltage jitter, wrong line voltage plugs in or surge test, (3) FBB low side resistor or FBB pin open circuit.

If  $V_{FBB}$ > $V_{FBB\_OVP}$ , Boost stage stops switching unless  $V_{FBB}$ < $V_{FBB}$  ovp minus a hysteresis voltage.

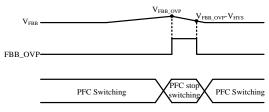

Fig.10 FBB OVP

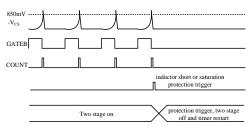

## <u>PFC Inductor Short Circuit or Saturation</u> <u>Protection</u>

In order to prevent the damage of IC and MOS, the inductor short circuit protection is added. If at every PFC switching cycle  $V_{CS}$  continuously 4 times reaches to -850mV limit, it triggers inductor short circuit protection and both two stages will stop working and the IC timeout restart.

Fig.11 Inductor Short or Saturation Protection

#### PFC+LLC Two Stage Disable Function

For extremely low standby power requirement, the PFC and the LLC stage can be both disabled by applying a voltage over 2.3V on FBB pin.

### **LLC Section**

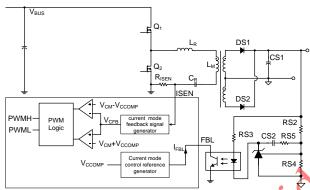

#### **Current Mode Control**

Fig.12 Control Mode Control Block

A certain current mode control is adopted in the LLC stage inner loop to achieve the fast dynamic response.

The outer loop controls output voltage via the amplifier or TL431 regulator in different applications. Via compensation circuit and opto-coupler, the compensation information will be transferred to primary side via to get  $t_{\rm FBL}$ . The  $V_{\rm CCOMP}$  is compensation voltage inside IC.

$V_{CFB}$  inside the IC demonstrates current loop feedback signal.  $V_{CFB}$  has a linear relationship with the output power. The voltage changes of  $V_{CFB}$  are a result of the primary current that drives the power conversion.

V<sub>CFB</sub> is compared with V<sub>CM</sub>-V<sub>CCOMP</sub> and V<sub>CM</sub>+V<sub>CCOMP</sub>.

If V<sub>CFB</sub> V<sub>CM</sub>-V<sub>CCOMP</sub>, PWMH=1, PWML=0, high side MOS turned on.

If  $V_{CFB} > V_{CM} + V_{CCOMP}$  PWMH=0, PWML=1, low side MOS turned on.

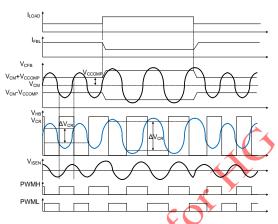

The typical waveforms are shown as below, when load increases,  $V_{\text{CCOMP}}$  increases. Otherwise,  $V_{\text{CCOMP}}$  decreases.

Fig.13Current Mode Control Waveform

#### **RISEN Design Principle**

The parameters design in this charge control is shown as follows,

$$P_{IN} = V_{BUS} \times C_R \times \Delta V_{CR} \times f_{SW} + C_i \times V_{BUS}^2 \times f_{SW}$$

$C_j$  is the total junction capacitance. PIN is the LLC input power. The CR is the resonant capacitor, the  $\Delta$ CR is the voltage change on the CR at PWMH=1 stage.

$$\Delta V_{GR} = \frac{P_{IN} - C_{j} \times V_{BUS}^{2} \times f_{SW}}{V_{BUS} \times C_{R} \times f_{SW}}$$

The relationship between  $V_{CCOMP}$  and  $\Delta V_{CR}$  is,

$$\Delta V_{CR} = V_{CCOMP} \times \frac{2 \times k}{C_R \times R_{ISEN}}$$

And the current sense resistor R<sub>ISEN</sub> could be chose to,

$$R_{ISEN} = \frac{2 \times V_{CCOMP\_OPP} \times k \times V_{BUS} \times f_{SW}}{P_{IN} - C_i \times V_{BUS}^2 \times f_{SW}}$$

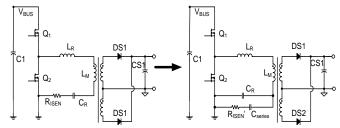

Where k is the  $R_{\rm ISEN}$  calculation coefficient. k can be set suitable for different working frequency application.  $V_{\rm CCOMP\_OPP}$  is the IC internal voltage threshold. Its typical value is 750mV. The setting principle will be demonstrated in external setting principal section. For typical application, there is a preferable resonant current sensing method as shown below.

Fig.14 Resonant Current Sense Circuit

$$R'_{ISEN} = \frac{C_R}{C_{series}} R_{ISEN}$$

In this way, the loss of sensing resistor can be decreased.

For example, if the designed operating frequency fsw=100kHz, the input voltage  $V_{BUS}$ =400V, the Maximum input power  $P_{IN\_OPP}$ =120W, the resonant capacitor  $C_R$ =33nF, current split capacitor  $C_{series}$ =200pF,  $V_{CCOMP\_100\%}$ =600mV,

$$R_{ISEN} = \frac{2 \times V_{CCOMP,100\%} \times K \times V_{BUS} \times T_{SW}}{P_{IN,100\%} - C_{j} \times V_{BUS} ^{2} \times T_{SW}} = 0.187\Omega$$

Thus,  $R_{ISEN}' = (33/0.2) * R_{ISEN} = 54\Omega$

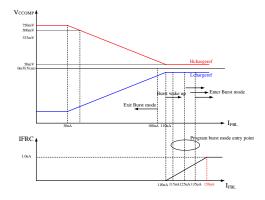

#### **Power Curve and Operation Modes**

The power curve is shown as below.

Fig.15 Power Curve and Modes of Operation

There are two operation modes from heavy load to light load: (1) CCM mode; (2) Burst mode.

In CCM mode, The CCM mode operates in continuous switching with a 50 % duty cycle, which is like the traditional LLC operation via frequency control. In all operation modes, the current mode control is adopted and the adaptive non-overlap function based on the HB end-of-slope detection switches on the gate drive.

In burst mode, each burst cycle consists of a series of CCM cycles and sleep time. The transition level of entering burst mode can be preset using VSEN pin. This preset principle will be demonstrated in external setting principal section.

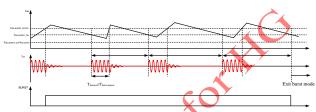

### **Burst Mode Operation**

As the output power decreasing, when the  $I_{FBL}$  rises to over the Burst mode entry threshold which can be set through VSEN pin external resistor, the IC enters sleep mode and the LLC stops switching.

When  $I_{FBL}$  drops below  $I_{FBL\_BST\_ON}$  and still higher than  $I_{FBL\_BST\_ON}$  - $I_{FBL\_BHYS}$ , LLC starts to work. The minimum burst on time  $T_{burst\_minon\_ini}$  is 60us. Before entering the burst mode, the frequency compensation current is available for lowing the output power when entering burst mode. Once entering burst mode, within the burst on time, the frequency compensation current

is disabled. At every beginning and end of burst on cycle, charge band soft off (works 4 pulse without IFRC) is applied. The soft on time and soft off time is set as tsofton and tsoftoff. The time of soft on and soft off is not counted into the minimum burst on time.

Once during soft on period, Iran, fast decreases to lower

Once during soft on period,  $I_{FBL}$  fast decreases to lower than  $100 \mu A$ , exit soft burst on immediately.

Fig.16 Burst Modes Working Principle

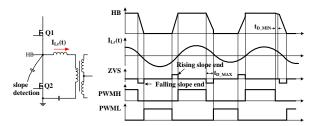

#### Adaptive Non-overlap ZVS Operation

To minimize the switching power loss, the adaptive zero voltage switching (ZVS) is adopted in every switching period. If the low side MOS turned off,  $V_{\rm ISEN}$  must be less than  $V_{\rm ISEN_{0+}}$  to enable high side ZVS; if the high side MOS turned off,  $V_{\rm ISEN}$  must be greater than  $V_{\rm ISEN_{0-}}$  to enable the low side ZVS, these constraints guarantee soft switching.

HB rising/falling slope will be detected via a slope detection circuit.

When ZVS is enabled, the dead time will begin. If HB rising or falling slope end is detected after minimum dead time  $T_{D\_MIN}$ , the high side or low side MOS is turned on again. If  $T_{D\_MAX}$  expires with no slope end detected, the MOS will be turned on directly.

Fig.17 Adaptive Non-overlap ZVS Operation

#### **External setting principle**

There are three pins which are used to preset LLC working characteristics. GATEB pin is used to set the current limit point of LLC. ISEN pin is used to set LLC working frequency range. VSEN pin is used to set burst entry level.

Fig. 18 External Setting Circuit

LLC resonant current limit point set principle:

| R <sub>GATEB</sub> | First stage current limit point | Second stage current limit point |

|--------------------|---------------------------------|----------------------------------|

| 10kΩ               | ±750mV                          | ±850mV                           |

| 20kΩ               | ±650mV                          | ±750mV                           |

| 30kΩ               | ±550mV                          | ±650mV                           |

LLC working frequency range set principle:

| Ele working frequency range set principle.    |                                |             |                            |  |  |

|-----------------------------------------------|--------------------------------|-------------|----------------------------|--|--|

| RISENSET +RISEN                               | Application working frequency* | Minton (μs) | Captive mode blanking time |  |  |

| $R_{ISENSET} + R_{ISEN} = 100\Omega$          | 300kHz                         | 0.46µs      | 3.3µs                      |  |  |

| $R_{ISENSET} + R_{ISEN} = 200\Omega$          | 200kHz                         | 0.67µs      | 5μs                        |  |  |

| $R_{ISENSET} + R_{ISEN} = 300\Omega$          | 150kHz                         | 0.95μs      | 6.7µs                      |  |  |

| R <sub>ISENSET</sub> +R <sub>ISEN</sub> =400Ω | 100kHz                         | 1.5µs       | 10μs                       |  |  |

Burst entry level set principle:

| Rvsen_d | Enter Burst Mode   |

|---------|--------------------|

| 5.1k    | 115μΑ              |

| 10k     | 125μΑ              |

| 15k     | 135μA              |

| 20k     | Without Burst Mode |

<sup>\*</sup>means the percentage of designed 100% load

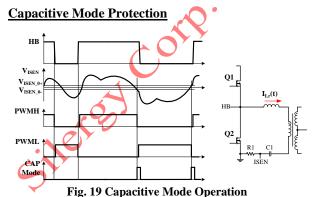

Capacitive mode should be prevented to avoid high switching loss and control logic error. Improved adaptive non-overlap ZVS logic is used to avoid capacitive mode switching.

Fig. 20 PWM Logic

When high side MOS turns on, if VISEN<0-, capacitive mode will be triggered and PWMH will turn off. After TD\_MAX expires or ZVS detected after TD\_MIN, the low side MOS will turn on. The resonant current is close to 0, the hard switching and shoot through of low side MOS are avoided.

The logic works the same when low side MOS turns off.

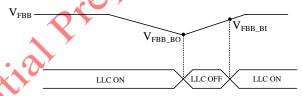

#### LLC Input Brown In and Brown Out

The LLC input voltage is also sensed via FBB pin.

If V<sub>FBB</sub><V<sub>FBB</sub> <sub>BO</sub>, the LLC stops switching.

If V<sub>FBB</sub>>V<sub>FBB\_BL</sub>, the LLC begins to switch.

Fig. 21 LLC BO and BI

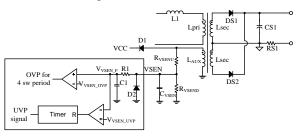

#### LLC Output OVP

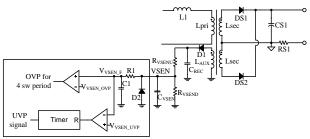

The LLC output OVP is sensed via the VSEN pin. The circuit on VSEN pin is shown as below:

Fig. 22 Output OVP and UVP Sensing Directly from AUX Winding

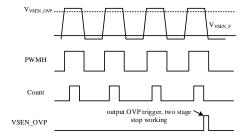

If V<sub>VSEN\_F</sub>>V<sub>VSEN\_OVP</sub> for consecutive 4 LLC switching cycle, LLC output OVP is triggered.

Fig. 23 LLC Output OVP Logic

For example, if output voltage is regulated at Vo, and 20% over voltage range is acceptable.  $R_{VSEND}$  has been decided for Burst entry level. The  $R_{VSENU}$  can be calculated by the following equation.

$$R_{VSENU} = R_{VSEND} \times \left( \frac{120\% \times N_{AUX} \times Vo}{V_{VSEN~OVP} \times N_{sec}} - 1 \right)$$

For noise immunity consideration, a 100pF~200pF capacitor is suggested to be applied between the VSEN pin and GND. And the capacitor should be close to the IC.

Another kind of VSEN circuit can also be adopted which is shown below. The voltage across AUX winding firstly be rectified to the DC component and then resistor divided into the VSEN pin.  $R_{\text{EVSEN}}$ ,  $R_{\text{EVSEU}}$  and  $C_{\text{VSEN}}$  can be chosen the same as descript above. The  $C_{\text{REC}}$  is suggested to set at 1uF.

Fig.24 Output OVP and UVP Sensing Via Rectified Voltage of AUX Winding

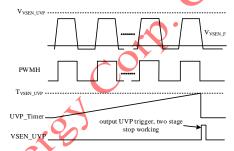

### **LLC Output UVP**

The LLC output UVP is also sensed via the VSEN pin. If V<sub>VSEN\_F</sub><V<sub>VSEN\_UVP</sub> for continuous T<sub>VSEN\_UVP</sub>, the LLC output UVP is triggered and two stage stops working and enters error timer restart.

Fig.25 LLC Output UVP Logic

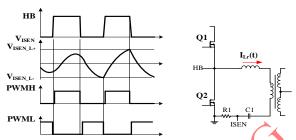

## LLC Cycle by Cycle Current Limit Protection

$V_{ISEN\_L}(+)$  and  $V_{ISEN\_L}(-)$  are the maximum current limit for LLC stage.

When V<sub>ISEN\_L(+)</sub> is touched, the high side MOS will be turned off immediately, the low side MOS will be turned on after dead time; When V<sub>ISEN\_L(-)</sub> is touched, the low side MOS will be turned off immediately, the high side MOS will be turned on after dead time.

Fig. 26 LLC Cycle by Cycle Current Limit Protection

When the output of LLC is short circuit, and V<sub>ISEN\_L</sub> has been touched cycle by cycle and last for T<sub>ILL\_protect</sub>, output short circuit protection will be triggered.

### **LLC Open Loop Protection (OLP)**

If the secondary side feedback loop is damaged, such as the short circuited of opto-couple, to make  $I_{FBL}$  to be lower than  $I_{FBL\_200\%}$  (30uA) for continuous  $T_{OLP}$  (64ms), the opening loop protection will be triggered.

#### VCC Over Voltage Protection (VCC OVP)

Before VCC rises to  $V_{VCC\_OVP}$ , if VCC is once over  $V_{VCC\_shunt}$ , the VCC shunt current  $I_{VCC\_Shunt}$  will take action to pull down VCC, if VCC cannot be pulled down and continually rises to  $V_{VCC\_OVP}$ , when  $V_{VCC\_OVP}$  and lasts for continuous 4 LLC switching cycles, VCC OVP will be triggered.

Fig.27 VCC OVP

#### **Over Temperature Protection**

The internal thermal protection works by sensing junction temperature  $T_J$ . If  $T_J$  reaches  $T_{SD}$ , all switching will stop and the IC timeout restart. Then the IC starts again, when  $T_J$  is lower than  $T_{SD}$ - $T_{hys}$ , switching will be enabled.

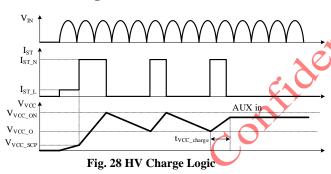

## **Start Up and Power Supply**

### **High Voltage Charge and VCC Management**

The SY5955 controller features a HV startup current source that allows fast startup time and extremely low standby power consumption. Two startup current levels ( $I_{ST\_L}$  and  $I_{ST\_N}$ ) are provided by the system for safety in case of short circuit between the VCC and GND pins.

The HV startup current source charges the VCC capacitor before IC starts up.

#### VCC start-up sequence:

- 1)  $V_{VCC} < V_{VCC\_SCP}$ , the star-tup current is limited to  $I_{ST\_L}$ , this logic prevents the IC over heat if the VCC is short circuit to GND (VCC cap short circuit).

- 2)  $V_{VCC\_SCP} < V_{VCC\_ON}$ , startup current is  $I_{ST\_N}$ ,  $V_{VCC}$  rises quickly to  $V_{VCC\_ON}$  to satisfy start-up time.

- 3)  $V_{VCC}>V_{VCC\_ON}$ , the HV charge current pauses, then other logic work (sense external parameter, Boost starting switching, LLC starts switching). If VCC drops below  $V_{VCC\_LO}$ , charge current works again to charge VCC. The maximum charge time after VCC start is  $T_{VCC\_charge}$  to prevent over heat. This logic guarantee  $V_{VCC}$  between  $V_{VCC\_LO}$  and  $V_{VCC\_ON}$  before load voltage rises.

- 4) When  $V_{OUT}$  rises enough, the VCC will be supplied by auxiliary winding and not drop below  $V_{VCC\_LO}$ , start-up current will stop. If output short circuit or other errors occur, the auxiliary winding supply will stop, then the HV start-up may works again to guarantee VCC above  $V_{VCC\_LO}$ .

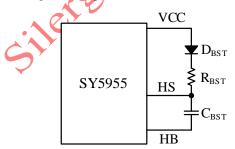

#### **High Side Driver Power Supply**

An external bootstrap buffer capacitor supplies the high-side driver. The bootstrap capacitor is connected between the high-side reference HB pin and the HS pin of the high-side driver supply input. When HB is low, an external diode charges this capacitor from the VCC pin charges this capacitor.

Fig. 29 High Side Driver Power Supply Circuit

The external diode  $D_{BST}$  is suggested to be fast recovery and low voltage drop diode. The series resistor  $R_{BST}$  is used to limit the charge current to protect  $D_{BST}$ . Typically, the  $R_{BST} = 1\Omega \sim 10\Omega$ .

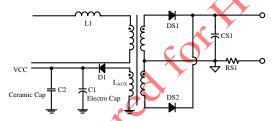

#### Capacitor Values on VCC Pin and HS Pin

Generally, two types of capacitors are used on the VCC pin. An SMD ceramic type with a smaller value located close to the IC to the filter noise and an electrolytic capacitance to supply IC operation power.

Fig. 30 VCC Power Supply Circuit

Typical values are:

$$C_{VCC\_electrolytical} = 47 \mu F$$

and  $C_{VCC\_ceramic} = 1 u F$

The VCC capacitor must be sufficient to handle the start-up during the period when the LLC starts until the auxiliary winding takes over the supply of the VCC pin.

For example, during start-up, suppose the consumption current of IC is  $i_{oper=}25mA$ , and the time of aux winding begins to take over VCC supply is  $\Delta t=15ms$ , allowable VCC drop during start-up is  $V_{VCC\_ON}-V_{VCC\_Lo}$  which is  $\Delta U=15V$ .

Then the VCC capacitor should be

$$C_{VCC} > \frac{i_{oper} \times \Delta t}{\Delta U} = 25 \mu F$$

To support charging the gate of the high-side MOSFET, the HS capacitor value must be much higher than the gate capacitance. It prevents a significant decrease in voltage on the HS due to gate charges. Typically, the suggested capacitor across HS and HB is 100nF~470nF.

## **PCB Layout Design Rules**

### FBL Track Shielded by GND Tracks or Plane

Because the FBL function works on the low current levels to minimize energy consumption at no load, this signal is more sensitive to disturbance.

Disturbance by the capacitive coupling to converter switching tracks (HB or PFC DRAIN) can make regulation unstable. To avoid disturbance in FBL:

The FBL track must be placed at a relatively large distance from the power part of the converters (LLC and PFC).

Tracks along the FBL track must be grounded for shielding (and a ground plane if the design is a double-sided copper design). FBL track also should be as short as possible.

#### Separate GND Connections for LLC and PFC

To avoid mutual disturbances, the grounding of the PFC and LLC controller must be separated in the PCB layout structure. The current pulses through ground tracks can lead to a wrong value or a signal on a pin that uses the ground level as a reference. The main potential sources of disturbance are the significant energy switching of the PFC and LLC converters and the MOSFET gate drive currents generated by the controllers.

Figure below shows these energy flows. It also shows that, to avoid disturbances, a special ground structure can keep them separated.

Keep these energy flow loops for each converter as small as possible, concerning track length and surface area. The track length of A and B marked in the figure below should be as short as possible. By connecting the IC to the shared bulk capacitor function via a separate

ground track, disturbances caused by converter current can be minimized.

The connection of primary ground is recommended as:

- ①: Ground node of PFC bulk capacitor

- ②: Ground node of CS resistor and source of PFC MOS

- ③: Ground node of LLC resonant capacitor and source of LLC low side MOS

- 4: Ground node of transformer auxiliary winding

- (5): Ground node of IC GND

- 6: Ground node of VCC capacitor

- 7: Ground node of opto-coupler

- Ground node of FBB pin lower resistor

- (9): Ground node of VSEN pin lower resistor

- ①: Ground node of LNS pin lower resistor

The recommendation of ground connection is shown in Fig36. The ground traces marked in red should be as short and wide as possible.

# FBB, LNS, CS, ISEN, VSEN sensing resistor should be close to IC

For all the input sensing pins, the sensing resistors should be close to IC to minimize disturbance by capacitive coupling.

Fig. 31 Recommendation of ground connection

# **Application Circuit**

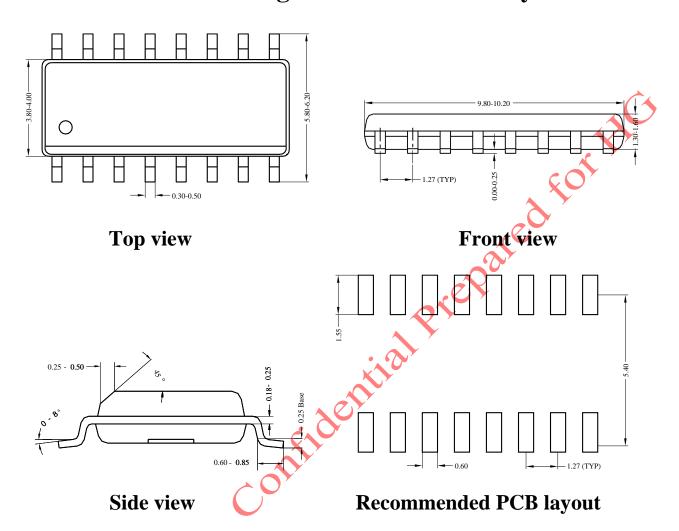

# **SOP16 Package Outline & PCB Layout**

Notes: All dimension in millimeter and exclude mold flash & metal burr

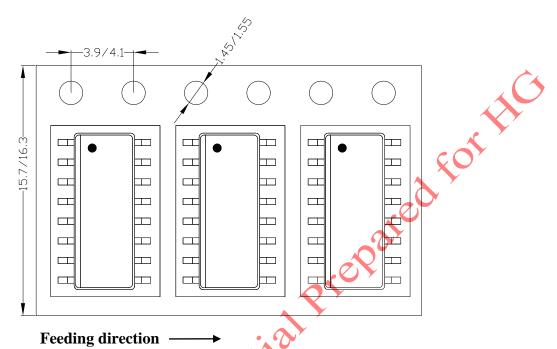

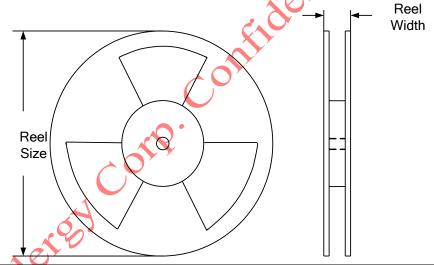

# **Taping & Reel Specification**

# 1. Taping orientation

# 2. Carrier Tape & Reel specification for packages

| Package<br>types | Tape<br>width<br>(mm) | Pocket<br>pitch(mm) | Reel size<br>(Inch) | Reel<br>width(mm) | Trailer<br>length(mm) | Leader length (mm) | Qty per<br>reel |

|------------------|-----------------------|---------------------|---------------------|-------------------|-----------------------|--------------------|-----------------|

| SOP16            | 16                    | 8                   | 13"                 | 12.4              | 400                   | 400                | 2500            |

## 3. Others: NA

# **Revision History**

The revision history provided is for informational purpose only and is believed to be accurate, however, not warranted. Please make sure that you have the latest revision.

| Date | Revision     | Change          |

|------|--------------|-----------------|

|      | Revision 0.9 | Initial Release |

Silered Confidential Prepared For HC

#### IMPORTANT NOTICE

- 1. **Right to make changes.** Silergy and its subsidiaries (hereafter Silergy) reserve the right to change any information published in this document, including but not limited to circuitry, specification and/or product design, manufacturing or descriptions, at any time and without notice. This document supersedes and replaces all information supplied prior to the publication hereof. Buyers should obtain the latest relevant information before placing orders and should verify that such information is current and complete. All semiconductor products are sold subject to Silergy's standard terms and conditions of sale.

- 2. Applications. Application examples that are described herein for any of these products are for illustrative purposes only. Silergy makes no representation or warranty that such applications will be suitable for the specified use without further testing or modification. Buyers are responsible for the design and operation of their applications and products using Silergy products. Silergy or its subsidiaries assume no liability for any application assistance or designs of customer products. It is customer's sole responsibility to determine whether the Silergy product is suitable and fit for the customer's applications and products planned. To minimize the risks associated with customer's products and applications, customer should provide adequate design and operating safeguards. Customer represents and agrees that it has all the necessary expertise to create and implement safeguards which anticipate dangerous consequences of failures, monitor failures and their consequences, lessen the likelihood of failures that might cause harm and take appropriate remedial actions. Silergy assumes no liability related to any default, damage, costs or problem in the customer's applications or products, or the application or use by customer's third-party buyers. Customer will fully indemnify Silergy, its subsidiaries, and their representatives against any damages arising out of the use of any Silergy components in safety-critical applications. It is also buyers' sole responsibility to warrant and guarantee that any intellectual property rights of a third party are not infringed upon when integrating Silergy products into any application. Silergy assumes no responsibility for any said applications or for any use of any circuitry other than circuitry entirely embodied in a Silergy product.

- 3. **Limited warranty and liability.** Information furnished by Silergy in this document is believed to be accurate and reliable. However, Silergy makes no representation or warranty, expressed or implied, as to the accuracy or completeness of such information and shall have no liability for the consequences of use of such information. In no event shall Silergy be liable for any indirect, incidental, punitive, special or consequential damages, including but not limited to lost profits, lost savings, business interruption, costs related to the removal or replacement of any products or rework charges, whether or not such damages are based on tort or negligence, warranty, breach of contract or any other legal theory. Notwithstanding any damages that customer might incur for any reason whatsoever, Silergy' aggregate and cumulative liability towards customer for the products described herein shall be limited in accordance with the Standard Terms and Conditions of Sale of Silergy.

- 4. **Suitability for use.** Customer acknowledges and agrees that it is solely responsible for compliance with all legal, regulatory and safety-related requirements concerning its products, and any use of Silergy components in its applications, notwithstanding any applications-related information or support that may be provided by Silergy. Silergy products are not designed, authorized or warranted to be suitable for use in life support, life-critical or safety-critical systems or equipment, nor in applications where failure or malfunction of an Silergy product can reasonably be expected to result in personal injury, death or severe property or environmental damage. Silergy assumes no liability for inclusion and/or use of Silergy products in such equipment or applications and therefore such inclusion and/or use is at the customer's own risk.

- 5. **Terms and conditions of commercial sale**. Silergy products are sold subject to the standard terms and conditions of commercial sale, as published at http://www.silergy.com/stdterms, unless otherwise agreed in a valid written individual agreement specifically agreed to in writing by an authorized officer of Silergy. In case an individual agreement is concluded only the terms and conditions of the respective agreement shall apply. Silergy hereby expressly objects to and denies the application of any customer's general terms and conditions with regard to the purchase of Silergy products by the customer.

- 6. No offer to sell or license. Nothing in this document may be interpreted or construed as an offer to sell products that is open for acceptance or the grant, conveyance or implication of any license under any copyrights, patents or other industrial or intellectual property rights. Silergy makes no representation or warranty that any license, either express or implied, is granted under any patent right, copyright, mask work right, or other intellectual property right. Information published by Silergy regarding third-party products or services does not constitute a license to use such products or services or a warranty or endorsement thereof. Use of such information may require a license from a third party under the patents or other intellectual property of the third party, or a license from Silergy under the patents or other intellectual property of Silergy.

For more information, please visit: www.silergy.com

©2023 Silergy Corp.

All Rights Reserved.