# **Application Note: SY6953**

High Efficiency, 2-4 cell Buck Li-Ion Battery Charger

Advanced Design Specification

## **General Description**

SY6953 is a wide input, high integrated and high efficiency Buck mode battery charger. It accepts 4-28V input and supports 2-4 cells Li-ion and Lipolymer battery. The charge current up to 2A can be programmed by using the external resistor for different portable applications. It also has a programmable charge timeout and adaptive input power limit for safety battery charge operation. It consists of 30V rating reverse blocking FET and power switching FETs with low ON resistance to achieve high charge efficiency and simple peripheral circuit design.

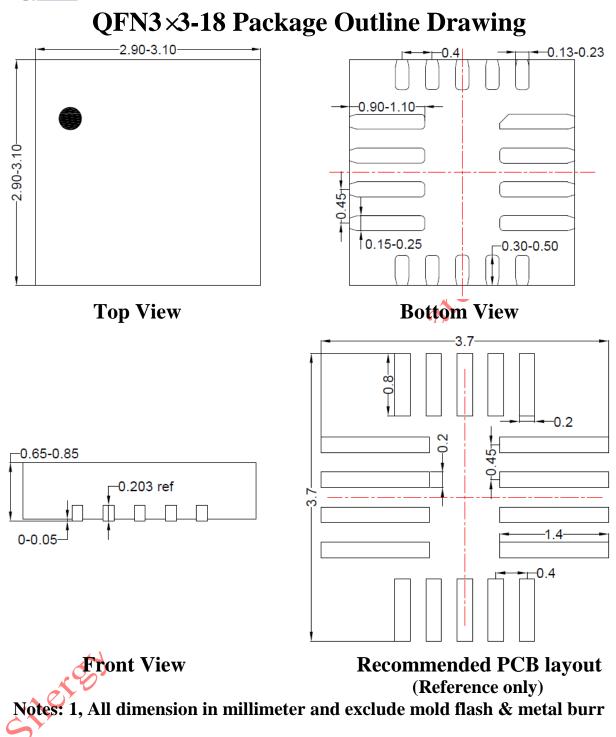

SY6953 along with small QFN3x3-18 footprint provides small PCB area application.

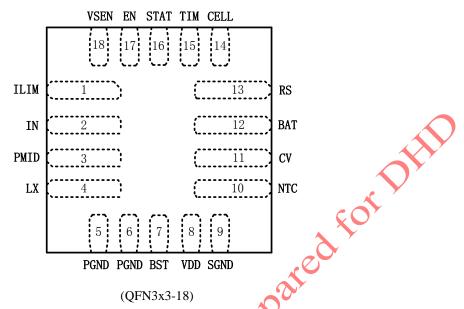

## **Ordering Information**

| Ordering Number | Package type | Note |

|-----------------|--------------|------|

| SY6953QIC       | QFN3×3-18    |      |

|                 |              |      |

### Features

- Wide Input Voltage Range: 4V to 28V

- Constant Voltage Selectable: 4.1V/4.2V/4.35V per Cell

- Charge Current up to 2A for 2 Cells Battery

- Charge Current up to 1.6A for 3 Cells Battery

- Charge Current up to 1.5A for 4 Cells Battery

- Programmable VDPM

- Programmable Input Current Limit

- Programmable Charge Timer

- Trickle Current / Constant Current / Constant Voltage Charging Mode

- Thermal Regulation

- Input Voltage UVLO and OVP Protection

- BAT OVP and Short Protection

- Over Temperature Protection

- Charging Status Indication

- NTC JEITA Compliance

- Package QFN3x3-18

# Applications

Floor Cleaning Robot Window & Door Automation Smart Speaker Electrical Tools

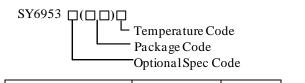

## **Application Circuit**

Figure1. Schematic Diagram

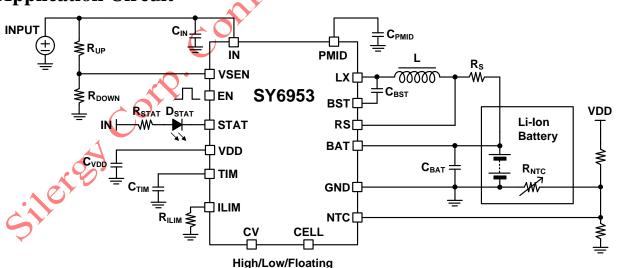

## **Pinout (top view)**

Top Mark: CNWxyz, (Device code: CNW, x=year code, y=week code, z= lot number code)

|          | 1      |                                                                                                                                                                                                                                                                                                                  |

|----------|--------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| Pin Name | Pin No | Description                                                                                                                                                                                                                                                                                                      |

| ILIM     | 1      | Input current limit program pin. Connect a resistor from this pin to GND to program input current limit. The mirror current about 1/3000 of the blocking FET current will dump into the external resistor through IKIM pin and compared to the internal reverence 1V. So $I_{INLIM} = (1V/R_{ILIM}) \times 3000$ |

| IN       | 2      | Analog power input pin. Connect a MLCC from this pin to ground to decouple high harmonic noise. This pin has OVP and UVLO function to make the charger operate within safe input voltage area. Suggest 1uF at least on this pin to ground.                                                                       |

| PMID     | 3      | Connected to the drain of the reverse blocking NFET and HSFET. Suggest 10uF at least on this pin to ground.                                                                                                                                                                                                      |

| LX       | 4      | Switch node pin. Connect to external inductor.                                                                                                                                                                                                                                                                   |

| PGND     | 5,6    | Power ground pin.                                                                                                                                                                                                                                                                                                |

| BST      | 7      | Boot strap for high HSFET driver.                                                                                                                                                                                                                                                                                |

| VDD      | 8      | Internal LDO output. Connect this pin with 1uF capacitor to ground.                                                                                                                                                                                                                                              |

| SGND     | 9      | Signal ground pin.                                                                                                                                                                                                                                                                                               |

| NTC      | 10     | Thermal protection pin. It will meet JEITA spec and refer to description section.                                                                                                                                                                                                                                |

| CV       | 11     | Battery CV voltage selection pin. Pull low for 4.2V/cell, pull high for 4.35V/cell and float this pin for 4.1V/cell.                                                                                                                                                                                             |

| BAT      | 12     | Battery positive pin.                                                                                                                                                                                                                                                                                            |

| RS       | 13     | Charge current sense resistor positive pin.                                                                                                                                                                                                                                                                      |

| CELL     | 14     | Battery cell selection pin. Different cell numbers can be selected by this pin. Float for 2 cells, pull low for 3 cells, pull high for 4 cells.                                                                                                                                                                  |

| TIM      | 15     | Charge time limit pin. Connect this pin with a capacitor to ground. Internal current source charges the capacitor for TC mode and fast charge (CV&CC) mode's charge time limit. TC charge time limit is about 1/9 of fast charge time limit.                                                                     |

| STAT     | 16     | Charge status indication pin. It is open drain output and pulled high to IN thru a LED to indicate the charge in process. When the charge is done, LED is off. When some fault happens during charging, LED will flash with 2Hz frequency.                                                                       |

| EN       | 17     | IC enable pin. Pull high to enable the IC and low to shut down the IC. Floating this pin will also shut down the IC.                                                                                                                                                                                             |

| VSEN     | 18     | Input voltage sense pin. If the voltage drops to internal 1.2V reference voltage, the input voltage will be clamped to the setting value.                                                                                                                                                                        |

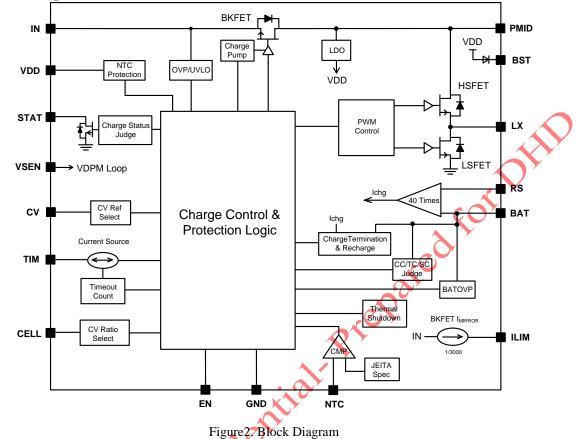

### **Block Diagram**

## Absolute Maximum Ratings (Note 1)

| IN, PMID, LX, BAT, VSEN, STAT, CV, CELL, EN        |                 |

|----------------------------------------------------|-----------------|

| TIM, VDD, NTC, ILIM                                | 0.3V to 4V      |

| RS-BAT                                             |                 |

| BST-LX                                             | 0.3V to 4V      |

| LX Pin Current Continuous                          |                 |

| Power Dissipation, PD @ TA <b>25°C</b> , QFN3x3-18 | 1.6W            |

| Package Thermal Resistance (Note 2)                |                 |

| θ <sub>JA</sub>                                    | 75 °C/W         |

| θ <sub>IC</sub>                                    | 20 °C/W         |

| Junction Temperature Range                         | 40 ℃ to +125 ℃  |

| Lead Temperature (Soldering, 10 sec.)              | 260 °C          |

| Storage Temperature Range                          | 65 °C to 150 °C |

|                                                    |                 |

## Recommended Operating Conditions (Note 3)

| IN -2                                   | 4V to 28V        |

|-----------------------------------------|------------------|

| PMID, LX, BAT, VSEN, STAT, CV, CELL, EN | 0V to 28V        |

| TIM, ILIM, NTC                          | 0V to 3.3V       |

| RS-BAT                                  | -0.25V to +0.25V |

| Junction Temperature Range              | 40 ℃ to 100 ℃    |

| Ambient Temperature Range               | 40 ℃ to 85 ℃     |

## **Electrical Characteristics**

$T_A=25 \text{ C}, V_{IN}=20V, \text{GND}=0V, C_{IN}=1uF, C_{PMID}=10uF, L=4.7uH, R_S=25m\Omega, C_{TIM}=330nF, \text{unless otherwise specified.}$

| Parameter                                            | Symbol                    | Conditions                                                                                                        | Min  | Тур   | Max   | Unit  |

|------------------------------------------------------|---------------------------|-------------------------------------------------------------------------------------------------------------------|------|-------|-------|-------|

| Bias Supply (V <sub>IN</sub> )                       | •                         | ·                                                                                                                 | •    |       |       |       |

| Supply Voltage Operation                             | V                         |                                                                                                                   | 4    |       | 28    | V     |

| Range                                                | V <sub>IN</sub>           |                                                                                                                   | 4    |       | 28    | v     |

| Input Voltage Lockout                                | V <sub>UVLO</sub>         | V <sub>IN</sub> rising and measured from                                                                          | 3.5  |       | 3.9 🖌 |       |

| Threshold                                            | V UVLO                    | IN to PGND                                                                                                        | 5.5  |       | 5.5   | V     |

| Input Voltage Lockout                                | $\Delta V_{\rm UVLO}$     | Measured from IN to PGND                                                                                          |      | 0.2   |       | v     |

| Hysteresis                                           | A V UVLO                  |                                                                                                                   |      | 0.2   |       | v     |

| Input Over Voltage                                   | V <sub>IN_OVP</sub>       | $V_{\ensuremath{\text{IN}}}$ rising and measured from                                                             |      | 29    | s Y   | V     |

| Protection                                           | V IN_OVP                  | IN to PGND                                                                                                        |      | 29    |       | v     |

| Input Over Voltage                                   | $\Delta V_{IN\_OVP}$      | Measured from IN to PGND                                                                                          |      | 0.5   |       | V     |

| Protection Hysteresis                                | Δ V IN_OVP                | Weasured from invito 1 GIVD                                                                                       |      | 0.5   |       | v     |

| Quiescent Current                                    | -                         |                                                                                                                   |      |       |       |       |

| Battery Discharge Current                            | I <sub>BAT</sub>          | Input absent, V <sub>BAT</sub> =17.4V                                                                             |      | 15    | 25    | uA    |

| Input Quiescent Current                              | I <sub>IN</sub>           | V <sub>IN</sub> =28V, EN=1, No switching                                                                          |      | 0.8   | 1.1   | mA    |

| Input Shutdown Current                               | I <sub>SD</sub>           | V <sub>IN</sub> =28V, EN=0                                                                                        |      | 60    |       | uA    |

| Oscillator and PWM                                   |                           |                                                                                                                   | 25   |       |       |       |

| Switching Frequency                                  | f <sub>SW</sub>           |                                                                                                                   |      | 500   |       | kHz   |

| Main NFET Minimum On                                 | 511                       | × ′                                                                                                               |      |       |       |       |

| Time                                                 | t <sub>ON_MIN</sub>       |                                                                                                                   |      | 100   |       | ns    |

| Main N-FET Minimum Off                               |                           | · · · ·                                                                                                           |      |       |       |       |

| Time                                                 | t <sub>OFF_MIN</sub>      |                                                                                                                   |      | 100   |       | ns    |

| Power MOSFET                                         |                           |                                                                                                                   | L    |       |       |       |

| R <sub>DS(ON)</sub> of Main N-FET                    | <b>R</b> <sub>HSFET</sub> |                                                                                                                   |      | 120   |       | mΩ    |

| $R_{DS(ON)}$ of Rectified N-FET                      | R <sub>LSFET</sub>        |                                                                                                                   |      | 180   |       | mΩ    |

| R <sub>DS(ON)</sub> of Blocking N-FET                | R <sub>BKFET</sub>        | CAN CANA                                                                                                          |      | 150   |       | mΩ    |

| Voltage Regulation                                   | BKFEI                     |                                                                                                                   |      | 150   |       | 11132 |

| vonage Regulation                                    |                           | 2-cell, CV is floating                                                                                            |      | 8.2   |       |       |

|                                                      |                           | $2$ -cell, $V_{CV} < 0.4V$                                                                                        |      | 8.4   |       |       |

|                                                      |                           | $\frac{2 \text{-cell}, \text{V}_{\text{CV}} < 0.4 \text{V}}{2 \text{-cell}, \text{V}_{\text{CV}} > 1.5 \text{V}}$ |      | 8.7   |       | -     |

|                                                      |                           | 3-cell, CV is floating                                                                                            |      | 12.3  |       |       |

| Battery Charge Voltage                               | v ·                       | $3$ -cell, $V_{CV} < 0.4V$                                                                                        |      | 12.5  |       | V     |

| Battery Charge Voltage                               | VBAT_REG                  | $3$ -cell, $V_{CV} < 0.4 V$<br>$3$ -cell, $V_{CV} > 1.5 V$                                                        |      | 13.05 |       | v     |

| $\rightarrow$                                        |                           | 4-cell, CV is floating                                                                                            |      | 16.4  |       | -     |

|                                                      |                           | 4-cell, $V_{CV} < 0.4V$                                                                                           |      | 16.8  |       |       |

|                                                      |                           |                                                                                                                   |      | 10.8  |       |       |

|                                                      |                           | 4-cell, $V_{CV}$ >1.5V                                                                                            |      |       |       |       |

| Recharge Threshold refer                             |                           | 2-cell battery                                                                                                    |      | 200   |       |       |

| to V <sub>BAT_REG</sub>                              | $\Delta V_{RCH}$          | 3-cell battery                                                                                                    |      | 300   |       | mV    |

|                                                      |                           | 4-cell battery                                                                                                    |      | 400   |       |       |

| Trickle Charge Rising                                |                           | 2-cell battery                                                                                                    |      | 5.6   |       | _     |

| Edge Threshold                                       | V <sub>TRK</sub>          | 3-cell battery                                                                                                    |      | 8.4   |       | V     |

|                                                      |                           | 4-cell battery                                                                                                    |      | 11.2  |       |       |

| Charge Current                                       |                           |                                                                                                                   |      |       |       |       |

| Charge Current Accuracy<br>for Constant Current Mode | I <sub>CC</sub>           | I <sub>CC</sub> =30mV/R <sub>S</sub>                                                                              | -4%  |       | 4%    |       |

| Charge Current Accuracy<br>for Trickle Current Mode  | I <sub>TC</sub>           | I <sub>TC</sub> =3mV/R <sub>S</sub>                                                                               | -25% |       | 25%   |       |

| Termination Current                                  | I <sub>TERM</sub>         | I <sub>TERM</sub> =3mV/R <sub>S</sub>                                                                             | -25% |       | 25%   |       |

| Input Current Limit                                                  |                         |                                           |     |        |     |                   |  |

|----------------------------------------------------------------------|-------------------------|-------------------------------------------|-----|--------|-----|-------------------|--|

| Input Current Limit Accuracy                                         | I <sub>INLIM</sub>      | I <sub>INLIM</sub> =500mA                 | -5% |        | 5%  |                   |  |

| BAT Voltage OVP                                                      |                         |                                           |     |        |     |                   |  |

| BAT OVP Threshold                                                    | V <sub>BAT_OVP</sub>    | V <sub>BAT</sub> rising                   |     | 104    |     | $% V_{BAT\_REG}$  |  |

| BAT OVP Threshold Hysteresis                                         | $\Delta V_{BAT_OVP}$    |                                           |     | 2      |     | $% V_{BAT\_REG}$  |  |

| VDPM Reference                                                       |                         |                                           |     |        |     |                   |  |

| Reference for VDPM                                                   | V <sub>VSEN_DPM</sub>   |                                           |     | 1.2    |     | V                 |  |

| VDD Regulation                                                       |                         |                                           |     |        |     |                   |  |

| VDD LDO Voltage                                                      | V <sub>VDD</sub>        | $V_{IN}>4V, EN=1$                         |     | 3.3    |     | V                 |  |

| VDD Current Capacity                                                 | I <sub>VDD</sub>        | V <sub>VDD</sub> =3V                      | 20  |        |     | mA                |  |

| VDD Current Limit                                                    | I <sub>VDD_LIMIT</sub>  | VDD short to ground                       |     |        | 50  | mA                |  |

| Timer                                                                | •                       |                                           |     |        |     |                   |  |

| Trickle Current Charge Timeout                                       | t <sub>TC</sub>         |                                           |     | 0.5    |     | hour              |  |

| Constant Current Charge                                              | taa                     | C <sub>TIM</sub> =330nF                   |     | 4.5    | K Ó | hour              |  |

| Timeout                                                              | t <sub>CC</sub>         |                                           |     | 4.2    |     | noui              |  |

| Charge Mode Change Delay                                             | t <sub>MC</sub>         |                                           |     | 30     |     | ms                |  |

| Time                                                                 |                         |                                           |     | $\sim$ |     |                   |  |

| Termination Delay Time                                               | t <sub>TERM</sub>       |                                           |     | 30     |     | ms                |  |

| Recharge Time Delay                                                  | t <sub>RCHG</sub>       |                                           |     | 30     |     | ms                |  |

| Cycle-by-Cycle Peak Current                                          |                         |                                           |     |        |     |                   |  |

| Power FET Current Limit                                              | I <sub>PEAK</sub>       | V <sub>BAT</sub> >V <sub>SHORT</sub>      |     | 3      |     | A                 |  |

| BAT Short Protection                                                 |                         |                                           |     |        |     |                   |  |

| BAT Short Protection                                                 | V <sub>SHORT</sub>      | $V_{BAT}$ falling                         |     | 2.00   |     | V                 |  |

| Threshold                                                            | bitotti                 |                                           |     |        |     |                   |  |

| Auto Shut Down                                                       |                         | M. falling many d from                    | 1   |        |     |                   |  |

| Auto Shutdown Voltage<br>Threshold                                   | V <sub>ASD</sub>        | $V_{IN}$ falling, measured from IN to BAT |     | 200    |     |                   |  |

| Auto Shutdown Voltage                                                |                         | V <sub>IN</sub> rising hysteresis,        |     |        |     | mV                |  |

| Threshold Hysteresis                                                 | V <sub>ASD_HYS</sub>    | measured from IN to BAT                   |     | 80     |     |                   |  |

| Logic Control                                                        |                         | incustred from it to Diff                 |     |        |     |                   |  |

| High Level Logic for EN                                              | V <sub>EN_H</sub>       | CA CA                                     | 1.5 |        |     | V                 |  |

| Low Level Logic for EN                                               | V <sub>EN_L</sub>       |                                           | 1.5 |        | 0.4 | V                 |  |

| High Level Logic for CV,CELL                                         | V <sub>LOGIC</sub> H    | · · · · · · · · · · · · · · · · · · ·     | 3   |        | 0.1 | V                 |  |

| Low Level Logic for CV,CELL                                          | VLOGIC L                |                                           | 5   |        | 0.5 | V                 |  |

| NTC Thermal Protection JEI                                           |                         |                                           |     |        | 0.5 | •                 |  |

| T1(0 °C) Threshold                                                   | V <sub>NTC_TI</sub>     | V <sub>NTC</sub> rising                   |     | 73.25  |     |                   |  |

| T1(0 $\mathbb{C}$ ) Threshold Hysteresis                             | V <sub>NTC_TI_HYS</sub> |                                           |     | 1.25   |     |                   |  |

| $T2(10 \ C)$ Threshold                                               |                         | V <sub>NTC</sub> rising                   |     | 68.25  |     |                   |  |

|                                                                      | V <sub>NTC_T2</sub>     | V NTC HSHIP                               |     |        |     | %V <sub>VDD</sub> |  |

| T2(10 °C) Threshold Hysteresis $T2(45 \circ C)$ Threshold Hysteresis | V <sub>NTC_T2_HYS</sub> | V fallina                                 |     | 1.25   |     |                   |  |

| T3(45 °C) Threshold                                                  | V <sub>NTC_T3</sub>     | V <sub>NTC</sub> falling                  |     | 44.75  |     |                   |  |

| T3(45 °C) Threshold Hysteresis                                       | V <sub>NTC_T3_HYS</sub> |                                           |     | 1.2    |     |                   |  |

| T5(60 °C) Threshold                                                  | V <sub>NTC_T5</sub>     | V <sub>NTC</sub> falling                  |     | 34.375 |     |                   |  |

| T5(60 C) Threshold Hysteresis                                        | V <sub>NTC_T5_HYS</sub> |                                           |     | 1.2    |     |                   |  |

| Thermal Regulation and Thermal Shutdown                              |                         |                                           |     |        |     |                   |  |

| Junction Thermal Regulation                                          | T <sub>J_REG</sub>      |                                           |     | 120    |     | С                 |  |

| Accuracy<br>Thermal Shutdown Threshold                               |                         |                                           |     | 150    |     | C                 |  |

| Thermal Shutdown Threshold                                           | T <sub>SD</sub>         |                                           |     |        |     |                   |  |

| Hysteresis                                                           | T <sub>SD_HYS</sub>     | Falling Edge                              |     | 20     |     | С                 |  |

Note 1: Stresses beyond the "Absolute Maximum Ratings" may cause permanent damage to the device. These are stress ratings only. Functional operation of the device at these or any other conditions beyond those indicated in the operational sections of the specification is not implied. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

Note 2:  $\theta_{JA}$  is measured in the natural convection at  $T_A = 25 \ C$  on a low effective four-layer thermal conductivity test board of JEDEC 51-3 thermal measurement standard. Silered corp.

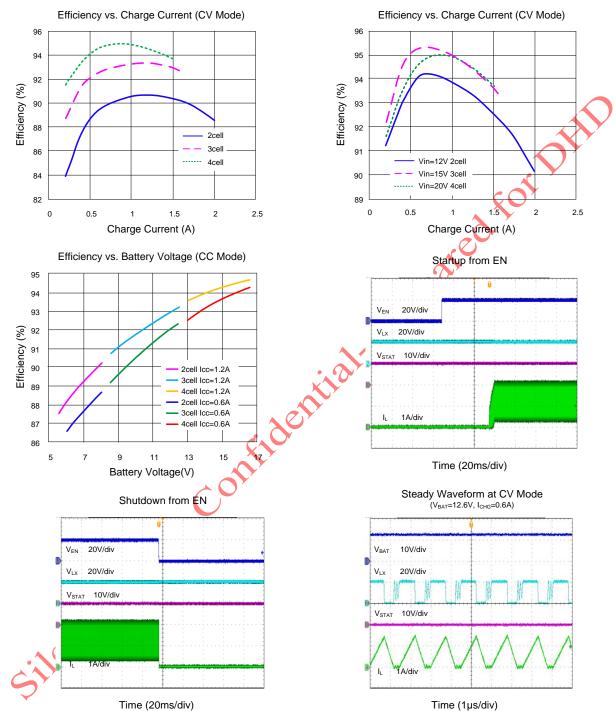

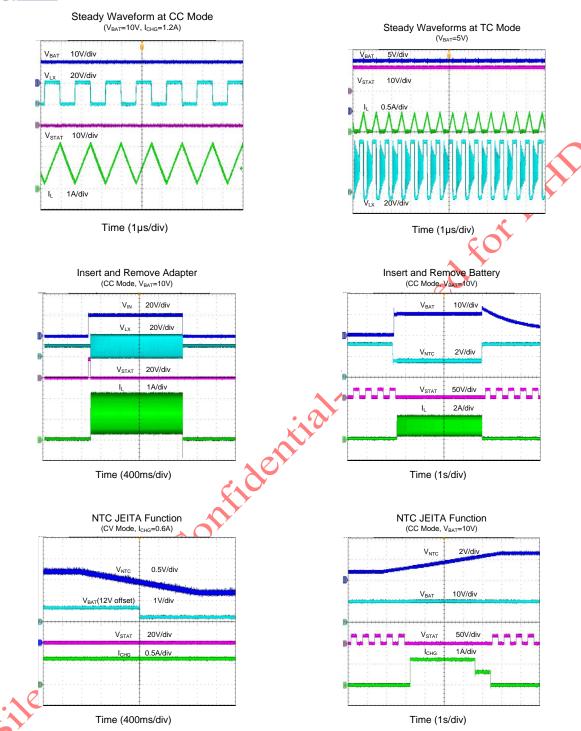

### **Typical Performance Characteristics**

$(T_A=25 \text{ C}, V_{IN}=20V, C_{IN}=1uF, C_{PMID}=10uF, L=4.7uH, R_S=25m\Omega$ , unless otherwise specified)

## **General Function Description**

SY6953 is a 4-28V input, 2-4 cells Li-Ion synchronous Buck charger. The charge current up to 2A can be programmed by using the external resistor for different portable applications. It also has a programmable charge timeout and adaptive input power limit for safety battery charge operation. It consists of 30V rating reverse blocking FET and power switching FETs with low ON resistance to achieve high charge efficiency and simple peripheral circuit design.

SY6953 along with small QFN3x3-18 footprint provides small PCB area application.

#### Switching Mode Control Strategy

SY6953 utilizes quasi-fixed frequency control to simplify the internal close-loop compensation design. The quasi-fixed frequency settled at 500 kHz is easy for the size minimization of peripheral circuit design.

#### **Operation Principle**

SY6953 works as a synchronous Buck mode battery charger when the adapter is present. It utilizes 500 kHz switching frequency to minimize the PCB design.

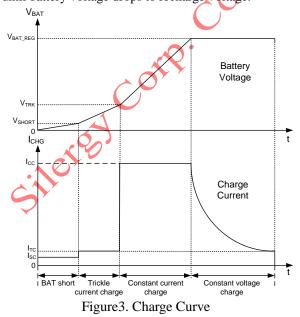

The charger will operate in battery short mode, trickle charge mode, constant current charge mode and constant voltage charge mode according to the battery voltage. The charge current in every mode is showed in following charge curve. In constant voltage mode, if charge current is lower than termination current, the charger will stop charging until battery voltage drops to recharge voltage.

#### **Input Power Limit Principle**

For prevent input source overloading, SY6953 has IDPM and VDPM loop to limit the input power.

It will automatically decrease charge current when input current exceeds setting value or VSEN voltage drops to internal 1.2V reference.

#### **Charging Status Indication Description**

STAT is an open drain pin and a pull up resistor is needed for charging status indication. Connect a LED from IN to STAT pin, LED ON means Charge-in-Process, LED OFF means Charge Done, LED Flashing with 2Hz means Fault Mode.

- 1. Charge-In-Process Pull and keep STAT pin to Low;

- 2. Charge Done Pull and keep STAT pin to High;

- 3. Fault Mode Output high and low voltage alternatively with 2Hz frequency. The faults include input OVP, BAT OVP, BAT short, NTC JEITA UTP/OTP (below T1 or above T5), Time-out and Thermal shutdown.

#### Full Charger Protections Description

In charge mode, SY6953 has full protections to protect the IC and the battery.

<u>Input Over Voltage Protection</u> – SY6953 has IN over voltage protection. It will stop charge when input OVP occurs. IC will auto recover normal operation when this fault removes.

<u>BAT Over Voltage Protection</u> – SY6953 will stop charge when BAT OVP occurs. IC will auto recover normal operation when this fault removes.

$\frac{Timeout\ Protection}{I} - The\ charger\ can\ detect\ a\ bad} battery.\ It\ will\ stop\ charge\ and\ latch\ off\ when\ the\ charger\ works\ over\ safety\ time\ which\ is\ set\ by\ C_{TIM}.$  Only recycling the input or EN signal can release this fault.

<u>JEITA NTC Thermal Protection</u> – When NTC voltage is lower than  $V_{NTC_T5}$  threshold or higher than  $V_{NTC_T1}$  threshold, the converter will stop charge. IC will auto recover when this fault removes.

<u>Thermal Shutdown Protection</u> – The IC will stop operation when the junction temperature is higher than 150 °C. It will auto recover normal when this fault removes.

## **AN SY6953**

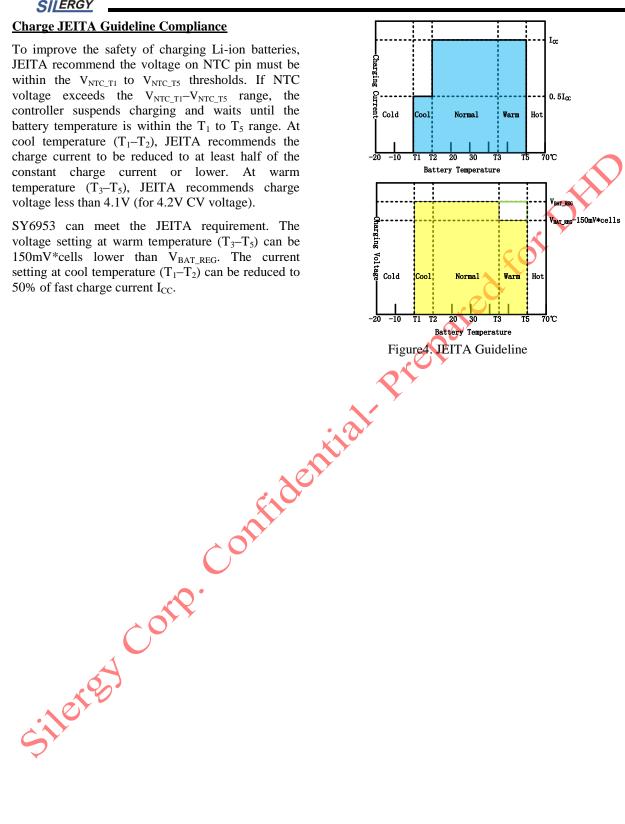

#### **Charge JEITA Guideline Compliance**

To improve the safety of charging Li-ion batteries, JEITA recommend the voltage on NTC pin must be within the  $V_{NTC_T1}$  to  $V_{NTC_T5}$  thresholds. If NTC voltage exceeds the  $V_{\text{NTC}\_\text{T1}}\text{-}V_{\text{NTC}\_\text{T5}}$  range, the controller suspends charging and waits until the battery temperature is within the  $T_1$  to  $T_5$  range. At cool temperature (T1-T2), JEITA recommends the charge current to be reduced to at least half of the constant charge current or lower. At warm temperature  $(T_3-T_5)$ , JEITA recommends charge voltage less than 4.1V (for 4.2V CV voltage).

SY6953 can meet the JEITA requirement. The voltage setting at warm temperature  $(T_3-T_5)$  can be 150mV\*cells lower than  $V_{BAT\_REG}$ . The current setting at cool temperature  $(T_1-T_2)$  can be reduced to 50% of fast charge current  $I_{CC}$ .

mΩ

## **Application Information**

Because of the high integration of SY6953, the application circuit based on this regulator IC is rather simple. Only input capacitor  $C_{PMID}$ , output capacitor  $C_{BAT}$ , inductor L, NTC resistors  $R_1$ ,  $R_2$ , charge current sense resistor  $R_S$  and timer capacitor  $C_{TIM}$  need to be selected for the targeted application specification.

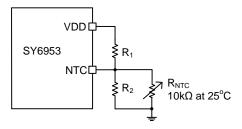

#### **NTC Resistor**

SY6953 monitors battery temperature by measuring the VDD voltage and NTC voltage. It will trigger JEITA protection when the ratio K (K=  $V_{NTC}/V_{VDD}$ ) reaches the related threshold.

The temperature sensing network is showed as below.

Figure 5. NTC Resistors

For JEITA standard,  $T_1=0$  °C,  $T_2=10^{\circ}$ C,  $T_3=45^{\circ}$ C,  $T_5=60^{\circ}$ C.

NTC resistors should be chosen at  $R_1=5.24k\Omega$ ,  $R_2=30.28k\Omega$ .

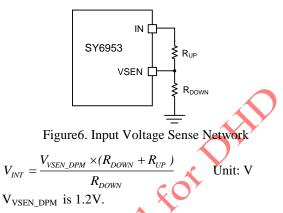

#### Input Voltage Threshold for Input Power Limit

SY6953 will monitor input voltage by measuring the VSEN voltage, when VSEN drops below the internal 1.2V reference, SY6953 will decrease the duty cycle to reduce the charge current.

The input voltage sense network is shown below, choose  $R_{\rm UP},\,R_{\rm DOWN}$  to set the input voltage threshold  $V_{\rm INT}$ :

#### Charge Current Sense Resistor Rs

The charging current sense resistor  $R_s$  is calculated as below:

$$R_{s} = \frac{30mV}{L_{s}}$$

Unit:

where the  $I_{CC}$  is the battery constant charge current, unit is ampere.

#### Timer Capacitor C<sub>TIM</sub>

The charger also provides a programmable charge timer. The charge time is programmed by the capacitor connected between the TIM pin and GND. The capacitance is given by the formula:

$$C_{TIM}=2 \times 10^{-11} S \times t_{CC}$$

Unit: F

$t_{CC}$  is the permitted fast charge time, unit is second.

#### Input Capacitor C<sub>PMID</sub>

The main input capacitor is connected between PMID pin to PGND. It can absorb input ripple current from the Buck stage, which is given by below equation.

$$I_{RMS} = I_{CHG} \times \frac{\sqrt{V_{BAT} \times (V_{IN} - V_{BAT})}}{V_{IN}}$$

The maximum value of this RMS ripple current in the application must be smaller than the rated RMS current in the chosen capacitor datasheet. Care should be taken to minimize the loop area formed by  $C_{PMID}$ , and PMID and PGND pins.

To minimize the potential noise problem, IN should be decoupled to PGND with typical  $1\mu F$ capacitance, X7R or a better grade ceramic capacitor.

#### **Output Capacitor C<sub>BAT</sub>**

The output capacitor in parallel with the battery is used for absorbing the high frequency switching ripple current and smoothing the output voltage. The RMS value of the output ripple current  $I_{RMS}$  is calculated as follow.

$$I_{RMS} = \frac{V_{IN} \times D \times (1 - D)}{\sqrt{12} \times L \times f_{SW}}$$

Where the duty cycle D is the ratio of the output voltage (battery voltage) over the input voltage for CCM mode which is typical operation for the battery charger. During the battery charge period, battery voltage varies from its initial battery voltage to the rated voltage. The maximum value of this RMS ripple current in the application must be smaller than the rated RMS current in the chosen capacitor datasheet. A typical 20µF ceramic capacitor is recommended to absorb this current and also has small size.

#### **Output Inductor L**

There are several considerations in choosing the inductor.

1) Choose the inductance to provide the desired ripple current. It is suggested to choose the ripple current to be about 20%-40% of the maximum charge current  $I_{CC}$ . The inductance is calculated as:

$$L = \frac{V_{BAT\_REG} (1 - V_{BAT\_REG} / V_{IN})}{f_{SW} \times I_{CC} \times (20\% - 40\%)}$$

where  $f_{SW}$  is the switching frequency and  $V_{I\!N}$  is the input voltage in the application

SY6953 is quite tolerant of different ripple current amplitude. Consequently, the final choice of inductance can be slightly off the calculation value without significantly impacting the performance.

2) The saturation current rating of the inductor must be selected to be greater than the maximum peak inductor current under all the range of battery voltage and full load conditions.

$$I_{\text{SAT}} \ge I_{\text{CC}} + \frac{V_{BAT\_\text{REG}} (1 - V_{BAT\_\text{REG}} / V_{IN})}{2 \times f_{SW} \times L}$$

The maximum peak inductor current happens when battery voltage is equivalent with half of input voltage.

3) The DCR of the inductor and the core loss at the switching frequency must be low enough to achieve the desired efficiency requirement. It is desirable to choose an inductor with DCR<20mohm to achieve a good overall efficiency.

A 47uH inductor is usually recommended to cover most of the conventional applications.

#### <u>Layout Design</u>

The layout design of SY6953 is relatively simple. For the best efficiency and minimum noise problems, we should place the following components close to the IC:  $C_{IN}$ ,  $C_{PMID}$ , L,  $C_{VDD}$  and  $C_{BST}$ .

- 1) It is desirable to maximize the PCB copper area connecting to PGND pin to achieve the best thermal and noise performance. If the board space allowed, a ground plane is highly desirable.

- 2)  $C_{PMID}$  must be close to pins PMID and PGND. The loop area formed by  $C_{PMID}$  and PGND must be minimized.

- 3) The PCB copper area associated with LX pin must be minimized to avoid the potential noise problem.

- 4) The capacitor  $C_{TIM}$  and the trace connecting to the TIM pin must not be adjacent to the LX net on the PCB.

The SY6953 PCB layout is suggested as below.

# AN\_SY6953

| SGND SGND<br>CRS RR. Rold Ca<br>SSND<br>SY6953 | <ul> <li>Top Layer</li> <li>Bottom Layer</li> <li>PCB Via</li> <li>Top Component</li> <li>Bottom Component</li> </ul> |

|------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------|

| Power In IN CIN<br>PGND<br>● ● ● ● LX L RS     | CBATI CBAT2<br>PGND<br>• • •<br>• • •                                                                                 |

Firef. Proposed PCB Layou

PCB PCB Layou

<td