**Enhanced Differential Receiver**

#### **General Description**

The SY89251V is a differential PECL/ECL receiver/buffer in a space saving (2mm x 2mm) DFN package. The device is functionally equivalent to the SY100EL16VC, except for an active HIGH enable pin and a 70% smaller footprint. It is also equivalent to the SY89250V, except for an active HIGH enable pin. It provides a V<sub>BB</sub> output for either single-ended application or as a DC bias for AC-coupling to the device.

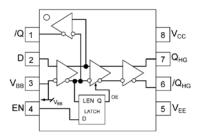

The SY89251V provides an EN input which is synchronized with the data input (D) signal in a way that provides glitchless gating of the Q<sub>HG</sub> and /Q<sub>HG</sub> outputs. When the EN signal is HIGH, the input is passed to the outputs and the data output equals the data input. When the data input is HIGH and the EN goes LOW, it will force the Q<sub>HG</sub> LOW and the /Q<sub>HG</sub> HIGH on the next negative transition of the data input. If the data input is LOW when the EN goes LOW, the next data transition to a HIGH is ignored and Q<sub>HG</sub> remains LOW and /Q<sub>HG</sub> remains HIGH. The next positive transition of the data input is not passed on to the data outputs under these conditions. The QHG and  $/Q_{HG}$  outputs remain in their disabled state as long as the EN input is held LOW. The EN input has no influence on the /Q output and the data input is passed on (inverted) to this output whether EN is HIGH or LOW. This configuration is ideal for crystal oscillator applications, where the oscillator can be free running and gated on and off synchronously without adding extra counts to the

Datasheets and support documentation can be found on Micrel's web site at: <a href="http://www.micrel.com">www.micrel.com</a>.

#### **Features**

- 3.3V and 5V power supply options

- 250ps propagation delay

- Very high voltage gain

- Ideal for pulse amplifier and limiting amplifier applications

- Data synchronous enable/disable (EN) on Q<sub>HG</sub> and /Q<sub>HG</sub> provides for complete glitchless gating of the outputs

- Ideal for gating timing signals

- Complete solution for high quality, high frequency crystal oscillator applications

- Available in an ultra-small 8-pin (2mm x 2mm) DFN package

#### **Applications**

Oscillator modules

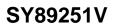

#### **Block Diagram**

output.

Micrel Inc. • 2180 Fortune Drive • San Jose, CA 95131 • USA • tel +1 (408) 944-0800 • fax + 1 (408) 474-1000 • http://www.micrel.com

# Ordering Information<sup>(1)</sup>

| Part Number                 | Package<br>Type | Operating<br>Range | Package Marking                        | Lead<br>Finish    |

|-----------------------------|-----------------|--------------------|----------------------------------------|-------------------|

| SY89251VMI                  | DFN-8           | Industrial         | 251                                    | Sn-Pb             |

| SY89251VMITR(2)             | DFN-8           | Industrial         | 251                                    | Sn-Pb             |

| SY89251VMG                  | DFN-8           | Industrial         | 251 with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| SY89251VMGTR <sup>(2)</sup> | DFN-8           | Industrial         | 251 with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

#### Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25^{\circ}$ C, DC electricals only.

2. Tape and Reel.

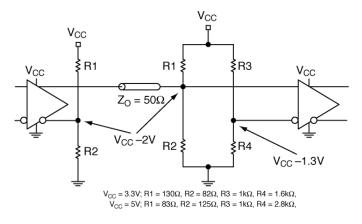

# Pin Configuration

8-Pin DFN (Ultra-Small Outline)

#### **Truth Table**

| EN | QHG Output |  |  |

|----|------------|--|--|

| 0  | Logic Low  |  |  |

| 1  | Data       |  |  |

#### **Pin Description**

| Pin Number | Pin Name           | Туре                           | Pin Function                                                                                                                                                                                            |

|------------|--------------------|--------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 1          | /Q                 | 100k                           | Single-Ended PECL/ECL Feedback Output.                                                                                                                                                                  |

| 2          | D                  | 100k                           | Single-Ended PECL/ECL Input: The signal input includes an internal $75k \Omega$ pull-down resistor. If input is left open, Q output will default to LOW.                                                |

| 3          | VBB                | Reference<br>Output<br>Voltage | Bias Voltage: $V_{CC}$ -1.3V. Used as reference voltage when AC-coupling to the D input. Max sink/source current is ±0.5mA.                                                                             |

| 4          | EN                 | Enable Input                   | EN Input which is synchronized with data input (D) signal in a way that provides glitchless gating of $Q_{HG}$ and $/Q_{HG}$ outputs. Includes internal 75k $\Omega$ pull-up resistor. Default is HIGH. |

| 5          | VEE<br>Exposed Pad | Negative<br>Power<br>Supply    | Negative Power Supply: V <sub>EE</sub> and exposed pad must be tied to most negative supply. For PECL/LVPECL connect to ground.                                                                         |

| 6, 7       | /QHG, QHG          | 100k                           | Differential PECL/ECL Output: QHG defaults to LOW and /QHG defaults to HIGH if D input is left open. See "Output Interface Applications" section for recommendations on terminations.                   |

| 8          | VCC                | Positive<br>Power<br>Supply    | Positive Power Supply: Bypass with $0.1\mu F/0.01\mu F$ low ESR capacitors as close to VCC pin as possible.                                                                                             |

## Absolute Maximum Ratings<sup>(1)</sup>

| Power Supply Voltage (V <sub>CC</sub> )<br>ECL Input Voltage (V <sub>IN</sub> ) |                   |

|---------------------------------------------------------------------------------|-------------------|

| Voltage Applied to Output at HIGH State                                         |                   |

| (V <sub>OUT</sub> )                                                             | –0.5V to $V_{CC}$ |

| Output Current (I <sub>OUT</sub> )                                              |                   |

| Continuous                                                                      | 50mA              |

| Surge                                                                           | 100mA             |

| Lead Temperature (soldering, 20 sec.)                                           | 260°C             |

| Storage Temperature (T <sub>S</sub> )                                           | -65°C to +150°C   |

# **Operating Ratings**<sup>(2)</sup>

| Power Supply Voltage  V <sub>CC</sub> -V <sub>EE</sub> | 3.3V ±10% or 5V ±10% |

|--------------------------------------------------------|----------------------|

| Ambient Temperature (T <sub>A</sub> )                  | 40°C to +85°C        |

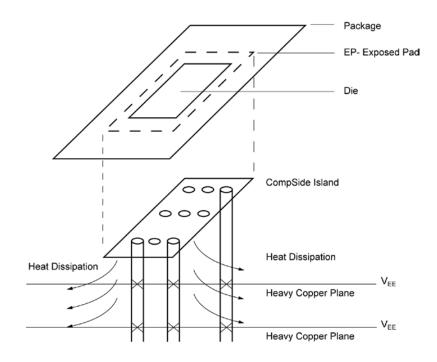

| Package Thermal Resistance,(3)                         |                      |

| DFN ( $\theta_{JA}$ ) Still-Air ······                 | 93°C/W               |

| $DFN\;(\psi_{JB})\;\;$                                 | 60°C/W               |

## DC Electrical Characteristics<sup>(4)</sup>

$T_A = -40^{\circ}C$  to +85°C, unless noted.

| Symbol          | Parameter                | Condition                        | Min                   | Тур                   | Max                   | Units |

|-----------------|--------------------------|----------------------------------|-----------------------|-----------------------|-----------------------|-------|

| V <sub>EE</sub> | Power Supply             | V <sub>CC</sub> -V <sub>EE</sub> | 3.0                   | 3.3                   | 3.6                   | V     |

|                 |                          | V <sub>CC</sub> -V <sub>EE</sub> | 4.5                   | 5.0                   | 5.5                   | V     |

| I <sub>EE</sub> | Power Supply Current     |                                  |                       |                       | 46                    | mA    |

| l⊫              | Input Low Current        | EN                               | -150                  |                       |                       | μA    |

| $V_{BB}$        | Output Reference Voltage |                                  | V <sub>CC</sub> –1.38 | V <sub>CC</sub> -1.32 | V <sub>CC</sub> -1.26 | V     |

# DC Electrical Characteristics<sup>(4)</sup>

$V_{CC} = +3.3V \pm 10\%$  or  $+5V \pm 10\%$  and  $V_{EE} = 0V$ ;  $V_{CC} = 0V$  and  $V_{EE} = -3.3V \pm 10\%$  or  $-5V \pm 10\%$ ;  $T_A = -40$ °C to +85°C; unless noted.

| Symbol          | Parameter           | Condition | Min                    | Тур | Max                    | Units |

|-----------------|---------------------|-----------|------------------------|-----|------------------------|-------|

| V <sub>OH</sub> | Output HIGH Voltage | Note 4    | V <sub>CC</sub> -1.085 |     | V <sub>CC</sub> -0.880 | V     |

| V <sub>OL</sub> | Output LOW Voltage  | Note 4    | V <sub>CC</sub> -1.830 |     | V <sub>CC</sub> -1.555 | V     |

| VIH             | Input HIGH Voltage  |           | V <sub>CC</sub> -1.165 |     | V <sub>CC</sub> -0.880 | V     |

| VIL             | Input LOW Voltage   |           | V <sub>CC</sub> -1.810 |     | V <sub>CC</sub> -1.475 | V     |

| $V_{PP}$        | Minimum Input Swing |           | 150                    |     |                        | mV    |

| IIH             | Input HIGH Current  | D         |                        |     | 150                    | μA    |

| IIL             | Input LOW Current   | D         | 0.5                    |     |                        | μA    |

Notes:

1. Exceeding the absolute maximum rating may damage the device.

2. The device is not guaranteed to function outside its operating rating.

3. Package thermal resistance assumes exposed pad is soldered (or equivalent) to the devices most negative potential on the PCB.

4. Output loaded with 50 $\Omega$  to V<sub>CC</sub>-2V.

# **AC Electrical Characteristics**

| Symbol                          | Parameter                                                |                    | Condition            | Min        | Тур      | Max        | Units    |

|---------------------------------|----------------------------------------------------------|--------------------|----------------------|------------|----------|------------|----------|

| t <sub>pd</sub>                 | Propagation Delay to:<br>/Q Output                       | D (Diff)<br>D (SE) |                      | 380<br>430 | ps<br>ps |            |          |

|                                 | QHG, /QHG Output                                         | D (Diff)<br>D (SE) |                      |            |          | 730<br>780 | ps<br>ps |

| ts                              | Set-Up Time                                              | EN                 |                      | 150        |          |            | ps       |

| t <sub>H</sub>                  | Hold Time                                                | EN                 |                      | 150        |          |            | ps       |

| t <sub>SKEW</sub>               | Duty Cycle Skew                                          | (Diff)             | Note 5               |            | 5        | 20         | ps       |

| V <sub>PP</sub>                 | Minimum Input Swing                                      |                    | Note 6               | 150        |          |            | mV       |

| V <sub>CMR</sub>                | Common Mode Range                                        | )                  | Note 7               | -1.3       |          | -0.4       | V        |

| t <sub>r</sub> , t <sub>f</sub> | Output /Q and QHG, /0<br>Rise/Fall Times<br>(20% to 80%) | QHG                | At full output swing | 100        | 225      | 350        | ps       |

$V_{EE} = V_{EE}$  (min) to  $V_{EE}$  (max);  $V_{CC} = GND$ ;  $T_A = -40^{\circ}C$  to +85°C; unless noted.

Notes:

5. Duty cycle skew is the difference between a  $t_{pd}$  propagation delay through a device.

Minimum input swing for which AC parameters are guaranteed. The device has a DC gain of ≈ 40 to Q, /Q outputs and a DC gain d ≈ 200 or higher to /Q<sub>HG</sub>, Q<sub>HG</sub> outputs.

7. The CMR range is referenced to the most positive side of the differential input signal. Normal operation is obtained if the HIGH level falls within the specified range and the peak-to-peak voltage lies between  $V_{PP}(min)$  and 1V. The lower end of the CMR range varies 1:1 with  $V_{EE}$ . The numbers in the spec table assume a nominal  $V_{EE} = -3.3V$ . Note for PECL operation, the  $V_{CMR}(min)$  will be fixed at  $3.3V - |V_{CMR}(min)|$ .

# Timing Diagram

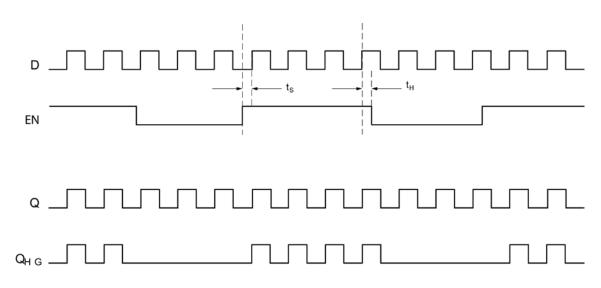

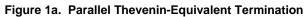

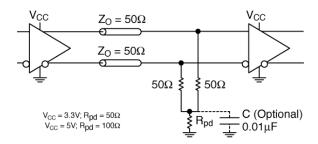

#### **Output Interface Applications**

Figure 1b. Three Resistor "Y" Termination

Figure 1c. Terminating Unused I/O

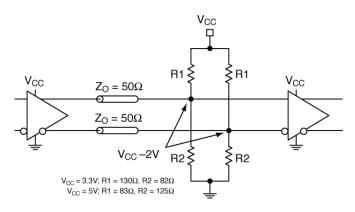

## **Package Information**

<u>SIDE VIEW</u>

8-Pin Ultra-Small EPAD-DFN

PCB Thermal Consideration for 8-Pin DFN Package

Package Notes:

- 1. Packaging meets Leve 2 qualification.

- 2. All pasrts are dry-packaged before shipment.

- 3. Exposed pads must be soldered to a ground for proper thermal management.

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA TEL +1 (408) 944-0800 FAX +1 (408) 474-1000 WEB http://www.micrel.com

The information furnished by Micrel in this data sheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2009 Micrel, Incorporated.