## 3.3V 200MHz PRECISION SPREAD-SPECTRUM CLOCK SYNTHESIZER

Precision Edge<sup>®</sup> SY89529L

### **FEATURES**

- Low voltage, 3.3V power supply operation

- 200MHz precision LVPECL output from a low cost 16.66MHz crystal

- 0.5% spread-spectrum modulation control

- >7dB reduction in EMI with spread-spectrum modulation

- LVTTL/LVCMOS compatible control inputs

- interfaces directly to a crystal

- Precision PLL architecture ensures < 30ps peak-to-peak, cycle-to-cycle output jitter

- 48%-to-52% precision duty cycle is ideal for doubledata-rate clocking applications

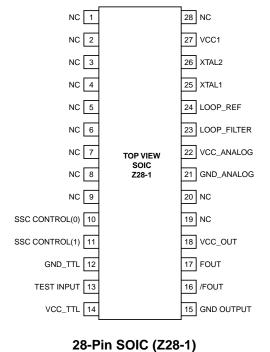

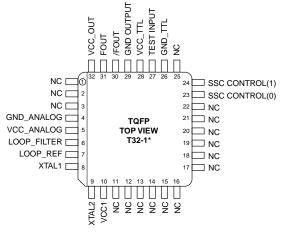

- Available in low cost 32-pin TQFP and 28-pin SOIC packages

### DESCRIPTION

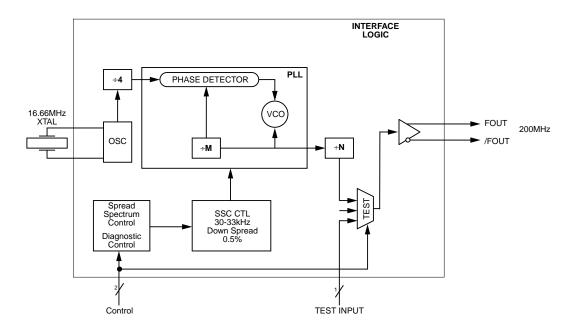

The SY89529L is a high-speed, precision PLL-based LVPECL clock synthesizer with spread-spectrum modulation control. With an external 16.66MHz crystal providing a reference frequency to the internal PLL, the differential PECL output frequency will be 200MHz with < 30ps (20ps typ.) peak-to-peak, cycle-to-cycle output jitter. The SY89529L spread-spectrum mode operates with a 30kHz triangle modulation with 0.5% down-spread (+0.0%/ -0.5%). When spread-spectrum is activated, the output signal is modulated which spreads the peak amplitudes and, thus, decreases EMI (Electro-Magnetic Interference).

### APPLICATIONS

- High-speed synchronous systems

- CPU clock

- Multi-processor workstations and servers

- Networking

M9999-110405 hbwhelp@micrel.com or (408) 955-1690

# PACKAGE/ORDERING INFORMATION

## Ordering Information<sup>(1)</sup>

| Part Number                    | Package<br>Type | Operating<br>Range | Package<br>Marking                            | Lead<br>Finish    |

|--------------------------------|-----------------|--------------------|-----------------------------------------------|-------------------|

| SY89529LZC                     | Z28-1           | Commercial         | SY89529LZC                                    | Sn-Pb             |

| SY89529LZCTR <sup>(2)</sup>    | Z28-1           | Commercial         | SY89529LZC                                    | Sn-Pb             |

| SY89529LTC                     | T32-1           | Commercial         | SY89529LTC                                    | Sn-Pb             |

| SY89529LTCTR <sup>(2)</sup>    | T32-1           | Commercial         | SY89529LTC                                    | Sn-Pb             |

| SY89529LZH <sup>(3)</sup>      | Z28-1           | Commercial         | SY89529LZH with Pb-Free bar-line indicator    | Pb-Free<br>NiPdAu |

| SY89529LZHTR <sup>(2, 3)</sup> | Z28-1           | Commercial         | SY89529LZH with Pb-Free bar-line indicator    | Pb-Free<br>NiPdAu |

| SY89529LTH <sup>(3)</sup>      | T32-1           | Commercial         | SY89529LTH with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

| SY89529LTHTR <sup>(2, 3)</sup> | T32-1           | Commercial         | SY89529LTH with<br>Pb-Free bar-line indicator | Pb-Free<br>NiPdAu |

#### Notes:

1. Contact factory for die availability. Dice are guaranteed at  $T_A = 25^{\circ}C$ , DC Electricals only.

2. Tape and Reel.

3. Pb-Free package is recommended for new designs.

32-Pin TQFP (T32-1)

## **BLOCK DIAGRAM**

|                  | C    | ommands |             |                                                         |  |  |

|------------------|------|---------|-------------|---------------------------------------------------------|--|--|

| SSC_CTL<br>(1:0) | vco  | SSC     | FOUT, /FOUT | Operational Modes                                       |  |  |

| 0 0              | —    | _       | —           | Reserved (Supplier Internal Test Mode)                  |  |  |

| 0 1              | Run  | Run     | 200MHz      | Default SSC; Modulation Factor = 0.5%                   |  |  |

| 1 0              | Stop | Stop    | TEST_I/O    | Diagnostic Mode; (1MHz $\leq$ TEST INPUT $\leq$ 200MHz) |  |  |

| 1 1              | Run  | Stop    | 200MHz      | No Spread-Spectrum                                      |  |  |

Table 1. SY89529L Control/Operational Modes

# **PIN DESCRIPTIONS**

## Input/Output Pins

| Pin Number<br>SOIC | Pin Number<br>TQFP | Pin Name          | I/O              | Pin Function                                                                                                                                                                                                                                                                                                                                              |

|--------------------|--------------------|-------------------|------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25,26              | 8, 9               | XTAL1, XTAL2      | Analog<br>Inputs | These pins form an oscillator when connected to an external crystal. Either series or parallel-resonant crystals are acceptable. Connect directly to the device.                                                                                                                                                                                          |

| 10, 11             | 23, 24             | SSC Control (0:1) | LVTTL<br>Inputs  | LVTTL-compatible spread-spectrum control pins. Data on<br>control pins maintain device control. For spread-spectrum<br>operation, leave SSC_0 and SSC_1 pins floating (default is<br>spread ON). To reconfigure the device, simply change the<br>SSC and the device will respond dynamically.<br>SSC_0 = $24k\Omega$ pullup. SSC_1 = $24k\Omega$ pulldown |

| 16, 17             | 30, 31             | FOUT, /FOUT       | Differential     | Differential, LVPECL clock outputs. These outputs must be terminated to $V_{CC}$ –2V. (see Figure 6)                                                                                                                                                                                                                                                      |

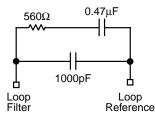

| 23                 | 6                  | LOOP_FILTER       | Analog I/O       | Used for the R//C PLL loop filter. (see Figure 2.)                                                                                                                                                                                                                                                                                                        |

| 24                 | 7                  | LOOP_REF          | Analog I/O       | Provides the reference voltage for the PLL. (see Figure 2).                                                                                                                                                                                                                                                                                               |

| 13                 | 27                 | TEST INPUT        | LVTTL<br>Inputs  | Pin is used for test and debug purposes. Is intended to be left floating in production environment. Programmed as input in PLL-bypass mode. Pin includes an internal $24k\Omega$ pullup resistor.                                                                                                                                                         |

## **Power Supply Pins**

| Pin Number<br>SOIC | Pin Number<br>TQFP | Pin Name                               | I/O             | Pin Function                                                                                                                                                                                                                                                               |

|--------------------|--------------------|----------------------------------------|-----------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 14, 27             | 10, 28             | V <sub>CC1</sub> , V <sub>CC_TTL</sub> | Logic<br>Power  | 3.3V LVTTL core logic power-supply pins. Connect each pin directly to the logic-supply plane and use proper bypassing at each pin as close to the pin as possible; Ferrite bead in parallel with $1\mu F/0.01\mu F$ capacitors. (see Figure 5 for typical bypass circuit.) |

| 22                 | 5                  | ANALOG_ V <sub>cc</sub><br>Power       | PLL             | 3.3V PLL core supply pin. Must be a noise free supply. Bypass as close to the pin as possible; ferrite bead in parallel with $1\mu$ F//0.01 $\mu$ F capacitors. (see Figure 5 for typical bypass circuit.)                                                                 |

| 18                 | 32                 | V <sub>cc_out</sub>                    | Output<br>Power | This is the positive power supply reference for the LVPECL outputs (FOUT and /FOUT). See Figure 5 for typical bypass circuit.                                                                                                                                              |

| 12                 | 26                 | GND_TTL                                | Logic           | This is the ground pin for for the TTL control logic. Normally connected to the logic ground.                                                                                                                                                                              |

| 21                 | 4                  | GND_ANALOG                             | Analog<br>GND   | This is the ground pin for the PLL Core. Normally connected to a quiet, noise-free ground plane for low jitter perfomance.                                                                                                                                                 |

| 15                 | 29                 | GND_OUTPUT                             | Output<br>GND   | Ground for differential outputs. Normally connected to the logic ground plane.                                                                                                                                                                                             |

## **No Connect Pins**

| Pin Number<br>SOIC | Pin Number<br>TQFP                                              | Pin Name | I/O           | Pin Function                                                                                                                                         |

|--------------------|-----------------------------------------------------------------|----------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6, 7, 8, 9, 19     | 1, 2, 3, 11, 12, 13<br>14, 15, 16, 17, 18<br>19, 20, 21, 22, 25 |          | No<br>Connect | Pins are high-impedance, low leakage and are not used by internal circuits of the device. These pins are intended to be left floating in production. |

### FUNCTIONAL DESCRIPTION AND TEST MODES

#### Introduction

The SY89529L supports three operational modes, as shown in Table 1, page 2. The three modes are spread-spectrum clocking (SSC), non-spread-spectrum clock, and a test mode dynamically controlled with the SSC\_Control pins. Unlike other synthesizers, the SY89529L can change spreadspectrum operation on the fly.

In SSC mode, the output clock is modulated (30KHz, triangle waveform) in order to achieve a reduction in EMI. In the PLL-bypass test mode, the PLL is disconnected as the source to the differential output, thus allowing an external source to be connected to the TEST INPUT pin. This is useful for in-circuit testing by enabling the differential output to be driven at a lower frequency.

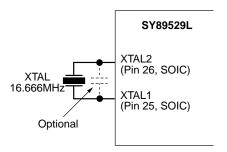

#### **Crystal Input and Oscillator Interface**

The SY89529L features a fully integrated on-board oscillator to minimize system implementation costs. The oscillator is a series resonant, multivibrator type design, and thus, a seriesresonant crystal is preferred, but not required.

A parallel-resonant crystal can be used with the SY89529L with only a minor error in the desired frequency. A parallel-resonant mode crystal used in a series resonant circuit will exhibit a frequency of oscillation a few hundred ppm lower than specified, a few hundred ppm translates to KHz inaccuracies. In a general computer application this level of inaccuracy is immaterial.

As the oscillator is somewhat sensitive to loading on its inputs, the user is advised to mount the crystal as close to the SY89529L as possible to avoid any board level parasitics. In addition, trace lengths should be matched. Figure 1 shows how to interface with a crystal. Table 2 illustrates the crystal specifications. If a start-up problem occurs, consider adding a 10pf capacitor across XTAL1 and XTAL2.

Quartz Crystal Selection:

(1) Raltron Series Resonant: AS-16.666-S-SMD-T-MI (2) Raltron Parallel Resonant: AS-16.666-18-SMD-T-MI

#### Figure 1. Crystal Interface

#### Loop Filter Design

The filter for any Phase Locked Loop (PLL) based device deserves special attention. SY89529L provides filter pins for an external filter. A simple three-component passive filter is required for achieving ultra low jitter. Figure 2 shows the recommended three-components. Due to the differential design, the filter is connected between LOOP\_FILTER and LOOP\_REF pins. With this configuration, extremely high supply noise rejection is achieved. It is important that the filter circuit and filter pins be isolated from any non-common mode coupling plane.

Figure 2. External Loop Filter Connection

| Output Frequency: 16.666MHz          |      |                |      |      |

|--------------------------------------|------|----------------|------|------|

| Mode of Oscillation: Fundamental     |      |                |      |      |

|                                      | Min. | Тур.           | Max. | Unit |

| Frequency Tolerance @25°C            | _    | ±30            | ±50  | ppm  |

| Frequency Stability over 0°C to 70°C | _    | ±50            | ±100 | ppm  |

| Operating Temperature Range          | -20  | —              | +70  | °C   |

| Storage Temperature Range            | -55  | —              | +125 | °C   |

| Aging (per yr/1st 3yrs)              | _    | —              | ±5   | ppm  |

| Load Capacitance                     | _    | 18 (or series) | _    | pF   |

| Equivalent Series Resistance (ESR)   | _    | —              | 50   | Ω    |

| Drive Level                          | _    | 100            | _    | μW   |

#### **Table 2. Quartz Crystal Oscillator Specifications**

#### **Spread Spectrum**

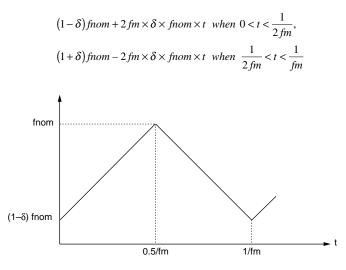

Spread-spectrum clocking is a frequency modulation technique for EMI reduction. When spread-spectrum is enabled, a 30kHz triangle waveform is used with 0.5% down-spread (+0.0%/-0.5%) from the nominal 200MHz clock frequency. An example of a triangle frequency modulation profile is shown in the figure 3 below. The ramp profile can be expressed as:

- Fnom = Nominal Clock Frequency in Spread OFF mode (200MHz with 16.66MHz IN)

- Fm = Nominal Modulation Frequency (30kHz)

- $\delta$  = Modulation Factor (0.5% down spread)

Figure 3. Triangle Frequency Modulation

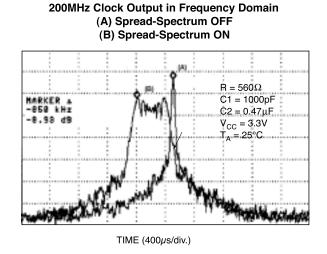

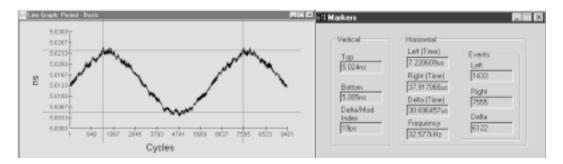

The SY89529L triangle modulation frequency deviation ( $\delta$ ) will not exceed 0.6% down-spread from the nominal clock frequency (+0.0%/–0.5%). An example of the amount of down spread relative to the nominal clock frequency can be seen in the frequency domain, as shown in Figure 4. The ratio of this width to the fundamental frequency is typically 0.5%, and will not exceed 0.6%. The resulting spectral reduction will be greater than 7dB, as shown in Figure 5. It is important to note the SY89529L 7dB minimum spectral reduction is the component-specific EMI reduction, and will not necessarily be the same as the system EMI reduction.

Figure 5. 200MHz Clock Output in Frequency Domain

Figure 4. 0.38% Modulation, 32.7KHz Modulation Frequency

#### **Power Supply Filtering Techniques**

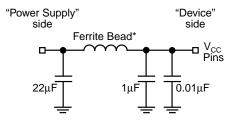

As in any high speed integrated circuits, power supply filtering is very important.  $V_{CC1}$ ,  $V_{CC}$ -Analog,  $V_{CC_TTL}$  and  $V_{CC_OUT}$  should be individually connected to the power supply plane through vias, and bypass capacitors should be used for each pin. To achieve optimum jitter performance, better power-supply isolation is required. In this case a ferrite bead along with a 1µF and a 0.01µF bypass capacitor should be connected to each power supply pin. Figure 6 illustrates power-supply filtering using ferrite beads and bypass capacitors.

\*For Vcc\_Analog,Vcc\_ttL, Vcc1, use ferrite bead = 200mA, 0.45Ω DC, Murata P/N BLM21A1025

\*For Vcc\_out use ferrite bead = 3A,  $0.025\Omega$  DC, Murata, P/N BLM31P005

\*Componet sizs: 0805

Figure 5. Power Supply Filtering

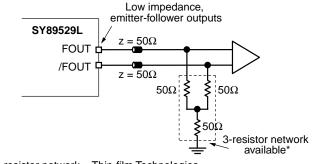

#### **Termination for PECL Outputs**

The differential PECL outputs, FOUT and /FOUT, are lowimpedance emitter-follower outputs. Therefore, terminating resistors (DC current path to ground) or current sources must be used for functionality. These outputs are designed to drive  $50\Omega$  transmission lines. Matched impedance techniques should be used to maximize operating frequency and minimize signal distortion. There are a few simple termination schemes. Figure 7 shows a common 3-resistor termination scheme. For more termination examples, see Micrel's Application Note 9 online at www.micrel.com.

\*3-resistor network = Thin-film Technologies, P/N TFT-RN1632-AN1DNC

Figure7. LVPECL Output Termination

## ABSOLUTE MAXIMUM RATINGS<sup>(1)</sup>

| Symbol             | Parameter            |                       | Value                      | Unit |              |   |

|--------------------|----------------------|-----------------------|----------------------------|------|--------------|---|

| V <sub>CC</sub>    | Power Supply Voltage |                       | -0.5 to +7.0               | V    |              |   |

| V <sub>IN</sub>    | Input Voltage        |                       | Input Voltage -0.5 to +7.0 |      | -0.5 to +7.0 | V |

| I <sub>OUT</sub>   | Output Source        | –Continuous<br>–Surge | 50<br>100                  | mA   |              |   |

| T <sub>LEAD</sub>  | Lead Temperature (sc | Idering, 20sec.)      | 260                        | °C   |              |   |

| T <sub>store</sub> | Storage Temperature  |                       | -65 to +150                | °C   |              |   |

| T <sub>A</sub>     | Operating Temperatur | e                     | –0 to +75                  | °C   |              |   |

NOTE:

1. Permanent device damage may occur if absolute maximum ratings are exceeded. This is a stress rating only and functional operation is not implied at conditions other than those detailed in the operational sections of this data sheet. Exposure to absolute maximum rating conditions for extended periods may affect device reliability.

## LVPECL DC ELECTRICAL CHARACTERISTICS

## $V_{CC1} = V_{CC\_}Analog = V_{CC\_TTL} = V_{CC\_OUT} = +3.3V \pm 10\%; T_A = 0^{\circ}C \text{ to } +85^{\circ}C$

| Symbol           | Parameter           | Min.                       | Тур. | Max.                       | Unit | Condition                              |

|------------------|---------------------|----------------------------|------|----------------------------|------|----------------------------------------|

| V <sub>OH</sub>  | Output HIGH Voltage | V <sub>CC_OUT</sub> -1.075 | _    | V <sub>CC_OUT</sub> -0.830 | V    | 50 $\Omega$ to V <sub>CC_OUT</sub> –2V |

| V <sub>OL</sub>  | Output LOW Voltage  | V <sub>CC_OUT</sub> -1.860 | _    | V <sub>CC_OUT</sub> -1.570 | V    | 50 $\Omega$ to V <sub>CC_OUT</sub> –2V |

| V <sub>CMR</sub> | Common Mode Range   | 600                        | 700  | 800                        | mV   |                                        |

## LVTTL DC ELECTRICAL CHARACTERISTICS

$V_{CC1} = V_{CC}$ Analog =  $V_{CC}$ TTL =  $V_{CC}$ OUT = +3.3V ±10%; T<sub>A</sub> = 0°C to +85°C

| Symbol          | Paramet                                                                             | er                                                                                       | Min.                           | Тур.                          | Max.                            | Unit     | Condition               |

|-----------------|-------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------|--------------------------------|-------------------------------|---------------------------------|----------|-------------------------|

|                 | Power Supply Voltage<br>(V <sub>CC</sub> _Analog, V <sub>CC1</sub> , V <sub>C</sub> | c_out, V <sub>CC_TTL</sub> )                                                             | 3.135                          | 3.3                           | 3.465                           | V        |                         |

| ∨ <sub>IH</sub> | Input HIGH Voltage                                                                  | SSC<br>TEST INPUT                                                                        | 2.0<br>V <sub>CC</sub> /2 +0.3 |                               | V <sub>CC</sub> +0.3            | V<br>V   | Note 1                  |

| V <sub>IL</sub> | Input LOW Voltage                                                                   | SSC<br>TEST INPUT                                                                        | -0.3<br>—                      |                               | 0.80<br>V <sub>CC</sub> /2 –0.3 | V<br>V   | Note 1                  |

| V <sub>IK</sub> | Input Clamp Voltage                                                                 |                                                                                          | _                              | _                             | -1.2                            | V        | I <sub>IN</sub> = -12mA |

| IIH             | Input HIGH Current                                                                  | SSC<br>TEST INPUT                                                                        | _                              | _                             | 50<br>50                        | μΑ<br>μΑ | Note 2                  |

| I <sub>IL</sub> | Input LOW Current                                                                   | SSC<br>TEST INPUT                                                                        | _                              | _                             | 0.60<br>0.60                    | mA<br>mA | Note 2                  |

| I <sub>CC</sub> | Total Supply Current<br>Typcial % of I <sub>CC</sub>                                | V <sub>CC1</sub><br>V <sub>CC_OUT</sub><br>V <sub>CC</sub> Analog<br>V <sub>CC_TTL</sub> | <br>                           | 110<br>14%<br>5%<br>5%<br>76% | 145<br>—<br>—<br>—<br>—         | mA       | No output load          |

NOTES:

1. For TEST INPUT, input threshold is  $V_{CC}/2$ .

2. Posituve and negative-going input threshold is set internally to track  $V_{CC}\!/\!2.$

# AC ELECTRICAL CHARACTERISTICS

$V_{CC1} = V_{CC}$ Analog =  $V_{CC}$ TTL =  $V_{CC}OUT$  = +3.3V ±10%; T<sub>A</sub> = 0°C to +85°C

| Symbol                           | Parameter                                          | Min. | Тур.  | Max.  | Unit | Condition                    |

|----------------------------------|----------------------------------------------------|------|-------|-------|------|------------------------------|

| F <sub>M</sub>                   | SSC Modulation Frequency                           | 30   | —     | 33.33 | KHz  |                              |

| F <sub>MF</sub>                  | SSC Modulation Factor                              | _    | 0.5   | 0.6   | %    |                              |

| S <sub>RED'N</sub>               | Spectral Reduction                                 | 7    | 9     | _     | dB   | FOUT = 200MHz <sup>(2)</sup> |

| F <sub>XTAL</sub>                | Crystal Input Range                                | 14   | 16.66 | 18    | MHz  |                              |

| t <sub>DC</sub>                  | Output Duty Cycle <sup>(1)</sup>                   | 48   |       | 52    | %    | FOUT = 200MHz                |

| t <sub>JIT</sub>                 | Peak-to-Peak, Cycle-to-Cycle Jitter <sup>(1)</sup> | _    | 20    | 30    | ps   | FOUT = 200MHz                |

| t <sub>PERIOD</sub>              | Output Period <sup>(1)</sup>                       | 4995 |       | 5005  | ps   | FOUT = 200MHz                |

| t <sub>STABLE</sub>              | Power-Up to Stable Clock<br>Output                 | _    | —     | 10    | ms   |                              |

| t <sub>r</sub><br>t <sub>f</sub> | Output Rise/Fall Times<br>(20% to 80%)             | 300  | -     | 800   | ps   | FOUT, /FOUT                  |

#### NOTES:

1. Spread-spectrum clocking enabled.

2. SY89529L spectral reduction is the component-specific indication of EMI reduction. The SY89529L's spectral peak reduction is not necessarily the same as the system EMI reduction.

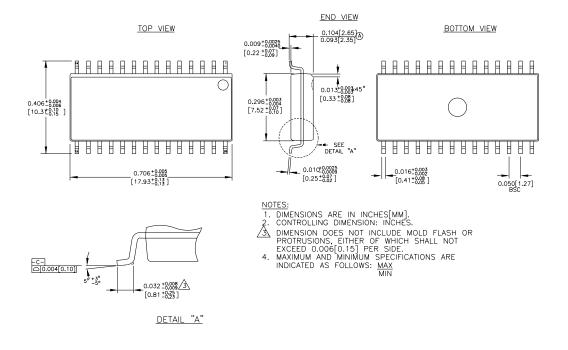

## 28-PIN SOIC .300" WIDE (Z28-1)

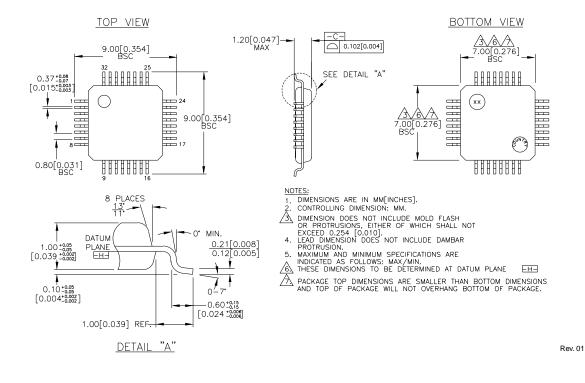

### 32-PIN TQFP (T32-1)

#### MICREL, INC. 2180 FORTUNE DRIVE SAN JOSE, CA 95131 USA

тец + 1 (408) 944-0800 FAX + 1 (408) 474-1000 web http://www.micrel.com

The information furnished by Micrel in this datasheet is believed to be accurate and reliable. However, no responsibility is assumed by Micrel for its use. Micrel reserves the right to change circuitry and specifications at any time without notification to the customer.

Micrel Products are not designed or authorized for use as components in life support appliances, devices or systems where malfunction of a product can reasonably be expected to result in personal injury. Life support devices or systems are devices or systems that (a) are intended for surgical implant into the body or (b) support or sustain life, and whose failure to perform can be reasonably expected to result in a significant injury to the user. A Purchaser's use or sale of Micrel Products for use in life support appliances, devices or systems is at Purchaser's own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale.

© 2005 Micrel, Incorporated.