Si9241

#### Siliconix

# Single-Ended Bus Driver

#### **Features**

- Single-Ended Transceiver

- Survives Shorts and Transients on Automotive Bus

- Wide Power Supply Voltage Range

- Fault Detection

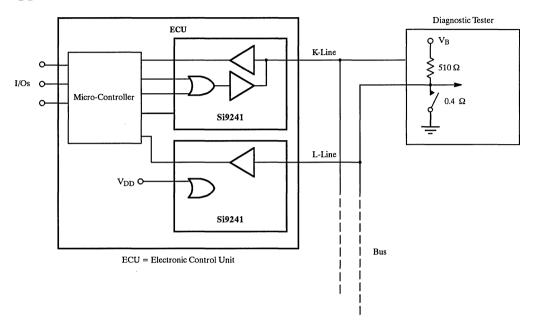

- ISO 9141 Compatible

#### **Benefits**

- Single-Wire Multiplexer Interface

- ISO Diagnosis Bus

#### **Applications**

- Automobiles

- Trucks

- Tractors

#### **Description**

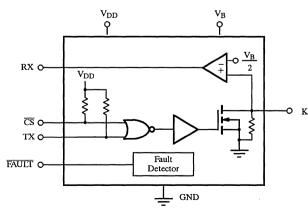

The Si9241 is a monolithic bus driver designed to provide bidirectional serial communication in automotive diagnostic applications.

The device incorporates protection against overvoltages and short circuits to GND or V<sub>B</sub>. The transceiver pin is protected and can be driven beyond the V<sub>B</sub> voltage.

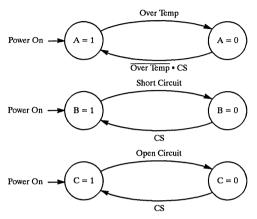

A fault detector provides an active low in case of short circuit to V<sub>B</sub> or an open load prevent proper data transmission. The open drain Fault output can be wire or-ed. The CS input can be tied high for receive only interfaces.

In the event of an over temperature condition, the output is immediately switched off and a fault indicated. This condition can only be reset once the over temperature condition is removed, and  $\overline{\text{CS}}$  is toggled high.

The Si9241 is built on the Siliconix BiC/DMOS process. This process supports bipolar transistors, CMOS and DMOS. An epitaxial layer prevents latchup.

The RX output is capable of driving CMOS or 1 × LSTTL load.

The Si9241 is available in a space efficient 8-pin SO package. It operates reliably over the automotive temperature range (-40 to 125°C).

#### Pin Configurations and Functional Block Diagram

**Bus Interface**

P-34770-Rev. A (04/05/94)

Si9241 Siliconix

## **Output Table and State Diagrams**

| Inputs CS TX |   | State<br>Variable |   |   |     | Outpi<br>Table |       |               |  |

|--------------|---|-------------------|---|---|-----|----------------|-------|---------------|--|

|              |   | A                 | В | С | RXK | K              | FAULT | Comments      |  |

| 0            | 0 | 1                 | 1 | 1 | 0   | 0              | 1     |               |  |

| 0            | 1 | 1                 | 1 | 1 | 1   | 1              | 1     |               |  |

| x            | x | 0                 | 1 | 1 | K   | HiZ            | 0     | Over Temp     |  |

| 0            | х | 1                 | 0 | 1 | K   | ΗıΖ            | 0     | Short Circuit |  |

| 0            | х | 1                 | 1 | 0 | K   | HiZ            | 0     | Open Circuit  |  |

| 1            | x | 1                 | 1 | 1 | 0   | 0              | 1     | Receive Mode  |  |

| 1            | х | 1                 | 1 | 1 | 1   | 1              | 1     |               |  |

X = "1" or "0" HiZ = High Impedance State

Note: Over Temp is a condition and not meant to be a logic signal.

## **Absolute Maximum Ratings**

| Voltage Referenced to Ground       |

|------------------------------------|

| Voltage On $V_{BAT}$               |

| Voltage K –3 to $V_{BAT}$ + 1 V    |

| Voltage or Max. Current On Any Pin |

| (Except $V_{BAT}$ , K)             |

| Voltage on V <sub>DD</sub>              | 7 V          |

|-----------------------------------------|--------------|

| Short Circuit Duration (to VBAT or GND) | Continuous   |

| Operating Temperature (TA)              | -40 to 125°C |

| Junction and Storage Temperature        | 55 to 150°C  |

| Thermal Resistance $\Theta_{1A}$        | TBD          |

## Specifications<sup>a</sup>

|                                   |                                 | Test Conditions<br>Unless Otherwise Specified                                  |       | Limits E Suffix: -40 to 125°C |                  |                      |      |

|-----------------------------------|---------------------------------|--------------------------------------------------------------------------------|-------|-------------------------------|------------------|----------------------|------|

| Parameter Symbol                  |                                 | $V_{DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{BAT} = 8 \text{ to } 35 \text{ V}$ | Tempb | Min <sup>c</sup>              | Typ <sup>d</sup> | Maxc                 | Unit |

| Transmitter and Logic Le          | vels                            |                                                                                |       |                               |                  |                      |      |

| CS, TX Input Low Voltage          | V <sub>ILT</sub>                | :                                                                              | Full  |                               |                  | 1.5                  |      |

| CS, TX Input High Voltage         | V <sub>IHT</sub>                |                                                                                | Full  | 3.5                           |                  |                      | ,    |

| K Output Low Voltage              | V <sub>OLK</sub>                |                                                                                | Full  |                               |                  | 0.2 V <sub>BAT</sub> | v    |

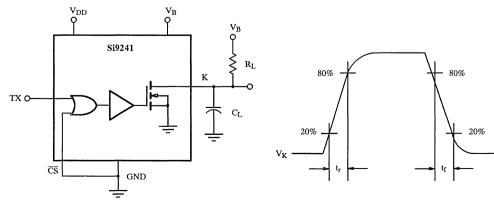

| K Output High Voltage             | V <sub>OHK</sub>                | $R_L = 510 \Omega$ , $C_L = 10 nF$<br>See Test Circuit                         | Full  | 0.91 V <sub>BAT</sub>         |                  |                      |      |

| K Rise, Fall Times                | t <sub>r</sub> , t <sub>f</sub> |                                                                                | Fuli  |                               |                  | 96                   | μs   |

| K Output Sink Resistance          | Rsi                             | $\overline{\text{CS}} = 0 \text{ V, TX} = 0 \text{ V}$                         | Full  |                               |                  | 110                  | Ω    |

| K Output Capacitance <sup>e</sup> | Co                              | $\overline{\text{CS}} = 0 \text{ V}$                                           | Full  |                               |                  | 20                   | "E   |

| TX Input Capacitance <sup>e</sup> | C <sub>INT</sub>                |                                                                                | Full  |                               |                  | 10                   | pF   |

| CS, TX Input Current              | I <sub>INT</sub>                |                                                                                | Full  | -60                           |                  | -4                   | μА   |

5-2 P-34770—Rev. A (04/05/94)

Si9241 Siliconix

## **Specifications**<sup>a</sup>

|                                   |                   | Unl                                                                                    | Test Conditions<br>ess Otherwise Specified                       |       | Limits<br>E Suffix: -40 to 125°C |                         |                       |        |

|-----------------------------------|-------------------|----------------------------------------------------------------------------------------|------------------------------------------------------------------|-------|----------------------------------|-------------------------|-----------------------|--------|

| Parameter                         | Symbol            | $V_{\rm DD} = 4.5 \text{ to } 5.5 \text{ V}, V_{\rm BAT} = 8 \text{ to } 35 \text{ V}$ |                                                                  | Tempb | Min <sup>c</sup>                 | Typd                    | Maxc                  | Unit   |

| Receiver                          |                   |                                                                                        |                                                                  | •     |                                  |                         |                       |        |

| K Input Low Voltagef              | V <sub>ILK</sub>  |                                                                                        |                                                                  | Full  |                                  | 0.4<br>V <sub>BAT</sub> | 0.30 V <sub>BAT</sub> |        |

| K Input High Voltage <sup>f</sup> | V <sub>IHK</sub>  |                                                                                        |                                                                  | Full  | 0.70 V <sub>BAT</sub>            | 0.6<br>V <sub>BAT</sub> |                       | V      |

| RX Output Low Voltage             | V <sub>OLR</sub>  |                                                                                        | $V_{ILK}$ , $V_{ILL} = 0.30 V_{BAT}$<br>$I_{OLR} = 1 \text{ mA}$ | Full  |                                  |                         | 0.4                   |        |

| RX High Voltage                   | V <sub>OHR</sub>  | $\overline{\text{CS}} = 4 \text{ V}$                                                   | $V_{IHK}$ , $V_{IHL} = 0.70 V_{BAT}$<br>$I_{OHR} = -40 \mu A$    | Full  | 2.8                              |                         |                       |        |

| K Input Currents                  | $I_{IHK}$         |                                                                                        | $V_{IHK} = V_{BAT}$                                              | Full  | 15                               |                         | 20                    | μА     |

| Supplies                          |                   |                                                                                        |                                                                  |       |                                  |                         |                       |        |

| Bat Supply Current                | I <sub>BAT</sub>  | CS, TX = 1.5 V<br>K Open                                                               |                                                                  | Full  |                                  | 2.7                     | 5.0                   | mA     |

| Logic Supply Current              | $I_{\mathrm{DD}}$ |                                                                                        |                                                                  | Full  |                                  | 1                       | 3.0                   | IIIA   |

| Miscellaneous                     |                   |                                                                                        |                                                                  |       |                                  |                         |                       |        |

| Baud Rate                         | BR                | F                                                                                      | $R_{\rm L} = 510 \Omega,  C_{\rm L} = 10 \rm nF$                 | Full  | 10.4                             |                         |                       | k Baud |

| Fault Output Low Voltage          | V <sub>OLF</sub>  | V <sub>ILT</sub> =                                                                     | $= 0V$ , $V_K = V_B$ , $I_{OLF} = 1 \text{ mA}$                  | Full  |                                  |                         | 0.4                   | V      |

- Notes

a. Refer to PROCESS OPTION FLOWCHART for additional information.

b. Room = 25°C, Cold and Hot = as determined by the operating temperature suffix.

c. The algebraic convention whereby the most negative value is a minimum and the most positive a maximum, is used in this data sheet.

d. Typical values are for DESIGN AID ONLY, not guaranteed nor subject to production testing.

Guaranteed by design, not subject to production test

- Guaranteed by design, not subject to production test Hysterisis 0.2 V<sub>BAT</sub> typical.

#### **Test Circuit**

Bus Interface 07

Si9241 Siliconix

# Application

5-4 P-34770—Rev. A (04/05/94)