# Model Name: T320HVN05.2

## Issue Date : 2013/11/01

## (\*)Preliminary Specifications

## ()Final Specifications

| Customer Signature | Date | AUO                                                   | Date |  |

|--------------------|------|-------------------------------------------------------|------|--|

| Approved By        |      | Approval By PM Director<br>Tsang Kalai-Shang          |      |  |

| Note               |      | Reviewed By RD Director<br>Reviewed By Project Leader |      |  |

|                    |      | Prepared By PM<br>Blaine Huang                        |      |  |

## CONTENTS

| 1. | GEN   | ERAL DESCRIPTION                                      | 4  |

|----|-------|-------------------------------------------------------|----|

| 2. | ABS   | OLUTE MAXIMUM RATINGS                                 | 5  |

| 3. | ELE   | CTRICAL SPECIFICATION                                 |    |

|    |       |                                                       |    |

|    | 3.1   | ELECTRICAL CHARACTERISTICS                            |    |

|    | 3.1.1 |                                                       |    |

|    | 3.1.2 |                                                       |    |

|    | 3.1.3 |                                                       |    |

|    | 3.2   | INTERFACE CONNECTIONS                                 |    |

|    | 3.2.1 |                                                       |    |

|    | 3.2.2 |                                                       |    |

|    | 3.2.3 |                                                       |    |

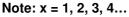

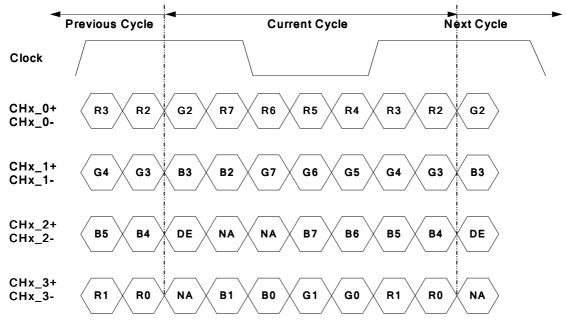

|    | 3.3   | SIGNAL TIMING WAVEFORMS                               |    |

|    | 3.4   | COLOR INPUT DATA REFERENCE                            |    |

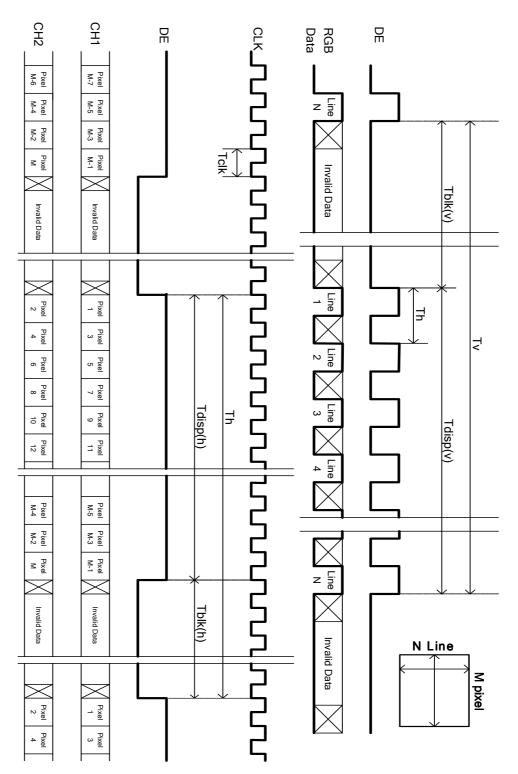

|    | 3.5   | POWER SEQUENCE FOR LCD                                |    |

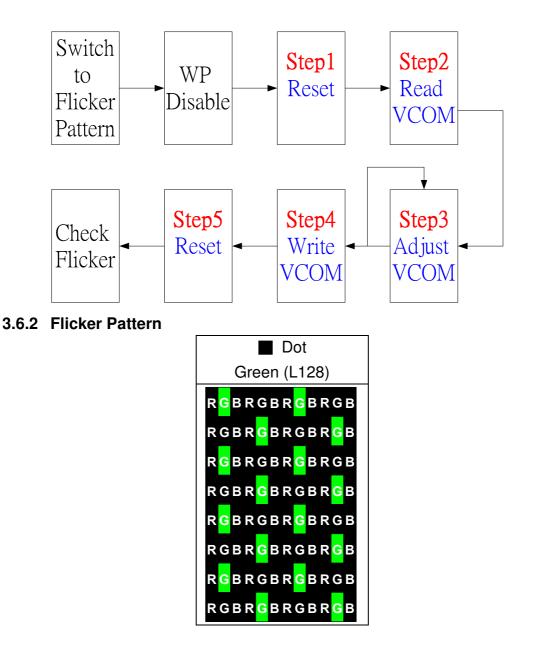

|    | 3.6   | VCOM ADJUST SOP                                       |    |

|    | 3.6.1 |                                                       |    |

|    | 3.6.2 |                                                       |    |

|    | 3.6.3 |                                                       |    |

|    | 3.6.4 | 0                                                     |    |

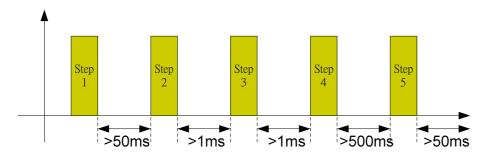

|    | 3.6.5 | Interval of Step to Step                              | 17 |

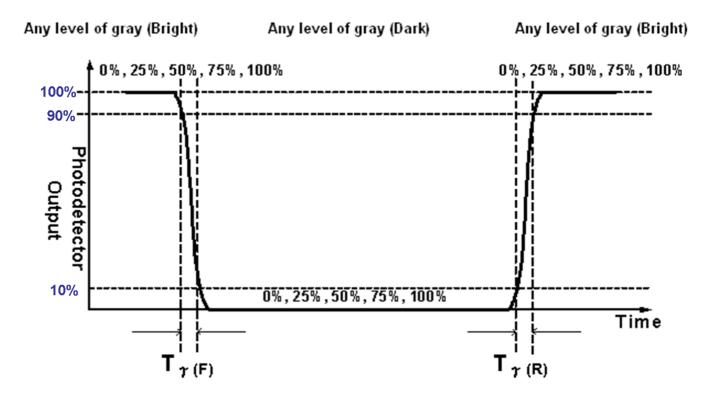

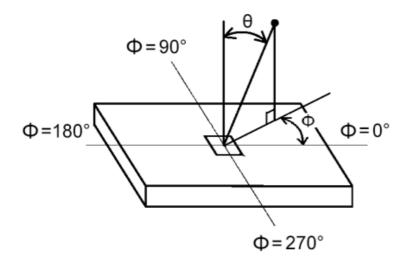

| 4. | ОРТ   | ICAL SPECIFICATION                                    |    |

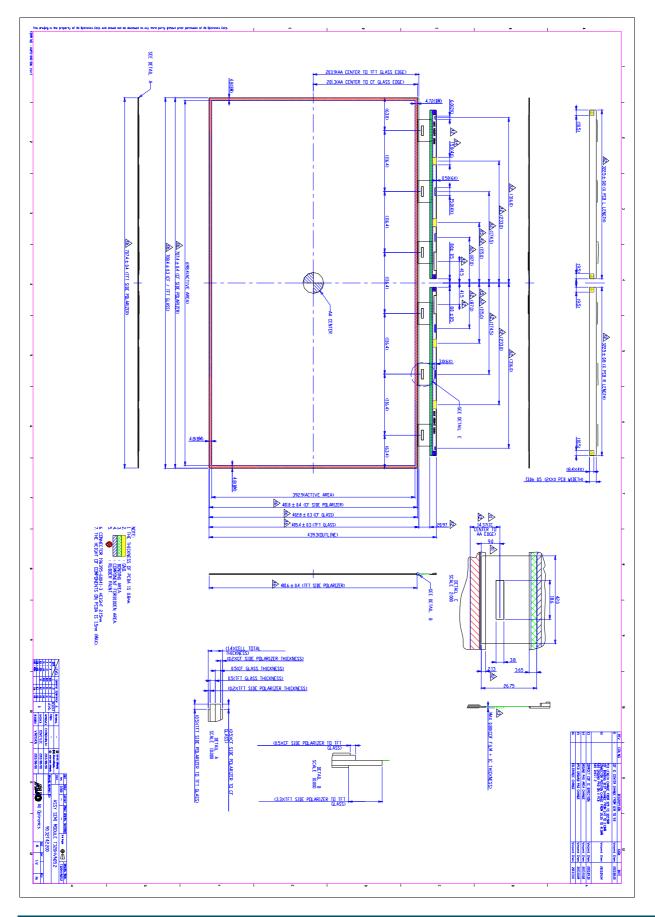

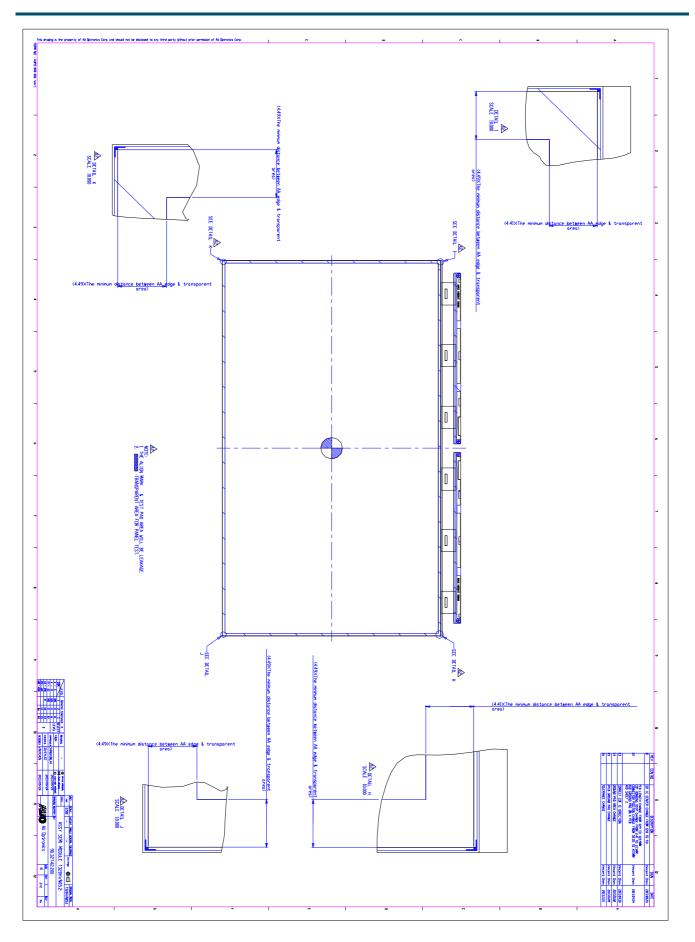

| 5. | MEC   | CHANICAL CHARACTERISTICS                              | 22 |

| 6. | PAC   | KING                                                  | 24 |

|    |       |                                                       |    |

| 7. | PRE   | CAUTIONS                                              | 26 |

|    | 7.1   | MOUNTING PRECAUTIONS                                  | 26 |

|    | 7.2   | OPERATING PRECAUTIONS                                 | 26 |

|    | 7.3   | ELECTROSTATIC DISCHARGE CONTROL                       | 26 |

|    | 7.4   | PRECAUTIONS FOR STRONG LIGHT EXPOSURE                 | 27 |

|    | 7.5   | STORAGE                                               | 27 |

|    | 7.6   | HANDLING PRECAUTIONS FOR PROTECTION FILM OF POLARIZER | 27 |

## **RECORD OF REVISION**

| Version | Date       | Page | Description                                             |

|---------|------------|------|---------------------------------------------------------|

| 0.0     | 2013/10/28 |      | First release                                           |

| 0.1     | 2013/11/01 | 18   | Contrast Ratio                                          |

|         |            | 18   | Color Chromaticity                                      |

|         |            | 22   | Mechanical Characteristics has been modified tolerance. |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

|         |            |      |                                                         |

### **1. General Description**

This specification applies to the 32 inch Color TFT-LCD SKD model T320HVN05.2. This Open Cell Unit has a TFT active matrix type liquid crystal panel 1,920x1,080 pixels, and diagonal size of 32 inch. This Open Cell Unit supports 1,920x1,080 mode. Each pixel is divided into Red, Green and Blue sub-pixels or dots which are arranged in vertical stripes. Gray scale or the brightness of the sub-pixel color is determined with a 8-bit gray scale signal for each dot.

## \* General Information

| Items                  | Specification                   | Unit   | Note              |

|------------------------|---------------------------------|--------|-------------------|

| Active Screen Size     | 32                              | inch   |                   |

| Display Area           | 698.4 (H) x 392.85 (V)          | mm     |                   |

| Outline Dimension      | 708.4 (H) x 439.3 (V) x 1.4 (D) | mm     |                   |

| Cell Dimension         | 708.4 (H) x 405.4 (V) x 1.4(D)  | mm     | D: cell thickness |

| Driver Element         | a-Si TFT active matrix          |        |                   |

| Display Colors         | 8 bit                           | Colors |                   |

| Number of Pixels       | 1,920x1,080                     | Pixel  |                   |

| Pixel Pitch            | 0.36375 (H) x 0.36375 (W)       | mm     |                   |

| Pixel Arrangement      | RGB vertical stripe             |        |                   |

| Display Operation Mode | Normally Black                  |        |                   |

| Surface Treatment      | Anti-Glare, 3H                  |        | Haze=2%           |

| Weight                 | Тур. 875                        | g      |                   |

| Rotate Function        | Unachievable                    |        | Note 1            |

| Display Orientation    | Signal input with "ABC"         |        | Note 2            |

Note 1: Rotate Function refers to LCD display could be able to rotate.

Note 2: LCD display as below illustrated when signal input with "ABC".

Front side

### 2. Absolute Maximum Ratings

The followings are maximum values which, if exceeded, may cause faulty operation or damage to the unit

| Item                      | Symbol          | Min  | Мах | Unit                 | Conditions |

|---------------------------|-----------------|------|-----|----------------------|------------|

| Logic/LCD Drive Voltage   | V <sub>DD</sub> | -0.3 | 14  | [Volt] <sub>DC</sub> | Note 1     |

| Input Voltage of Signal   | Vin             | -0.3 | 4   | [Volt] <sub>DC</sub> | Note 1     |

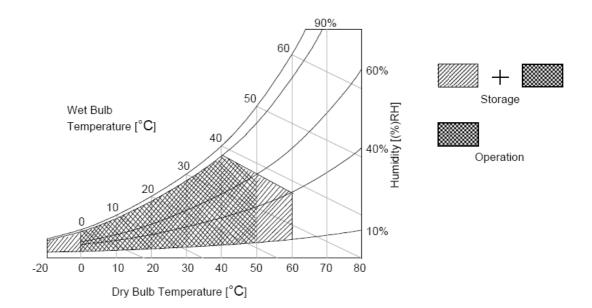

| Operating Temperature     | TOP             | 0    | +50 | [°C]                 | Note 2     |

| Operating Humidity        | HOP             | 10   | 90  | [%RH]                | Note 2     |

| Storage Temperature       | TST             | -20  | +60 | [°C]                 | Note 2     |

| Storage Humidity          | HST             | 10   | 90  | [%RH]                | Note 2     |

| Panel Surface Temperature | PST             |      | 65  | [°C]                 | Note 3     |

| Electro Statistic Voltage | ESD             |      | ±2  | [KV]                 | Note 4     |

Note 1: Duration:50 msec.

Note 2 : Maximum Wet-Bulb should be  $39^\circ\!\mathrm{C}$  and No condensation.

The relative humidity must not exceed 90% non-condensing at temperatures of  $40^{\circ}$ C or less. At temperatures greater than  $40^{\circ}$ C, the wet bulb temperature must not exceed  $39^{\circ}$ C.

Note 3: Surface temperature is measured at 50  $^\circ\! \mathbb C$  Dry condition

Note 4: ESD protection procedure must be applied during production process; especially polarizer protection films remove process. Please directly contact AUO if module process advice is required.

## 3. Electrical Specification

The T320HVN05.2 Open Cell Unit requires power input which is employed to power the LCD electronics and to drive the TFT array and liquid crystal.

#### 3.1 Electrical Characteristics

#### 3.1.1 DC Characteristics

|                                                  | Parameter                                    | Symbol                    |      | Value | Unit                 | Note                        |      |

|--------------------------------------------------|----------------------------------------------|---------------------------|------|-------|----------------------|-----------------------------|------|

|                                                  |                                              | Symbol                    | Min. | Тур.  | Max                  |                             | Unit |

| LCD                                              |                                              |                           |      |       |                      |                             |      |

| Power Sup                                        | oly Input Voltage                            | V <sub>DD</sub>           | 10.8 | 12    | 13.2                 | V <sub>DC</sub>             |      |

| Power Supp                                       | oly Input Current                            | I <sub>DD</sub>           |      | 0.34  | 0.6                  | A                           | 1    |

| Power Con                                        | sumption                                     | Pc                        |      | 4.08  | 7.2                  | Watt                        | 1    |

| Inrush Current                                   |                                              | I <sub>RUSH</sub>         |      |       | 4                    | А                           | 2    |

| Permissible Ripple of Power Supply Input Voltage |                                              | V <sub>RP</sub>           |      |       | V <sub>DD</sub> * 5% | $mV_{pk\text{-}pk}$         | 3    |

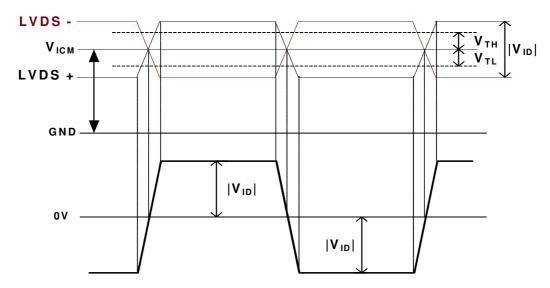

|                                                  | Input Differential Voltage                   | V <sub>ID</sub>           | 200  | 400   | 600                  | $\mathrm{mV}_{\mathrm{DC}}$ | 4    |

| LVDS                                             | Differential Input High Threshold<br>Voltage | V <sub>TH</sub>           | +100 |       | +300                 | mV <sub>DC</sub>            | 4    |

| Interface                                        | Differential Input Low Threshold<br>Voltage  | V <sub>TL</sub>           | -300 |       | -100                 | mV <sub>DC</sub>            | 4    |

|                                                  | Input Common Mode Voltage                    | V <sub>ICM</sub>          | 1.1  | 1.25  | 1.4                  | V <sub>DC</sub>             | 4    |

| CMOS                                             | Input High Threshold Voltage                 | V <sub>IH</sub><br>(High) | 2.7  |       | 3.3                  | V <sub>DC</sub>             | 5    |

| Interface                                        | Input Low Threshold Voltage                  | V <sub>IL</sub><br>(Low)  | 0    |       | 0.6                  | $V_{\text{DC}}$             | 5    |

#### 3.1.2 AC Characteristics

| Parameter         |                                                              | Symbol  |              | Value | Unit        | Note |      |

|-------------------|--------------------------------------------------------------|---------|--------------|-------|-------------|------|------|

|                   | Falamelei                                                    | Symbol  | Min.         | Тур.  | Max         | Unit | Note |

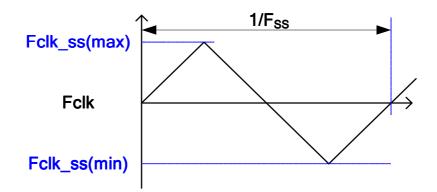

| LVDS<br>Interface | Receiver Clock : Spread Spectrum<br>Modulation range         | Fclk_ss | Fclk<br>-3%  |       | Fclk<br>+3% | MHz  | 6    |

|                   | Receiver Clock : Spread Spectrum<br>Modulation frequency     | Fss     | 30           |       | 200         | KHz  | 6    |

|                   | Receiver Data Input Margin<br>Fclk = 85 MHz<br>Fclk = 65 MHz | tRMG    | -0.4<br>-0.5 |       | 0.4<br>0.5  | ns   | 7    |

#### 3.1.3 DRIVER CHARACTERISTICS

| Item                       | Symbol | Min | Max | Unit | condition |

|----------------------------|--------|-----|-----|------|-----------|

| Driver Surface Temperature | DST    |     | 100 | [°C] | Note      |

Note : Any point on the driver surface must be less than 100°C under any conditions

#### Note :

- 1. Test Condition:

- (1)  $V_{DD} = 12.0V$

- (2) Fv = 60Hz

- (3) Fclk= Max freq.

- (4) Temperature = 25 °C

- (5) Typ. Input current : White Pattern Max. Input current: Heavy loading pattern defined by AUO

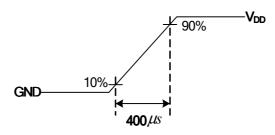

- 2. Measurement condition : Rising time = 400us

- 3. Test Condition:

- (1) The measure point of  $V_{RP}$  is in LCM side after connecting the System Board and LCM.

- (2) Under Max. Input current spec. condition.

**4.**  $V_{ICM} = 1.25V$

5. The measure points of  $V_{IH}$  and  $V_{IL}$  are in LCM side after connecting the System Board and LCM.

6. LVDS Receiver Clock SSCG (Spread spectrum clock generator) is defined as below figures.

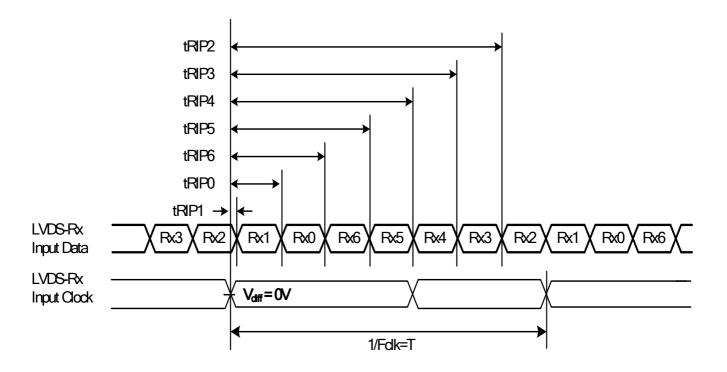

7. Receiver Data Input Margin

| Parameter             | Symbol |            | Unit | Note       |      |          |

|-----------------------|--------|------------|------|------------|------|----------|

| Falameter             | Symbol | Min        | Туре | Мах        | Unit | Note     |

| Input Clock Frequency | Fclk   | Fclk (min) |      | Fclk (max) | MHz  | T=1/Fclk |

| Input Data Position0  | tRIP1  | - tRMG     | 0    | tRMG       | ns   |          |

| Input Data Position1  | tRIP0  | T/7- tRMG  | T/7  | T/7+ tRMG  | ns   |          |

| Input Data Position2  | tRIP6  | 2T/7- tRMG | 2T/7 | 2T/7+ tRMG | ns   |          |

| Input Data Position3  | tRIP5  | 3T/7- tRMG | 3T/7 | 3T/7+ tRMG | ns   |          |

| Input Data Position4  | tRIP4  | 4T/7- tRMG | 4T/7 | 4T/7+ tRMG | ns   |          |

| Input Data Position5  | tRIP3  | 5T/7- tRMG | 5T/7 | 5T/7+ tRMG | ns   |          |

| Input Data Position6  | tRIP2  | 6T/7- tRMG | 6T/7 | 6T/7+ tRMG | ns   |          |

#### 3.2 Interface Connections

#### 3.2.1 T-Con Board Pin Map

• LCD connector: JAE FI-RE51S-HF (LVDS connector)

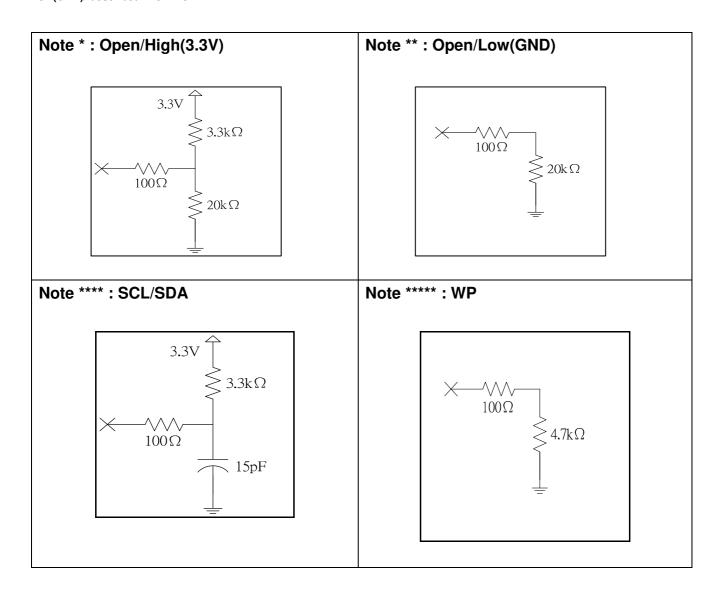

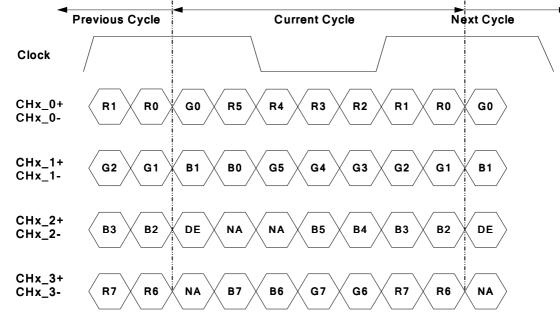

| PIN         Symbol         Description         PIN         Symbol         Description           1         N.C.         No connection (for AUO test only. Do not connect)         26         GND or N.C.         Ground or No connection (for AUO test only. Do not connect)           2         SCL         AUO Internal Use Only (SCL - EEPROM Serial Clock)         27         N.C.         No connection (for AUO test only. Do not connect)           3         WP         (EEPROM Write Protection High(3.3V) for Writable, Open/Low(GND) for Protection)         28         CH2_0+         LVDS Channel 2, Signal           4         SDA         AUO Internal Use Only (SDA - EEPROM Serial Data)         29         CH2_0+         LVDS Channel 2, Signal           5         N.C.         No connection (for AUO test only. Do not connect)         30         CH2_1+         LVDS Channel 2, Signal           6         N.C.         No connection (for AUO test only. Do not connect)         31         CH2_1+         LVDS Channel 2, Signal           7         LVDS_SEL         Open/High(3.3V) for NS, Low(GND) for 32         CH2_2+         LVDS Channel 2, Signal           8         N.C.         Oconnection (for AUO test only. Do not connect)         33         CH2_2+         LVDS Channel 2, Signal           9         N.C.         No connection (for AUO test only. Do not connect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| 1       N.C.       connect)       26       GND or N.C.       only. Do not connect)         2       SCL       AUO Internal Use Only<br>(SCL - EEPROM Serial Clock)       27       N.C.       No connection (for AUO test or<br>not connect)         3       WP       AUO Internal Use Only<br>(EEPROM Write Protection<br>High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       28       CH2_0+       LVDS Channel 2, Signal         4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1+       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not<br>connect)       35       CH2_CLK+       LVDS Channel 2, Clock         11 <t< td=""><td>UO test</td></t<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | UO test  |

| 2       SCL       (SCL - EEPROM Serial Clock)       27       N.C.       not connect)         3       WP       AUO Internal Use Only<br>(EEPROM Write Protection<br>High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       28       CH2_0-       LVDS Channel 2, Signal         4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not<br>connect)       35       CH2_CLK+       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_2-L       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |          |

| 2       SCL       (SCL - EEPROM Serial Clock)       27       N.C.       not connect)         3       WP       AUO Internal Use Only<br>(EEPROM Write Protection<br>High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       28       CH2_0-       LVDS Channel 2, Signal         4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not<br>connect)       35       CH2_CLK+       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_2-L       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | nly. Do  |

| 3       WP       (EEPROM Write Protection<br>High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       28       CH2_0-       LVDS Channel 2, Signal         4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         10       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-       37       GND       Ground         13       CH1_0+       LVDS Channel 1, Signal 0+       38       CH2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | -        |

| 3       WP       High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       28       CH2_0-       LVDS Channel 2, Signal         4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         10       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-       37       GND       Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| High(3.3V) for Writable,<br>Open/Low(GND) for Protection)       Image: Comparison of the second se                      |          |

| 4       SDA       AUO Internal Use Only<br>(SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not<br>connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not<br>connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for<br>JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not<br>connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not<br>connect)       35       CH2_CLK-       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_3-       LVDS Channel 2, Clock         12       CH1_0+       LVDS Channel 1, Signal 0-       37       GND       Ground         13       CH1_0+       LVDS Channel 1, Signal 0+       38       CH2_3+       LVDS Chann                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )-       |

| 4       SDA       (SDA - EEPROM Serial Data)       29       CH2_0+       LVDS Channel 2, Signal         5       N.C.       No connection (for AUO test only. Do not connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for JEIDA       32       CH2_2-       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not connect)       33       CH2_2+       LVDS Channel 2, Signal         10       N.C.       No connection (for AUO test only. Do not connect)       34       GND       Ground         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_3+       LVDS Channel 2, Signal         13       CH1_0-       LVDS Channel 1, Signal 0-       37       GND       Ground         13       CH1_0+       LVDS Channel 1, Signal 1-       39       CH2_3+       LVDS Channel 2, Signal         14 <td< td=""><td></td></td<>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |          |

| 1       GNA - EEPROM Serial Data)       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1       1<                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| 5       N.C.       connect)       30       CH2_1-       LVDS Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for JEIDA       32       CH2_2+       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not connect)       35       CH2_CLK-       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-       37       GND       Ground         13       CH1_0+       LVDS Channel 1, Signal 0+       38       CH2_3+       LVDS Channel 2, Signal         14       CH1_1+       LVDS Channel 1, Signal 1+       40       N.C.       No connection (for AUO test or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | )+       |

| Connection       Connection       Connection       Connection       Connection       Channel 2, Signal         6       N.C.       No connection (for AUO test only. Do not connect)       31       CH2_1+       LVDS Channel 2, Signal         7       LVDS_SEL       Open/High(3.3V) for NS, Low(GND) for JEIDA       32       CH2_2-       LVDS Channel 2, Signal         8       N.C.       No connection (for AUO test only. Do not connect)       33       CH2_2+       LVDS Channel 2, Signal         9       N.C.       No connection (for AUO test only. Do not connect)       34       GND       Ground         10       N.C.       No connection (for AUO test only. Do not connect)       35       CH2_CLK-       LVDS Channel 2, Clock         11       GND       Ground       36       CH2_CLK+       LVDS Channel 2, Clock         12       CH1_0-       LVDS Channel 1, Signal 0-       37       GND       Ground         13       CH1_0+       LVDS Channel 1, Signal 0+       38       CH2_3+       LVDS Channel 2, Signal         14       CH1_1+       LVDS Channel 1, Signal 1-       39       CH2_3+       LVDS Channel 2, Signal         15       CH1 1+       LVDS Channel 1, Signal 1+       40       N.C.       No connection (for AUO test only. <td></td>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |          |

| 6N.C.connect)31CH2_1+LVDS Channel 2, Signal7LVDS_SELOpen/High(3.3V) for NS, Low(GND) for<br>JEIDA32CH2_2-LVDS Channel 2, Signal8N.C.No connection (for AUO test only. Do not<br>connect)33CH2_2+LVDS Channel 2, Signal9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3+LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test on<br>connect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1-       |

| 7LVDS_SELOpen/High(3.3V) for NS, Low(GND) for<br>JEIDA32CH2_2-LVDS Channel 2, Signal8N.C.No connection (for AUO test only. Do not<br>connect)33CH2_2+LVDS Channel 2, Signal9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test on                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |          |

| 7LVDS_SELJEIDA32CH2_2-LVDS Channel 2, Signal8N.C.No connection (for AUO test only. Do not<br>connect)33CH2_2+LVDS Channel 2, Signal9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test on)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 1+       |

| JEIDAJEIDA8N.C.No connection (for AUO test only. Do not<br>connect)33CH2_2+LVDS Channel 2, Signal9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 2-       |

| 8N.C.connect)33CH2_2+LVDS Channel 2, Signal9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | <u> </u> |

| 9N.C.No connection (for AUO test only. Do not<br>connect)34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 2+       |

| 9N.C.34GNDGround10N.C.No connection (for AUO test only. Do not<br>connect)35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test or                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |          |

| Image: connect bit of the connect b |          |

| 10N.C.35CH2_CLK-LVDS Channel 2, Clock11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test of the second secon                                                                                                                                                                                                                                                                                                                                                                |          |

| InterfaceConnectionInterface11GNDGround36CH2_CLK+LVDS Channel 2, Clock12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test of the second seco                                                                                                                                                                                                                                                                                                                                              | -        |

| 12CH1_0-LVDS Channel 1, Signal 0-37GNDGround13CH1_0+LVDS Channel 1, Signal 0+38CH2_3-LVDS Channel 2, Signal14CH1_1-LVDS Channel 1, Signal 1-39CH2_3+LVDS Channel 2, Signal15CH1 1+LVDS Channel 1, Signal 1+40N.C.No connection (for AUO test of the second secon                                                                                                                                                                                                                                           |          |

| 13       CH1_0+       LVDS Channel 1, Signal 0+       38       CH2_3-       LVDS Channel 2, Signal         14       CH1_1-       LVDS Channel 1, Signal 1-       39       CH2_3+       LVDS Channel 2, Signal         15       CH1_1+       LVDS Channel 1, Signal 1+       40       N.C.       No connection (for AUO test of AUO test                                                                                                                                                                                                            | +        |

| 14       CH1_1-       LVDS Channel 1, Signal 1-       39       CH2_3+       LVDS Channel 2, Signal         15       CH1 1+       LVDS Channel 1, Signal 1+       40       N.C.       No connection (for AUO test of the second sec                                                                                                                                    |          |

| 15 CH1 1+ LVDS Channel 1, Signal 1+ 40 N.C. No connection (for AUO test c                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 15 CH1 1+ LVDS Channel 1, Signal 1+ 40 N.C.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 3+       |

| not connect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | nly. Do  |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |          |

| 16     CH1_2-     LVDS Channel 1, Signal 2-     41     N.C.     No connection (for AUO test of the second se                                               | nly. Do  |

| not connect)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |          |

| 17     CH1_2+     LVDS Channel 1, Signal 2+     42     GND     Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 18GNDGround43GNDGround                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |          |

| 19     CH1_CLK-     LVDS Channel 1, Clock -     44     GND     Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |          |

| 20         CH1_CLK+         LVDS Channel 1, Clock +         45         GND         Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |          |

| 21         GND         Ground         46         GND         Ground                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |          |

© Copyright AU Optronics Corp. 2013 All Rights Reserved.

| 22 | CH1_3- | LVDS Channel 1, Signal 3-                | 47                 | N.C.            | No connection (for AUO test only. Do |

|----|--------|------------------------------------------|--------------------|-----------------|--------------------------------------|

| 22 | 001_0- | LVDS Charmer 1, Signal 3-                | 47                 | N.C.            | not connect)                         |