# Crystal Clear Technology

## **Product Specification**

T3224C11VR01 (without Touch Panel)

16Jalan TP5—Taman Perindustrian Sime UEP 47600 Subang Jaya—Selangor DE Malaysia. T: +603 80247099 F: +603 80247098

Spec. No: T3224C10VX0X Preliminary

#### 1.0 Record of revision

| Rev | Date     | Item | Page | Comment     | Originator | Checked By |

|-----|----------|------|------|-------------|------------|------------|

|     | 15/03/10 |      |      | Preliminary | CF Liew    | Azhar      |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

|     |          |      |      |             |            |            |

### **CONTENTS**

|     |                                             | Page No |

|-----|---------------------------------------------|---------|

| 1.  | GENERAL DESCRIPTION                         | 4       |

| 2.  | MECHANICAL SPECIFICATIONS                   | 4       |

| 3.  | INTERFACE SIGNALS                           | 7       |

| 4.  | ABSOLUTE MAXIMUM RATINGS                    | 8       |

| 4.1 | ELECTRICAL MAXIMUM RATINGS - FOR IC ONLY    | 8       |

| 4.2 | ENVIRONMENTAL CONDITION                     | 8       |

| 5.  | ELECTRICAL SPECIFICATIONS                   | 9       |

| 5.1 | TYPICAL ELECTRICAL CHARACTERISTICS          | 9       |

| 5.2 | TIMING CHARACTERISTICS                      | 10      |

| 5.3 | REFERENTIAL INSTRUCTION SETUP FLOW          | 13      |

| 6.  | OPTICAL CHARACTERISTICS(FOR TFT PANEL ONLY) | 17      |

| 7.  | TFT PANEL INSPECTION SPECIFICATIONS         | 20      |

| 8.  | USING LCD MODULE                            | 22      |

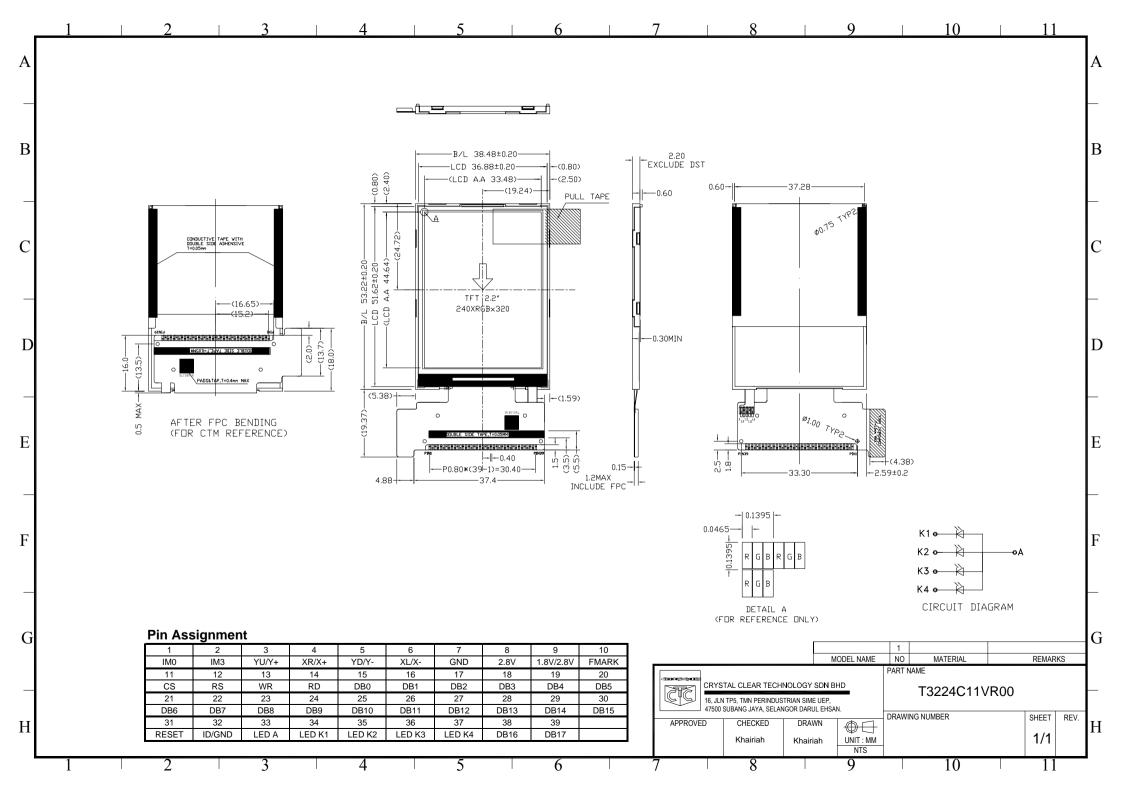

#### 3.0 General specification

| Display format     | : 240 (W) x RGB x 320 (H) dots            |

|--------------------|-------------------------------------------|

| Screen size        | : 2.2 inch                                |

| Surface treatment  | : Glare                                   |

| Active area        | : 33.48mm x 44.64mm                       |

| General dimensions | s : 39.84mm x 56.90mm x 3.00mm            |

| Pixel pitch        | : 0.1395mm x 0.1395mm                     |

| Controller         | : HIMAX, HX8347D                          |

| LCD type           | : CSTN TFT OLED                           |

| Polarizer mode     | : Reflective Transflective                |

|                    | Transmissive                              |

| View angle         | : 6 O' clock 20 12 O'clock                |

|                    | 9 O'clock 3 O'clock                       |

| Backlight          | : NONE LED CCFL                           |

| Backlight color    | : Yellow Green Amber White                |

|                    | Blue Green Others                         |

| Temperature range  | <u> </u>                                  |

|                    | Operating 0 to 50 C Operating –20 to 70 C |

|                    | Storage -20 to 70 C Storage -30 to 80 C   |

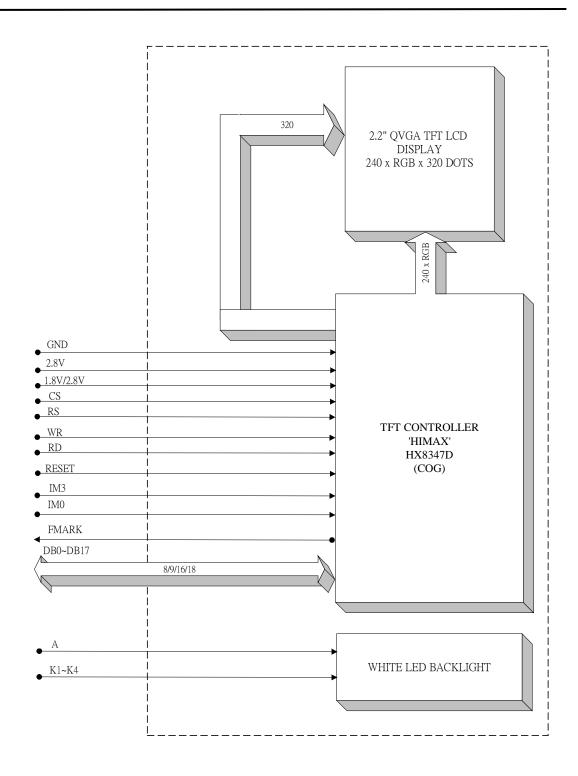

Figure 2: Block Diagram

#### 3. Interface signals

Table 2: Pin assignment

| Pin No. | Symbol    | Description                                                                                                |  |  |  |  |  |

|---------|-----------|------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|         |           | System interface select.                                                                                   |  |  |  |  |  |

| 1       | IM0       | IM3 IM0 Interface                                                                                          |  |  |  |  |  |

|         |           | 0 0 8080 MCU 16-bits Parallel                                                                              |  |  |  |  |  |

|         |           | 0 1 8080 MCU 8-bits Parallel                                                                               |  |  |  |  |  |

| 2       | IM3       | 1 0 8080 MCU 18-bits Parallel                                                                              |  |  |  |  |  |

|         |           | 1 1 8080 MCU 9-bits Parallel                                                                               |  |  |  |  |  |

| 3       | YU/Y+     | No connection.                                                                                             |  |  |  |  |  |

| 4       | XR/X+     | No connection.                                                                                             |  |  |  |  |  |

| 5       | YD/Y-     | No connection.                                                                                             |  |  |  |  |  |

| 6       | XL/X-     | No connection.                                                                                             |  |  |  |  |  |

| 7       | GND       | Ground.                                                                                                    |  |  |  |  |  |

| 8       | 2.8V      | Power supply.                                                                                              |  |  |  |  |  |

| 9       | 1.8V/2.8V | Power supply.                                                                                              |  |  |  |  |  |

| 10      | FMARK     | Output a frame head pulse signal is used as synchronies MCU to frame rate.                                 |  |  |  |  |  |

| 11      | CS        | Chip select signal.                                                                                        |  |  |  |  |  |

| 11      | CB        | Low: chip can be accessed; High: chip cannot be accessed.                                                  |  |  |  |  |  |

| 12      | RS        | The signal for command or parameter select under parallel mode:                                            |  |  |  |  |  |

|         | 110       | Low: command. High: parameter.                                                                             |  |  |  |  |  |

| 13      | WR        | I80 system:                                                                                                |  |  |  |  |  |

|         |           | Serves as a write signal and writes data at the rising edge.                                               |  |  |  |  |  |

| 14      | RD        | I80 system:                                                                                                |  |  |  |  |  |

|         |           | Serves as a read signal and read data at the low level.  8/9/16/18-bit bi-directional data bus.            |  |  |  |  |  |

| 15~30   | DB0~DB15  |                                                                                                            |  |  |  |  |  |

|         |           | The unused pins let to open.                                                                               |  |  |  |  |  |

| 31      | RESET     | Reset pin. Setting either pin low initializes the LSI.  Must be reset the chip after power being supplied. |  |  |  |  |  |

| 32      | ID/GND    | Ground.                                                                                                    |  |  |  |  |  |

| 33      | A         | Anode of LED backlight.                                                                                    |  |  |  |  |  |

| 34      | K1        | Cathode of LED backlight.                                                                                  |  |  |  |  |  |

| 35      | K2        | Cathode of LED backlight.                                                                                  |  |  |  |  |  |

| 36      | K3        | Cathode of LED backlight.                                                                                  |  |  |  |  |  |

| 37      | K4        | Cathode of LED backlight.                                                                                  |  |  |  |  |  |

|         |           | 8/9/16/18-bit bi-directional data bus.                                                                     |  |  |  |  |  |

| 38~39   | DB16~DB17 | The unused pins let to open.                                                                               |  |  |  |  |  |

| L       | 1         | r · · · · · · · · · · · · · · ·                                                                            |  |  |  |  |  |

#### 4. Absolute Maximum Ratings

#### 4.1 Electrical Maximum Ratings – for IC Only

Table 3

| Parameter                  | Symbol | Min. | Max. | Unit |

|----------------------------|--------|------|------|------|

| Power supply voltage (VCC) | IOVCC  | -0.3 | +4.6 | V    |

| Power supply voltage (VCI) | VCI    | -0.3 | +4.6 | V    |

Note: The modules may be destroyed if they are used beyond the absolute maximum ratings. GND=0V.

#### 4.2 Environmental Condition

Table 4

| Table 4                                                              |              |                                                                                 |                                            |                                  |                 |  |  |

|----------------------------------------------------------------------|--------------|---------------------------------------------------------------------------------|--------------------------------------------|----------------------------------|-----------------|--|--|

| Item                                                                 | tempe        | rating<br>rature<br>opr)                                                        | tempe<br>(Ts                               | rage<br>erature<br>etg)<br>te 1) | Remark          |  |  |

|                                                                      | Min.         | Max.                                                                            | Min.                                       | Max.                             |                 |  |  |

| Ambient temperature(Ta)                                              | -20°C        | +70°C                                                                           | -30°C                                      | +80°C                            | Dry             |  |  |

| Humidity (note 1)                                                    |              | for 40°C < Ta                                                                   | for Ta $\leq 40^{\circ}$ 0 Maximum rature. |                                  | No condensation |  |  |

| Vibration (IEC 68-2-6) cells must be mounted on a suitable connector | Dura         | Frequency: 10 ~ 55 Hz Amplitude: 0.75 mm Duration: 20 cycles in each direction. |                                            |                                  |                 |  |  |

| Shock (IEC 68-2-27)<br>Half-sine pulse shape                         | Pea<br>Numbe | 3 directions                                                                    |                                            |                                  |                 |  |  |

Note 1: Product cannot sustain at extreme storage conditions for long time.

#### 5. Electrical Specifications

#### **5.1** Typical Electrical Characteristics

At Ta = 25 °C, VDD=  $2.8V \pm 0.1V$ , GND=0V.

Table 5

| Parameter                             | Symbol   | Conditions             | Min.   | Тур. | Max.   | Unit              |

|---------------------------------------|----------|------------------------|--------|------|--------|-------------------|

| Power supply voltage                  | VDD      |                        | 2.7    | 2.8  | 2.9    | V                 |

| TFT gate ON voltage                   | VGH      | Note 1                 | 12     | -    | 18     | V                 |

| TFT gate OFF voltage                  | VGL      | Note 2                 | -12    | -    | -7     | V                 |

| TFT common electrode voltage          | Vcom     | Note 3                 | -2     | -    | 5      | V                 |

| Input signal voltage                  | $V_{IH}$ | "H" level              | 0.8VDD | -    | VDD    | V                 |

| input signar voltage                  | $V_{IL}$ | "L" level              | -0.3   | 1    | 0.2VDD | V                 |

| Supply current (Logic)                | IDD      | VDD=2.8V               | -      | TBD  | -      | mA                |

| Supply voltage of white LED backlight | VLED     | Forward current =60mA  | -      | 3.0  | -      | V                 |

| Luminance (on the backlight surface)  |          | Number of LED dies = 3 | -      | 3500 | -      | cd/m <sup>2</sup> |

Note 1: VGH is TFT Gate operating voltage.

Note 2: VGL is TFT Gate operating voltage.

Note 3: Vcom must be adjusted to optimize display quality.

#### 5.2 **Timing Characteristics**

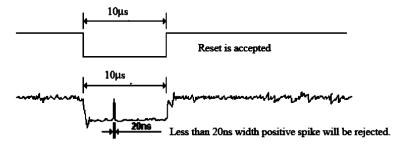

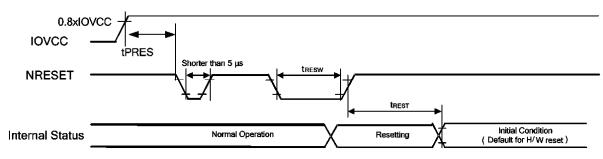

#### **5.2.1** Reset Input Timing

At  $Ta = 25^{\circ}C$ , GND=0V,  $VDD=2.8V\pm0.1V$ .

Table 6

| Symbol | Parameter                                 | Related           | Spec. |      |      | Note                                    | Unit  |

|--------|-------------------------------------------|-------------------|-------|------|------|-----------------------------------------|-------|

| Symbol | raiainetei                                | Pins              | Min.  | Тур. | Max. | Note                                    | Oille |

| tRESW  | Reset low pulse width <sup>(1)</sup>      | NRESET            | 10    | -    | -    | -                                       | μs    |

| tREST  | Boost complete time <sup>(2)</sup>        | -                 | -     | -    | 5    | When reset applied during STB mode      | ms    |

|        | Reset complete time <sup>(2)</sup>        | -                 |       | -    | 120  | When reset applied during STB mode      | ms    |

| tPRES  | Reset goes high level after Power on time | NRESET &<br>IOVCC | 1     | -    | -    | Reset goes high level after<br>Power on | ms    |

Note: (1) Spike due to an electrostatic discharge on NRESET line does not cause irregular system reset according to the table below.

| NRESET Pulse           | Action         |

|------------------------|----------------|

| Shorter than 5 µ       | Reset Rejected |

| Longer than 10 µs      | Reset          |

| Between 5 µs and 10 µs | Reset Start    |

- (2) During the resetting period, the display will be blanked (The display is entering blanking sequence, which maximum time is 120 ms, when Reset Starts in STB Out -mode. The display remains the blank state in STB -mode) and then return to Default condition for H/W reset.

- (3) During Reset Complete Time, VMF value in OTP will be latched to internal register during this period. This loading is done every time when there is H/W reset complete time (tREST) within 5ms after a rising edge of NRESET.

- (4) Spike Rejection also applies during a valid reset pulse as shown below:

(5) It is necessary to wait 5msec after releasing IRES before sending commands. Also STB Out

Figure 4: Reset Input Timing

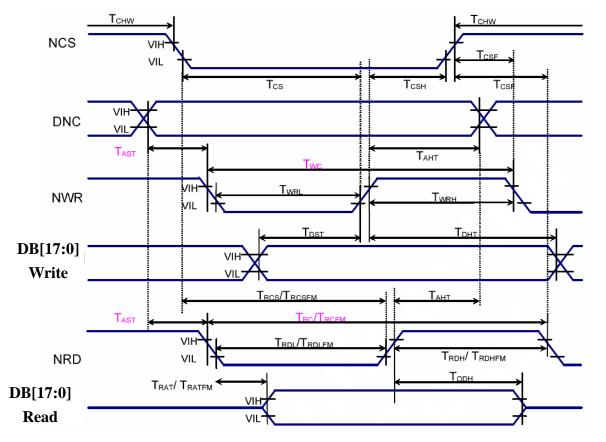

#### **5.2.2** Parallel Interface Characteristics (I80-system interface)

At  $Ta = 25^{\circ}C$ , GND=0V,  $VDD=2.8V \pm 0.1V$ .

Table 7

| Signal   | Symbol       | Parameter                          | Min. | Max. | Unit | Description          |  |

|----------|--------------|------------------------------------|------|------|------|----------------------|--|

| DNC SCI  | tast         | Address setup time                 | 0    | -    | no   |                      |  |

| DNC_SCL  | taht         | Address hold time (Write/Read)     | 10   | -    | ns   | -                    |  |

|          | tchw         | Chip select "H" pulse width        | 0    | -    |      |                      |  |

|          | tcs          | Chip select setup time (Write)     | 15   | -    |      |                      |  |

| NCS      | trcs         | Chip select setup time (Read ID)   | 45   | -    | ns   |                      |  |

| NCS      | trcsfm       | Chip select setup time (Read FM)   | 355  | -    | 115  | -                    |  |

|          | tcsF         | Chip select wait time (Write/Read) | 10   | -    |      |                      |  |

|          | tсsн         | Chip select hold time              | 10   | -    |      |                      |  |

|          | twc          | Write cycle                        | 66   | -    |      |                      |  |

| NWR_SCL  | twrn         | Control pulse "H" duration         | 15   | -    | ns   | -                    |  |

|          | twrl         | Control pulse "L" duration         | 15   | -    |      |                      |  |

|          | trc          | Read cycle (ID)                    | 160  | -    |      |                      |  |

| NRD(ID)  | trdh         | Control pulse "H" duration (ID)    | 90   | -    | ns   | When read ID data    |  |

|          | trdl         | Control pulse "L" duration (ID)    | 45   | -    |      |                      |  |

|          | trсғм        | Read cycle (FM)                    | 450  | -    |      | When read from frame |  |

| DB17~DB0 | trdhfm       | Control pulse "H" duration (FM)    | 90   | -    | ns   |                      |  |

|          | trdlfm       | Control pulse "L" duration (FM)    | 355  | -    |      | memory               |  |

|          | tost         | Data setup time                    | 10   | -    |      |                      |  |

| DB17~DB0 | <b>t</b> DHT | Data hold time                     |      | -    |      | For maximum C = 20nF |  |

|          | trat         |                                    |      | 40   | ns   | For maximum CL=30pF  |  |

|          | tratem       | Read access time (FM)              | -    | 340  |      | For minimum C∟=8pF   |  |

|          | todн         | Output disable time                | 20   | 80   |      |                      |  |

Note: The input signal rise time and fall time (tr, tf) is specified at 15 ns or less.

Logic high and low levels are specified as 30% and 70% of IOVCC for Input signals.

# Input Signal Slope Output Signal Slope V<sub>IH</sub>=0.7\*IOVCC V<sub>IH</sub>=0.3\*IOVCC V<sub>OH</sub>=0.8\*IOVCC

Figure 5

Note: Logic high and low levels are specified as 30% and 70% of IOVCC

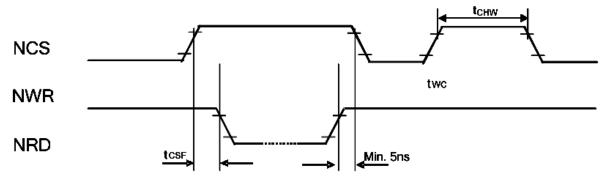

Figure 6: Chip Select Timing

Note: Logic high and low levels are specified as 30% and 70% of IOVCC

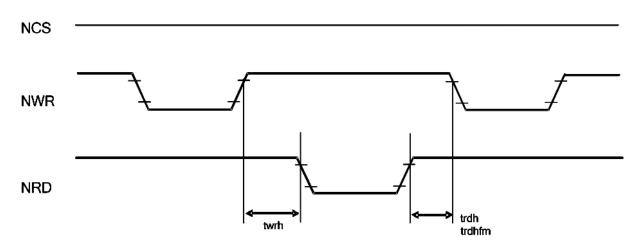

Figure 7: Write to Read and Read to Write Timing

Figure 8: Parallel Interface Characteristics (I80-system interface)

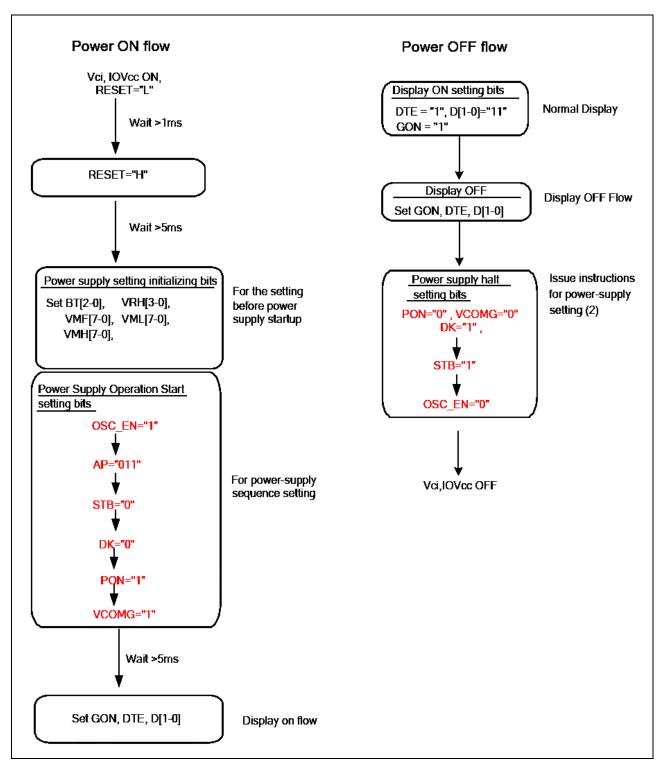

#### **5.3** Referential Instruction Setup Flow

#### **5.3.1 Power Supply Setting Flow**

Figure 9: Power Supply Setting Flow

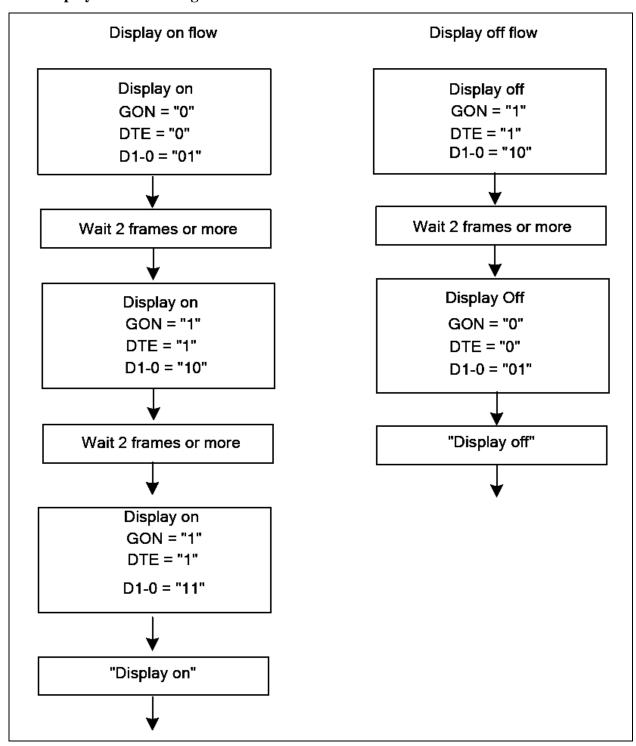

#### 5.3.2 Display On/Off Setting Flow

Figure 10: Display On/Off Setting Flow

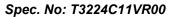

#### 5.3.3 Standby Mode Setting Flow

Figure 11: Standby Mode Setting Flow

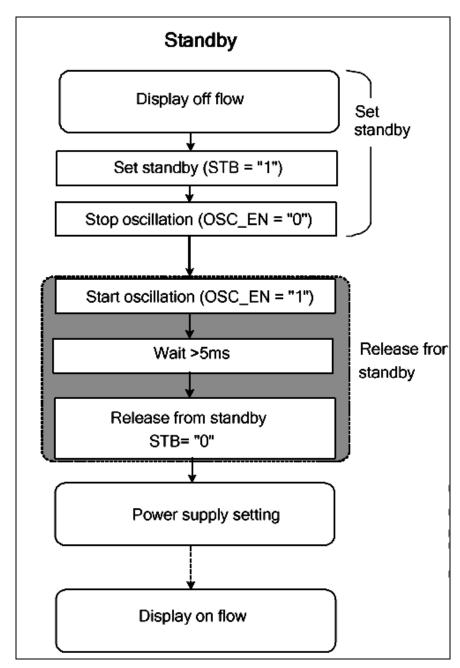

#### 5.3.4 Deep Standby Mode Set up Flow

Figure 12: Deep Standby Mode Setting flow

#### 6. Optical Characteristics

Table 8

| Items              |                |                 | Symbol           | Condition            | specifications |       |       | Unit   | Remark  |  |

|--------------------|----------------|-----------------|------------------|----------------------|----------------|-------|-------|--------|---------|--|

| Items              |                | Symbol Conditio |                  | Min.                 | Typ.           | Max.  | Oiiit | Kemark |         |  |

| Throshold          | voltar         | 70              | Vsat             |                      | 2.9            | 3.2   | 3.5   | V      | Eig 12  |  |

| Threshold v        | vonaş          | ge              | Vth              |                      | 1.2            | 1.5   | 1.8   | V      | Fig. 13 |  |

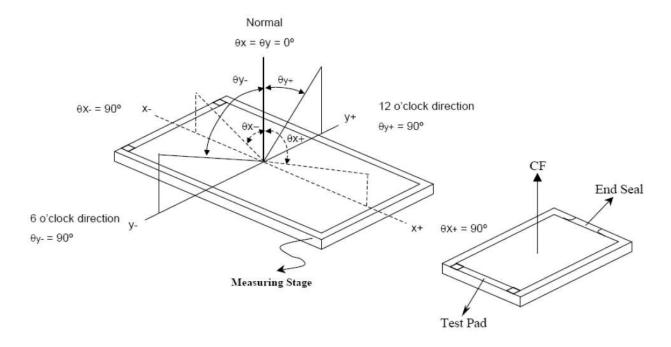

|                    | Ho             | rizontal        | \$1 (3 o'clock)  |                      | ı              | 45    | -     | Deg.   |         |  |

| Viewing angle      |                |                 | φ2 (9 o'clock)   | CR>10                | -              | 45    | -     | Deg.   | Note 1  |  |

| range              | V              | ertical         | θ2 (12 o'clock)  | CK > 10              | -              | 35    | -     | Deg.   | Note 1  |  |

|                    |                |                 | θ1 (6 o'clock)   |                      | -              | 15    | -     | Det.   |         |  |

| Contrast           | Contrast ratio |                 | CR               | $\theta = 0^{\circ}$ | -              | 300   | -     | -      | Note 2  |  |

| Transmitt          | tance          |                 | T (%)            | $\theta = 0^{\circ}$ | 1              | 5.6   | -     | -      | Note 3  |  |

| White chron        | natic          | its             | Xw               | $\theta = 0^{\circ}$ | 0.270          | 0.300 | 0.330 | -      |         |  |

| winte chion        | matic          | ity             | Yw               | 0 = 0                | 0.304          | 0.334 | 0.364 | -      |         |  |

|                    |                | Red             | $X_R$            |                      | 0.616          | 0.646 | 0.676 | -      | Note 4  |  |

|                    |                | Reu             | $Y_R$            |                      | 0.291          | 0.321 | 0.351 | -      | Color   |  |

| Reproduction of co | olor           | Green           | $X_{G}$          | $\theta = 0^{\circ}$ | 0.268          | 0.298 | 0.328 | -      | filter  |  |

| Reproduction of Co | Oloi           | Often           | $Y_{G}$          | 0 - 0                | 0.543          | 0.573 | 0.603 | -      | glass   |  |

|                    |                | Blue            | $X_{\mathrm{B}}$ |                      | 0.104          | 0.134 | 0.164 | -      |         |  |

|                    | Blue           |                 | $Y_{B}$          |                      | 0.103          | 0.133 | 0.163 | -      |         |  |

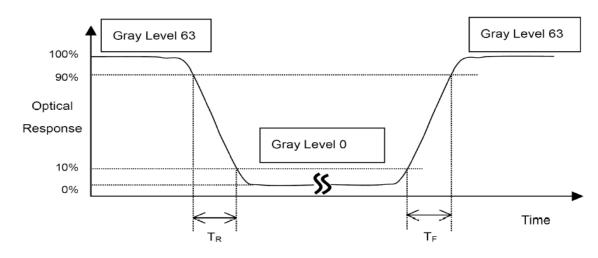

| Response           | time           |                 | Tr + Tf          | $\theta = 0^{\circ}$ | -              | 40    | -     | msec   | Note 5  |  |

Note (1) Definition of Contrast Ratio (CR):

The contrast ratio can be calculated by the following expression.

Contrast Ratio (CR) = L63 / L0

L63: Luminance of gray level 63

L0: Luminance of gray level 0

CR = CR(5)

CR (X) is corresponding to the Contrast Ratio of the point X at Figure in Note (5).

Note (2) Definition of Response Time (TR, TF):

#### \*Note(3) Definition of Viewing Angle

\*\*\* The above "Viewing Angle" is the measuring position with Largest Contrast Ratio; not for good image quality. View Direction for good image quality is 6 O'clock. Module maker can increase the "Viewing Angle" by applying Wide View Film.

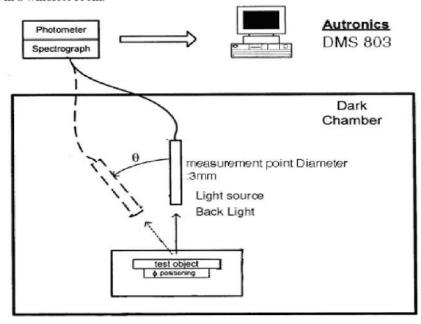

#### \*Note (4) Measurement Set-Up:

The LCD module should be stabilized at a given temperature for 20 minutes to avoid abrupt temperature change during measuring. In order to stabilize the luminance, the measurement should be executed after lighting Backlight for 20 minutes in a windless room.

\*Note (5)

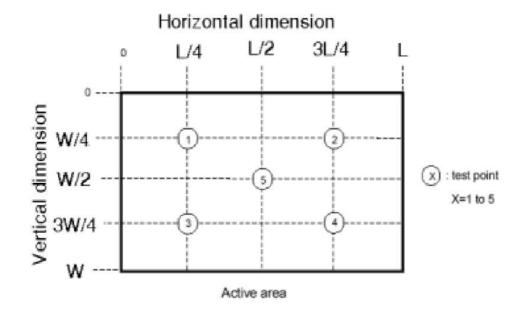

#### 7. TFT Panel Inspection Specifications

| Failure                                                                                                | The continue                            | Catagory | (Unit: mm)                                                | Acceptable count                                        |                  |  |  |  |  |

|--------------------------------------------------------------------------------------------------------|-----------------------------------------|----------|-----------------------------------------------------------|---------------------------------------------------------|------------------|--|--|--|--|

| mode                                                                                                   | Illustration                            | Category | (Unit: mm)                                                | Viewing area                                            | non-Viewing area |  |  |  |  |

|                                                                                                        | Width                                   | A        | Φ≤0. 10                                                   | Not count                                               |                  |  |  |  |  |

| Black spot White spot                                                                                  | Length $\Phi = (\text{Length+width})/2$ | В        | 0. 10<Φ≤0. 15                                             | The gap between the two spots should be 5 mm and above. | Not count        |  |  |  |  |

|                                                                                                        |                                         | С        | $0.15 < \Phi \le 0.20$                                    | 1                                                       | -                |  |  |  |  |

|                                                                                                        |                                         | D        | 0. 20< Φ                                                  | 0                                                       |                  |  |  |  |  |

| Bright<br>spot(Red<br>spot,green<br>spot and<br>blue spot<br>caused by<br>damaged<br>colour<br>filter) |                                         | A        | Area≦1<br>sub-pixel                                       | 0                                                       | N/A              |  |  |  |  |

| ,                                                                                                      |                                         | A        | W ≤ 0.03                                                  | Not count                                               | Not count        |  |  |  |  |

| Black line                                                                                             | W                                       | В        | 0. 03<₩≤0.05,<br>L≤3.0                                    | 2                                                       |                  |  |  |  |  |

| White line                                                                                             | T L                                     | С        | 0.05 <w< td=""><td>Judged by spot spec</td><td></td></w<> | Judged by spot spec                                     |                  |  |  |  |  |

| (Below are cosmetic inspection specifications)                                                         |                                         |          |                                                           |                                                         |                  |  |  |  |  |

| Excess glass                                                                                           | \\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\\  |          |                                                           |                                                         |                  |  |  |  |  |

|                                                                                                           |                                                                          | This defect shall not affect the outline dimension or assembly process. |                                                                                        |

|-----------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------|-------------------------------------------------------------------------|----------------------------------------------------------------------------------------|

|                                                                                                           | LCD ledge damage                                                         | Category                                                                |                                                                                        |

| Glass<br>defect<br>(scratch,<br>damage)                                                                   | b b c                                                                    | A                                                                       | The defect shall not affect the outline dimension or assembly process at non ITO zone. |

|                                                                                                           |                                                                          | В                                                                       | $b \le 1/4w$ , a & c not count (at ITO zone)                                           |

|                                                                                                           |                                                                          | С                                                                       | Alignment mark on LCD ledge shall not be damaged.                                      |

|                                                                                                           | Outside of perimeter damage                                              |                                                                         |                                                                                        |

|                                                                                                           | 边框内沿(Inside of perimeter)<br>边框外沿(outside of perimeter)                  |                                                                         |                                                                                        |

|                                                                                                           | Joint glass damage                                                       |                                                                         |                                                                                        |

|                                                                                                           | 边框架(Perimeter).  边框内沿(Inside of perimeter).  边框外沿(Outside of perimeter). | b can't reach outside of perimeter or ITO layout.                       |                                                                                        |

|                                                                                                           | (Corner damage)                                                          | A                                                                       | $a \le t, b \le 3.0, c \le 3.0$                                                        |

|                                                                                                           | w b a t                                                                  | B. Alignment mark on LCD ledge shall not be damaged.                    |                                                                                        |

| Remark: a stands for thickness of damage, b for width, c for length and t for glass thickness. (Unit: mm) |                                                                          |                                                                         |                                                                                        |

#### 8.0 USING LCD MODULES

#### 8-1. Liquid Crystal Display Modules

LCD is composed of glass and polarizer. Pay attention to the following items when handling.

- 1. Please keep the temperature within specified range for use and storage. Polarization degradation, bubble generation or polarizer peel-off may occur with high temperature and high humidity.

- 2. Do not touch, push or rub the exposed polarizers with anything harder than an HB pencil lead (glass, tweezers, etc).

- 3. N-hexane is recommended for cleaning the adhesive used to attach front/rear polarizers and reflectors made of organic substances which will be damaged by chemicals such as acetone, toluene, ethanol and isopropylalcohol.

- 4. When the display surface becomes dusty, wipe gently with absorbent cotton or other soft material like chamois soaked in petroleum benzin. Do not scrub hard to avoid damaging the display surface.

- 5. Wipe off saliva or water drops immediately, contact with water over a long period of time may cause deformation or color fading.

- 6. Avoid contacting oil and fats.

- 7. Condensation on the surface and contact with terminals due to cold will damage, stain or dirty the polarizers. After products are tested at low temperature they must be warmed up in a container before coming is contacting with room temperature air.

- 8. Do not put or attach anything on the display area to avoid leaving marks on.

- 9. Do not touch the display with bare hands .This will stain the display area and degradate insulation between terminals (some cosmetics are determinated to the polarizers).

- 10. As glass is fragile. It tends to become or chipped during handling especially on the edges. Please avoid dropping or jarring.

#### 8-2. Precaution for Handling LCD Modules

Since LCM has been assembled and adjusted with a high degree of precision, avoid applying excessive shocks to the module or making any alterations or modifications to it.

- 1. Do not alter, modify or change the shape of the tab on the metal frame.

- 2. Do not make extra holes on the printed circuit board, modify its shape or change the positions of components to be attached.

- 3. Do not damage or modify the pattern writing on the printed circuit board.

- 4. Absolutely do no modify the zebra rubber strip (conductive rubber) or heat seal connector.

- 5. Except for soldering the interface, do not make any alterations or modifications with a soldering iron.

- 6. Do not drop, bend or twist LCM.

#### 8-3. Electro-Static Discharge Control

Since this module uses a CMOS LSI, the same careful attention should be paid to electrostatic discharge as for an ordinary CMOS IC.

- 1. Make certain that you are grounded when handing LCM.

- 2. Before remove LCM from its packing case or incorporating it into a set, be sure the module and your body have the same electric potential.

- 3. When soldering the terminal of LCM, make certain the AC power source for the soldering iron does not leak.

- 4. When using an electric screwdriver to attach LCM, the screwdriver should be of ground potentiality to minimize as much as possible any transmission of electromagnetic waves produced sparks coming from the commutator of the motor.

- 5. As far as possible make the electric potential of your work clothes and that of the work bench the ground potential.

- 6. To reduce the generation of static electricity be careful that the air in the work is not too dried. A relative humidity of 50%~60% is recommended.

#### 8-4. Precaution for soldering to the LCM

- 1. Observe the following when soldering lead wire, connector cable and etc. to the LCM.

- Soldering iron temperature: 280°C±10°C

- Soldering time: 3-4 sec.

- Solder: eutectic solder.

If soldering flux is used, be sure to remove any remaining flux after finishing to soldering operation. (This does not apply in the case of a non-halogen type of flux.) It is recommended that you protect the LCD surface with a cover during soldering to prevent any damage dug to flux spatters.

- When soldering the electroluminescent panel and PC board, the panel and board should not be detached more than three times. This maximum number is determined by the temperature of the soldering iron.

- 3. When remove the electroluminescent panel form the PC board, be sure the solder has completely melted, the soldered pad on the PC board could be damaged

#### 8-5. Precaution for Operation

- 1. Viewing angle varies with the change of liquid crystal driving voltage (Vo). Adjust Vo to show the best contrast.

- 2. Driving the LCD in the voltage above the limit shortens its life.

- 3. Response time is greatly at temperature below the operating temperature range. However, this does not mean the LCM will be out of the order. It will recover when it returns to the specified temperature range.

- 4. If the display area is pushed hard during operation, the display will become abnormal. However, it will return to normal if it is turned off and then back on.

- 5. Condensation of terminals can cause an electrochemical reaction disrupting the terminal circuit. Therefore, it must be used under the relative condition of 40°C, 50%RH.

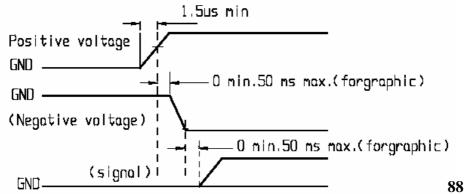

- 6. When turning the power on, input each signal after the positive/negative voltage becomes stable.

#### 8-6. Storage

When storing LCD as spares for some years, the following precaution are necessary.

- 1. Store them in a sealed polyethylene bag. If properly sealed, there is no need for desiccant.

- 2. Store them in a dark place. Do not expose to sunlight or fluorescent light, keep the temperature between  $0^{\circ}$ C and  $35^{\circ}$ C.

- 3. The polarizer surface should not come in contact with any other objects. (We advise you to store them in the container in which they were shipped.)

- 4. Environmental conditions:

- Do not leave them for more than 168hrs. at 60°C.

- Should not be left for more than 48hrs. at  $-20^{\circ}$ C.

#### **8-7. Safety**

- 1. It is recommended to crush damaged or unnecessary LCD into pieces and wash off with solvents such as acetone and ethanol, which should later be burned.

- 2. If any liquid leak out of a damaged glass cell and comes in contact with the hands, wash off thoroughly with soap and water.

#### 8-8. Limited Warranty

Unless agreed between CCT and customer, CCT will replace or repair any of its LCD modules which are found to be functionally defective when inspected in accordance with CCT LCD acceptance standards (copies available upon request) for a period of one year from date of shipments. Cosmetic/ visual defects must be returned to CCT within 90 days of shipment. Confirmation of such date shall be based on freight documents. The warranty liability of CCT limited to repair and/or replacement on the terms set forth above. CCT will not be responsible for any subsequent or consequential events.

#### 8-9. Return LCM under warranty

No warranty can be granted if the precautions stated above have been disregarded. The typical examples of violations are:

- Broken LCD glass.

- PCB eyelet's damaged.

- PCB conductors damaged.

- -Circuit modified in any way, including addition of components.

- PCB tampered with by grinding, engraving or painting varnish.

- -Soldering to or modifying the bezel in any manner.

Module repairs will be invoiced to the customer upon mutual agreement. Modules must be returned with sufficient description of the failures or defects. Any connectors or cable installed by the customer must be removed completely without damaging the PCB eyelet's conductors and terminals.

**Crystal Clear Technology** 16 Jalan TP5—Taman Perindustrian Sime UEP 47600 Subang Jaya—Selangor DE Malaysia