Advance Data

# Clock Generator Controller for Z80 CPU CMOS

- SGS CMOS Z80 Compatible

- 5 Volt Single Power Supply 5V ± 10%

- Selectable Three Modes RUN MODE IDLE MODE STOP MODE

- Low Power Consumption

2 mA Typ. @5V @4 MHz (Run Mode)

500 μA Typ. @5V @4 MHz (Idle Mode)

10 μA Max. @5V (Stop Mode)

- Extended Operating Temperature Range -40°C to 85°C

#### General Description

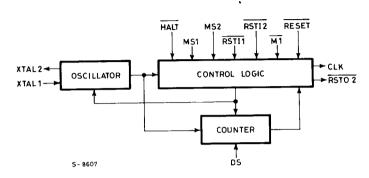

The T6497 is a clock generator/controller for SGS CMOS Z80 microprocessor (Z84C00) and peripheral devices. The T6497 has two inputs for choosing one of three modes. When CPU executes HALT instruction, T6497 enters to one of three states described below.

Run Mode. The T6497 is always providing the clock (CLK) to Z80 CPU and peripheral devices. (CPU is actually in HALT state and execute NOP instruction until and interrupt signal or a reset signal is recognized).

**Idle Mode.** The T6497 stops providing the

clock. However only the internal oscillator continues its operation.

Stop Mode. The T6497 stops its operation.

In the STOP MODE, CMOS Z80 microcomputer system may stop its operation, so that power consumption to maintain microcomputer system will be extremely reduced.

An interrupt signal  $(\overline{NMI} \text{ or } \overline{INT})$  or a reset signal  $(\overline{RESET})$  makes CPU terminate HALT states. The T6497 is molded in 16-pin standard dual-in-line plastic package.

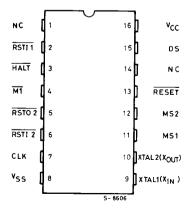

Figure 1. Pin Configuration

## General Description (Continued)

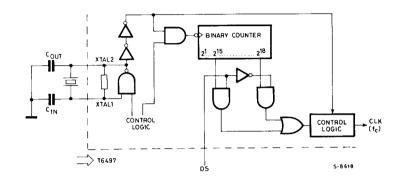

Figure 2. Block Diagram

Pin Names and Pin Description

| Pin Name        | No. of Pins | I/O, 3-State |                                                                                                                              |  |  |  |

|-----------------|-------------|--------------|------------------------------------------------------------------------------------------------------------------------------|--|--|--|

| MS1, MS2        | 2           | Input        | Input for Mode select.                                                                                                       |  |  |  |

| XTAL1, XTAL2    | 2           | Input        | Terminals for a crystal.                                                                                                     |  |  |  |

| RSTII           | 1           | Input        | Input to resume the CLK. (Level trigger) Usually input for INT request.                                                      |  |  |  |

| RSTI2           | 1           | Input        | Input with a latch to resume the CLK. (Edge trigger) Usually input for NMI request.                                          |  |  |  |

| RSTO2           | 1           | Output       | Output corresponding to RSTI2. Usually output for NMI terminal of CPU.                                                       |  |  |  |

| Ml              | 1           | Input        | Input for $\overline{\text{M1}}$ signal from CPU.                                                                            |  |  |  |

| HALT            | 1           | Input        | Input for HALT signal from CPU.                                                                                              |  |  |  |

| RESET           | 1           | Input        | Input signal to resume the CLK. Usually input for RESET signal.                                                              |  |  |  |

| CLK             | 1           | Output       | Clock output. When HALT instruction is executed by Z80 CPU in either IDLE MODE or STOP MODE, CLK is kept a low level.        |  |  |  |

| DS              | 1           | Input        | Input for selecting the number of counter stage. It is used to determine warming-up time when T6497 restarts from STOP MODE. |  |  |  |

| NC              | 2           | _            | No connection.                                                                                                               |  |  |  |

| V <sub>CC</sub> | 1           | Power        | Single 5V power supply.                                                                                                      |  |  |  |

| $v_{ss}$        | ı           | Power        | Ground reference.                                                                                                            |  |  |  |

#### Functional Description

Table 1 illustrates mode select and those functions.

There are two modes (IDLE and STOP) effective when HALT instruction is executed by Z80 CPU. The T6497 continuously

provides the system clock (CLK) to Z80 CPU and peripherals unless HALT instruction is executed. In Idle Mode or Stop Mode, RSTI1, RSTI2 or RESET makes the T6497 resume the CLK.

| MS1 | MS2         | Mode | Functions                                                                                          |

|-----|-------------|------|----------------------------------------------------------------------------------------------------|

| 1   | 1           | RUN  | Always provides the system clock (CLK)                                                             |

| 0   | (Note)<br>X | IDLE | Stops the system clock (CLK), but keeps the oscillator operation. The CLK is kept low in this mode |

| 1   | 0           | STOP | Stop all the internal operation and the CLK is kept low.                                           |

(Note) X = Don't care

Table 1. Operation Modes

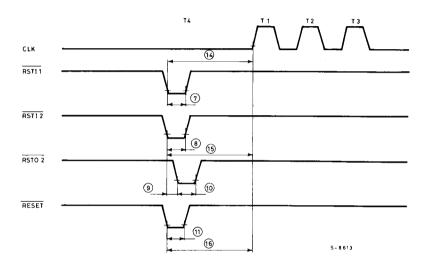

#### Halt Operation in Each Mode

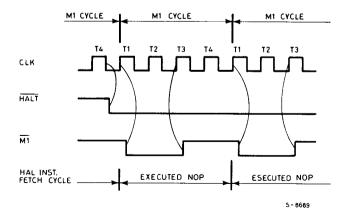

Run Mode (MS1=1. MS2=1). Figure 3 shows a basic timing when HALT instruction is executed. When Z80 CPU fetches the OPcode of HALT instruction (76H) from program memory, HALT signal goes active

("0" level) at the timing synchronized with the falling edge of T4 clock cycle and it shows that Z80 CPU is in the HALT state. In this mode, T6497 always provides the CLK.

Figure 3. Run Mode

## Halt Operation In Each Mode (Continued)

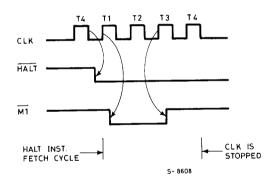

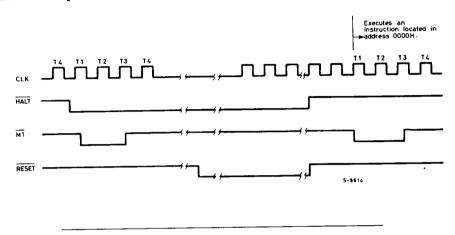

Idle Mode (MS1=0, MS2=don't care).

Figure 4 shows a basic timing when HALT instruction is executed in Idle Mode. When Z80 CPU fetches the OPcode of HALT instruction (76H) from program memory, HALT signal goes active at the timing sychronized with the falling edge of T4 clock cycle and it shows that Z80 CPU is in the HALT state.

T6497 stops providing the CLK at low level state during the T4 clock cycle of the following machine cycle next to OPcode fetch cycle of HALT instruction.

A rising edge of  $\overline{\text{M1}}$  signal during active  $\overline{\text{HALT}}$  signal makes the T6497 stop the CLK.

However the internal oscillator continuously works.

Stop Mode (MS1=1, MS2=0). The same function as IDLE MODE is implemented when HALT instruction is executed. (See Figure 4).

Only difference from IDLE MODE is that the T6497 completely stops its operation.

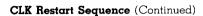

## **CLK Restart Sequence**

There are three inputs to resume the CLK.  $\overline{RSTI1}$  (level trigger),  $\overline{RSTI2}$  (edge trigger) or  $\overline{RESET}$  (level trigger) can be used.

**Idle mode.** Figure 5 shows the sequence to resume the CLK in IDLE MODE. In IDLE MODE, the CLK will resume in small delay when a signal to terminate is generated as the internal oscillator is working.

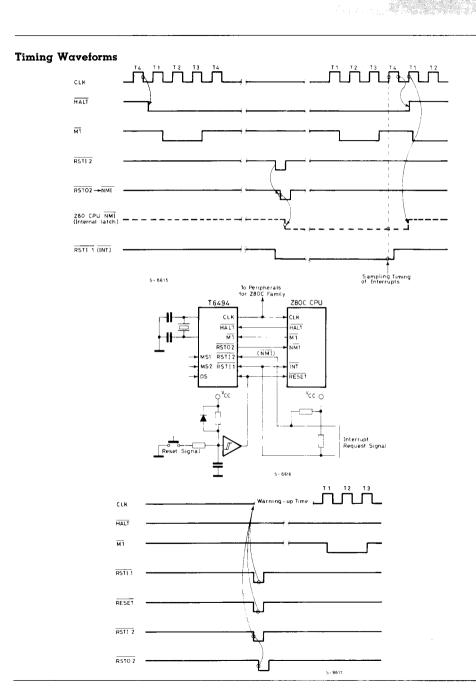

Stop Mode. Figure 6 shows the sequence to resume the CLK in STOP MODE. As the T6497 needs warming-up time to stabilize the frequency it uses the counter when a restart signal is generated.

DS (Divider Select) input must be used to determine warming-up time. External crystal frequency is divided by either 2<sup>17</sup> or 2<sup>14</sup>.

Figure 7 shows the block diagram regarding counter and Table 2 illustrates the warming-up time.

| DS     | Counter<br>Output                  |                          | Warming-up Time            |                            |  |  |

|--------|------------------------------------|--------------------------|----------------------------|----------------------------|--|--|

|        |                                    | f <sub>XTAL</sub> =4 MHz | f <sub>XTAL</sub> =2.5 MHz | f <sub>XTAL</sub> =400 KHz |  |  |

| 0<br>1 | 2 <sup>18</sup><br>2 <sup>15</sup> | 32.8 ms<br>4 ms          | 52.4 ms<br>6.6 ms          | 328 ms<br>40 ms            |  |  |

Table 2. Warming-up Time in Stop Mode

#### CLK Restart Sequence (Continued)

Note (1)

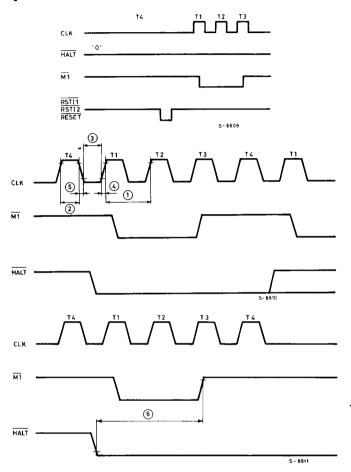

Note that either interrupt input or  $\overline{RESET}$  input must be generated to terminate the HALT state of Z80 CPU, where CLK is stopped at a low level during T4 state, in either IDLE MODE or STOP MODE.

(1) In case of  $\overline{\text{RESET}}$  input signal is connected with both Z80 CPU  $\overline{\text{RESET}}$  terminal and T6497  $\overline{\text{RESET}}$  terminal.

RESET input signal to Z80 CPU must be kept active (Low) during at least three clock cycles. When RESET input signal goes inactive, CPU fetches the first OPcode from address 0000H after at least two dummy clock cycles.

Thus CPU will terminate HALT state.

Note that if RESET input is connected with both Z80 CPU RESET terminal and T6497 RESET terminal, the RESET signal should be active for enough period to reset the Z80 CPU surely at power on reset. (See Figure 8.)

(2) In case of using an interrupt signal

Figure 9 shows the timing to resume the CLK and to terminate HALT state by an interrupt signal.

RSTII or RSTI2 input makes T6497 resume the CLK, And then an interrupt signal (INT or NMI) must be generated to terminate HALT state.

Note that Z80 CPU in HALT state executes

NOP instruction unless an interrupt is recognized.

a) In case of using  $\overline{NMI}$

$\overline{\text{NMI}}$  of Z80 CPU is an input (edge trigger) with a latch. If active (low)  $\overline{\text{NMI}}$  signal is accepted prior to sampling timing for an interrupt request signal, Z80 CPU recognizes  $\overline{\text{NMI}}$ .  $\overline{\text{RSTI2}}$  of T6497 may be used as  $\overline{\text{NMI}}$  input, since  $\overline{\text{RSTI2}}$  has a latch and  $\overline{\text{RSTO2}}$  may be connected with  $\overline{\text{NMI}}$  input of Z80 CPU.

b) In case of using  $\overline{INT}$

In maskable interrupt  $(\overline{\text{INT}})$ , interrupt enable flip flop (IFF) must be set by software before receiving an interrupt signal.

Figure 9 shows the timing when an interrupt signal is connected with both RSTI1 terminal of T6497 and INT terminal of 7.80 CPU.

Note 2)

The internal counter of T6497 to determine warming-up time is not used in Stop Mode when RESET input is activated to resume the clock, so Z80 CPU may not restart properly due to unstable clok when the oscillator restarts.

Therefore connect RESET input of T6497 with that of Z80 CPU when RESET input of T6497 is used to restart the clock in Stop Mode. Also it is suggested that RESET input be kept low for enough period to initialize Z80 CPU.

#### **CLK Restart Sequence** (Continued)

Note the followings when release from power down state.

- When external oscillator has been stopped to enter power down state, some warming-up time may be required to obtain precious and stable system clock for release from power down state.

- (2) When HALT instruction is executed to enter power down state, Z80 CPU will enter HALT state. An interrupt signal (NMI or INT) or RESET signal must be generated to Z80 CPU after the system clock is supplied to release power down state. Otherwise Z80 CPU is still in HALT state even if the system clock is supplied.

## CLK Restart Sequence (Continued)

# Release from Power Down State for CMOS 280

The system clock must be supplied to Z80 CPU to release power down state. When the system clock is supplied to CLK terminal of

Z80 CPU, CPU restarts operation continuously from the state when power down function has been implemented.

# Absolute Maximum Ratings

| Symbol              | Item                                                           | Rating                         |  |  |

|---------------------|----------------------------------------------------------------|--------------------------------|--|--|

| V <sub>CC</sub>     | V <sub>CC</sub> Supply Voltage with respect to V <sub>SS</sub> | -0.5V to 7.0V                  |  |  |

| V <sub>IN</sub>     | Input Voltage                                                  | -0.5V to V <sub>CC</sub> +0.5V |  |  |

| I <sub>IN</sub>     | Input Current                                                  | ±10mA                          |  |  |

| $P_{D}$             | Power Dissipation (TA-85°C)                                    | 250mW                          |  |  |

| T <sub>SOLDER</sub> | Soldering Temperature (Soldering Time 10 sec.)                 | 260°C                          |  |  |

| T <sub>STG</sub>    | Storage Temperature                                            | −65°C to 150°C                 |  |  |

| T <sub>OPR</sub>    | Operating Temperature                                          | −40°C to 85°C                  |  |  |

# DC Characteristics (TA = -40°C to 85°C, $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ )

| Symbol              | Parameter                                           | Min                  | Typ | Max          | Unit | Test Condition                                                                                                          |

|---------------------|-----------------------------------------------------|----------------------|-----|--------------|------|-------------------------------------------------------------------------------------------------------------------------|

| V <sub>IL</sub>     | Input Low Voltage (except XTAL1,2)                  | -0.5                 | _   | 0.8          | v    |                                                                                                                         |

| $\overline{v_{IH}}$ | Input High Voltage (except XTAL1,2)                 | 2.2                  | _   | $v_{\rm CC}$ | v    |                                                                                                                         |

| V <sub>OLC</sub>    | Output Low Voltage (CLK)                            | _                    |     | 0.4          | v    | I <sub>OL</sub> = 2.0mA                                                                                                 |

| $v_{OL}$            | Output Low Voltage (except CLK)                     | _                    | _   | 0.4          | V    | I <sub>OL</sub> = 2.0mA                                                                                                 |

| v <sub>OHC</sub>    | Output High Voltage (CLK)                           | V <sub>CC</sub> -0.6 | _   |              | v    | I <sub>OH</sub> = 250μA                                                                                                 |

| V <sub>OH1</sub>    | Ouput High Voltage (except CLK)                     | 2.4                  | -   | _            | V    | $I_{OH} = -1.6 \text{mA}$                                                                                               |

| V <sub>OH2</sub>    | Output High Voltage (except CLK)                    | V <sub>CC</sub> 0.8  | _   | _            | V    | $I_{OH} = -250 \mu A$                                                                                                   |

| I <sub>IL</sub>     | Input Leakage                                       | _                    | _   | ±1           | μA   | $V_{SS} \leq V_{IN} \leq V_{CC}$                                                                                        |

| I <sub>OL</sub>     | Output Leakage                                      | _                    | _   | ± l          | μA   | $V_{SS} + 0.4V \le V_{IN} \le V_{CC}$                                                                                   |

| I <sub>CC1</sub>    | V <sub>CC</sub> Supply Current<br>(NORMAL/RUN MODE) | _                    | 2   | 4            | mA   | $V_{CC} = 5V$ $f_{XTAL} = 4 \text{ MHz}$ $V_{IH} = V_{CC} - 0.2V$ $V_{IL} = 0.2V$                                       |

| I <sub>CC2</sub>    | V <sub>CC</sub> Supply Current<br>(STOP MODE)       | _                    | 0.3 | 10           | μА   | $V_{CC} = 5V$<br>$V_{IH} = V_{CC} - 0.2V$<br>$V_{IL} = 0.2V$                                                            |

| I <sub>CC3</sub>    | V <sub>CC</sub> Supply Current<br>(IDLE MODE)       | -                    | 0.5 | 1            | mA   | V <sub>CC</sub> = 5V<br>f <sub>XTAL</sub> = 4 MHz<br>V <sub>IH</sub> = V <sub>CC</sub> - 0.2V<br>V <sub>IL</sub> = 0.2V |

# AC Characteristics (TA = $-40^{\circ}$ C to 85°C, $V_{CC} = 5V \pm 10\%$ , $V_{SS} = 0V$ )

| Number | Symbol              | Parameter                                 |                  | Min      | Тур                                                      | Мах    | Unit     | Test<br>Conditions |

|--------|---------------------|-------------------------------------------|------------------|----------|----------------------------------------------------------|--------|----------|--------------------|

| 1      | TcC                 | CLK Cycle Time                            |                  | 250      | _                                                        |        | ns       |                    |

| 2      | TwCh                | CLK Pulse Width (High)                    |                  | 110      |                                                          | _      | ns       |                    |

| 3      | TwCl                | CLK Pulse Width (Low)                     |                  | 110      |                                                          |        | ns       |                    |

| 4      | TrC                 | CLK Rise Time                             |                  |          | _                                                        | 15     | ns       |                    |

| 5      | TfC                 | CLK Fall Time                             |                  | _        |                                                          | 15     | ns       |                    |

| 6      | TsHALT(Mlr)         | HALT Setup Time to Ml↑                    |                  | 10       |                                                          |        | ns       |                    |

| 7      | TwRSTI1             | RSTII Pulse Width (Low)                   |                  | 80       | _                                                        |        | ns       |                    |

| 8      | TwRSTI2             | RSTI2 Pulse Width (Low)                   |                  | 200      |                                                          |        | ns       |                    |

| 9      | TdRSTO2<br>(RSTI2f) | RSTI2 to RSTO2↓ Delay                     |                  | _        |                                                          | 100    | ns       |                    |

| 10     | TwRSTO2             | RST02 Pulse Width (Low)                   |                  | 80       |                                                          |        | ns       | $C_L = 100 pF$     |

| 11     | Twreset             | RESET Pulse Width (Low)                   |                  | 80       |                                                          |        | ns       | <u> </u>           |

| 12     | TRSTIS              | CLK Restart Delay by RSTI1 (Stop Mode)    | DS = 0<br>DS = 1 | <u> </u> | (2 <sup>17</sup> + 2.5)TcC<br>(2 <sup>14</sup> + 2.5)TcC | _<br>_ | ns<br>ns |                    |

| 13     | TRST2S              | CLK Restart Delay by RSTI2 (Stop Mode)    | DS = 0<br>DS = 1 |          | (2 <sup>17</sup> + 2.5)TcC<br>(2 <sup>14</sup> + 2.5)TcC | _<br>_ | ns<br>ns |                    |

| 14     | TRST1I              | CLK Restart Delay by<br>RSTII (Idle Mode) |                  | _        | 2.5 TcC                                                  |        | ns       |                    |

| 15     | TRST2I              | CLK Restart Delay by<br>RSTI2 (Idle Mode) |                  |          | 2.5 TcC                                                  |        | ns       |                    |

| 16     | TRESETI             | CLK Restart Delay by RESET (Idle Mode)    |                  |          | l TcC                                                    |        | ns       |                    |

Note) A.C. Testing: Inputs are driven at 2.4V for a logic "1" and 0.4V for a logic "0". Timing measurements are made at 2.2V for a logic "1" and 0.8V for a logic "0" except CLK output. CLK is made at V<sub>CC</sub> = 0.6V for a logic "1" and 0.4V for a logic "0".

TO CONTRA

# Timing Waveforms (Continued)

## Ordering Information

| Туре     | Package | Temp.       | Clock | Description                                |  |  |

|----------|---------|-------------|-------|--------------------------------------------|--|--|

| T6497 B6 | Plastic | - 40°/+85°C | 4 MHz | Clock Generator Controller<br>for Z80 CMOS |  |  |