#### TOSHIBA CMOS DIGITAL INTEGRATED CIRCUIT SILICON MONOLITHIC

# T6B65AFG

#### Column Driver LSI for Dot Matrix Graphic LCD's

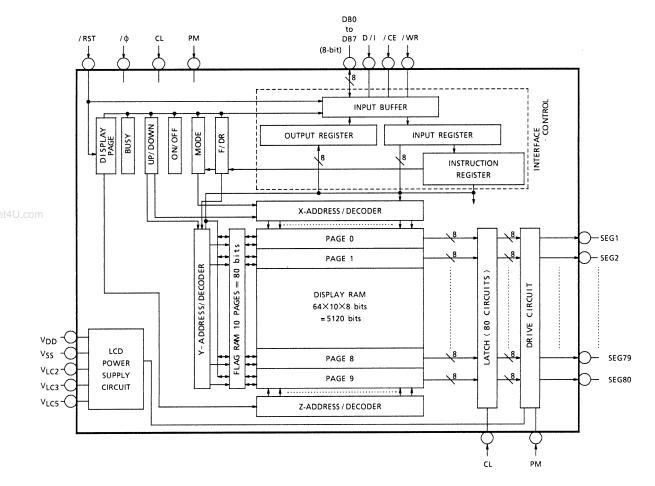

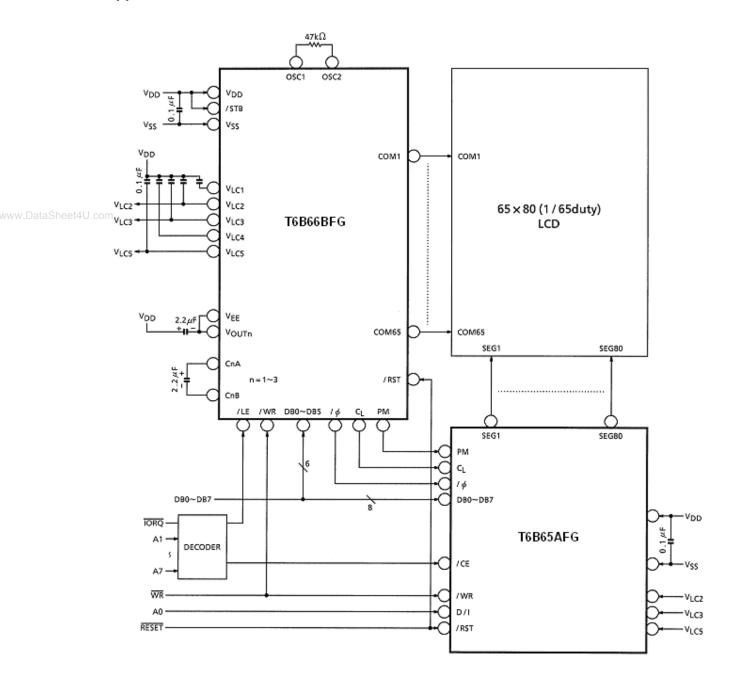

Manufactured using the CMOS process, the T6B65AFG is a column (segment) driver for small-to-medium-sized dot matrix graphic LCDs. Use of the T6B65AFG enables power dissipation to be reduced. It is designed to connect directly to an 8-bit microprocessor unit. The MPU can program all operating modes for the T6B65AFG asynchronously.

www.DataSheet4U.com The T6B65AFG stores display data transferred from an MPU in its internal display RAM. The contents of the internal display RAM correspond to the image on the LCD screen and are used to generate the LCD drive signal.

Three T6B65AFGs can be combined with a Toshiba T6B66BFG row (common) driver to drive a 240-dot by 65-dot LCD screen. The T6B65AFG is lead (Pb)-free product.

Weight: 1.6 g (typ.)

#### **Features**

• Dot matrix graphic LCD column driver with display RAM

• Display RAM capacity : 64 lines × 10 pages × 8 bits = 5120 bits (display area)

$1 \text{ line} \times 10 \text{ pages} \times 8 \text{ bits} = 80 \text{ bits (flag area)}$

Total = 5200 bits

• LCD drive outputs : 80

• Interface : 80-family MPU (8-bit)

• RAM data directly echoed to LCD

(1) RAM bit data = 1 ..... ON (2) RAM bit data = 0 ..... OFF

• Duty: Can be controlled by the T6B66BFG.

• Display OFF functions

Various functions

X/Y-counter selection, Up/Down mode selection, X-address setting, Y-address setting, Display Start Line setting, "Status Read", display data read/write

• Low power consumption

Logic power supply : 2.7 to 5.5 V

CMOS Si-Gate process

100-pin-plastic flat package

## **Block Diagram**

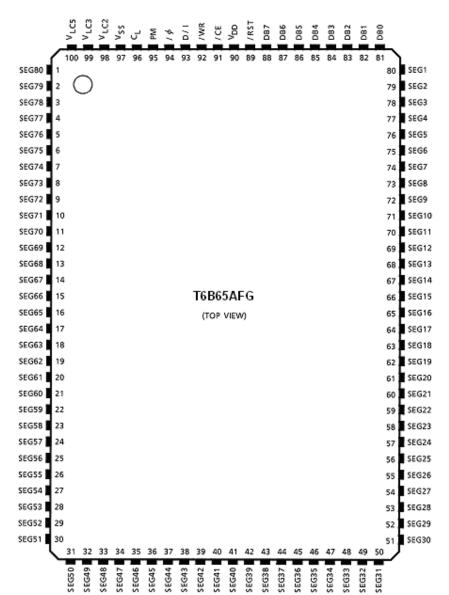

#### **Pin Assignment**

www.DataSheet4U.co

#### **Pin Functions**

| Pin Name                          | Pin No .    | 1/0    | Function                                      |

|-----------------------------------|-------------|--------|-----------------------------------------------|

| SEG1 to SEG80                     | 1 to 80     | Output | Column driver outputs                         |

| CL                                | 96          | Input  | Shift clock pulse                             |

| PM                                | 95          | Input  | Pre-frame signal input                        |

| /φ                                | 94          | Input  | Clock signal                                  |

| DB0 to DB7                        | 81 to 88    | 1/0    | Data bus                                      |

| D/I                               | 93          | Input  | Data/instruction select signal input (Note 1) |

| /WR                               | 92          | Input  | Write select signal input (Note 2)            |

| / CE                              | 91          | Input  | Chip enable signal input (Note 3)             |

| / RST                             | 89          | Input  | Reset signal input: / RST = L Reset state     |

| V <sub>DD</sub> , V <sub>SS</sub> | 90, 97      | _      | Power supply                                  |

| V <sub>LC2, 3, 5</sub>            | 98, 99, 100 | _      | Power supply for LCD drive                    |

ww.DataSheet4U.com

Note 1: D / I = H ...... Indicates that the data on DB0 to DB7 is display data.

D / I = L ...... Indicates that the data on DB0 to DB7 is control data.

Note 2: / WR = H ..... Read is selected. / WR = L ..... Write is selected.

Note 3: When writing....... Data on DB0 to DB7 is latched on the rising edge of / CE. When reading...... Data appears at DB0 to DB7 while / CE is LOW.

#### **Function of Each Block**

#### Interface

The T6B65AFG is equipped with interface logic enabling interfacing to an 8-bit (80-family) MPU.

#### Input register

This register holds 8-bit data from the MPU. Instruction and display data are distinguished by the  $\rm D\,/\,I$  signal and the 8-bit data.

#### Output register

This register holds 8-bit data from the display RAM. When display data is read, the display data in the address is copied to this register. The address is then automatically incremented or decremented. When an address is set, therefore, the correct data does not appear on the first data reading. The data at the specified address appears on the second data reading.

#### X, Y (Page)-address counter

The X, Y (Page)-address counter holds a display RAM address. Reading or writing to the display RAM causes the X / Y-address to increment or decrement automatically.

#### Z-address counter

The Z-address counter holds the 6-bit datum that indicates the display start line. This value is preset by the PM signal. The value indicates the address of the display start line, which is the line that appears at the top of the screen.

#### Counter Up / Down register

This register determines the counter and Up / Down mode. When the X-counter / Up mode is selected, reading or writing to the RAM causes the X-counter to increment automatically.

When the X-counter / Down mode is selected, reading or writing to the RAM causes the X-counter to decrement automatically. When the Y-counter / Up mode is selected, reading or writing to the RAM causes the Y-counter to increment automatically. When the Y-counter / Down mode is selected, reading or writing to the RAM causes the Y-counter to decrement automatically.

#### Display ON / OFF register

This 1-bit register holds the ON / OFF state. In the OFF state, the output is ignored. In the ON state, the data in the display RAM is displayed.

The data in the display RAM is independent of the value of the display ON / OFF setting.

#### Busy flag

The Busy flag is set when an instruction other than the Status Read instruction is executed. Using Status Read, you can find out whether the Busy flag has been set or not. While the Busy flag is set, the T6B65A cannot accept any instruction other than Status Read.

Ensure, therefore, that the Busy flag is reset before an instruction is issued.

The Busy state time (T) is always as follows:

$1/F \le T \le 2/F$  [seconds] F:  $\varphi$  frequency (one half of the T6B66BFG's oscillation frequency)

#### Latch

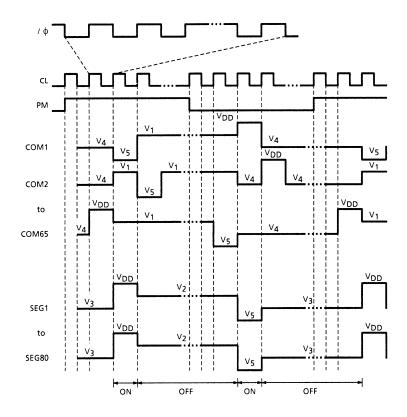

The rising edge of CL latches data from the display RAM.

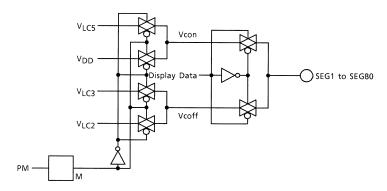

#### Column driver circuit and LCD voltage generation circuit

The column driver circuit consists of 80 driver circuits. The combination of display data from latches and the M signal selects one of the four LCD levels. Details of the voltage generation circuit and column driver circuit are shown in the diagram below:

#### **Command Definitions**

|     |               |              |     |     |      |          | Code       |          |                    |                                                               |

|-----|---------------|--------------|-----|-----|------|----------|------------|----------|--------------------|---------------------------------------------------------------|

| /WR | D/I           | DB7          | DB6 | DB5 | DB4  | DB3      | DB2        | DB1      | DB0                | Function                                                      |

| 0   | 0             | 0            | 0   | 0   | 0    | 0        | 0          | 1        | 1/0                | Display ON (1) / OFF (0)                                      |

| 0   | 0             | 0            | 0   | 0   | 0    | 0        | 1          | Y/X      | U/D                | Y (1) / X (0) Counter Select<br>UP (1) / Down (0) Mode Select |

| 0   | 0             | 0            | 0   | 0   | 0    | 1        | *          | *        | *                  | Test Mode Select                                              |

| 0   | 0             | 0            | 1   |     | Z    | Z-Addres | s (0 to 63 | 5)       |                    | Set Z-Address                                                 |

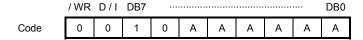

| 0   | 0             | 1            | 0   |     | >    | (-Addres | s (0 to 63 | 3)       |                    | Set X-Address                                                 |

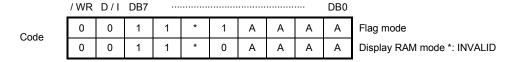

| 0   | 0             | 1            | 1   | *   | F/DR | Y (P     | age) -Ad   | dress (0 | to 9)              | Set Y (Page) -Address                                         |

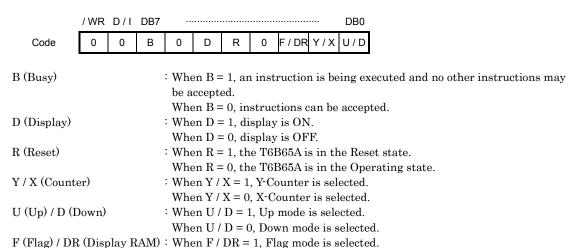

| 1   | 0             | В            | 0   | D   | R    | 0        | F/DR       | Y / X    | U/D                | Status Read (Note)                                            |

| 0   | 1             | 1 Write Data |     |     |      |          |            |          | Write Display Data |                                                               |

| 1   | 1 1 Read Data |              |     |     |      |          |            |          | Read Display Data  |                                                               |

ww.DataSheet4U.com

#### \*: INVALID

Note: B : Busy flag

D : Display ON (1) / OFF (0)

R : Reset

Y / X : Counter Select 1: Y-Counter 0: X-Counter U / D : Up / Down Select 1: Up 0: Down

F / DR: Flag Mode 1: Flag Mode 0: Display RAM Mode

#### Display ON / OFF

Code

Code

/WR D/I DB7 DB0 Display ON Display OFF

This command controls the display ON / OFF setting. Display ON / OFF does not change the display RAM data. When / RST = L, Display = OFF (all the segment outputs are at the VDD level when Display = OFF). The T6B65A is in display OFF mode after a reset operation.

#### Counter UP / DOWN select

/WR D/I DB7 DB0 X-Counter / Down Mode X-Counter / Up Mode Y-Counter / Down Mode Y-Counter / Up Mode

This command selects the counter and Up / Down mode. When / RST = L, Y-Counter / Up mode is selected.

#### • Test mode select

|      | /WR | D/I | DB7 |   |   |   |   |   |   | DB0 |            |

|------|-----|-----|-----|---|---|---|---|---|---|-----|------------|

| Code | 0   | 0   | 0   | 0 | 0 | 0 | 1 | * | * | *   | *: INVALID |

This command selects the Test mode. Do not use this command.

#### Set Z-address (Display Start Line)

|      | /WR | D/I | DB7 |   |   |   |   |   |   | DB0 |

|------|-----|-----|-----|---|---|---|---|---|---|-----|

| Code | 0   | 0   | 0   | 1 | Α | Α | Α | Α | Α | Α   |

This command specifies which RAM line (0 to 63) is displayed at the top of the screen. When the display duty is more than 1/64 (e.g., 1/33, 1/49), display begins at a line within the range 1 to 33 or 1 to 49. This command only applied to display RAM. The line following the last line of the display RAM is the flag RAM.

#### Set X-address

This command sets the X-address (0 to 63). When the Counter Up / Down Select command selects this address counter, reading or writing to the RAM causes the X-address to increment or decrement automatically.

In X-Counter / Up mode, if the previous X-address is 63, the new X-address after the increment will be 0 and the Y (page)-address will be incremented. In Y-Counter / Down mode, if the previous X-address is 0, the new X-address after the decrement will be 63 and the Y (page)-address will be decremented.

#### Set Y (Page)-address

This command sets the Y (page) -address and also selects Flag mode or Display RAM mode.

In Flag mode, you can read data from or write data to Flag RAM only but cannot access the Display RAM.

In Display RAM mode, you can read data from or write data to the Display RAM only but cannot access the Flag RAM.

When the Counter Up / Down Select command selects this address counter, reading from or writing to the RAM causes the Y-address to increment or decrement automatically.

In Y-Counter / Up mode, if the previous Y-address is 9, the new Y-address after the increment will be 0 and the X-address will be incremented. In Y-Counter / Down mode, if the previous Y-address is 0, the new Y-address after the decrement will be 9 and the X-address will be decremented.

In Flag mode, only Y-Counter / Up or Down mode is permitted.

#### Status Read

ww.DataSheet4U.com

• Read / Write display data

|      | /WR | D/I | DB7 |   |   |   |   |   |   | DB0 | _          |

|------|-----|-----|-----|---|---|---|---|---|---|-----|------------|

| Code | 0   | 1   | D   | D | D | D | D | D | D | D   | Write Data |

| Code | 1   | 1   | D   | D | D | D | D | D | D | D   | Read Data  |

This command sends data to or receives data from the LCD RAM address that was specified. However, the correct data does not appear on the first read of the display data.

When F/DR = 0, Display RAM is selected.

Refer to the description of the Output Register in the section FUNCTION OF EACH BLOCK.

#### **LCD Drive Waveform**

LCD driver timing chart (1 / 65 duty)

### Absolute Maximum Ratings (Ta = 25°C)

| Item                  | Symbol                             | Rating                                          | Unit |

|-----------------------|------------------------------------|-------------------------------------------------|------|

| Supply Voltage (1)    | V <sub>DD</sub><br>(Note 1)        | -0.3 to 7.0                                     | V    |

| Supply Voltage (2)    | V <sub>LC2, 3, 5</sub><br>(Note 3) | V <sub>DD</sub> - 18.0 to V <sub>DD</sub> + 0.3 | V    |

| Input Voltage         | V <sub>IN</sub><br>(Note 1, 2)     | -0.3 to V <sub>DD</sub> + 0.3                   | V    |

| Operating Temperature | T <sub>opr</sub>                   | −20 to 75                                       | °C   |

| Storage Temperature   | T <sub>stg</sub>                   | -55 to 125                                      | °C   |

Note 1: Referenced to  $V_{SS}$

Note 2: Applies to all data bus pins and input pins except  $V_{LC2}$ ,  $V_{LC3}$  and  $V_{LC5}$

Note 3: Ensure that the following condition is always maintained:

$V_{DD} \geq V_{LC2} \geq V_{LC3} \geq V_{LC5}$

# Electrical Characteristics DC Characteristics Test Conditions (1)

(Unless otherwise specified,  $V_{SS} = 0$ ,  $V_{DD} = 3.0 \text{ V} \pm 10\%$ ,  $V_{LC5} = V_{DD} - 16 \text{ V}$ , Ta = -20 to 75°C)

| Ite                      | m                                                   | Symbol           | Test<br>Circuit           | Test Condition                                                        | Min                      | Тур. | Max                     | Unit       | Pin Name                                                   |

|--------------------------|-----------------------------------------------------|------------------|---------------------------|-----------------------------------------------------------------------|--------------------------|------|-------------------------|------------|------------------------------------------------------------|

| Operating S              | Supply (1)                                          | $V_{DD}$         | _                         | _                                                                     | 2.7                      | _    | 3.3                     | V          | $V_{DD}$                                                   |

| Operating S              | Supply (2)                                          | $V_{LC5}$        | _                         | _                                                                     | V <sub>DD</sub><br>-16.0 | _    | V <sub>DD</sub><br>-4.0 | ٧          | V <sub>LC5</sub>                                           |

| Input                    | H Level                                             | V <sub>IH</sub>  | _                         | _                                                                     | 0.8<br>V <sub>DD</sub>   | -    | V <sub>DD</sub>         | ٧          | CL, PM, / φ<br>DB0 to DB7,                                 |

| Voltage                  | L Level                                             | V <sub>IL</sub>  | _                         | _                                                                     | 0                        | _    | 0.2<br>V <sub>DD</sub>  | ٧          | D / I, / WR,<br>/ CE, / RST                                |

| Output                   | H Level V <sub>OH</sub> — I <sub>OH</sub> = -400 μA |                  | I <sub>OH</sub> = -400 μA | V <sub>DD</sub><br>-0.2                                               | ı                        | _    | >                       | DB0 to DB7 |                                                            |

| Voltage                  | L Level                                             | V <sub>OL</sub>  | _                         | Ι <sub>ΟL</sub> = 400 μΑ                                              | _                        | _    | 0.2                     | ٧          | DB0 10 DB1                                                 |

| Column Dri<br>Resistance |                                                     | R <sub>col</sub> | _                         | V <sub>DD</sub> - V <sub>LC5</sub> = 11.0 V<br>Load current = ±100 μA | _                        | _    | 7.5                     | ΚΩ         | SEG1 to<br>SEG80                                           |

| Input Leaka              | ige                                                 | I <sub>IL</sub>  | _                         | V <sub>IN</sub> = V <sub>DD</sub> to GND                              | -1                       | _    | 1                       | μA         | DB0 to DB7,<br>D / I, / WR,<br>/ CE, / RST,<br>CL, PM, / φ |

| Operating F              | requency                                            | fφ               |                           | _                                                                     | 10                       | 1    | 250                     | kHz        | / φ                                                        |

| Current Cor<br>(1)       | nsumption                                           | I <sub>DD1</sub> | _                         | (Note 1)                                                              | _                        | 100  | 140                     | μΑ         | V <sub>DD</sub>                                            |

| Current Cor<br>(2)       | nsumption                                           | I <sub>DD2</sub> |                           | (Note 2)                                                              |                          | 20   | 30                      | μA         | V <sub>DD</sub>                                            |

| Current Cor<br>(3)       | nsumption                                           | I <sub>DD3</sub> | _                         | (Note 3)                                                              | -1                       | _    | 1                       | μA         | V <sub>DD</sub>                                            |

Note 1: Current consumption while the internal data receiver is operating:

$V_{DD}$  = 2.7 to 3.3 V,  $V_{LC5}$  =  $V_{DD}$  – 16 V, Ta = 25°C

1/9 bias, 1/65 duty, no load,  $f_{PM} = 35$  Hz,  $f_{CE} = 1$  MHz

Note 2: Current consumption while the internal data receiver is inactive:

$V_{DD}$  = 2.7 to 3.3 V,  $V_{LC5}$  =  $V_{DD}$  -16 V, Ta = 25°C

1/9 bias, 1/65 duty, no load

Note 3: Current consumption in low power mode ( / STB pin of T6B66BFG = L):

$V_{DD}$  = 3.0V,  $V_{LC5}$  = 0 V, Ta = 25°C, no load

# Test Conditions (2) (Unless otherwise noted, $V_{SS}$ = 0, $V_{DD}$ = 5.0 V ± 10%, $V_{LC5}$ = $V_{DD}$ = 16 V, Ta = -20 to 75°C)

| Ite                     | m                                 | Symbol                 | Test<br>Circuit          | Test Condition                                                        | Min                      | Тур. | Max                     | Unit | Pin Name                                                  |

|-------------------------|-----------------------------------|------------------------|--------------------------|-----------------------------------------------------------------------|--------------------------|------|-------------------------|------|-----------------------------------------------------------|

| Operating S             | Supply (1)                        | $V_{DD}$               | _                        | _                                                                     | 4.5                      | _    | 5.5                     | V    | $V_{DD}$                                                  |

| Operating S             | Supply (2)                        | $V_{LC5}$              | _                        | _                                                                     | V <sub>DD</sub><br>-16.0 | _    | V <sub>DD</sub><br>-4.0 | ٧    | V <sub>LC5</sub>                                          |

| Input                   | H Level                           | V <sub>IH</sub>        | _                        | _                                                                     | 0.7<br>V <sub>DD</sub>   | _    | V <sub>DD</sub>         | ٧    | CL, PM, /φ<br>DB0 to DB7,                                 |

| Voltage                 | L Level                           | evel V <sub>IL</sub> — |                          |                                                                       | 0                        | ı    | 0.3<br>V <sub>DD</sub>  | ٧    | D / I, / WR,<br>/ CE, / RST                               |

| Output                  | H Level                           | V <sub>OH</sub>        | _                        | I <sub>OH</sub> = -400 μA                                             | . 1 -0.4 1 1 1           |      | DB0 to DB7              |      |                                                           |

| Voltage                 | Voltage L Level V <sub>OL</sub> — |                        | I <sub>OL</sub> = 400 μA | _                                                                     | _                        | 0.4  | 0.4 V                   |      |                                                           |

| Column Ou<br>Resistance |                                   | R <sub>col</sub>       | _                        | V <sub>DD</sub> - V <sub>LC5</sub> = 11.0 V<br>Load current = ±100 μA | _                        | _    | 7.5                     | kΩ   | SEG1 to<br>SEG80                                          |

| Input Leaka             | ige                               | I <sub>IL</sub>        | _                        | V <sub>IN</sub> = V <sub>DD</sub> to GND                              | -1                       | 1    | 1                       | μA   | DB0 to DB7,<br>D / I, / WR,<br>/ CE, / RST,<br>CL, PM, /φ |

| Operating F             | requency                          | fφ                     | _                        |                                                                       | 10                       | ı    | 250                     | kHz  | / φ                                                       |

| Current Cor<br>(1)      | nsumption                         | I <sub>DD1</sub>       | _                        | (Note 1)                                                              | _                        | 220  | 330                     | μΑ   | V <sub>DD</sub>                                           |

| Current Cor<br>(2)      | nsumption                         | I <sub>DD2</sub>       |                          | (Note 2)                                                              |                          | 35   | 50                      | μΑ   | V <sub>DD</sub>                                           |

| Current Cor<br>(3)      | nsumption                         | I <sub>DD3</sub>       | _                        | (Note 3)                                                              | -1                       | -    | 1                       | μΑ   | V <sub>DD</sub>                                           |

Note 1: Current consumption while the internal data receiver is operating:

$V_{DD}$  = 4.0 to 5.5 V,  $V_{LC5}$  =  $V_{DD}$  - 16 V, Ta = 25°C

1/9 bias, 1/65 duty, no load,  $f_{PM} = 35$  Hz,  $f_{CE} = 1$  MHz

Note 2: Current consumption while the internal data receiver is inactive:

$V_{DD}$  = 4.0 to 5.5 V,  $V_{LC5}$  =  $V_{DD}$  - 16 V, Ta = 25°C

1/9 bias, 1/65 duty, no load

Note 3: Current consumption in Low Power mode ( / STB pin of T6B66BFG = L):

$V_{DD}$  = 5.0 V,  $V_{LC5}$  = 0 V, Ta = 25°C, no load

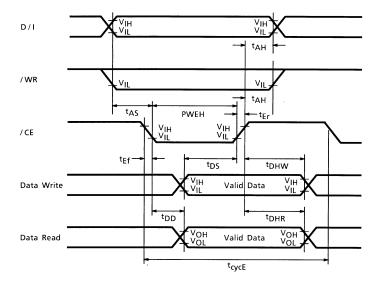

#### **AC Characteristics**

ww.DataSheet4U.com

# Test Conditions (1) (VSS = 0 V , VDD = 3.0 V $\pm$ 10%, VLC5 = 0 V , Ta = -20 to 75°C)

| ltem                    | Symbol                            | Min  | Max | Unit |

|-------------------------|-----------------------------------|------|-----|------|

| Enable Cycle Time       | t <sub>cycE</sub>                 | 1000 | _   | ns   |

| Enable Pulse Width      | PWEH                              | 450  | _   | ns   |

| Enable Rise / Fall Time | t <sub>Er</sub> , t <sub>Ef</sub> | _    | 25  | ns   |

| Address Set-up Time     | t <sub>AS</sub>                   | 40   | _   | ns   |

| Address Hold Time       | t <sub>AH</sub>                   | 10   | _   | ns   |

| Data Set-up Time        | t <sub>DS</sub>                   | 280  | _   | ns   |

| Data Hold Time          | t <sub>DHW</sub>                  | 10   | 1   | ns   |

| Data Delay Time         | t <sub>DD</sub> (Note)            | _    | 300 | ns   |

| Data Hold Time          | t <sub>DHR</sub> (Note)           | 20   |     | ns   |

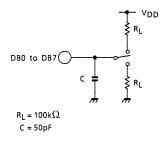

**Load Circuit**

Test Conditions (2) (V<sub>SS</sub> = 0 V, V<sub>DD</sub> = 5.0 V  $\pm$  10%, V<sub>LC5</sub> = 0 V, Ta = -20 to 75°C)

| Item                    | Symbol                            | Min | Max | Unit |

|-------------------------|-----------------------------------|-----|-----|------|

| Enable Cycle Time       | t <sub>cycE</sub>                 | 500 | _   | ns   |

| Enable Pulse Width      | PWEH                              | 220 | _   | ns   |

| Enable Rise / Fall Time | t <sub>Er</sub> , t <sub>Ef</sub> | _   | 20  | ns   |

| Address Set-up Time     | tas                               | 40  | _   | ns   |

| Address Hold Time       | t <sub>AH</sub>                   | 0   | _   | ns   |

| Data Set-up Time        | t <sub>DS</sub>                   | 60  | _   | ns   |

| Data Hold Time          | t <sub>DHW</sub>                  | 10  | _   | ns   |

| Data Delay Time         | t <sub>DD</sub> (Note)            | _   | 120 | ns   |

| Data Hold Time          | t <sub>DHR</sub> (Note)           | 20  | _   | ns   |

Note: With load circuit connected

## **Application Circuit**

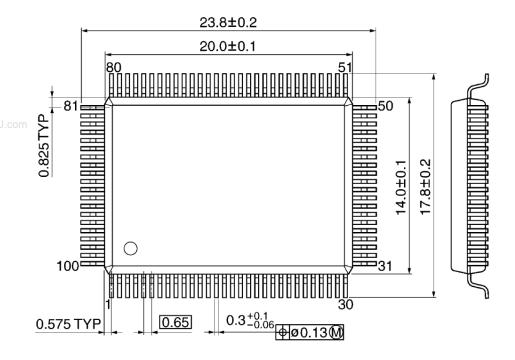

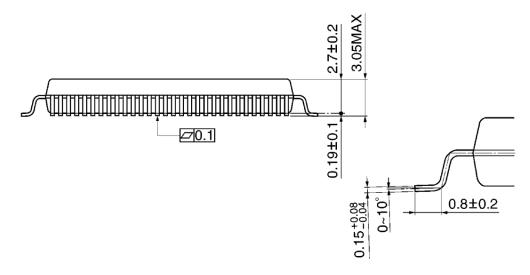

### **Package Dimensions**

QFP100-P-1420-0.65Q

Unit: mm

14

Weight:1.6g (Typ.)

nan DataChaat411 aar

#### **RESTRICTIONS ON PRODUCT USE**

030619EBA

- The information contained herein is subject to change without notice.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of TOSHIBA or others.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- TOSHIBA products should not be embedded to the downstream products which are prohibited to be produced and sold, under any law and regulations.