TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

## **T6B70BFG**

### Interface IC for Hot Water Dispensers

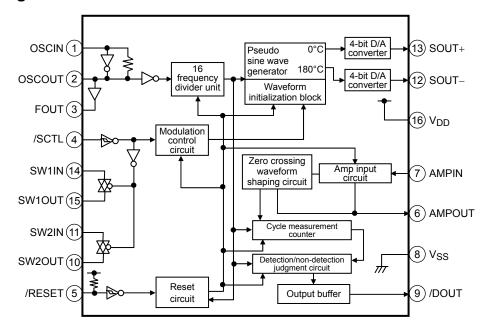

The T6B70BFG is designed to be used mainly as an interface IC for communication between hot water dispensers and the corresponding controller unit, and comes equipped with a two channel 4-bit D/A converter, pseudo sine wave generator and an external analog signal detection circuit.

### **Features**

- Built-in two channel 4-bit D/A converter (opposite polarities)

- Built-in pseudo sine wave generator (external clock 1/16 frequency divider)

- Built-in external analog signal detection/non-detection circuit

- Built-in two channel analog switch

Weight: 0.16 g (typ.)

### **Block Diagram**

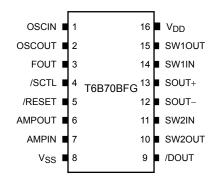

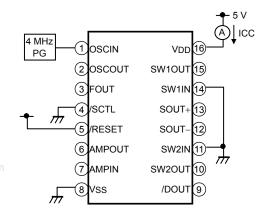

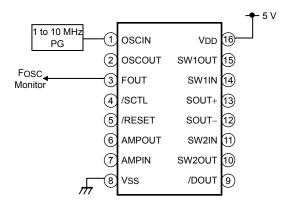

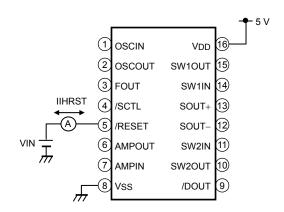

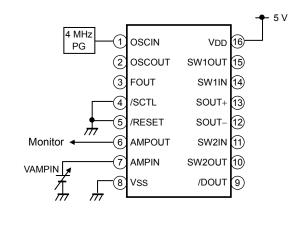

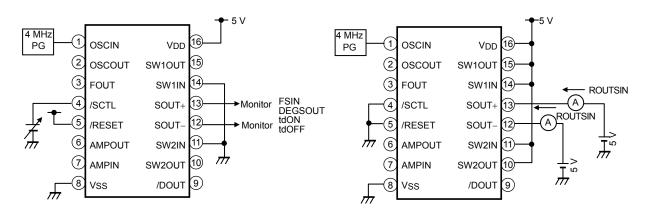

### **Pin Assignment Diagram**

### **Pin Functions**

| Pin No.    | Symbol          | Input/Output | Function                                                         |

|------------|-----------------|--------------|------------------------------------------------------------------|

| 1          | OSCIN           | Input        | Pins connected to oscillation                                    |

| 2          | OSCOUT          | Output       | Pins connected to oscillation                                    |

| 3          | FOUT            | Output       | Output pin for oscillation waveform shaping circuit              |

| 4          | /SCTL           | Input        | Modulation control signal input pin                              |

| 5          | /RESET          | Input        | Reset signal input pin                                           |

| 6          | AMPOUT          | Output       | Amplifier signal output pin                                      |

| 7          | AMPIN           | Input        | Amplifier signal input pin                                       |

| 8<br>I com | V <sub>SS</sub> | _            | Device ground pin (0 V)                                          |

| 9          | /DOUT           | Output       | Output pin for amplifier input signal detector                   |

| 10         | SW2OUT          | Output       | Output pin on analog SW2 side                                    |

| 11         | SW2IN           | Input        | Input pin on analog SW2 side                                     |

| 12         | SOUT-           | Output       | Pseudo sine wave (opposite polarity of SOUT + output) output pin |

| 13         | SOUT+           | Output       | Pseudo sine wave output pin                                      |

| 14         | SW1IN           | Input        | Input pin on analog SW1 side                                     |

| 15         | SW1OUT          | Output       | Output pin on analog SW1 side                                    |

| 16         | $V_{DD}$        | _            | Device power supply pin (+5 V)                                   |

The equivalent circuit diagrams provided in the above table are given to facilitate understanding in designing the external circuitry but are not intended to accurately represent the internal circuitry.

### **Functions**

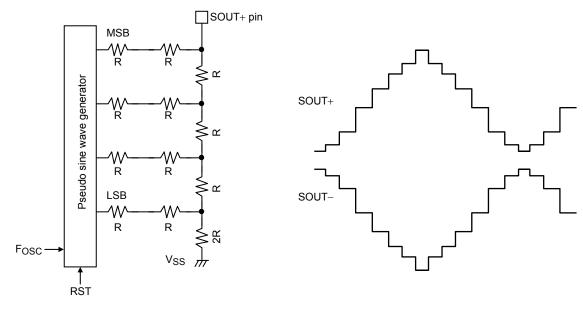

### 1. Pseudo sine wave generator and 4-bit D/A converters (transmission block)

The pseudo sine wave signal with Fosc/16 frequency is output from the pseudo sine wave output pins (SOUT+ and SOUT-).

The output polarity of SOUT+ and SOUT- are the opposite.

The transmission block (pseudo sine wave generator and 4-bit D/A converter are as shown below (SOUT+pin side):

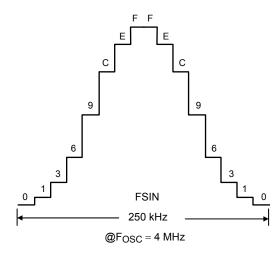

The data of the pseudo sine wave generator is output in the following sequence:  $0 \to 1 \to 3 \to 6 \to 9 \to C \to E \to F \to F \to E \to C \to 9 \to 6 \to 3 \to 1 \to 0$  (hexadecimal)

Therefore, when there is no load, the pseudo sine waveform of the positive and negative output is like a staircase (as illustrated above).

An analog switch is built-in so that the driver output buffer connects to the transmission line only during transmission.

However, an emitter follower circuit is externally connected to the driver output buffer.

The phase difference between the positive and negative output is within  $180^{\circ} \pm 5^{\circ}$  (to account for fluctuation in the pseudo sine wave output phase).

### 2. Amplifier input circuit and signal detection/non-detection circuit (reception block)

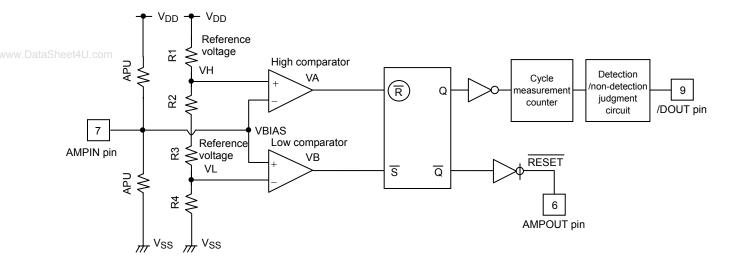

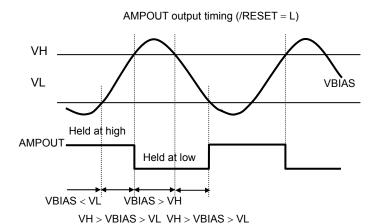

The modulation signal input block is equipped with high and a low comparator to detect only when the external sine wave signal's amplitude is above the defined threshold. In this way, signals with amplitudes lower than the specified threshold (e.g., noise signals) are prevented from being mistakenly detected as sine waves.

The detection frequency range (frequency window) is determined by the divider ratio 1/17 to 1/15 of  $F_{\rm osc}$ . Detection/non-detection confirmation conditions are such that when the signals within the specified frequency range are detected (or not detected) in succession, the signals are controlled. It takes about 9 to 15 waves (based on  $F_{\rm osc}$  1/16 frequency) to make detection/non-detection confirmation in this manner.

VH Input sensitivity Vpp

AMP IN input sine waveform

Reception detected Reception non-detected Reception non-detected Reception non-detected

|                 | VA | VB | AMPOUT |

|-----------------|----|----|--------|

| VBIAS > VH      | L  | Н  | L      |

| VH > VBIAS > VL | Н  | Н  | Hold   |

| VBIAS < VL      | Н  | L  | Н      |

**AMPOUT Truth Table**

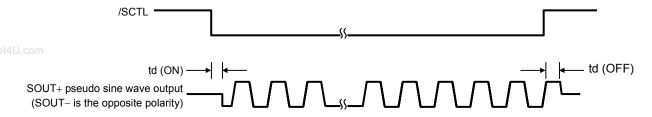

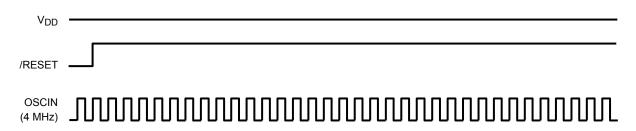

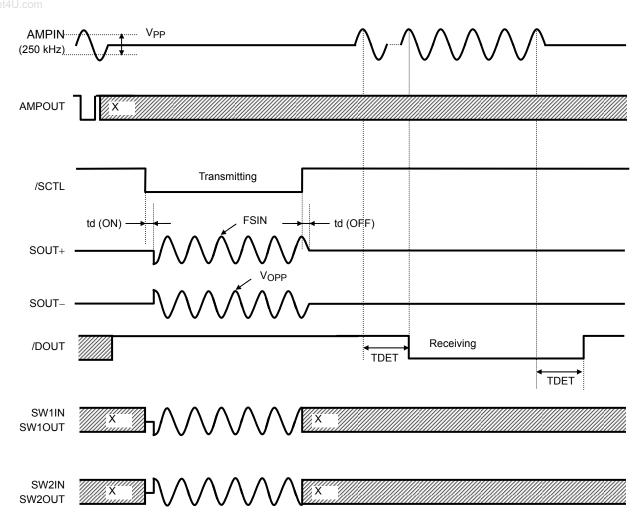

### 3. Transmission block function and timing

When the modulation control input (/SCTL) is in High-level, the pseudo sine wave output is held at 0° phase of the pseudo sine wave. When the modulation control input changes from High-level to Low-level, the pseudo sine wave output (SOUT+) initially outputs from -90° (SOUT- outputs from +90°).

The time required to turn ON in this case is as follows:

td(ON) < 500 ns

When modulation control input changes from Low-level to High-level, the phase is forcibly held at 0° (the pseudo sine wave output is stopped), regardless of the phase of the pseudo sine wave output. The time required to turn OFF in this case is as follows:

td (OFF)  $< 1 \mu s$

### 4. Reception block function and timing

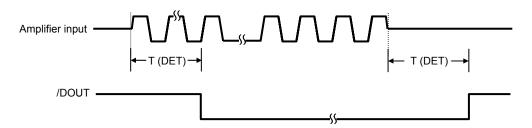

Once it is okay to receive the amplifier input signal, the time it takes for the /DOUT pin to changes from High to Low (T (DET)) is about 9 to 15 waves (based on  $F_{\rm OSC}$  1/16 frequency). This condition is only valid when the cyclic input signal within the range specified by the frequency window is detected (or not detected) in continuation.

Note 1: You are free to use any kind of communication protocol you wish, however be sure to configure a time of carrier wave × 15 waves or more for both when there are and aren't signals.

Timing Chart (SOUT+ = SW1IN, SW1OUT, SOUT- = SW2IN, SW2OUT)

## FOUT WWW. FOUT WAS A STATE OF THE STATE OF T

### Absolute Maximum Ratings (Ta = $25 \pm 1.5$ °C)

| Characteristics       | Symbol                  | Rating                   | Unit     |

|-----------------------|-------------------------|--------------------------|----------|

| Power supply voltage  | $V_{DD}$                | -0.3 to 6.0              | V        |

| Input voltage         | VI                      | $-0.3$ to $V_{DD} + 0.3$ | <b>V</b> |

| Input peak current    | IIK                     | -20 to 20                | mA       |

| Operating temperature | T <sub>opr</sub>        | -20 to 80                | °C       |

| Storage temperature   | T <sub>stg</sub>        | -55 to 125               | °C       |

| Power dissipation     | P <sub>D</sub> (Note 1) | 0.54                     | W        |

# www.DataSheet4U.comCAUTION

The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings.

Exceeding the rating(s) may cause device breakdown, damage or deterioration, and may result injury by explosion or combustion.

Note 1: Power dissipation decreases approximately 4.35 mW per degree (Centigrade).

# Electrical Characteristics (unless otherwise specified, $V_{DD}=5.0\ V,\ V_{SS}=0\ V,\ F_{OSC}=4\ MHz$ and Ta = -20 to 80°C)

| Characteristics                |                                           | Symbol          | Test<br>Circuit | Test Condition                                                                                        | Min                      | Тур.  | Max                      | Unit |  |

|--------------------------------|-------------------------------------------|-----------------|-----------------|-------------------------------------------------------------------------------------------------------|--------------------------|-------|--------------------------|------|--|

| V <sub>DD</sub> pin (pin 16    | 3)                                        |                 | •               |                                                                                                       |                          |       |                          |      |  |

| Operating volta                | ige                                       | V <sub>DD</sub> | _               |                                                                                                       | 4.5                      | 5.0   | 5.5                      | V    |  |

| Current consur                 | mption                                    | I <sub>DD</sub> | 1               | When there is no load;<br>FOSC = 4 MHz                                                                | _                        | _     | 10                       | mA   |  |

| OSCIN pin (pin                 | 1) and OSCOUT pi                          | n (pin 2)       |                 |                                                                                                       |                          |       |                          |      |  |

| Oscillation freq               | uency                                     | FOSC            | 2               |                                                                                                       | 1                        | 4     | 10                       | MHz  |  |

| Input voltage                  | High level                                | VIHOSC          | 3               |                                                                                                       | 0.7<br>V <sub>DD</sub>   |       | V <sub>DD</sub>          | V    |  |

| imput voltago                  | Low level                                 | VILOSC          | 3               |                                                                                                       | V <sub>SS</sub>          | _     | 0.3<br>V <sub>DD</sub>   | ·    |  |

| Input current                  | High level                                | IIHROSC         | 4               | VIN = 5 V, Ta = 25°C                                                                                  | 3.2                      | 6.58  | 13.2                     | μА   |  |

| input durient                  | Low level                                 | IILROSC         | 4               | VIN = 0 V, Ta = 25°C                                                                                  | -3.2                     | -6.58 | -13.2                    | μπ   |  |

| Output                         | High level                                | VOHOSC          | 3               | IOH = -0.1 mA                                                                                         | V <sub>DD</sub> – 1      |       | $V_{DD}$                 |      |  |

| voltage                        | Low level                                 | VOLOSC          | 4               | IOL = +0.1 mA                                                                                         | V <sub>SS</sub>          |       | V <sub>SS</sub><br>+ 0.6 | V    |  |

| /RESET pin (5                  | pin)                                      | _               |                 |                                                                                                       |                          |       | -                        | -    |  |

| Low to High inp                | out switching level                       | VIHRST          | 5               |                                                                                                       | 0.65<br>V <sub>DD</sub>  |       | V <sub>DD</sub>          | V    |  |

| High to Low inp                | out switching level                       | VILRST          | 5               |                                                                                                       | V <sub>SS</sub>          | l     | 0.35<br>V <sub>DD</sub>  | ٧    |  |

| High-level inpu                | t current                                 | IIHRST          | 6               | $VIN = V_{DD}$                                                                                        | -10                      | _     | 10                       | μΑ   |  |

| Pull-up resistar               | Pull-up resistance 1                      |                 | 7               | VIN = V <sub>SS</sub> , Ta = 25°C                                                                     | 9                        | 15    | 21                       | kΩ   |  |

| Pull-up resistar               | nce 2                                     | IILRRST2        | 7               | $VIN = V_{SS}$ , $Ta = -20$ to $80^{\circ}C$                                                          | 6.3                      |       | 27.3                     | kΩ   |  |

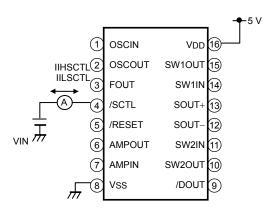

| /SCTL pin (pin                 | 4)                                        |                 | _               |                                                                                                       |                          |       |                          |      |  |

| Low to High inp                | out switching level                       | VIHSCTL         | 8               |                                                                                                       | 0.65<br>V <sub>DD</sub>  | l     | V <sub>DD</sub>          | ٧    |  |

| High to Low inp                | out switching level                       | VILSCTL         | 8               |                                                                                                       | V <sub>SS</sub>          | l     | 0.35<br>V <sub>DD</sub>  | V    |  |

| Input current                  | High level                                | IIHSCTL         | 9               | $VIN = V_{DD}$                                                                                        | -1                       | 1     | 1                        | μА   |  |

| input current                  | Low level                                 | IILSCTL         | 9               | $VIN = V_{DD}$                                                                                        | -1                       | _     | 1                        | μΑ   |  |

| FOUT pin (pin                  | 3)                                        |                 |                 |                                                                                                       |                          |       |                          |      |  |

| Output                         | High level                                | VOHFOUT         | 10              | IOH = -1.0 mA                                                                                         | V <sub>DD</sub> – 1      |       | $V_{DD}$                 |      |  |

| voltage                        | Low level                                 | VOLFOUT         | 11              | IOL = +1.0 mA                                                                                         | V <sub>SS</sub>          | _     | V <sub>SS</sub><br>+ 0.6 | V    |  |

| /DOUT pin (pin                 | 9)                                        |                 |                 |                                                                                                       | •                        |       |                          |      |  |

| Output                         | High level                                | VOHDOUT         | 12              | IOH = -1.0 mA                                                                                         | V <sub>DD</sub><br>- 1.0 |       | V <sub>DD</sub>          | V    |  |

| voltage                        | Low level                                 | VOLDOUT         | 13              | IOL = +1.0 mA                                                                                         | V <sub>SS</sub>          | _     | V <sub>SS</sub><br>+ 0.6 | v    |  |

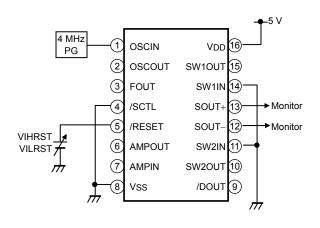

| Non-reception detection time   | Non-reception to reception detection time |                 | 19              | F <sub>OSC</sub> = 4 MHz,<br>AMPIN = 250 kHz<br>Time it takes for /DOUT to<br>change from High to Low | 40                       | _     | 60                       | μ\$  |  |

| Reception to no detection time | on-reception                              | TDET2           | 19              | FOSC = 4 MHz,<br>AMPIN = 250 kHz<br>Time it takes for /DOUT to<br>change from Low to High             | 36                       | _     | 56                       | μS   |  |

Note: The direction of current flow should be + (sink) when flowing into the IC and – (drain) when flowing out of the IC.

| Characteristics                          | Symbol            | Test<br>Circuit | Test Condition                                                                                             | Min                     | Тур. | Max             | Unit |  |  |  |

|------------------------------------------|-------------------|-----------------|------------------------------------------------------------------------------------------------------------|-------------------------|------|-----------------|------|--|--|--|

| AMPIN pin (pin 7)                        | AMPIN pin (pin 7) |                 |                                                                                                            |                         |      |                 |      |  |  |  |

| Input dynamic range                      | VAMPIN            | 14              |                                                                                                            | $V_{SS}$                | _    | $V_{DD}$        | V    |  |  |  |

| Pull-up resistance 1                     | IILRAPU1          | 15              | V <sub>IN</sub> = V <sub>SS</sub> , Ta = 25°C                                                              | 11.6                    | 19.4 | 27.2            | kΩ   |  |  |  |

| Pull-up resistance 2                     | IILRAPU2          | 15              | $V_{IN} = V_{SS}$ , Ta = -20 to 80°C                                                                       | 7                       | _    | 38              | kΩ   |  |  |  |

| Pull-down resistance 1                   | IIHRAPD1          | 16              | V <sub>IN</sub> = V <sub>DD</sub> , Ta = 25°C                                                              | 5.9                     | 9.8  | 13.7            | kΩ   |  |  |  |

| Pull-down resistance 2                   | IIHRAPD2          | 16              | $V_{IN} = V_{DD}$ , Ta = -20 to 80°C                                                                       | 3                       | _    | 19.2            | kΩ   |  |  |  |

| Amplifier input bias voltage             | VBIAS             | 17              | No load (design target)                                                                                    | 1.54                    | 1.63 | 1.71            | ٧    |  |  |  |

| Amplifier input sensitivity              | VPP               | 18              | No load, receivable amplitude<br>range is 250 kHz, when sine<br>wave signal is applied.<br>(design target) | 0.3                     | _    | 0.45            | >    |  |  |  |

| Detection frequency range                | DETON             | 19              | F <sub>OSC</sub> = 4 MHz                                                                                   | 236                     | _    | 266             | kHz  |  |  |  |

| Non-detection frequency (low frequency)  | DETOFF1           | 19              | F <sub>OSC</sub> = 4 MHz                                                                                   | _                       | _    | 236             | kHz  |  |  |  |

| Non-detection frequency (high frequency) | DETOFF2           | 19              | F <sub>OSC</sub> = 4 MHz                                                                                   | 266                     | _    | _               | kHz  |  |  |  |

| SW1IN pin (pin 14) and SW1OUT            | oin (pin 15)      |                 |                                                                                                            |                         |      |                 |      |  |  |  |

| Analog switch input voltage              | VINASW1           | —               |                                                                                                            | V <sub>SS</sub>         | _    | $V_{DD}$        | V    |  |  |  |

| Analog switch output voltage             | VOUTASW1          | —               |                                                                                                            | V <sub>SS</sub>         | _    | $V_{DD}$        | V    |  |  |  |

| OFF-leak current of analog switch 1      | IOFFASW1          | 20              | /SCTL = H, SW1IN = V <sub>DD</sub> ,<br>SW1OUT = V <sub>SS</sub>                                           | -1                      | _    | 1               | μА   |  |  |  |

| ON-resistance of analog switch 1         | RONASW1           | 21              | /SCTL = L, SW1IN = 5 V,<br>SW1OUT = 0 V<br>Current measure                                                 | 35                      | _    | 105             | Ω    |  |  |  |

| SW2IN pin (pin 11) and SW2OUT p          | pin (pin 10)      |                 |                                                                                                            |                         |      |                 |      |  |  |  |

| Analog switch input voltage              | VINASW2           | _               |                                                                                                            | V <sub>SS</sub>         | _    | $V_{DD}$        | V    |  |  |  |

| Analog switch output voltage             | VOUTASW2          | _               |                                                                                                            | V <sub>SS</sub>         | _    | $V_{DD}$        | ٧    |  |  |  |

| OFF-leak current of analog switch 2      | IOFFASW2          | 20              | /SCTL = H, SW2IN = V <sub>DD</sub> ,<br>SW2OUT = V <sub>SS</sub>                                           | -1                      | _    | 1               | μА   |  |  |  |

| ON-resistance of analog switch 2         | RONASW2           | 21              | /SCTL = L, SW2IN = 5 V,<br>SW2OUT = 0 V<br>Current measure                                                 | 35                      | _    | 105             | Ω    |  |  |  |

| SOUT+ pin (13 pin), SOUT- pin (12        | 2 pin)            |                 |                                                                                                            |                         |      |                 |      |  |  |  |

| Output voltage                           | VOPP              | 22              | Maximum voltage value when there is no load                                                                | 0.85<br>V <sub>DD</sub> | _    | V <sub>DD</sub> | V    |  |  |  |

| Pseudo sine wave output frequency        | FSIN              | 23              | F <sub>OSC</sub> = 4 MHz                                                                                   | _                       | 250  | _               | kHz  |  |  |  |

| Pseudo sine wave output start time       | tdON              | 23              | /SCTL = H → L                                                                                              | _                       | _    | 500             | ns   |  |  |  |

| Pseudo sine wave output stop time        | tdOFF             | 23              | /SCTL = L → H                                                                                              | _                       | _    | 1               | μS   |  |  |  |

| Equivalent output impedance              | ROUTSIN           | 24              | No load                                                                                                    | 2.8                     | 4    | 5.2             | kΩ   |  |  |  |

$Note: \ \ \, \text{The direction of current flow should be} + \text{(sink) when flowing into the IC and} - \text{(drain) when flowing out of the IC}.$

### **Test Circuit**

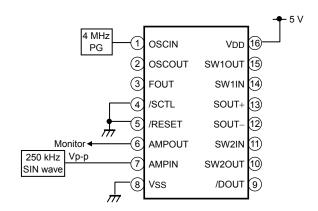

### (1) Current consumption

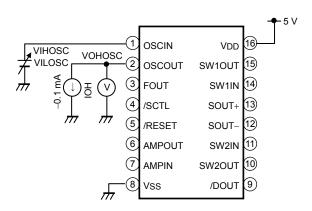

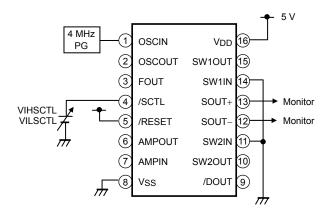

### (2) Oscillation frequency

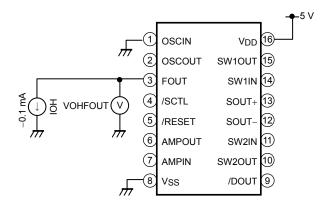

### (3) High-level input voltage Low-level input voltage High-level output voltage

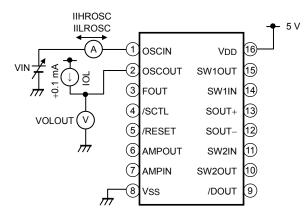

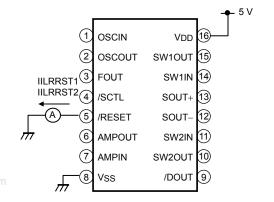

(4) High-level input current Low-level input current Low-level output voltage

(5) Low to High input switching level High to Low input switching level

(6) High-level input current

### (7) Pull-up resistance 1 Pull-up resistance 2

### (8) Low to High input switching level High to Low input switching level

## (9) High-level input current Low-level input current

### (10) High-level output voltage

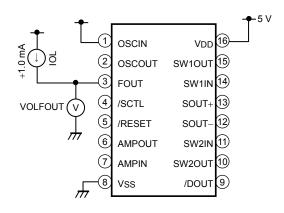

### (11) Low-level output voltage

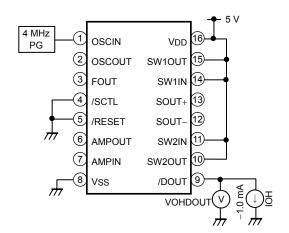

### (12) High-level output voltage

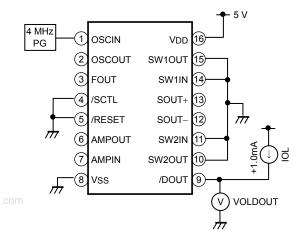

### (13) Low-level output voltage

### (14) Input dynamic range

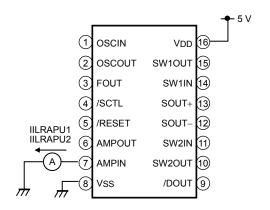

### (15) Pull-up resistance 1 Pull-up resistance 2

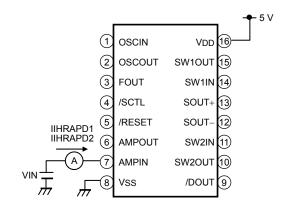

## (16) Pull-down resistance 1 Pull-down resistance 2

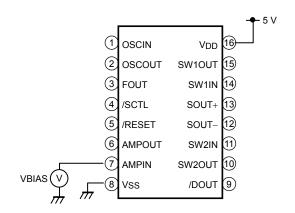

### (17) Amplifier input bias voltage

### (18) Amplifier input sensitivity

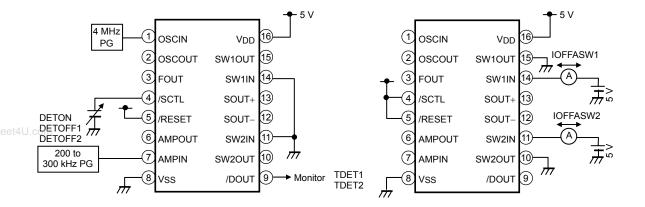

# (19) Detection frequency range Non-detection frequency (low frequency) Non-detection frequency (high frequency) Non-reception to reception detection time Reception to non-reception detection time

## (20) OFF-leak current of analog switch 1 OFF-leak current of analog switch 2

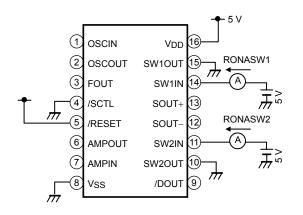

## (21) ON-resistance of analog switch 1 ON-resistance of analog switch 2

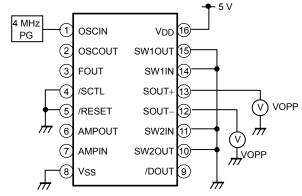

### (22) Output voltage

### (23) Pseudo sine wave output frequency Pseudo sine wave output start time Pseudo sine wave output stop time

### (24) Equivalent output impedance

### **IC Marking Specification**

www.DataSheet4II.com

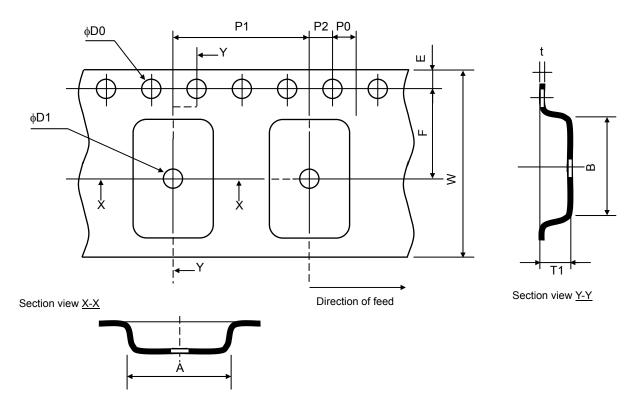

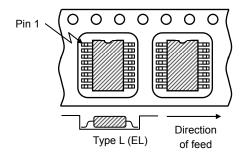

### **Toshiba CMOS SOP Embossed Taping - Common Specifications**

### 1. Applicable Scope

This specification defines the embossed taping package specifications and related items for Toshiba flat package CMOS ICs. As a rule, these taping specifications comply with JEITA (RC-1009B) and EIA (EIA481).

### 2. Specifications

### 2.1 Tape Form and Dimensions

| Package                           | JEITA Tape Standard |

|-----------------------------------|---------------------|

| 300 mm 14, 16 pin (JEITA Type II) | TE1612              |

| 300 mm 20 pin (JEITA Type II)     | TE2412              |

ww.DataSheet4U.com

|                    |              |               |               |               |               |               |              |              |                     |              | Į.           | Jnit: mm      |

|--------------------|--------------|---------------|---------------|---------------|---------------|---------------|--------------|--------------|---------------------|--------------|--------------|---------------|

|                    | А            | В             | W             | F             | E             | P1            | P2           | P0           | φD0                 | t            | T1           | φD1           |

| 14, 16<br>pin type | 8.5<br>± 0.2 | 10.8<br>± 0.2 | 16.0<br>± 0.3 | 7.5<br>± 0.1  | 1.75<br>± 0.1 | 12.0<br>± 0.1 | 2.0<br>± 0.1 | 4.0<br>± 0.1 | 1.5<br>+ 0.1<br>- 0 | 0.3<br>± 0.1 | 2.1<br>± 0.2 | 1.65<br>± 0.1 |

| 20                 | 8.3          | 13.2          | 24.0          | 11.5<br>+ 0.1 | 1.75<br>+ 0.1 | 12.0          | 2.0          | 4.0          | 1.5<br>+ 0.1        | 0.3          | 2.2          | 2.0           |

Note 1: The tape surface resistance shall be  $10^6 \Omega$ /cm or less.

Note 2: The accumulated error tolerance for the feed hole pitch (P0) shall be  $\leq \pm 0.2$  mm per 10 pitches.

### 2.2 Seal Tape Dimensions

|                |            | Unit: mm       |

|----------------|------------|----------------|

|                | Tape Width | Tape Thickness |

| 14,16 pin type | 13.5       | 0.06           |

| 20 pin type    | 21.5       | 0.06           |

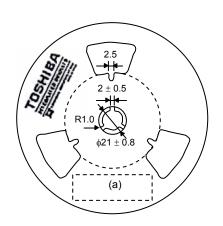

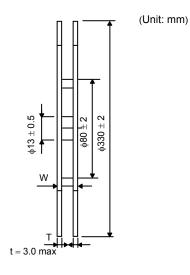

### 2.3 Reel Form and Dimensions

ww.DataSheet4U.com

|             |           | Unit: mm                             |

|-------------|-----------|--------------------------------------|

| W dimension | 14,16 pin | 16.4 <sup>+</sup> 2.0 <sub>-</sub> 0 |

| w dimension | 20 pin    | 24.4 + 2.0 - 0                       |

(a) Bar code label (See page 18)

### 2.4 Insertion Direction

### 2.5 Tape Minimum Bending Radius

The strength of the seal tape shall not change even when an IC is inserted into the tape and the tape is bent 40 mm. In addition, the tape and inserted IC shall not change under the corresponding conditions.

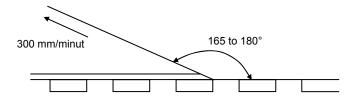

### 2.6 Seal Tape Peeling Strength

The seal tape shall maintain a peeling strength of  $0.1~\mathrm{N}$  (10 gf) when tape bonding surface is at 165 to 180° and being pulled at a speed of 300 mm per minute. However, the seal tape shall not fracture or break when it is being peeled.

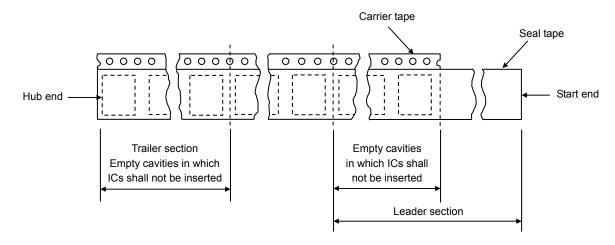

### 2.7 Leader and Trailer Sections of the Tape

Empty cavities shall be created in leader and trailer sections of the tape in which ICs shall not be inserted as specified below:

|                 | Seal Tape         | Carrier Tape      |

|-----------------|-------------------|-------------------|

| Leader section  | Minimum of 500 mm | Minimum of 400 mm |

| Trailer section | Minimum of 400 mm | Minimum of 400 mm |

### 2.8 IC Insertion Failure Ratio

| ltem                              | Tolerated Ratio          | Comments                                                                               |  |

|-----------------------------------|--------------------------|----------------------------------------------------------------------------------------|--|

| Consecutive insertion failure     | None                     | Does not apply to the empty cavities in the leading and trailing sections of the tape. |  |

| Non-consecutive insertion failure | 0.1 % or less (per reel) |                                                                                        |  |

### 3. Standard Packaging Unit

The standard packaging unit for one reel of tape shall be 2000 units.

### 4. Labeling

The reel shall be labeled with the following:

- 1) Product Name

- 2) Quantity

- 3) Lot No.

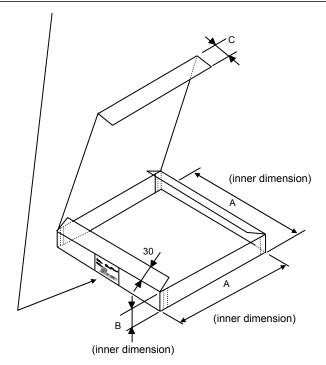

### 5. Boxing

Each completed reel of tape shall be boxed in a cardboard box (one per box). The box shall also be labeled with the same labeling information as the reel (see above).

ww.DataSheet4U.com

| Dimensions      | Unit: mm |    |    |

|-----------------|----------|----|----|

|                 | Α        | В  | С  |

| 14, 16 pin type | 340      | 25 | 27 |

| 20 pin type     | 340      | 33 | 35 |

Bar code label

### 6. Issuing Purchase Orders

When issuing IC purchase orders using the taping packaging information, be sure to include the product name, taping type, insertion direction and quantity as follows:

### Example:

ww DataSheet4U com

### 7. Delivery and Storage Precautions

Tape reels should be delivered with enough care so as to prevent extreme vibration from impacting the product. Tape reels should be kept out of direct sunlight and be kept below 45°C during delivery and storage so as to prevent wearing down the peeling strength of seal tape and/or causing other deformities to the tape.

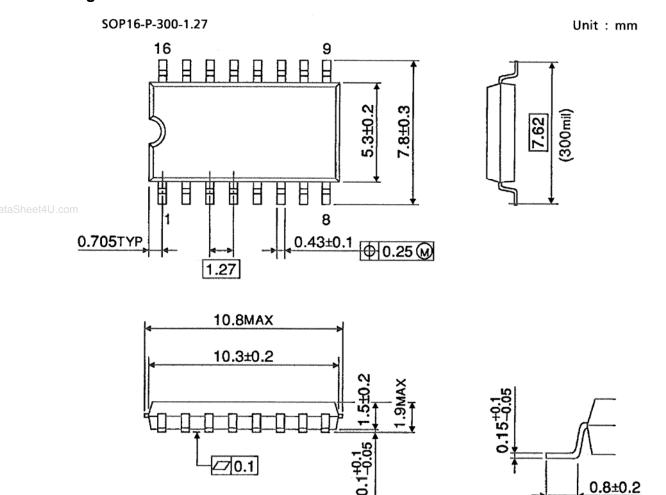

### **Package Dimensions**

Weight: 0.16 g (typ.)

About solderability, following conditions were confirmed

- Solderability

- (1) Use of Sn-37Pb solder Bath

- solder bath temperature = 230°C

- · dipping time = 5 seconds

- 4U.com · the number of times = once

- · use of R-type flux

- (2) Use of Sn-3.0Ag-0.5Cu solder Bath

- · solder bath temperature = 245°C

- · dipping time = 5 seconds

- · the number of times = once

- · use of R-type flux

### **RESTRICTIONS ON PRODUCT USE**

070711EBA

- The information contained herein is subject to change without notice.

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor

devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical

stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety

in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such

TOSHIBA products could cause loss of human life, bodily injury or damage to property.

- In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are designed and manufactured for usage in hot water dispensers.

Do not use any of these products for any purposes other than hot water dispensers, unless otherwise agreed in writing by TOSHIBA.

- The products described in this document shall not be used or embedded to any downstream products of which manufacture, use and/or sale are prohibited under any applicable laws and regulations.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility

is assumed by TOSHIBA for any infringements of patents or other rights of the third parties which may result from

its use. No license is granted by implication or otherwise under any patents or other rights of TOSHIBA or the third

parties.

- Please use this product in compliance with all applicable laws and regulations that regulate the inclusion or use of

controlled substances. Toshiba assumes no liability for damage or losses occurring as a result of noncompliance

with applicable laws and regulations.

- The products described in this document are subject to foreign exchange and foreign trade control laws.