## TC35661SBG/DBG-203 Bluetooth<sup>®</sup> IC ROM Profile Series

## Rev. 1.0

The Bluetooth<sup>®</sup> word mark and logos are registered trademarks owned by Bluetooth SIG, Inc. ARM is a registered trademark of ARM Limited (or its subsidiaries) in the EU and/or elsewhere. All rights reserved.

#### Data sheet composition

This data sheet consists of two parts describing the firmware and the hardware.

The chapter of the firmware describes the functions of the firmware built in the ROM of the IC.

The chapter of the hardware describes the functions of the hardware. Some functions are not supported by the firmware depending on ROM versions. Please refer to the chapter of the firmware for details.

## Firmware data sheet

## TC35661-203 Bluetooth<sup>®</sup> IC ROM Profile Series

# SPP Rev 1.02

#### Contents

| Firmwa | are data sheet                              | 3  |

|--------|---------------------------------------------|----|

| 1.     | General Description                         | 5  |

|        | Product Concept                             |    |

| 1.2.   | Features                                    | 5  |

| 1.3.   | Bluetooth <sup>®</sup> Support Feature List | 6  |

| 2.     | Pin Function                                | 7  |

| 2.1    | Pin Functions                               | 7  |

| 2.2    | System Configuration Example                | 10 |

|        |                                             |    |

#### 1. General Description

#### 1.1. Product Concept

TC35661 is the 1-chip CMOS IC for Bluetooth<sup>®</sup> communication, which includes an RF analog part and a Baseband digital part. Each supported function depends on ROM version. TC35661-203 is TC35661 with ROM version 203. It supports SPP (Serial Port Profile).

#### 1.2. Features

$\geq$

$\triangleright$

- SPP (Serial Port Profile)

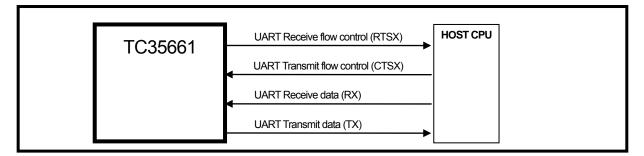

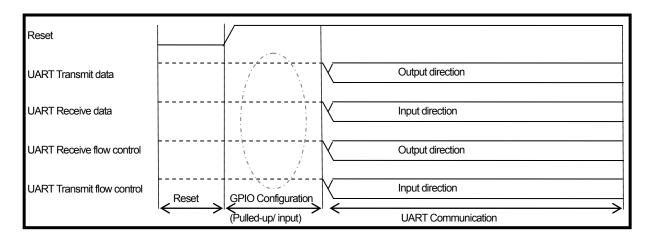

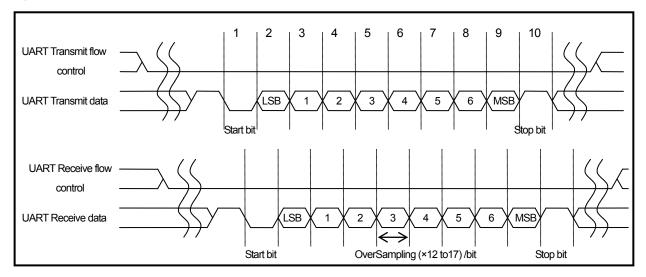

- > UART as Host CPU Interface

- ♦ Baud rate from 2400 bps to 3.25 Mbps (Default 115200 bps)

- ♦ 4-wire

- EEPROM control

- $\diamond$  I<sup>2</sup>C interface

- API for General Purpose I/O (GPIO) control

- ♦ 19 ports (with pull-up and pull-down resistors)

- API for Wake-up Interface

- ♦ Wake-up input

- ♦ Wake-up status output

- ♦ Host wake-up output

- API for Low power mode

- ♦ Sleep function

- ♦ Wake up by UART command

- ♦ Wake up by GPIO0 input

- ♦ Selectable source of the sleep clock 32.768 kHz (External input or Clock divided from 26 MHz)

- Synchronization signal output

- ♦ For LED blinking function

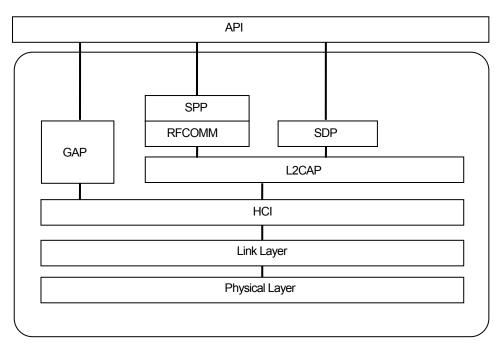

Figure 1-1 Diagram of Bluetooth® Stack in TC35661-203

#### 1.3. Bluetooth<sup>®</sup> Support Feature List

#### Table 1-1 Support Feature List

| Items                       | Description                             | Status                                                 |

|-----------------------------|-----------------------------------------|--------------------------------------------------------|

| Bluetooth <sup>®</sup> Core | Version                                 | 4.2                                                    |

|                             | Power Class                             | 2                                                      |

|                             | Basic Rate (BR)                         | Supported                                              |

|                             | Bluetooth <sup>®</sup> low energy (LE)  | Not Supported                                          |

|                             | High Speed (HS)                         | Not Supported                                          |

| Feature                     | Sniff                                   | Supported                                              |

|                             | Park/Hold                               | Not Supported                                          |

|                             | BR- 3slot packet                        | Supported                                              |

|                             | BR- 5slot packet                        | Supported                                              |

|                             | EDR                                     | Supported                                              |

|                             | Extended Inquiry Response               | Not Supported                                          |

|                             | Interlaced Inquiry/Page Scan            | Not Supported                                          |

|                             | Read RSSI                               | Supported                                              |

|                             | Secure Simple Pairing                   | Supported                                              |

|                             | Power Control                           | Supported                                              |

|                             | Enhanced Power Control                  | Not Supported                                          |

|                             | AFH                                     | Supported                                              |

|                             | SCO/eSCO                                | Not Supported                                          |

|                             | CQDDR                                   | Not Supported                                          |

|                             | Sniff subrating                         | Supported                                              |

|                             | SPP                                     | Supported (Initiator and Acceptor)                     |

|                             | SPP UUID Assignment                     | Supported                                              |

|                             | Multi Profile / Multi point connection  | Not supported                                          |

| Bluetooth <sup>®</sup> Dual | BR Page/Inquiry scan and LE Advertising | Not Supported                                          |

| mode                        | simultaneously                          |                                                        |

|                             | SPP+GATT connection establishment       | Not Supported                                          |

|                             | simultaneously                          |                                                        |

| Interface                   | UART Baudrate                           | 115200 bps (default). Selected by command.             |

|                             | UART Protocol                           | UART Transport Layer (Core 4.2 Transport Layer Part A) |

|                             | Multi Profile/point                     | Not supported                                          |

|                             | USB                                     | Not Supported                                          |

|                             | PCM                                     | Not Supported                                          |

|                             | WIFI Co-Ex                              | Not Supported                                          |

#### 2. Pin Function

#### 2.1 Pin Functions

Table 2-1 shows an attribute and the state of input or output at operation for each pin, and the function description.

| Pin name | Pin No. | Attribute         | Condition               | Functional description                              |

|----------|---------|-------------------|-------------------------|-----------------------------------------------------|

|          |         | VDD category      | Default configuration   |                                                     |

|          |         | Direction         | -                       |                                                     |

|          |         | Туре              |                         |                                                     |

|          |         |                   | General purpose I/O po  | ort                                                 |

| GPIO0    | C7      | DVDDA             | IN (Neither pull-up nor | General purpose I/O pin 0 (Wake-Up Input)           |

|          |         | IN/OUT            | pull-down resistor)     | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down |                         | command, this pin is able to operate as Wake-Up     |

|          |         | Schmitt trigger   |                         | input pin.                                          |

|          |         | 1, 2, and 4 mA    |                         | If not used for this function, this pin needs to be |

|          |         |                   |                         | pulled down by 100 k $\Omega$ .                     |

| GPIO1    | A4      | DVDDA             | OUT                     | General Purpose I/O pin 1 (Wake-up Status           |

|          |         | IN/OUT            |                         | Output)                                             |

|          |         | Pull-up/Pull-down |                         | After the boot-up, this pin is assigned to the      |

|          |         | Schmitt trigger   |                         | Wake-up Status output pin automatically.            |

|          |         | 1, 2, and 4 mA    |                         | L output: Active mode                               |

|          |         |                   |                         | H output: Sleep mode                                |

|          |         |                   |                         | If not used for this function, this pin needs to be |

|          |         |                   |                         | kept open.                                          |

| GPIO2    | H8      | DVDDB             | IN (Pull-up)            | General Purpose I/O pin 2 (LED Blinking Output)     |

|          |         | IN/OUT            |                         | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down |                         | command, this pin is able to operate as LED         |

|          |         | Schmitt trigger   |                         | Blinking output pin.                                |

|          |         | 1, 2, and 4 mA    |                         | If not used for this function, this pin needs to be |

|          |         |                   |                         | kept open.                                          |

| GPIO3    | G8      | DVDDB             | IN (Pull-up)            | General Purpose I/O pin 3 (LED Blinking Output)     |

|          |         | IN/OUT            |                         | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down |                         | command, this pin is able to operate as LED         |

|          |         | Schmitt trigger   |                         | Blinking output pin.                                |

|          |         | 1, 2, and 4 mA    |                         | If not used for this function, this pin needs to be |

|          |         |                   |                         | kept open.                                          |

| GPIO4    | G7      | DVDDB             | IN (Pull-up)            | General Purpose I/O pin 4 (Request Wake-Up          |

|          |         | IN/OUT            |                         | output for Host CPU)                                |

|          |         | Pull-up/Pull-down |                         | After the pin configuration done by the UART        |

|          |         | Schmitt trigger   |                         | command, this pin is able to operate as Request     |

|          |         | 1, 2, and 4 mA    |                         | Wake-up output port for Host CPU.                   |

|          |         |                   |                         | If not used for this function, this pin needs to be |

|          |         |                   |                         | kept open.                                          |

#### Table 2-1 Pin Functions

| Pin name | Pin No. | Attribute                         | Condition               | Functional description                              |

|----------|---------|-----------------------------------|-------------------------|-----------------------------------------------------|

|          |         | VDD category                      | Default configuration   |                                                     |

|          |         | Direction                         |                         |                                                     |

|          |         | Туре                              |                         |                                                     |

| GPIO5    | G6      | DVDDB                             | IN (Pull-up)            | General Purpose I/O pin 5                           |

|          |         | IN/OUT                            |                         | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down                 |                         | command, this pin is able to operate as a           |

|          |         | Schmitt trigger                   |                         | general-purpose input and output port.              |

|          |         | 1, 2, and 4 mA                    |                         | If not used for this function, this pin needs to be |

|          |         |                                   |                         | kept open.                                          |

| GPIO6    | E7      | DVDDA                             | OUT                     | General Purpose I/O pin 6 (UART-TX port)            |

|          |         | IN/OUT                            |                         | After the boot-up, this pin is assigned to the      |

|          |         | Pull-up/Pull-down                 |                         | UART-TX output pin automatically.                   |

|          |         | Schmitt trigger                   |                         |                                                     |

|          |         | 1, 2, and 4 mA                    |                         |                                                     |

| GPIO7    | F8      | DVDDA                             | IN (Neither pull-up nor | General Purpose I/O pin 7 (UART-RX port)            |

|          |         | IN/OUT                            | pull-down resistor)     | After the boot-up, this pin is assigned to the      |

|          |         | Pull-up/Pull-down                 |                         | UART-RX input pin automatically.                    |

|          |         | Schmitt trigger                   |                         |                                                     |

|          |         | 1, 2, and 4 mA                    |                         |                                                     |

| GPIO8    | F7      | DVDDA                             | OUT                     | General Purpose I/O pin 8 (UART-RTSX port)          |

|          |         | IN/OUT                            |                         | After the boot-up, this pin is assigned to the UART |

|          |         | Pull-up/Pull-down                 |                         | -RTSX (Request to send) output pin automatically.   |

|          |         | Schmitt trigger                   |                         |                                                     |

|          |         | 1, 2, and 4 mA                    |                         |                                                     |

| GPIO9    | D7      | DVDDA                             | IN (Neither pull-up nor | General Purpose I/O pin 9 (UART-CTSX port)          |

|          |         | IN/OUT                            | pull-down resistor)     | After the boot-up this pin is assigned to the UART  |

|          |         | Pull-up/Pull-down                 |                         | -CTSX (Clear to send) input pin automatically.      |

|          |         | Schmitt trigger                   |                         |                                                     |

| 0710/0   |         | 1, 2, and 4 mA                    |                         |                                                     |

| GPIO10   | B2      | DVDDA                             | IN (Pull-up)            | General Purpose I/O pin 10                          |

|          |         | IN/OUT                            |                         | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down                 |                         | command, this pin is able to operate as a           |

|          |         | Schmitt trigger                   |                         | general-purpose input and output port.              |

|          |         | 1, 2, and 4 mA                    |                         | If not used for this function, this pin needs to be |

|          | 40      |                                   |                         | kept open.                                          |

| GPIO11   | A2      |                                   | IN (Pull-up)            | General Purpose I/O pin 11                          |

|          |         |                                   |                         | After the pin configuration done by the UART        |

|          |         | Pull-up/Pull-down                 |                         | command, this pin is able to operate as a           |

|          |         | Schmitt trigger<br>1, 2, and 4 mA |                         | general-purpose input and output port.              |

|          |         | 1, 2, diu 4 mA                    |                         | If not used for this function, this pin needs to be |

| GPIO12   | C6      | DVDDA                             | IN (Pull-up)            | kept open.<br>General Purpose I/O pin 12            |

|          | 0       | IN/OUT                            | 114 (Full-up)           |                                                     |

|          |         | Pull-up/Pull-down                 |                         | After the pin configuration done by the UART        |

|          |         | Schmitt trigger                   |                         | command, this pin is able to operate as a           |

|          |         | 1, 2, and 4 mA                    |                         | general-purpose input and output port.              |

|          |         | 1, 2, and 4 mA                    |                         | If not used for this function, this pin needs to be |

|          |         |                                   |                         | kept open.                                          |

| Pin name | Pin No. | Attribute         | Condition             | Functional description                                        |

|----------|---------|-------------------|-----------------------|---------------------------------------------------------------|

|          |         | VDD category      | Default configuration |                                                               |

|          |         | Direction         |                       |                                                               |

|          |         | Туре              |                       |                                                               |

| GPIO13   | D8      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 13                                    |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin is able to operate as a                     |

|          |         | Schmitt trigger   |                       | general-purpose input and output port.                        |

|          |         | 1, 2, and 4 mA    |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

| GPIO14   | B6      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 14 (I <sup>2</sup> C SCL port)        |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin changes to SCL signal pin for               |

|          |         | Schmitt trigger   |                       | the serial memory interface. I <sup>2</sup> C can be selected |

|          |         | 1, 2, and 4 mA    |                       | for the serial memory interface.                              |

|          |         |                   |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

| GPIO15   | B5      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 15 (I <sup>2</sup> C SDA port)        |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin changes to SDA signal pin for               |

|          |         | Schmitt trigger   |                       | the serial memory interface. I <sup>2</sup> C can be selected |

|          |         | 1, 2, and 4 mA    |                       | for the serial memory interface.                              |

|          |         |                   |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

| GPIO16   | A5      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 16                                    |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin is able to operate as a                     |

|          |         | Schmitt trigger   |                       | general-purpose input and output port.                        |

|          |         | 1, 2, and 4 mA    |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

| GPIO17   | A3      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 17                                    |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin is able to operate as a                     |

|          |         | Schmitt trigger   |                       | general-purpose input and output port.                        |

|          |         | 1, 2, and 4 mA    |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

| GPIO18   | B4      | DVDDA             | IN (Pull-up)          | General Purpose I/O pin 18                                    |

|          |         | IN/OUT            |                       | After the pin configuration done by the UART                  |

|          |         | Pull-up/Pull-down |                       | command, this pin is able to operate as a                     |

|          |         | Schmitt trigger   |                       | general-purpose input and output port.                        |

|          |         | 1, 2, and 4 mA    |                       | If not used for this function, this pin needs to be           |

|          |         |                   |                       | kept open.                                                    |

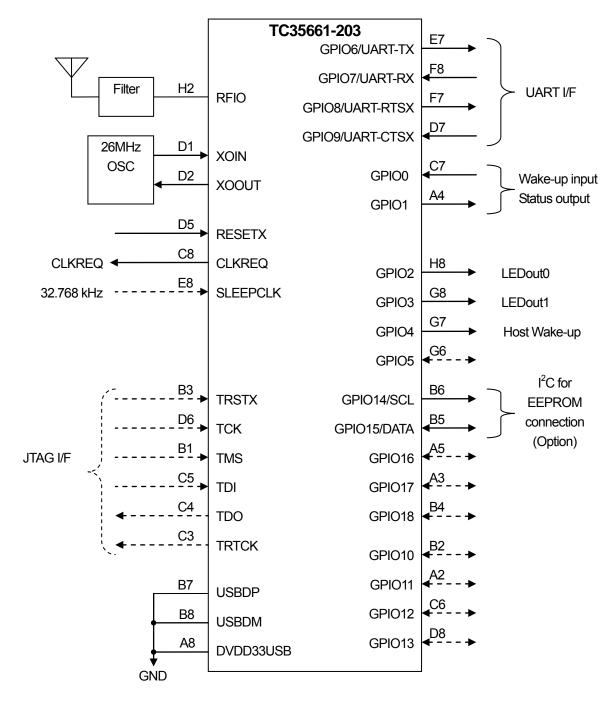

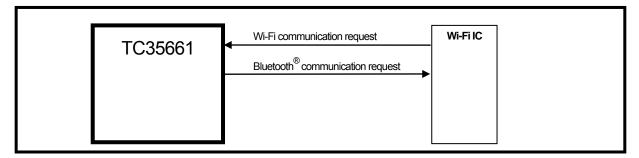

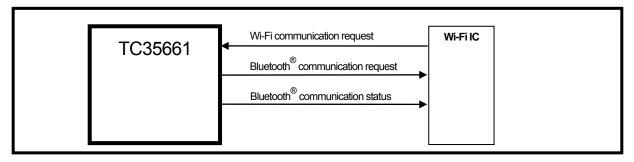

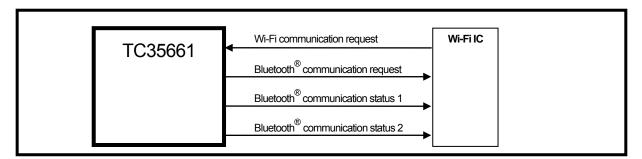

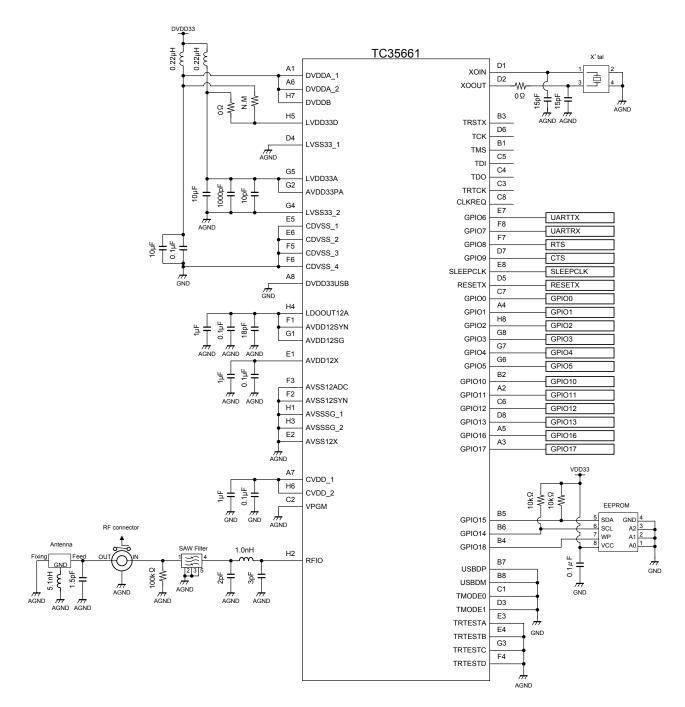

#### 2.2 System Configuration Example

This Figure 2-1 shows an example of system configuration.

Figure 2-1 TC35661-203 System Configuration Example

## Hardware data sheet

## TC35661SBG/DBG HW1 Bluetooth<sup>®</sup> IC ROM Profile Series

## **Rev 1.19**

#### Contents

| Hardware of | re data sheet11                                                                 |  |  |  |  |  |  |  |  |

|-------------|---------------------------------------------------------------------------------|--|--|--|--|--|--|--|--|

| 1. Ger      | neral Description14                                                             |  |  |  |  |  |  |  |  |

| 1.1.        | Product Concept                                                                 |  |  |  |  |  |  |  |  |

| 1.2.        | Features                                                                        |  |  |  |  |  |  |  |  |

| 1.3.        | Ordering Information                                                            |  |  |  |  |  |  |  |  |

| 2. Pin      | in Function                                                                     |  |  |  |  |  |  |  |  |

| 2.1.        | Pin Assignment                                                                  |  |  |  |  |  |  |  |  |

| 2.2.        | Pin Functions                                                                   |  |  |  |  |  |  |  |  |

| 2.2.1.      | Power Supply Pins                                                               |  |  |  |  |  |  |  |  |

| 3. Sys      | tem Configuration                                                               |  |  |  |  |  |  |  |  |

| 3.1.        | Block Diagram                                                                   |  |  |  |  |  |  |  |  |

| 4. Har      | dware Interface                                                                 |  |  |  |  |  |  |  |  |

| 4.1.        | Reset Interface (Power Supply Sequence)                                         |  |  |  |  |  |  |  |  |

| 4.1.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

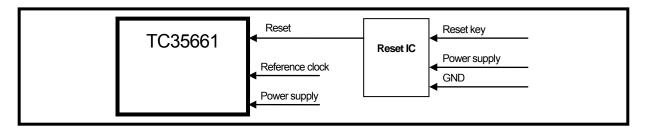

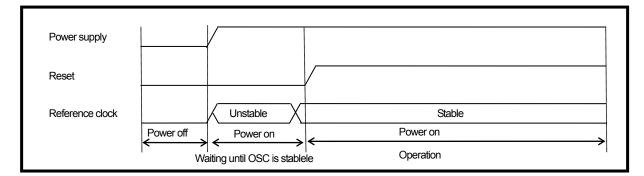

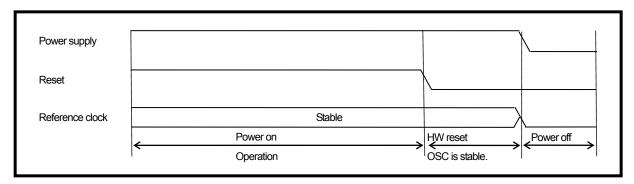

| 4.1.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

| 4.2.        | UART Interface                                                                  |  |  |  |  |  |  |  |  |

| 4.2.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

| 4.2.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

| 4.2.3.      | Frame Format                                                                    |  |  |  |  |  |  |  |  |

| 4.2.4.      | Flow Control Function                                                           |  |  |  |  |  |  |  |  |

| 4.2.5.      | UART Baud Rate Setting                                                          |  |  |  |  |  |  |  |  |

| 4.2.6.      | Error Detection Function                                                        |  |  |  |  |  |  |  |  |

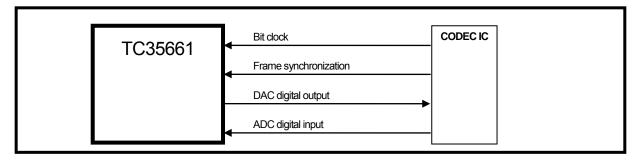

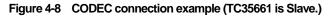

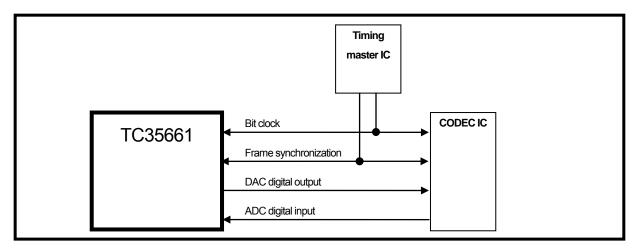

| 4.3.        | Audio CODEC Digital Interface                                                   |  |  |  |  |  |  |  |  |

| 4.3.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

| 4.3.2.      | Connection Examples                                                             |  |  |  |  |  |  |  |  |

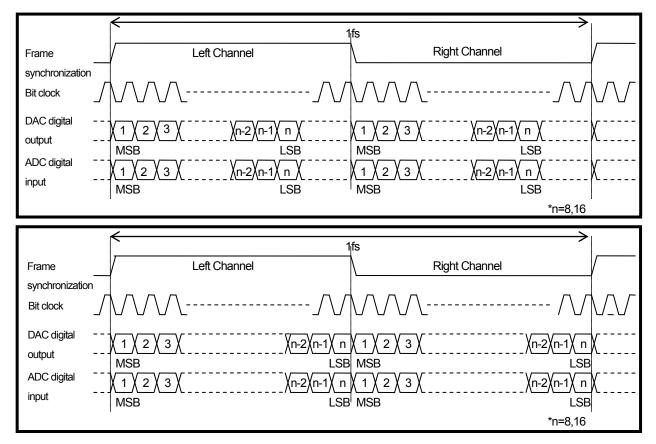

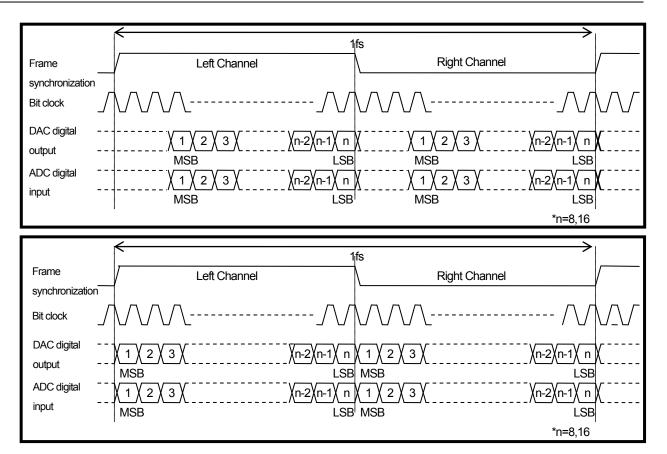

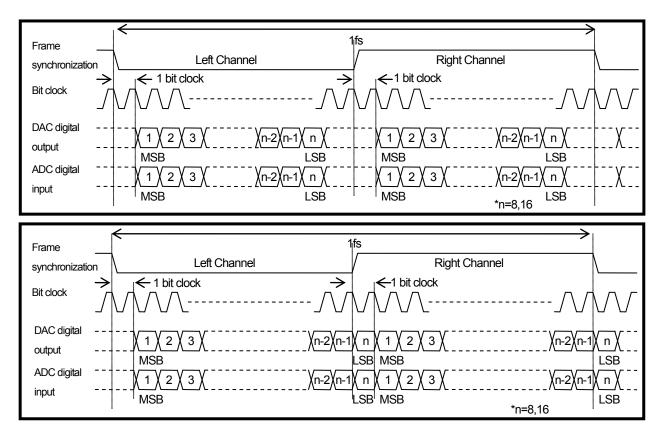

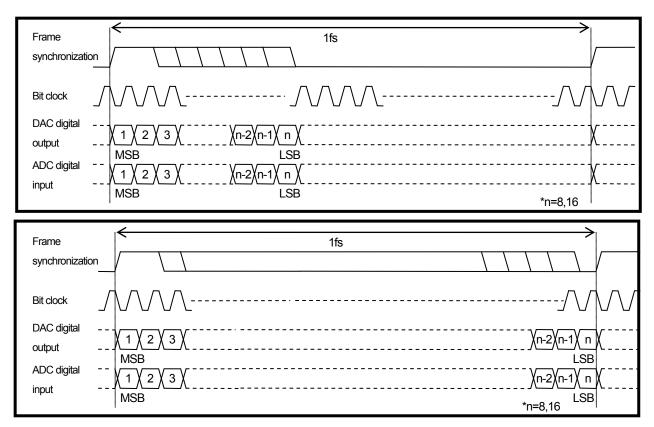

| 4.3.3.      | Frame Format                                                                    |  |  |  |  |  |  |  |  |

| 4.3.4.      | Programmable Polarity Changing                                                  |  |  |  |  |  |  |  |  |

| 4.3.5.      | Bit Clock Frequency in Master Mode                                              |  |  |  |  |  |  |  |  |

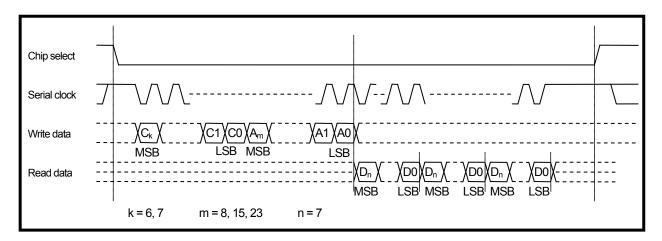

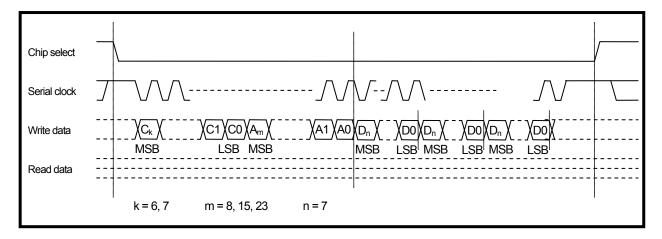

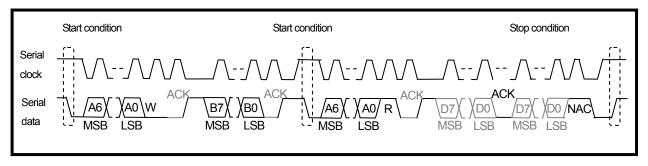

| 4.4.        | Serial Memory Interface                                                         |  |  |  |  |  |  |  |  |

| 4.4.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

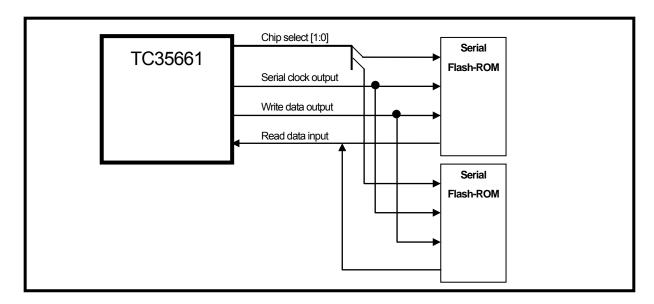

| 4.4.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

| 4.4.3.      | Selection of External Pull-up Resistor Value for I <sup>2</sup> C Bus Interface |  |  |  |  |  |  |  |  |

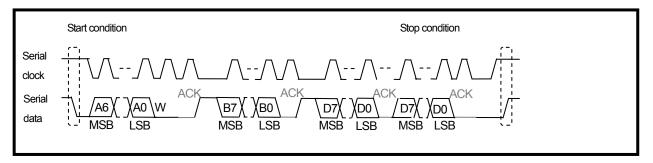

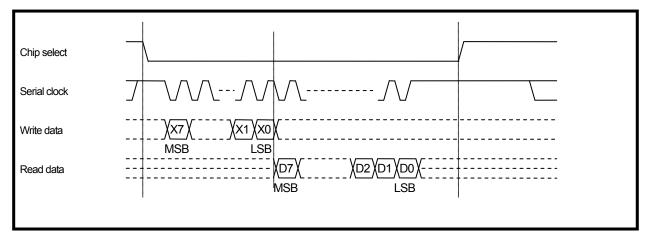

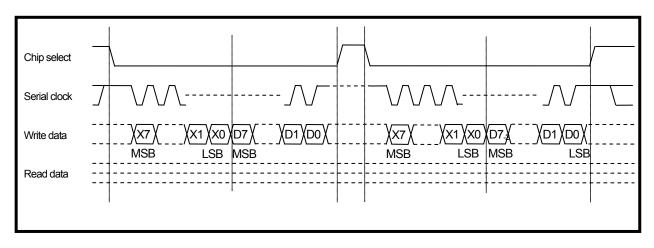

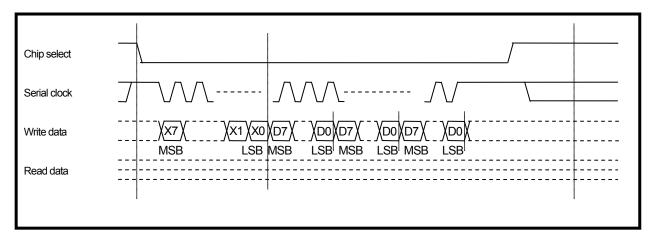

| 4.4.4.      | Frame Format                                                                    |  |  |  |  |  |  |  |  |

| 4.5.        | Wi-Fi Co-existence Interface                                                    |  |  |  |  |  |  |  |  |

| 4.5.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

| 4.5.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

| 4.6.        | Reference Clock Interface                                                       |  |  |  |  |  |  |  |  |

| 4.6.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

| 4.6.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

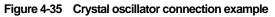

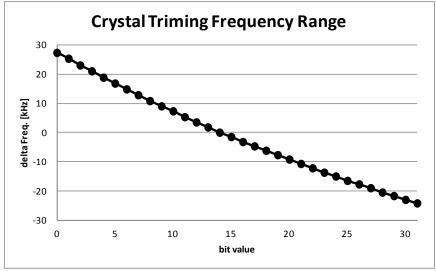

| 4.6.3.      | Fine Tuning Function for Crystal Oscillator                                     |  |  |  |  |  |  |  |  |

| 4.7.        | JTAG Interface                                                                  |  |  |  |  |  |  |  |  |

| 4.7.1.      | Features                                                                        |  |  |  |  |  |  |  |  |

| 4.7.2.      | Connection Example                                                              |  |  |  |  |  |  |  |  |

| 5. Elec     | 5. Electrical Characteristics                                                   |  |  |  |  |  |  |  |  |

| 5.1.        | Absolute Maximum Ratings                                                        |  |  |  |  |  |  |  |  |

| 5.2.        | Operation Condition                                                             |  |  |  |  |  |  |  |  |

| 5.3.        | DC Characteristics                                                              |  |  |  |  |  |  |  |  |

| 5.3.1.   |                                    |    |  |  |  |  |

|----------|------------------------------------|----|--|--|--|--|

| 5.4.     | Internal Regulator Characteristics |    |  |  |  |  |

| 5.5.     | RF Characteristics                 | 51 |  |  |  |  |

| 5.5.1.   | Basic Rate                         |    |  |  |  |  |

| 5.5.2.   | Enhanced Data Rate                 |    |  |  |  |  |

| 5.5.3.   | Bluetooth <sup>®</sup> Low Energy  |    |  |  |  |  |

| 5.6.     | AC Characteristics                 |    |  |  |  |  |

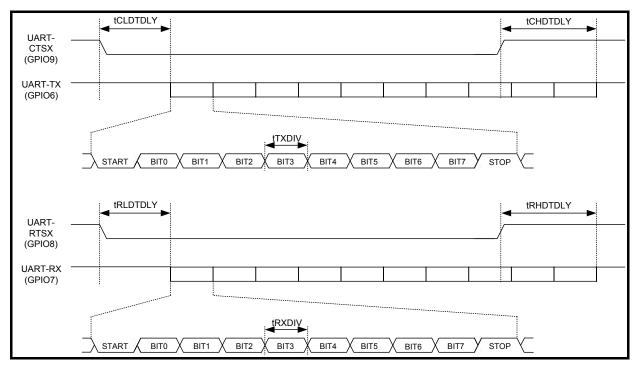

| 5.6.1.   | UART Interface                     |    |  |  |  |  |

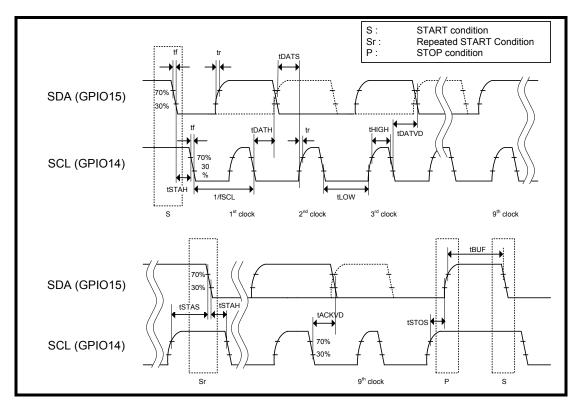

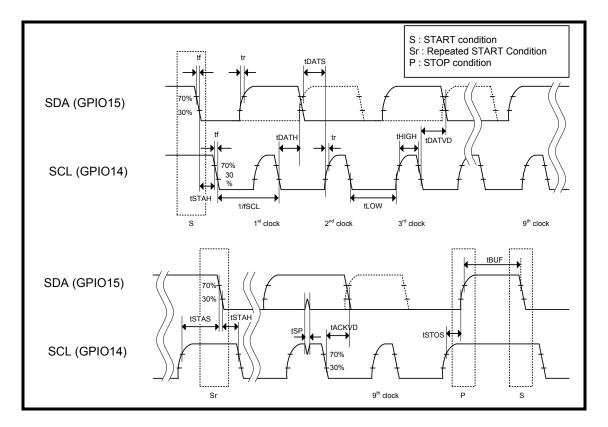

| 5.6.2.   | I <sup>2</sup> C Interface         |    |  |  |  |  |

| 6. Sys   | tem Configuration Example          |    |  |  |  |  |

| 6.1.     | System Configuration Example       |    |  |  |  |  |

| 6.2.     | Application Circuit Example        |    |  |  |  |  |

| 7. Pac   | kage                               |    |  |  |  |  |

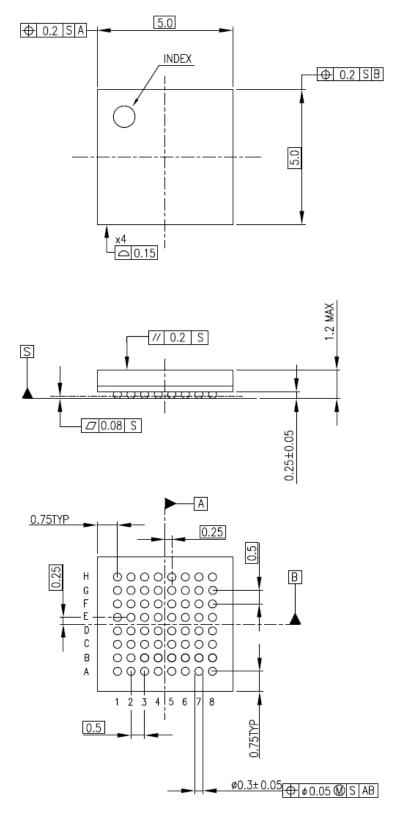

| 7.1.     | TC35661SBG Package Outline         | 61 |  |  |  |  |

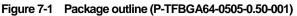

| 7.2.     | TC35661DBG Package Outline         |    |  |  |  |  |

| RESTRICT | IONS ON PRODUCT USE                |    |  |  |  |  |

#### 1. General Description

#### 1.1. Product Concept

TC35661 is a 1-chip CMOS IC for Bluetooth<sup>®</sup> communication. Each supported function depends on ROM version. Please see the firmware data sheet.

#### 1.2. Features

Each supported function depends on ROM version. Please see the firmware data sheet.

- Compliant with Bluetooth<sup>®</sup> specification

- Built-in Bluetooth<sup>®</sup> baseband digital core Built-in Bluetooth<sup>®</sup> RF analog core 办

- ∻

- Built-in PLL for multi-clock input Built-in ARM7TDMI-S<sup>™</sup> core ♦

- ∻

- On-chip Program Mask-ROM for Bluetooth® communication ∻

- On-chip Work memory (RAM) for Bluetooth® Baseband procedure ∻

- Supports patch program loader function ∻

- Supports a CODEC for audio communication

- ∻ CVSD (Continuous Variable Slope Delta Modulation) CODEC

- PCM (Pulse Code Modulation) CODEC ∻

- Connectable Serial Flash ROM/ EEPROM at external serial memory interface

- ♦ Serial Flash ROM interface (SPI)

- EEPROM interface (I<sup>2</sup>C/SPI) ∻

- Host Interface (set for the product test.)

- UART interface: Baud rate from 2400 bps to 4.33 Mbps ৵

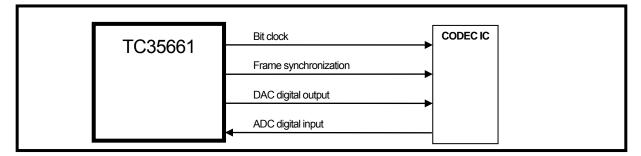

- Voice/Audio CODEC Digital Interface (1-ch)

- ∻ Supports I<sup>2</sup>S (The Inter-IC Sound Bus) interface

- Left-justified interface ∻

- Supports PCM (Pulse Code Modulation) digital interface ∻

- General Purpose I/O (GPIO) with pull-up and pull-down resistors (MAX: 19 ports)

- Wake-up Interface

- ∻ Wake-up input function and remote wake-up output function

- Wi-Fi co-existence interface (2-wire, 3-wire and 4-wire)

- Test Interface  $\triangleright$

$\triangleright$

- JTAG Interface (ICE Interface) ∻

- Supports OSC (Crystal oscillator: 26 MHz)

- ♦ Supports an external clock input

- ∻ Built-in oscillation circuit for an external crystal oscillator

- Supports a sleep clock

- ♦ Built-in divider for the reference operation clock

- Supports an external clock input ∻

- Built-in sleep function

- Power Supply: Single 1.8 or 3.3 V  $\triangleright$

- Package

- TC35661SBG: P-TFBGA64-0505-0.50-001 [64 balls, 5x5 mm, 0.5 mm pitch, and 1.2 mm height] ♦

- ♦ TC35661DBG: P-LFBGA64-0707-0.80-001 [64 balls, 7x7 mm, 0.8 mm pitch, and 1.4 mm height]

#### 1.3. Ordering Information

The product whose ending of the product number (the added code) is different has different specifications.

| Ending of Product Number<br>(Added Code) | Operating Temperature | Weight<br>(Typ.) |

|------------------------------------------|-----------------------|------------------|

| (ELA                                     | -20 to 85°C           | 0.052 g          |

| (ELC                                     | -20 to 85°C           | 0.049 g          |

| Others                                   | -40 to 85°C           | 0.049 g          |

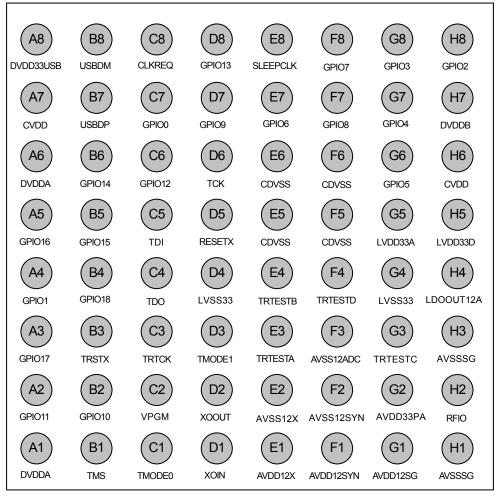

- 2. Pin Function

- 2.1. Pin Assignment

Figure 2-1 Pin Assignment (Top view)

#### 2.2. Pin Functions

Table 2-1 shows an attribute of each pin, input or output state at operation, and function of each pin. Each supported function depends on ROM version. Please see the firmware data sheet. The power supply pins are shown in Table 2-2.

| Pin name | Pin | Attribute                         | Condition                                                          | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           |

|----------|-----|-----------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|          | No. | VDD category<br>Direction<br>Type | During BT communication<br>During a reset<br>After a reset release |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |     |                                   | Reset interface                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

| RESETX   | D5  | DVDDA<br>IN                       | IN<br>IN                                                           | Hardware reset input pin<br>Low level indicates the reset.                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

|          |     | Schmitt trigger                   | IN                                                                 |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|          |     |                                   | Clock interface                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

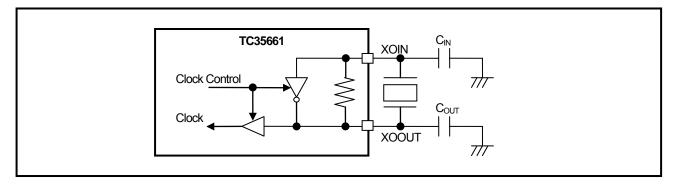

| XOIN     | D1  | AVDD12X<br>IN<br>OSC              | IN<br>IN<br>IN                                                     | Reference clock input pin<br>Crystal oscillator or TCXO input pin.<br>The clock frequency is 26 MHz. The clock<br>frequency uncertainty should be +/- 20 ppm or<br>less.<br>A feedback resistor is built in between XOIN pin<br>and XOOUT pin.<br>A resistor and a capacitor suitable for the used<br>crystal oscillator should be externally connected.<br>The clock is used as the internal reference clock.                                                                                                   |

| XOOUT    | D2  | AVDD12X<br>OUT<br>OSC             | OUT<br>OUT<br>OUT                                                  | Reference clock feedback output pin<br>Crystal oscillator output pin.<br>A feedback resistor is built in between XOIN pin<br>and XOOUT pin.<br>A resistor and a capacitor suitable for the used<br>crystal oscillator should be externally connected.<br>The clock is used as the internal reference clock.<br>If using TCXO for a reference clock, this pin<br>needs to be kept open.                                                                                                                           |

| CLKREQ   | C8  | DVDDA<br>OUT<br>2 mA              | OUT<br>OUT<br>OUT                                                  | Reference clock (26 MHz) request pin<br>Reference clock request signal.<br>By using this signal to control ON/OFF of an<br>external clock, lower power consumption of the<br>hardware system is achieved.<br>A high level indicates a request for the clock<br>supply.<br>If SLEEPCLK is not used and only X'tal is used,<br>or during a reset, this pin always outputs High.<br>When the clock supply is not necessary, this pin<br>outputs Low.<br>When not using this pin, this pin needs to be kept<br>open. |

| SLEEPCLK | E8  | DVDDA<br>IN<br>Schmitt trigger    | IN<br>IN<br>IN                                                     | Sleep clock input pin<br>This pin is a clock input for low power<br>consumption operation.<br>The clock frequency should be 32.768 kHz.<br>Frequency uncertainty of the sleep clock should<br>be less than or equal to +/-250 ppm.<br>When not using this pin, this pin needs to be<br>pulled down by 100 k $\Omega$ .                                                                                                                                                                                           |

#### Table 2-1 Pin Functions

| Pin name       | Pin          | Attribute                                                                     | Condition                                                          | Functional description                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

|----------------|--------------|-------------------------------------------------------------------------------|--------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|                | No.          | VDD category<br>Direction<br>Type                                             | During BT communication<br>During a reset<br>After a reset release |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

|                | RF interface |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| RFIO           | H2           | AVDD12SG<br>IN/OUT<br>Analog                                                  | IN/OUT<br>GND<br>GND                                               | RF I/O pin<br>Chapter 6 shows the external connection<br>example of the circuit which matches this pin to<br>$50 \Omega$ .<br>Refer to the connection example, confirm<br>operations in customer's environment, and<br>adjust the components constant.<br>The pattern before and behind the matching<br>circuit should wire with the $50 \Omega$ transmission line<br>as much as possible, and should not interfere<br>with the power supply line.<br>Don't connect DC voltage directly to this pin. |  |  |  |  |  |

|                |              |                                                                               | General purpose I/O port                                           |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO0          | C7           | DVDDA<br>IN/OUT<br>Pull-up/<br>Pull-down<br>Schmitt trigger<br>1, 2, and 4 mA | IN/OUT<br>No-pull-up<br>No-pull-up                                 | General purpose I/O pin 0<br>During a reset GPIO0 is set as an input whose<br>built-in pull-up resistor is disabled. After the reset<br>release, the data direction and the built-in pull-up<br>resistor are set by using the internal software.<br>When not using this pin, this pin needs to be<br>pulled down by 100 kΩ.<br>Each supported function depends on ROM<br>version. Please see the firmware data sheet.                                                                                |  |  |  |  |  |

| GPIO1          | A4           | DVDDA/DVDDB                                                                   | IN/OUT                                                             | General Purpose I/O pin 1 to 18                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO2<br>GPIO3 | H8<br>G8     | IN/OUT<br>Pull-up/<br>Pull-down<br>Schmitt trigger                            | Pull-up<br>Pull-up                                                 | During a reset the GPIO pin is set as an input<br>whose built-in pull-up resistor is enabled. After<br>the reset release, the data direction and the<br>built-in pull-up resistor are set by using the                                                                                                                                                                                                                                                                                               |  |  |  |  |  |

| GPIO4          | G7           | 1, 2, and 4 mA                                                                |                                                                    | internal software.<br>When not using this pin, this pin needs to be kept                                                                                                                                                                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| GPIO5          | G6           |                                                                               |                                                                    | open.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |  |  |  |  |  |

| GPIO6<br>GPIO7 | E7<br>F8     |                                                                               |                                                                    | Pin function of each GPIO pin is assigned to UART interface, the codec digital interface, the                                                                                                                                                                                                                                                                                                                                                                                                        |  |  |  |  |  |

| GPIO7<br>GPIO8 | F0<br>F7     |                                                                               |                                                                    | serial memory interface, and so on by the<br>firmware mounted on ROM or the commands                                                                                                                                                                                                                                                                                                                                                                                                                 |  |  |  |  |  |

| GPIO9          | D7           |                                                                               |                                                                    | from the external host mounted on that firmware.<br>Please see the firmware data sheet.                                                                                                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

| GPIO10         | B2           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO11         | A2           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO12         | C6           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO13         | D8           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO14         | B6           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO15         | B5           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO16         | A5           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO17         | A3           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| GPIO18         | B4           |                                                                               |                                                                    |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |  |  |  |  |  |

| Pin name | Pin               | Attribute                           | Condition                                                          | Functional description                                                                                                                                                                                                                                                                                                                              |  |  |  |  |  |

|----------|-------------------|-------------------------------------|--------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|--|--|

|          | No.               | VDD category<br>Direction<br>Type   | During BT communication<br>During a reset<br>After a reset release |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

|          | IC test interface |                                     |                                                                    |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

| TMODE0   | C1                | DVDDA<br>IN                         | IN<br>IN                                                           | Test mode setting pins<br>These pins are used to test a product in Toshiba.<br>TMODE0 and TMODE1 pins need to be                                                                                                                                                                                                                                    |  |  |  |  |  |

| TMODE1   | D3                | Schmitt trigger                     | IN                                                                 | connected to GND.                                                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| TRTESTA  | E3                | LVDD33A                             | IN                                                                 | Analog test pins                                                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| TRTESTB  | E4                | IN/OUT<br>Analog                    | IN<br>IN                                                           | These pins are used for analog inputs or outputs at the test of a product.                                                                                                                                                                                                                                                                          |  |  |  |  |  |

| TRTESTC  | G3                | / thatog                            |                                                                    | These pins are used to test a product in Toshiba.                                                                                                                                                                                                                                                                                                   |  |  |  |  |  |

| TRTESTD  | F4                |                                     |                                                                    | TRTESTA, TRTESTB, TRTESTC and TRTESTD pins have to be connected to GND.                                                                                                                                                                                                                                                                             |  |  |  |  |  |

| USBDP    | B7                | DVDD33USB<br>IN/OUT<br>Differential | IN/OUT<br>Hi-Z<br>Hi-Z                                             | Test pin<br>This pin has to be connected to GND.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

| USBDM    | B8                | DVDD33USB<br>IN/OUT<br>Differential | IN/OUT<br>Hi-Z<br>Hi-Z                                             | Test pin<br>This pin has to be connected to GND.                                                                                                                                                                                                                                                                                                    |  |  |  |  |  |

|          |                   |                                     | JTAG interface                                                     |                                                                                                                                                                                                                                                                                                                                                     |  |  |  |  |  |

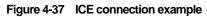

| TRSTX    | B3                | DVDDA<br>IN<br>Schmitt trigger      | Pull-down<br>Pull-down<br>Pull-down                                | JTAG reset input pin<br>This pin is a reset input for test or debugging.<br>During a reset the TRSTX is set as an input<br>whose built-in pull-down resistor is enabled.<br>Low level indicates JTAG reset.<br>High level indicates JTAG operation.<br>This pin needs to be kept open (not connected)<br>or to be pulled down if not used for JTAG. |  |  |  |  |  |

| TCK      | D6                | DVDDA<br>IN<br>Schmitt trigger      | Pull-up<br>Pull-up<br>Pull-up                                      | JTAG clock input pin<br>This pin is a clock input for test or debugging.<br>This pin needs to be kept open (unconnected) or<br>to be pulled up if not used for JTAG.                                                                                                                                                                                |  |  |  |  |  |

| TMS      | B1                | DVDDA<br>IN<br>Schmitt trigger      | Pull-up<br>Pull-up<br>Pull-up                                      | JTAG mode selection input pin<br>This pin is a serial signal input of the mode<br>selection for test or debugging.<br>This pin needs to be kept open (unconnected) or<br>to be pulled up if not used for JTAG.                                                                                                                                      |  |  |  |  |  |

| TDI      | C5                | DVDDA<br>IN<br>Schmitt trigger      | Pull-up<br>Pull-up<br>Pull-up                                      | JTAG data input pin<br>This pin is a serial data input for test or<br>debugging.<br>This pin is for a chip boundary test and firmware<br>development.<br>This pin needs to be kept open (unconnected) or<br>to be pulled up if not used for JTAG.                                                                                                   |  |  |  |  |  |

| TDO      | C4                | DVDDA<br>TristateOUT<br>4 mA        | Hi-Z<br>Hi-Z<br>Hi-Z                                               | JTAG data output pin<br>This pin is a serial data output for test or<br>debugging.<br>This pin needs to be kept open (unconnected) if<br>not used for JTAG.                                                                                                                                                                                         |  |  |  |  |  |

| TRTCK    | C3                | DVDDA<br>OUT<br>4 mA                | OUT<br>OUT<br>OUT                                                  | ICE retum clock output pin<br>Wait control signal to JTAG clock when using<br>ICE. This pin is used for firmware development<br>using ICE.<br>This pin needs to be kept open (unconnected) if<br>not used for JTAG.                                                                                                                                 |  |  |  |  |  |

#### 2.2.1. Power Supply Pins

Table 2-2 shows an attribute of each pin and the supply voltage for each pin at operation.

|           |                      | Condition          | Functional description |                                                                                                                                                                                                                                                                                                                            |  |  |  |

|-----------|----------------------|--------------------|------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|--|

|           | No.                  | Type<br>VDD/GND    | Normal<br>Exceptional  |                                                                                                                                                                                                                                                                                                                            |  |  |  |

|           | VDD/ GND             |                    |                        |                                                                                                                                                                                                                                                                                                                            |  |  |  |

| VPGM      | C2                   | Digital<br>VDD/GND | GND<br>3.3 V           | Test pin for IC manufacturing<br>VPGM shall be connected to GND directly.                                                                                                                                                                                                                                                  |  |  |  |

| DVDDA     | A1<br>A6             | Digital<br>VDD     | 3.3 V<br>—             | Power supply pin for GPIOm pins (m = 0, 1, and 6 to 18)<br>3.3 V needs to be supplied to all DVDDA pins because two<br>DVDDA pins, A1 and A6 are connected internally in the IC.                                                                                                                                           |  |  |  |

| DVDDB     | H7                   | Digital<br>VDD     | 3.3 V<br>—             | Power supply pin for GPIOn pins (n = 2 to 5)<br>3.3 V needs to be supplied to DVDDB pin.                                                                                                                                                                                                                                   |  |  |  |

| DVDD33USB | A8                   | Digital<br>VDD/GND | GND                    | Test pin (for power supply)<br>This pin needs to be connected to GND in normal operation.                                                                                                                                                                                                                                  |  |  |  |

| CVDD      | A7<br>H6             | Digital<br>VDD     | 1.2 V<br>—             | Power supply pin for the IC core<br>LDO output voltage (1.2 V) is supplied to the digital circuit in<br>the IC. A capacitor of at least 0.8 $\mu$ F or more in the operating<br>temperature range needs to be connected to this pin as the<br>load of LDO.<br>All CVDD pins, A7 and H6 are connected internally in the IC. |  |  |  |

| CDVSS     | E5<br>E6<br>F5<br>F6 | Digital<br>GND     | GND<br>—               | GND pin for the digital core logic and I/O interface<br>All CDVSS pins need to be connected to GND.                                                                                                                                                                                                                        |  |  |  |

| AVDD12X   | E1                   | Analog<br>VDD      | 1.2 V<br>—             | Power supply pin for the crystal oscillator interface LDO output voltage (1.2 V) is supplied to the digital circuit in the IC. A capacitor of 0.8 $\mu$ F or more needs to be connected in the operating temperature range as the load of the LDO.                                                                         |  |  |  |

| AVDD12SYN | F1                   | Analog<br>VDD      | 1.2 V<br>—             | Power supply pin for RFPLL<br>This pin needs to be connected to LDOOUT12A.                                                                                                                                                                                                                                                 |  |  |  |

| AVDD12SG  | G1                   | Analog<br>VDD      | 1.2 V<br>              | Power supply pin for LNA/ Receiver MIX (RxMIX)/ ADC/ DAC/<br>Low pass filter (LPF)/ PAcontrol/ BasebandPLL<br>This pin needs to be connected to LDOOUT12A.                                                                                                                                                                 |  |  |  |

| AVDD33PA  | G2                   | Analog<br>VDD      | 3.3 V<br>—             | Power supply pin for PA<br>3.3 V needs to be supplied to AVDD33PA pin.                                                                                                                                                                                                                                                     |  |  |  |

| AVSS12X   | E2                   | Analog<br>GND      | GND                    | GND pin for the crystal oscillator interface<br>AVSS12X pin needs to be connected to GND.                                                                                                                                                                                                                                  |  |  |  |

| AVSS12SYN | F2                   | Analog<br>GND      | GND                    | GND pin for RFPLL<br>AVSS12SYN pin needs to be connected to GND.                                                                                                                                                                                                                                                           |  |  |  |

| AVSS12ADC | F3                   | Analog<br>GND      | GND                    | GND pin for ADC/ DAC/ LPF/ BasebandPLL<br>AVSS12ADC pin needs to be connected to GND.                                                                                                                                                                                                                                      |  |  |  |

| AVSSSG    | H1<br>H3             | Analog<br>GND      | GND                    | GND pin for LNA/ RxMIX/ PAcontrol/ PA<br>All AVSSSG pins need to be connected to GND.                                                                                                                                                                                                                                      |  |  |  |

| LVDD33D   | H5                   | LDO IN<br>VDD      | 3.3 V<br>—             | Power supply pin for LDO-type regulator for the digital core 3.3 V needs to be supplied to LVDD33D pin.                                                                                                                                                                                                                    |  |  |  |

| LVDD33A   | G5                   | LDO IN<br>VDD      | 3.3 V<br>—             | Power supply pin for LDO-type regulator for the analog core 3.3 V needs to be supplied to LVDD33A pin.                                                                                                                                                                                                                     |  |  |  |

| LVSS33    | D4<br>G4             | LDO GND<br>GND     | GND<br>—               | GND pin for LDO-type regulators for the analog core and the digital core<br>All LVSS33 pins need to be connected to GND.                                                                                                                                                                                                   |  |  |  |

#### Table 2-2Power supply pins

#### TC35661SBG/DBG-203

| Pin name  | Pin | Attribute       | Condition             | Functional description                                                                                                                                                                                                                                       |

|-----------|-----|-----------------|-----------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|           | No. | Type<br>VDD/GND | Normal<br>Exceptional |                                                                                                                                                                                                                                                              |

| LDOOUT12A | H4  | LDO OUT<br>OUT  | OUT<br>—              | Voltage output pin of LDO-type regulator for the analog core LDOOUT12A pin needs to be connected to both AVDD12SYN pin and AVDD12SG pin. A capacitor of 0.8 $\mu$ F or more needs to be connected in the operating temperature range as the load of the LDO. |

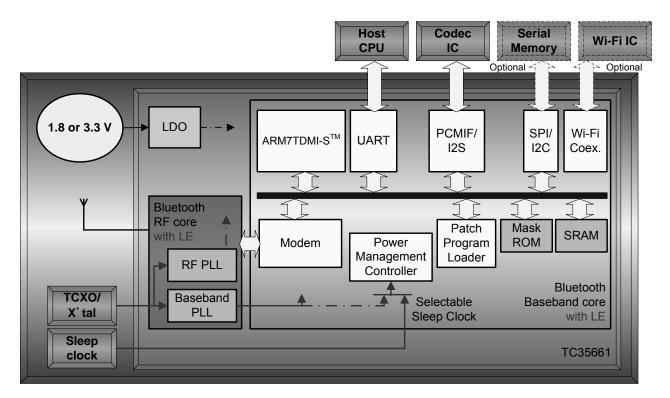

#### 3. System Configuration

#### 3.1. Block Diagram

Figure 3-1 shows a block diagram of TC35661 and a connection example to peripheral devices.

TC35661 should have a single power supply of 3.3 V or 1.8 V, and the IC has LDO regulators that have to have external capacitors.

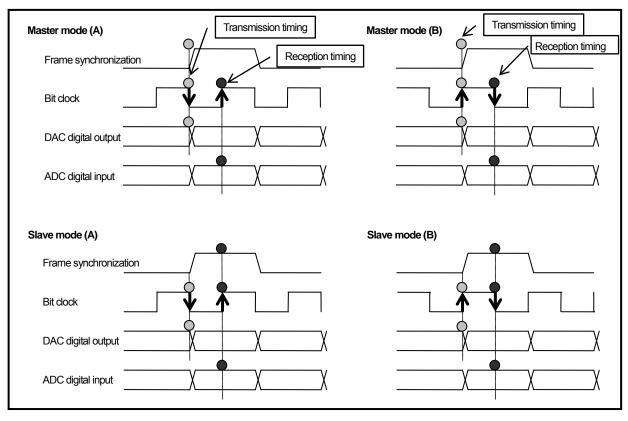

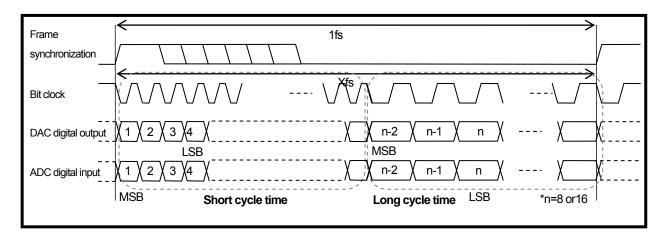

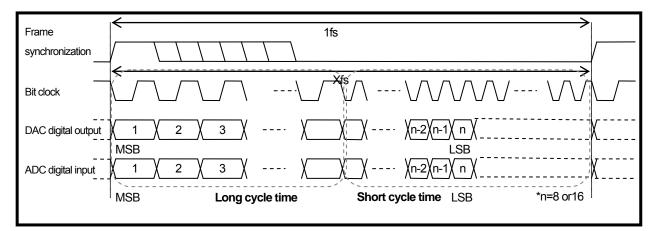

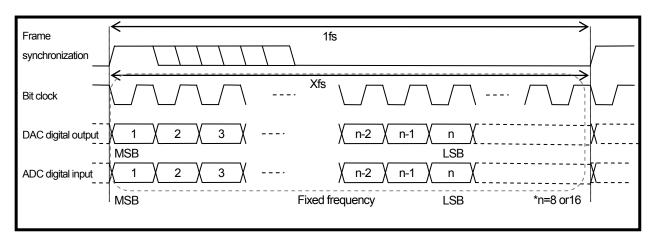

The reference operation clock of 26 MHz should be input.