CMOS Digital Integrated Circuit Silicon Monolithic

# **TC358767AXBG**

#### **Mobile Peripheral Devices**

#### Overview

TC358767AXBG is a bridge device that enables video streaming from a Host (application or baseband processor) over MIPI® DSI or DPI link to drive DisplayPort<sup>TM</sup> display panels. TC358767AXBG also supports audio streaming from the host via I2S interface to the Display panels. TC358767AXBG provides a low power bridge solution to efficiently translate MIPI® DSI or DPI transfers to DisplayPort<sup>TM</sup> transfers. As the

DisplayPort<sup>TM</sup> uses fewer wires compared to other existing display panel standards, it simplifies the LCD connectivity. The effect of using TC358767AXBG is to enable existing baseband devices supporting DSI or DPI streaming to connect to new panels supporting DisplayPort<sup>TM</sup> interface and also to connect to existing panels over longer distance using DisplayPort<sup>TM</sup> adaptors at far-end. TC358767AXBG can interface to up to two independent devices.

#### **Features**

- Translates MIPI<sup>®</sup> DSI/DPI Link video stream from Host to DisplayPort<sup>TM</sup> Link data to external display devices.

- The inputs are driven by a DSI Host with 4-Data Lanes, upto1 Gbps/lane or DPI Host with 16/18/24 bit interface upto154 MHz parallel clock.

- Supports HDCP Digital Content Protection version 1.3 (DisplayPort<sup>TM</sup> amendment Rev1.1).

- Embeds audio information from the I2S port into the DisplayPort<sup>™</sup> data stream.

- The output Interface consists of a DisplayPort<sup>™</sup>

Tx with a 2-lane Main Link and AUX-Ch.

- Register Configuration: From DSI link or I<sup>2</sup>C interface.

- Interrupt to host to inform any error status or status needing attention from Host.

- Internal test pattern (color bar) generator for DP o/p testing without any video (DSI/DPI) i/p.

- Debug/Test Port: I<sup>2</sup>C Slave

#### DSI Receiver

- → MIPI® DSI: v1.01 / MIPI® D-PHY: v0.90 Compliant.

- Up to four (4) Data Lanes with Bi-direction support on Data Lane 0.

- ♦ Maximum speed at 1 Gbps/lane.

- Supports Burst as well as Non-Burst Mode Video Data.

- Video data packets are limited to one row per Hsync period.

- Supports video stream packets for video data transmission.

- Supports generic long packets for accessing the chip's register set.

Video input data formats:

- RGB-565, RGB-666 and RGB-888.

- New DSI V1.02 Data Type Support: 16-bit YCbCr 422

- ♦ Interlaced video mode is not supported.

#### DPI Receiver

- ♦ Up to 16 / 18 / 24 bit parallel data interface.

- ♦ Maximum speed at 154 MPs (MPixel per sec.).

- ♦ Video input data formats: RGB-565, RGB-666 and RGB-888.

- ♦ Only Progressive mode supported.

- I2S Audio Interface: Supports one I2S port for audio streaming from the host to TC358767AXBG.

- Supports slave mode (BCLK, LRCLK & over-sampling clock input from Host).

- ♦ Supports sampling frequencies of 32, 44.1, 48, 88.2, 96, 176.4 & 192 kHz.

- ♦ Supports up to 2 audio channels.

- ♦ Supports 16, 18, 20 or 24bits per sample.

- Optionally inserts IEC60958 status bits and preamble bits per channel.

- DisplayPort<sup>™</sup> Interface: Supports a

DisplayPort<sup>™</sup> link from TC358767AXBG to

display panels.

- → High speed serial bridge chip using VESA DisplayPort<sup>TM</sup> 1.1a Standard.

- ♦ Supports one dual-lane DisplayPort<sup>TM</sup> port for high bandwidth applications

- ♦ Support 1.62 or 2.7 Gbps/lane data rate with voltage swings @0.4, 0.6, 0.8 or 1.2 V

- ♦ Support of pre-emphasis levels of 0, 3.5dB and 6dB.

- Supports Audio related Secondary Data Packets.

- ♦ AUX channel supported at 1 Mbps.

- ♦ HPD support through GPIO[0] based interrupts

- Enhanced mode supported for content protection.

- Support HDCP encryption Version 1.3 with DisplayPort™ amendment Revision 1.1.

- Secure ASSR (Alternate Scrambler Seed Reset) support for eDP panels

- System designer connects ASSR\_DisablePad to VSS to enable eDP panels and ASSR

- Drive ASSR\_DisablePad with an inner ring VDDS for using DP panels and disable ASSR

- System software read Revision ID field, 0x0500[7:0]:

- Ox01 indicates eDP panels are used, DPCD register bit 0x0010A[0] of eDP panel should be set

- Ox03 assumes DP panels are connected, DPCD register bit 0x0010A[0] of DP panel should Not be set

- Stream Policy Maker is assumed handled by the Host (software/firmware).

- Start Link training in response to HPD & read final Link training status

- Configure DP link for actual video streaming & start video streaming

- Link Policy maker is assumed shared between the Host and TC358767AXBG chip.

- In auto\_correction = 0 mode, control link training

- Initiate Display device capabilities read and configure TC358767AXBG accordingly.

- Video timing generation as per panel requirement.

- ♦ SSCG with to 30 kHz modulation to reduce EMI.

- → Toshiba Magic Square algorithm RGB666 18b produces RGB888 24b like quality (with up to 16-million colors).

- → Built in PRBS7 Generator to test DisplayPort<sup>TM</sup> Link.

#### • RGB Parallel Output Interface:

- → RGB888 output (DisplayPort<sup>TM</sup> disabled) with only DSI input supported in this mode

- ♦ PCLK max. = 100 MHz

- Polarity control for PCLK, VSYNC, HSYNC & DE

#### • I2C Interface:

- ♦ I<sup>2</sup>C slave interface for chip register set access enabled using a boot-strap option.

- → I<sup>2</sup>C compliant slave interface support for normal (100 kHz) and fast mode (400 kHz).

#### GPIO Interface:

- ♦ 2 bits of GPIO (shared with other digital logic).

- ♦ Direction controllable by Host I<sup>2</sup>C accesses.

### • Clock Source:

- → DisplayPort<sup>TM</sup> clock source is from an external clock input or clock from DSI interface (13, 26, 19.2 or 38.4 MHz) – generates all internal & output clocks to interfacing display devices.

- → Built-in PLLs generate high-speed DisplayPort<sup>TM</sup> link clock requiring no external components. These PLLs are part of the DisplayPort<sup>TM</sup> PHY.

- Clock and power management support to achieve low power states.

#### Possible modes of Operation:

- → MODE S21: TC358767AXBG uses DisplayPort<sup>TM</sup> Tx as single 2-lane DisplayPort<sup>TM</sup> link to interface to single DisplayPort<sup>TM</sup> display device. Video stream source is from MIPI<sup>®</sup> DSI Host.

- → MODE P21: TC358767AXBG uses DisplayPort<sup>TM</sup> Tx as single 2-lane DisplayPort<sup>TM</sup> link to interface to single DisplayPort<sup>TM</sup> display device. Video stream source is from MIPI<sup>®</sup> DPI Host.

- → MODE S2P: TC358767A uses only Parallel output port and disables DisplayPort<sup>TM</sup> Tx to interface to single RGB display device. Video stream source is from MIPI® DSI Host.

#### Power supply inputs

- ♦ Core and MIPI® D-PHY: 1.2 V ± 0.06 V

- DisplayPort™: 1.8 V ± 0.09 V

DisplayPort™: 1.2 V ± 0.06 V

- Power Consumption(Typical value based on estimation)

- → Power-down mode (DSI-Rx in ULPS, DP PHY & PLLs disabled, clocks stopped):

- DSI Rx: 0.01 mW - DP PHY: 2.34 mW - PLL9: 0.01 mW - Core: 0.96 mW - Rest: 0.01 mW

♦ Normal operation (1920 x 1080 resolution with DSI-Rx in 4-lane @925 Mbps per lane, DP PHY in dual lane link @2.7 Gbps per lane):

- DSI Rx: 21.79 mW - DP PHY: 142.70 mW - PLL9: 2.42 mW - Core: 87.64 mW - IOs: 1.68 mW

#### Package

0.5mm ball pitch, 81 balls, 5 x 5 mm BGA package

## Table of contents

| REFERENCES               |                                                                            | 6  |

|--------------------------|----------------------------------------------------------------------------|----|

| 1. Overview              |                                                                            | 7  |

| 2. Features              |                                                                            | 10 |

| 3. External Pins         | S                                                                          | 13 |

| 3.1. TC35876             | S7AXBG External Pins                                                       | 13 |

| 3.2. TC35876             | 67AXBG Pin Mapping                                                         | 15 |

| 4. Package               |                                                                            | 16 |

|                          | aracteristics                                                              |    |

| 5.1. Absolute            | Maximum Ratings                                                            | 18 |

|                          | g Condition                                                                |    |

| •                        | trical Specification                                                       |    |

|                          | onsumption (Typical value based on estimation)                             |    |

|                          | tory                                                                       |    |

|                          | S ON PRODUCT USE                                                           |    |

|                          | Table of Figures                                                           |    |

| Figure 1.1               | System Overview with TC358767AXBG in MODE_S21 Configuration                |    |

| Figure 1.2<br>Figure 1.3 | System Overview with TC358767AXBG in MODE_P21 Configuration                |    |

| Figure 3.1               | TC358767AXBG 81-Pin Layout                                                 |    |

| Figure 4.1               | 81 pin TC358767AXBG package                                                | 16 |

|                          | List of Tables                                                             |    |

|                          | TC358767AXBG operational modes summary with panel size support information | 12 |

| Table 2.2                | Panel Size v/s Data link required by TC358767AXBG in DSI input case        |    |

| Table 2.3                | Panel Size v/s Data link required by TC358767AXBG in DPI input case        |    |

| Table 3.1<br>Table 4.1   | TC358767AXBG Functional Signal List for 81-pin Package                     |    |

| Table 5.1                | Absolute Maximum Ratings                                                   |    |

| Table 5.2                | Operating Condition                                                        |    |

| Table 5.3                | DC Electrical Specification                                                |    |

| Table 6.1                | Revision History                                                           | 20 |

- MIPI is a trademark of MIPI Alliance, Inc.

- DisplayPort is trademark owned by the Video Electronics Standards Association (VESA®) in the United States and other countries.

- Other company names, product names, and service names may be trademarks of their respective companies.

#### NOTICE OF DISCLAIMER

The material contained herein is not a license, either expressly or impliedly, to any IPR owned or controlled by any of the authors or developers of this material or MIPI<sup>®</sup>. The material contained herein is provided on an "AS IS" basis and to the maximum extent permitted by applicable law, this material is provided AS IS AND WITH ALL FAULTS, and the authors and developers of this material and MIPI<sup>®</sup> hereby disclaim all other warranties and conditions, either express, implied or statutory, including, but not limited to, any (if any) implied warranties, duties or conditions of merchantability, of fitness for a particular purpose, of accuracy or completeness of responses, of results, of workmanlike effort, of lack of viruses, and of lack of negligence.

All materials contained herein are protected by copyright laws, and may not be reproduced, republished, distributed, transmitted, displayed, broadcast or otherwise exploited in any manner without the express prior written permission of MIPI<sup>®</sup> Alliance. MIPI<sup>®</sup>, MIPI<sup>®</sup> Alliance and the dotted rainbow arch and all related trademarks, tradenames, and other intellectual property are the exclusive property of MIPI<sup>®</sup> Alliance and cannot be used without its express prior written permission.

ALSO, THERE IS NO WARRANTY OF CONDITION OF TITLE, QUIET ENJOYMENT, QUIET POSSESSION, CORRESPONDENCE TO DESCRIPTION OR NON-INFRINGEMENT WITH REGARD TO THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT. IN NO EVENT WILL ANY AUTHOR OR DEVELOPER OF THIS MATERIAL OR THE CONTENTS OF THIS DOCUMENT OR MIPI® BE LIABLE TO ANY OTHER PARTY FOR THE COST OF PROCURING SUBSTITUTE GOODS OR SERVICES, LOST PROFITS, LOSS OF USE, LOSS OF DATA, OR ANY INCIDENTAL, CONSEQUENTIAL, DIRECT, INDIRECT, OR SPECIAL DAMAGES WHETHER UNDER CONTRACT, TORT, WARRANTY, OR OTHERWISE, ARISING IN ANY WAY OUT OF THIS OR ANY OTHER AGREEMENT, SPECIFICATION OR DOCUMENT RELATING TO THIS MATERIAL, WHETHER OR NOT SUCH PARTY HAD ADVANCE NOTICE OF THE POSSIBILITY OF SUCH DAMAGES.

Without limiting the generality of this Disclaimer stated above, the user of the contents of this Document is further notified that MIPI®: (a) does not evaluate, test or verify the accuracy, soundness or credibility of the contents of this Document; (b) does not monitor or enforce compliance with the contents of this Document; and (c) does not certify, test, or in any manner investigate products or services or any claims of compliance with the contents of this Document. The use or implementation of the contents of this Document may involve or require the use of intellectual property rights ("IPR") including (but not limited to) patents, patent applications, or copyrights owned by one or more parties, whether or not Members of MIPI®. MIPI® does not make any search or investigation for IPR, nor does MIPI® require or request the disclosure of any IPR or claims of IPR as respects the contents of this Document or otherwise.

Questions pertaining to this document, or the terms or conditions of its provision, should be addressed to:

MIPI<sup>®</sup> Alliance, Inc. c/o IEEE-ISTO 445 Hoes Lane Piscataway, NJ 08854 Attn: Board Secretary

This Notice of Disclaimer applies to all DSI input and processing paths related descriptions throughout this document.

#### REFERENCES

- 1. MIPI® DSI, "MIPI® Alliance Specification for DSI Version 1.01.00 21 February 2008"

- 2. MIPI® DPI, "MIPI® Alliance Standard for Display Pixel Interface (DPI-2) Version 2.00 15 September 2005"

- 3. MIPI® D-PHY, "DRAFT MIPI® Alliance Specification for D-PHY Version 0.91.00 r0.01 14-March-2008"

- 4. VESA DisplayPort<sup>TM</sup> Standard (Version 1, Revision 1A January 11, 2008)

- VESA Embedded DisplayPort<sup>TM</sup> (eDP) Standard (Version 1.1 October 23, 2009)

Digital Content Protection LLC, HDCP (Version 1.3 with DisplayPort<sup>TM</sup> amendment Revision 1.1, Jan. 15 2010)

- 7. I<sup>2</sup>C bus specification, version 2.1, January 2000, Philips Semiconductor

- 8. Draft CEA-861-C, A DTV Profile for Uncompressed High Speed Digital Interfaces (Doc. Number: CEA-861rCv9.pdf (PNXXX)) Date: 05/04/2005

- 9. DisplayPort<sup>™</sup> PHY DFT Strategy Specification Rev 1.3

### 1. Overview

The DSI/DPI to DisplayPort<sup>TM</sup> converter (TC358767AXBG) is a bridge device that enables video streaming from a Host (application or baseband processor) over MIPI® DSI or DPI link to drive DisplayPort<sup>TM</sup> display panels. TC358767AXBG also supports audio streaming from the host via I2S interface to the Display panels. TC358767AXBG provides a low power bridge solution to efficiently translate MIPI® DSI or DPI transfers to DisplayPort<sup>TM</sup> transfers. As the DisplayPort<sup>TM</sup> uses fewer wires compared to other existing display panel standards, it simplifies the LCD connectivity. The effect of using TC358767AXBG is to enable existing baseband devices supporting DSI or DPI streaming to connect to new panels supporting DisplayPort<sup>TM</sup> interface and also to connect to existing panels over longer distance using DisplayPort<sup>TM</sup> adaptors at far-end. TC358767AXBG can interface to up to two independent devices.

The chip can be configured through the DSI link by sending write/read register commands through DSI Generic Long Write packets. It can also be configured through the I<sup>2</sup>C Slave interface.

The DSI-RX receiver supports from 1 to 4-Lane configurations at bit rate up to 1 Gbps per lane. Host can transmit video in continuous video streaming mode. Host controls video timing by sending video frame and line sync events together with video pixel data; video data transmission can be burst or non-burst. Since the chip integrates only a small video buffer, Host still has to take care of transmitting pixel data at appropriate video line time in order to avoid buffer overflow (or underflow).

The DPI-Rx receiver supports 16, 18 or 24 bits parallel interface along with the required control signals for the Pixel clock and HSync/VSync/DE.

The TC358767AXBG also supports content protection using HDCP copy protection. (Option) The DisplayPort<sup>TM</sup> transmitter supports data throughput at 1.62 Gbps or 2.7 Gbps per lane of main link. TC358767AXBG supports three configuration modes. These modes mainly differ based on the source of input stream and number of display devices that TC358767AXBG can be connected to.

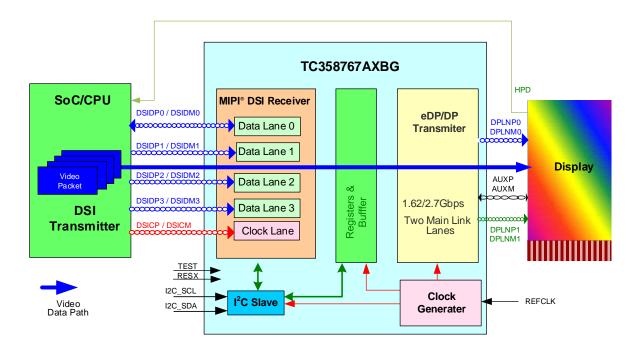

- Mode\_S21: A system configuration where TC358767AXBG may typically be used is shown in Figure 1.1. In this configuration, the TC358767AXBG can support displays with resolution up to WUXGA (1920×1200) at 24bit, 60 fps or WUXGA (1920×1200) at 18bit, 60 fps. Video stream source is from DSI Host.

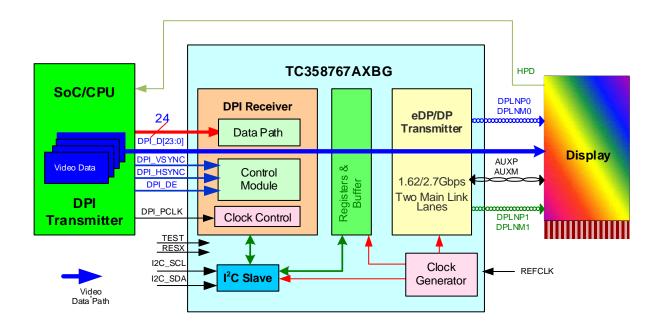

- Mode\_P21: A system configuration where TC358767AXBG may typically be used is shown in Figure 1.2. This is similar to the Mode\_S21 except that the video stream source is from DPI Host. In this configuration, the TC358767AXBG can support displays with resolution up to WUXGA (1920×1200) at 24bit, 60 fps.

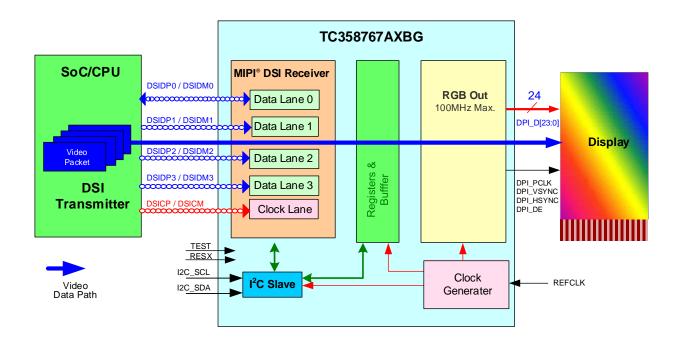

- Mode\_S2P: A system configuration where TC358767AXBG may typically be used is shown in Figure 1.3. In this mode, DisplayPort<sup>TM</sup> output is not used and the chip rather behaves as a DSI to RGB convertor. In this system, TC358767AXBG could be connected to a single display. In this configuration, the TC358767AXBG can support displays with resolution up to WXGA (1280x800 or 1366x768). Max. output PCLK is 100MHz. Video stream source is from DSI Host.

The chip supports power management to conserve power when its functions are not in use. Host manages the chip's power consumption modes by using ULPS messages over DSI link during DPI input mode.

The following figures show all these modes, where TC358767AXBG, display panels and a Host are connected in target Reference system for mobile large display panel applications.

Figure 1.1 System Overview with TC358767AXBG in MODE\_S21 Configuration

Figure 1.2 System Overview with TC358767AXBG in MODE\_P21 Configuration

Figure 1.3 System Overview with TC358767AXBG in MODE\_S2P Configuration

### 2. Features

Below are the main features supported by TC358767AXBG.

- Translates MIPI<sup>®</sup> DSI/DPI Link video stream from Host to DisplayPort<sup>™</sup> Link data to external display devices.

- The inputs are driven by a DSI Host with 4-Data Lanes, upto1 Gbps/lane or DPI Host with 16/18/24 bit interface upto154 MHz parallel clock.

- Supports HDCP Digital Content Protection version 1.3 (DisplayPort<sup>™</sup> amendment Rev1.1).

- Embeds audio information from the I2S port into the DisplayPort<sup>TM</sup> data stream.

- The output Interface consists of a DisplayPort<sup>TM</sup> Tx with a 2-lane Main Link and AUX-Ch.

- Register Configuration: From DSI link or I<sup>2</sup>C interface.

- Interrupt to host to inform any error status or status needing attention from Host.

- Internal test pattern (color bar) generator for DP o/p testing without any video (DSI/DPI) i/p.

- Debug/Test Port: I<sup>2</sup>C Slave

#### DSI Receiver

- ♦ MIPI® DSI: v1.01 / MIPI® D-PHY: v0.90 Compliant.

- ♦ Up to four (4) Data Lanes with Bi-direction support on Data Lane 0.

- ♦ Maximum speed at 1 Gbps/lane.

- ♦ Supports Burst as well as Non-Burst Mode Video Data.

- Video data packets are limited to one row per Hsync period.

- ♦ Supports video stream packets for video data transmission.

- ♦ Supports generic long packets for accessing the chip's register set.

- ♦ Video input data formats:

- RGB-565, RGB-666 and RGB-888.

- New DSI V1.02 Data Type Support: 16-bit YCbCr 422

- ♦ Interlaced video mode is not supported.

### • DPI Receiver

- ♦ Up to 16 / 18 / 24 bit parallel data interface.

- → Maximum speed at 154 MPs (MPixel per sec).

- ♦ Video input data formats: RGB-565, RGB-666 and RGB-888.

- ♦ Only Progressive mode supported.

- I2S Audio Interface: Supports one I2S port for audio streaming from the host to TC358767AXBG.

- ♦ Supports slave mode (BCLK, LRCLK & over-sampling clock input from Host).

- ♦ Supports sampling frequencies of 32, 44.1, 48, 88.2, 96, 176.4 & 192 kHz.

- ♦ Supports up to 2 audio channels.

- ♦ Supports 16, 18, 20 or 24 bits per sample.

- ♦ Optionally inserts IEC60958 status bits and preamble bits per channel.

- **DisplayPort<sup>TM</sup> Interface:** Supports a DisplayPort<sup>TM</sup> link from TC358767AXBG to display panels.

- ♦ High speed serial bridge chip using VESA® DisplayPort™ 1.1a Standard.

- ♦ Supports one dual-lane DisplayPort<sup>TM</sup> port for high bandwidth applications.

- ♦ Support 1.62 or 2.7 Gbps/lane data rate with voltage swings @0.4, 0.6, 0.8 or 1.2 V.

- ♦ Support of pre-emphasis levels of 0, 3.5 dB and 6 dB.

- ♦ Supports Audio related Secondary Data Packets.

- ♦ AUX channel supported at 1 Mbps.

- ♦ HPD support through GPIO[0] based interrupts

- ♦ Enhanced mode supported for content protection.

- ♦ Support HDCP encryption Version 1.3 with DisplayPort<sup>TM</sup> amendment Revision 1.1.

- ♦ Secure ASSR (Alternate Scrambler Seed Reset) support for eDP panels

- System designer connects ASSR\_DisablePad to VSS to enable eDP panels and ASSR

- Drive ASSR DisablePad with an inner ring VDDS for using DP panels and disable ASSR

- System software read Revision ID field, 0x0500[7:0]:

- Ox01 indicates eDP panels are used, DPCD register bit 0x0010A[0] of eDP panel should be set.

- 0x03 assumes DP panels are connected, DPCD register bit 0x0010A[0] of DP panel should Not be set.

- Stream Policy Maker is assumed handled by the Host (software/firmware).

- Start Link training in response to HPD & read final Link training status

- Configure DP link for actual video streaming & start video streaming

- ♦ Link Policy maker is assumed shared between the Host and TC358767AXBG chip.

- In auto\_correction = 0 mode, control link training

- Initiate Display device capabilities read and configure TC358767AXBG accordingly.

- ♦ Video timing generation as per panel requirement.

- ♦ SSCG with to 30 kHz modulation to reduce EMI.

- → Toshiba Magic Square algorithm RGB666 18b produces RGB888 24b like quality (with up to 16-million colors).

- ♦ Built in PRBS7 Generator to test DisplayPort<sup>TM</sup> Link.

### • RGB Parallel Output Interface:

- ♦ RGB888 output (DisplayPort<sup>™</sup> disabled) with only DSI input supported in this mode

- ♦ PCLK max. = 100 MHz

- ♦ Polarity control for PCLK, VSYNC, HSYNC & DE

#### • I<sup>2</sup>C Interface:

- ♦ I<sup>2</sup>C slave interface for chip register set access enabled using a boot-strap option.

- ♦ I<sup>2</sup>C compliant slave interface support for normal (100 kHz) and fast mode (400 kHz).

#### • GPIO Interface:

- ♦ 2 bits of GPIO (shared with other digital logic).

- ♦ Direction controllable by Host I<sup>2</sup>C accesses.

#### • Clock Source:

- ♦ DisplayPort<sup>TM</sup> clock source is from an external clock input or clock from DSI interface (13, 26, 19.2 or 38.4 MHz) generates all internal & output clocks to interfacing display devices.

- ♦ Built-in PLLs generate high-speed DisplayPort<sup>TM</sup> link clock requiring no external components. These PLLs are part of the DisplayPort<sup>TM</sup> PHY.

- Clock and power management support to achieve low power states.

### • Possible modes of Operation:

- ♦ MODE S21: TC358767AXBG uses DisplayPort<sup>TM</sup> Tx as single 2-lane DisplayPort<sup>TM</sup> link to interface to single DisplayPort<sup>TM</sup> display device. Video stream source is from MIPI® DSI Host.

- ♦ MODE P21: TC358767AXBG uses DisplayPort<sup>TM</sup> Tx as single 2-lane DisplayPort<sup>TM</sup> link to interface to single DisplayPort<sup>TM</sup> display device. Video stream source is from MIPI<sup>®</sup> DPI Host.

- ♦ MODE S2P: TC358767AXBG uses only Parallel output port and disables DisplayPort<sup>TM</sup> Tx to interface to single RGB display device. Video stream source is from MIPI<sup>®</sup> DSI Host.

#### Power supply inputs

- ♦ Core and MIPI® D-PHY: 1.2 V ± 0.06 V

- $\Leftrightarrow$  Digital I/O: 1.8 V  $\pm$  0.09 V

- ♦ DisplayPort<sup>TM</sup>: 1.8 V ± 0.09 V

- ♦ DisplayPort<sup>TM</sup>: 1.2 V ± 0.06 V

#### • Power Consumption (Typical value based on estimation)

- ♦ Power-down mode (DSI-Rx in ULPS, DP PHY & PLLs disabled, clocks stopped):

- DSI Rx: 0.01 mW

- DP PHY: 2.34 mW

- PLL9: 0.01 mW

- Core: 0.96 mW

- Rest: 0.01 mW

- ♦ Normal operation (1920×1080 resolution with DSI-Rx in 4-lane @925 Mbps per lane, DP PHY in dual lane link @2.7 Gbps per lane):

- DSI Rx: 21.79 mW

- DP PHY: 142.70 mW

- PLL9: 2.42 mW

- Core: 87.64 mW

- IOs: 1.68 mW

#### Package

- 0.5mm ball pitch, 81 balls, 5 x 5 mm BGA package

**Note:** Attention about ESD. This product is weak against ESD. Please handle it carefully.

Table 2.1 TC358767AXBG operational modes summary with panel size support information

| Mode | Input Configuration |           | Register Access         | Max Panel                                  |

|------|---------------------|-----------|-------------------------|--------------------------------------------|

| wode | DSI input           | DPI input | Method                  | size example                               |

| S21  | Active              | Х         | DSI or I <sup>2</sup> C | WUXGA 18bpp @ 60fps<br>WUXGA 24bpp @ 60fps |

| P21  | X                   | Active    | I <sup>2</sup> C        | WUXGA 24bpp @ 60fps                        |

Tables below provide an idea of different panel sizes that can be supported by using different data link lane configurations.

Table 2.2 Panel Size v/s Data link required by TC358767AXBG in DSI input case

|                  | Frame Size |                  |     |                         | RGB666   |               |           |      | RGB888   |               |         |          |

|------------------|------------|------------------|-----|-------------------------|----------|---------------|-----------|------|----------|---------------|---------|----------|

|                  |            | With<br>OverHead | FPS | Pixel<br>Clock<br>(MHz) | Bit Rate | # DSI<br>Data | # DP linl |      | Bit Rate | # DSI<br>Data | # DP Ma | in links |

|                  |            | Overneau         |     | (141112)                | (Gbps)   | lanes         | 1.62G     | 2.7G | (Gbps)   | lanes         | 1.62G   | 2.7G     |

| XGA              | 1024×768   | 1184×790         | 60  | 56                      | 1.01     | 2             | 1         | 1    | 1.34     | 2             | 2       | 1        |

| WXGA+<br>/ WSXGA | 1440×900   | 1600×926         | 60  | 89                      | 1.60     | 2             | 2         | 1    | 2.13     | 3             | 2       | 1        |

| SXGA+            | 1400×1050  | 1560×1080        | 60  | 89                      | 1.82     | 2             | 2         | 1    | 2.43     | 3             | 2       | 2        |

| WSXGA+           | 1680×1050  | 1840×1080        | 60  | 119                     | 2.15     | 3             | 2         | 1    | 2.86     | 3             | -       | 2        |

| UXGA             | 1600×1200  | 1760×1235        | 60  | 130                     | 2.35     | 3             | 2         | 2    | 3.13     | 4             | _       | 2        |

| WUXGA            | 1920×1200  | 2080×1235        | 60  | 154                     | 2.77     | 3             | _         | 2    | 3.70     | 4             | _       | 2        |

Table 2.3 Panel Size v/s Data link required by TC358767AXBG in DPI input case

|                  | Frame Size |                  |     |                         |                                |                    | GB666        |      | R                  | GB888 |            |

|------------------|------------|------------------|-----|-------------------------|--------------------------------|--------------------|--------------|------|--------------------|-------|------------|

|                  |            | With<br>OverHead | FPS | Pixel<br>Clock<br>(MHz) | DPI Support<br>154 MHz<br>PCLK | Bit Rate<br>(Gbps) | # DP<br>linl |      | Bit Rate<br>(Gbps) |       | Main<br>ks |

|                  |            | Overrieau        |     | (141112)                | 1 OLIK                         | (Gups)             | 1.62G        | 2.7G | (Gups)             | 1.62G | 2.7G       |

| XGA              | 1024×768   | 1184×790         | 60  | 56                      | Yes                            | 1.01               | 1            | 1    | 1.34               | 2     | 1          |

| WXGA+<br>/ WSXGA | 1440×900   | 1600×926         | 60  | 89                      | Yes                            | 1.60               | 2            | 1    | 2.13               | 2     | 1          |

| SXGA+            | 1400×1050  | 1560×1080        | 60  | 89                      | Yes                            | 1.82               | 2            | 1    | 2.43               | 2     | 2          |

| WSXGA+           | 1680×1050  | 1840×1080        | 60  | 119                     | Yes                            | 2.15               | 2            | 1    | 2.86               | -     | 2          |

| UXGA             | 1600×1200  | 1760×1235        | 60  | 130                     | Yes                            | 2.35               | 2            | 2    | 3.13               | _     | 2          |

| WUXGA            | 1920×1200  | 2080×1235        | 60  | 154                     | Yes                            | 2.77               | _            | 2    | 3.70               | _     | 2          |

Note: These are the formats commonly used by displays. Support for other sizes is possible as long

as they satisfy the maximum data rate constraints on the DSI and DisplayPort<sup>TM</sup> link interfaces.

Note: Throughout the rest of the document, "DP" is used to denote "DisplayPort™". Both these words have been used interchangeably and refer to the VESA DisplayPort™

specification as mentioned in the references.

## 3. External Pins

### 3.1. TC358767AXBG External Pins

TC358767AXBG uses an 81pin package. Following table gives the signals of TC358767AXBG and their function.

Table 3.1 TC358767AXBG Functional Signal List for 81-pin Package

| Group                                              | Pin Name               | I/O | Туре             | Function                                                                                                                                                                                                                                                                                                                                                      | Note |

|----------------------------------------------------|------------------------|-----|------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------|

|                                                    | RESX                   | I   | Sch              | System Reset – active Low 0: Reset 1: Normal operation                                                                                                                                                                                                                                                                                                        | _    |

|                                                    | REFCLK                 |     | Sch              | 13, 26, 19.2 or 38.4 MHz<br>50ps phase jitter p2p / WC duty cycle 40-60%                                                                                                                                                                                                                                                                                      | _    |

|                                                    | INT                    | 0   | N                | Interrupt to Host – active High 0: No interrupt is generated 1: Interrupt is generated                                                                                                                                                                                                                                                                        | 4mA  |

| System:                                            | DISABLE_ASSR           | I   | N                | ASSR control 0: Enable ASSR 1: Disable ASSR                                                                                                                                                                                                                                                                                                                   | _    |

| Reset,<br>Clock,<br>Mode<br>select,<br>Test<br>(9) | MODE[1:0]              | I   | N                | Mode Selection pins MODE_0: 0: REFCLK is source of internal DP PLL 1: When REFCLK = "0", DSI clock is source of internal DP PLL. When REFCLK = "1", DPI PCLK is source of internal DP PLL. MODE_1: When MODE_0 = "1" & REFCLK = "0" this pin will be effective. 0: DSI clock/2/7 is source of internal DP PLL. 1: DSI clock/2/9 is source of internal DP PLL. | _    |

|                                                    | TEST                   | ı   | N                | Test Pin - active high 0: Normal operation 1: Test mode                                                                                                                                                                                                                                                                                                       | _    |

|                                                    | TEST3                  | 0   | N                | Test Pin, Open                                                                                                                                                                                                                                                                                                                                                | _    |

|                                                    | VPGM0                  | NA  | _                | eFUSE programming voltage. Connect to GND                                                                                                                                                                                                                                                                                                                     | _    |

|                                                    | DSICP                  | I   | MIPI®-PHY        | MIPI®-DSI Rx Clock Lane Pos.                                                                                                                                                                                                                                                                                                                                  | _    |

|                                                    | DSICM                  | I   | MIPI®-PHY        | MIPI®-DSI Rx Clock Lane Neg.                                                                                                                                                                                                                                                                                                                                  | _    |

| DSI Rx                                             | DSIDP0                 | I/O | MIPI®-PHY        | MIPI®-DSI Rx Data Lane Pos.                                                                                                                                                                                                                                                                                                                                   | _    |

| (10)                                               | DSIDM0                 | I/O | MIPI®-PHY        | MIPI®-DSI Rx Data Lane Neg.                                                                                                                                                                                                                                                                                                                                   | _    |

|                                                    | DSIDP[3:1]             | I   | MIPI®-PHY        | MIPI®-DSI Rx Data Lane Pos.                                                                                                                                                                                                                                                                                                                                   | _    |

|                                                    | DSIDM[3:1]             | I   | MIPI®-PHY        | MIPI®-DSI Rx Data Lane Neg.                                                                                                                                                                                                                                                                                                                                   | _    |

|                                                    | DPLNP[1:0]             | 0   | DP-PHY           | embedded DisplayPort <sup>TM</sup> Output Main Link Pos.                                                                                                                                                                                                                                                                                                      |      |

| DP Out                                             | DPLNM[1:0]             | 0   | DP-PHY           | embedded DisplayPort™ Output Main Link Neg.                                                                                                                                                                                                                                                                                                                   |      |

| (8)                                                | DPAUXP                 | I/O | DP-PHY           | embedded DisplayPort™ Output AUX Channel Pos.                                                                                                                                                                                                                                                                                                                 |      |

|                                                    | DPAUXM                 | I/O | DP-PHY<br>DP-PHY | embedded DisplayPort™ Output AUX Channel Neg.  Precision Resistance (3kohm @ 1%) connection                                                                                                                                                                                                                                                                   |      |

|                                                    | PREC_RES[1:0] DPI_PCLK | I/O | N N              | DPI Pixel Clock (max 154 MHz) (default: Input)                                                                                                                                                                                                                                                                                                                | 4mA  |

|                                                    | DPI_VSYNC              | I/O | N                | DPI Vertical Sync (default: Input)                                                                                                                                                                                                                                                                                                                            | 4mA  |

| DPI Tx/Rx                                          | DPI_HSYNC              | I/O | N                | DPI Horizontal Sync (default: Input)                                                                                                                                                                                                                                                                                                                          | 4mA  |

| (28)                                               | DPI_DE                 | I/O | N                | DPI Data Enable (default: Input)                                                                                                                                                                                                                                                                                                                              | 4mA  |

|                                                    | DPI_D[23:0]            | I/O | N                | DPI Parallel Data (default: Input)                                                                                                                                                                                                                                                                                                                            | 4mA  |

|                                                    | I2C_SCL                | OD  | Sch              | I <sup>2</sup> C Clock                                                                                                                                                                                                                                                                                                                                        | _    |

| I <sup>2</sup> C                                   | I2C_SDA                | OD  | Sch              | I <sup>2</sup> C Data                                                                                                                                                                                                                                                                                                                                         | 4mA  |

| (3)                                                | I2C_ADR_SEL            | 1   | N                | I <sup>2</sup> C Slave Address Select 0: Slave address = 7'b1101_000 1: Slave address = 7'b0001_111                                                                                                                                                                                                                                                           | _    |

|               | SD/I2S_OSCLK      | I  | N     | I2S Over Sampling Clock                                          | _   |

|---------------|-------------------|----|-------|------------------------------------------------------------------|-----|

| I2S           | I2S_BCLK          |    | N     | I2S Bit Clock (max 12.5 MHz)                                     | _   |

| (4)           | I2S_LRCLK         | I  | N     | I2S sample clock (max 192 kHz)                                   | _   |

|               | I2S_DATA          | I  | N     | I2S Data                                                         | _   |

| GPIO<br>(2)   | GPIO[1:0]         | OD | 5T-OD | GPIO or Test Control Note1 GPIO[1:0] can be used for HPD support | 4mA |

|               | VDDC (1.2V)       | NA | _     | VDD for Internal Core (2)                                        | _   |

|               | VDDS (1.8V)       | NA | _     | VDDS for IO Ring power supply (1)                                | _   |

|               | VDD_PLL18 (1.8V)  | NA | _     | VDD for DP PHY PLLs (1)                                          | _   |

| POWER         | VDD_PLL12 (1.2V)  | NA | _     | VDD for DP PHY PLLs (1)                                          | _   |

| (10)          | VDD_DP18 (1.8V)   | NA | _     | VDD for DP PHY Main Channels (2)                                 | _   |

|               | VDD_PLL912 (1.2V) | NA | 1     | VDD for PLL9 (1)                                                 | _   |

|               | VDD_DP12 (1.2V)   | NA | _     | VDD for DP PHY (1)                                               | _   |

|               | VDD_DSI12 (1.2V)  | NA | _     | VDD for the MIPI® DSI PHY (1)                                    | _   |

| OD OLINID     | VSS               | NA | _     | Ground (Core, I/O) (3)                                           | _   |

| GROUND<br>(7) | VSS_DSI           | NA |       | Ground (DSI) (1)                                                 | _   |

| (,,           | VSS_DP            | NA | _     | Ground (DP) (3)                                                  |     |

Total 81 pins TC358767AXBG BGA package.

Note 1: Pins with multiplexed Functional mode functions

N: Normal IO

FS: Fail safe IO - gated

PHY: Either DP analog front end or MIPI® D-PHY

Sch: Schmitt trigger input

OD: Open drain

5T-OD: 5 V tolerant bi-direction buffer with Open drain

Pd: Pull Down

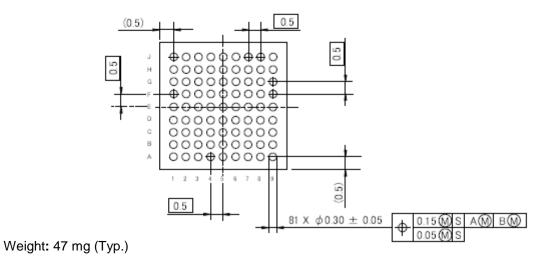

## 3.2. TC358767AXBG Pin Mapping

The mapping of TC358767AXBG signals to the external pins is given in the following figure. (BGA array)

Top View (through the die)

| A1         | A2           | А3        | A4        | <b>A</b> 5 | А6       | A7       | A8       | А9          |

|------------|--------------|-----------|-----------|------------|----------|----------|----------|-------------|

| DSIDM_0    | DSIDP_0      | I2S_LRCLK | VDDC      | VDDC       | INT      | VDDS     | I2C_SDA  | I2C_SCL     |

| B1         | B2           | В3        | В4        | B5         | В6       | В7       | В8       | В9          |

| DSIDM_1    | DSIDP_1      | GPIO_0    | I2S_BCLK  | I2S_DATA   | MODE_0   | MODE_1   | GPIO_1   | I2C_ADR_SEL |

| C1         | C2           | С3        | C4        | C5         | C6       | С7       | C8       | С9          |

| DSICM      | DSICP        | DPI_DE    | DPI_VSYNC | DPI_D_5    | DPI_D_7  | DPI_D_10 | TEST_3   | I2S_OSCLK   |

| D1         | D2           | D3        | D4        | D5         | D6       | D7       | D8       | D9          |

| VDD_DSI12  | VSS_DSI      | DPI_HSYNC | DPI_D_0   | VSS        | DPI_D_9  | DPI_D_12 | DPI_D_13 | DPI_D_14    |

| E1         | E2           | E3        | E4        | <b>E</b> 5 | E6       | E7       | E8       | E9          |

| DSIDM_2    | DSIDP_2      | DPI_D_1   | DPI_D_3   | VSS        | VSS      | DPI_D_16 | VPGM_0   | DPI_D_11    |

| F1         | F2           | F3        | F4        | F5         | F6       | F7       | F8       | F9          |

| DSIDM_3    | DSIDP_3      | DPI_D_2   | DPI_D_6   | DPI_D_8    | DPI_D_15 | DPI_D_18 | DPI_D_17 | DPI_D_20    |

| G1         | G2           | G3        | G4        | G5         | G6       | G7       | G8       | G9          |

| PREC_RES_0 | Disable_ASSR | DPI_D_4   | TEST      | DPI_D_19   | DPI_PCLK | DPI_D_21 | DPI_D_23 | DPI_D_22    |

| Н1         | H2           | Н3        | H4        | H5         | Н6       | Н7       | Н8       | Н9          |

| PREC_RES_1 | VSS_DP       | DPLNP_0   | VDD_DP12  | VSS_DP     | DPLNP_1  | VSS_DP   | DPAUXP_0 | VDD_PLL912  |

| J1         | J2           | J3        | J4        | J5         | J6       | J7       | J8       | J9          |

| REFCLK     | VDD_DP18     | DPLNM_0   | VDD_PLL12 | VDD_PLL18  | DPLNM_1  | VDD_DP18 | DPAUXM_0 | RESX        |

Figure 3.1 TC358767AXBG 81-Pin Layout

## 4. Package

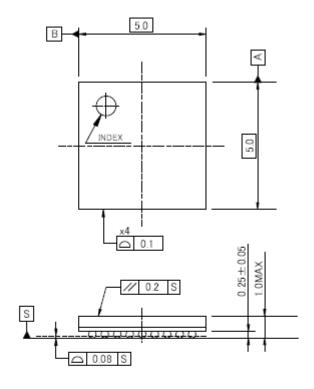

The package for TC358767AXBG is described in the figure below.

P-VFBGA81-0505-0.50-001 "Unit:mm"

Figure 4.1 81 pin TC358767AXBG package

The mechanical dimension of BGA81 package is listed below.

Table 4.1 Mechanical Dimension of P-VFBGA81-0505-0.50-001

| Package | Solder Ball<br>Pitch | Solder Ball<br>Height | Package<br>Dimension      | Package<br>Height | Note |

|---------|----------------------|-----------------------|---------------------------|-------------------|------|

| 81-Pin  | 0.50 mm              | 0.25 mm               | 5.0 × 5.0 mm <sup>2</sup> | 1.0 mm            | _    |

## 5. Electrical Characteristics

## 5.1. Absolute Maximum Ratings

VSS = 0 V reference

VDD18 used for VDDS as well as VDD-DP18; VDD12 used for VDDC as well as VDD-DSI12.

**Table 5.1 Absolute Maximum Ratings**

| Parameter              | Symbol | Rating           | Unit |

|------------------------|--------|------------------|------|

| Supply voltage (1.8 V) | VDD18  | -0.3 to +3.5     | V    |

| Supply voltage (1.2 V) | VDD12  | -0.3 to +2.0     | V    |

| Supply voltage (IO)    | VDD18  | -0.3 to +3.5     | V    |

| Supply voltage (IO)    | VREF   | -0.3 to +3.5     | V    |

| Input voltage          | VIN    | -0.3 to VDDS+0.3 | V    |

| Output voltage         | VOUT   | -0.3 to VDDS+0.3 | V    |

| Storage temperature    | Tstg   | -40 to +125      | °C   |

## 5.2. Operating Condition

VSS = 0 V reference

VDD18 used for VDDS as well as VDD-DP18; VDD12 used for VDDC as well as VDD-DSI12.

**Table 5.2 Operating Condition**

| Parameter                      | Symbol | Min  | Тур. | Max  | Unit |

|--------------------------------|--------|------|------|------|------|

| Supply voltage (1.8 V)         | VDD18  | 1.71 | 1.8  | 1.89 | V    |

| Supply voltage (1.2 V)         | VDD12  | 1.14 | 1.2  | 1.26 | V    |

| Operating frequency (internal) | Fopr   | _    | _    | 200  | MHz  |

| Operating temperature          | Та     | -20  | _    | +85  | °C   |

### 5.3. DC Electrical Specification

VSS = VSS\_C = VSS\_IO = VSS\_DSI = VSS\_DP = VSS\_PLL = VSS\_REG = 0V reference

**Parameter Symbol** Min Max Unit Typ. Input voltage High level VIH **0.7 VDDS** ٧ **VDDS** CMOS input Note1 Input voltage Low level VIL **0.3 VDDS** ٧ 0 CMOS input Note1 Input voltage High level VIHS **0.7 VDDS VDDS** V CMOS Schmitt Trigger Note1 Input voltage Low level **VILS 0.3 VDDS** V 0 CMOS Schmitt Trigger Note1 Output voltage High level VOH **0.8 VDDS VDDS** ٧ Note1, Note2 Output voltage Low level VOL 0 **0.2 VDDS** V Note1. Note2 IIH1 (Note3) Input leak current High level -10 10 μΑ

Table 5.3 DC Electrical Specification

Note1: VDDS within recommended operating condition.

Note2: Output current value is according to each IO buffer specification. Output voltage changes

-10

-200

10

-10

μΑ

μΑ

with output current value.

Input leak current Low level

Note3: Normal pin, or Pull-up I/O pin applied VDD18\_IO supply voltage to input pin

IIL1 (Note4)

IIL2 (Note5)

Note4: Normal pin applied VSS (0 V) to input pin

Note5: Pull-up I/O pin applied VSS (0 V) to input pin

## 5.4. Power Consumption (Typical value based on estimation)

Typical power consumption as measured for the power-down modes and for normal operation are provided below:

Power-down mode (DSI-Rx in ULPS, DP PHY & PLLs disabled, clocks stopped):

DSI Rx: 0.01 mW

DP PHY: 2.34 mW

PLL9: 0.01 mW

Core: 0.96 mW

Rest: 0.01 mW

Normal operation (1920×1080 resolution with DSI-Rx in 4-lane @925 Mbps per lane, DP PHY in dual lane link @2.7 Gbps per lane):

♦ DSI Rx: 21.79 mW

♦ DP PHY: 142.70 mW

♦ PLL9: 2.42 mW

♦ Core: 87.64 mW

♦ IOs: 1.68 mW

# 6. Revision History

Table 6.1 Revision History

| Revision | Date       | Description                                                                                                                                                                                                              |

|----------|------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 0.97     | 2014-04-10 | Newly released                                                                                                                                                                                                           |

| 0.972    | 2016-04-01 | Modified the weight of TC358767AXBG's package by rounding up digits after the decimal point to form an integer.                                                                                                          |

| 1.30     | 2017-07-10 | Changed header, footer and the last page. Added Figure 1.3 and modified descriptions in section 1. Modified descriptions in Features and section 2. Modified Table 3.1 and Figure 3.1. Added Table numbers in section 5. |

| 1.31     | 2017-12-27 | Modified Figure 1.1, Figure 1.2, Figure 1.3. Changed frequency to 100MHz in Figure 1.3. Added description, trademarks and registered trademarks.                                                                         |

| 1.4      | 2018-05-28 | Modified Figure 1.1, Figure 1.2 and Figure 1.3. Modified Table 2.2 and Table 2.3. Modified Table 3.1. Deleted Table 3.2. (Table 3.2 is the same as Table 4.1.) Modified description in 5.4.                              |

| 1.5      | 2018-07-09 | Added description to power consumption. Modified Table 3.1.                                                                                                                                                              |

| 1.66     | 2020-12-15 | Modified Figure 3.1                                                                                                                                                                                                      |

#### RESTRICTIONS ON PRODUCT USE

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE

EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH

MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT

("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes,

without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, lifesaving and/or life

supporting medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling

equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, and devices

related to power plant. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT.

For details, please contact your TOSHIBA sales representative or contact us via our website.

- · Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any

applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE

FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY

WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR

LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND

LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO

SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS

FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product.

Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES

OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION

https://toshiba.semicon-storage.com/