# ww.DataSheet4U.co

# **TOSHIBA MOS MEMORY PRODUCTS**

# TC524257P/Z/J-10, TC524257P/Z/J-12

#### DESCRIPTION

The TC524257P/Z/J is a CMOS Multiport memory equipped with a 262,144-word × 4 bit dynamic random access memory(RAM) port and a 512-word × 4 bit static serial access memory(SAM) port. In addition to the conventional DRAM operation modes, the TC524257P/Z/J features a logic function and a write-per-bit function on the RAM port; Bi-directional transfer capability between the DRAM memory array and the SAM data register and a high speed serial read/write capability on the SAM port. The RAM port and the SAM port can be accessed independently except when data is being transferred between them internally. The TC524257P/Z/J is fabricated using TOSHIBA's CMOS silicon gate process technology as well as advanced circuitry to provide low power dissipation and wide operating margin. Multiplexed address inputs and a common input/output organization allow the TC524257P/Z/J to be housed in a standard 28-pin, 400-mil wide plastic DIP and 400-mil height ZIP, and in a standard 32-pin 400-mil wide plastic SOJ. System oriented features include a single 5V±10% power supply operation and compatibility with high performance schottky TTL logic.

#### **FEATURES**

|                    | ITEM                                  | TC52425 | 7P/Z/J |

|--------------------|---------------------------------------|---------|--------|

|                    | 11141                                 | -10     | -12    |

| t <sub>RAC</sub>   | RAS Access Time (Max.)                | 100ns   | 120ns  |

| t CAC              | CAS Access Time (Max.)                | 50ns    | 60ns   |

| tRC                | Cycle Time (Min.)                     | 190ns   | 220ns  |

| tPC                | Page Mode Cycle Time(Min.)            | 90ns    | 105ns  |

| t <sub>SCA</sub>   | Serial Access Time (Max.)             | 25ns    | 35ns   |

| t <sub>SCC</sub>   | Serial Cycle Time (Min.)              | 30ns    | 40ns   |

| 1 <sub>CC1</sub>   | RAM: Operating Current (SAM: Standby) | 70mA    | 60mA   |

| I <sub>CC2</sub> A | SAM Operating Current (RAM: Standby)  | 50mA    | 45mA   |

| ICC2               | RAM/SAM<br>Standby Current            | 10      | )mA    |

- · Organization

- RAM port: 262,144 words × 4 bits SAM port: 512 words × 4 bits

- Single power supply of 5V±10% with a builtin V<sub>BB</sub> generator

- Read-Modify-Write, CAS before RAS refresh, Hidden refresh, Page mode, Write-Per-Bit, Raster operation, Read transfer, Write transfer, Serial read, Serial Write capability.

- · All inputs and outputs TTL compatible

- 512 refresh cycle/Sms

- · Package

- TC524257P: 0.4 inches 28 pins standard

- Plastic DIP

- TC524257Z: 0.4 inches 28 pins standard

- Plastic ZIP

- TC524257J: 0.4 inches 32 pins standard Plastic SOJ

#### PIN NAMES

| A0 ∿ A8         | Address Inputs                 |

|-----------------|--------------------------------|

| RAS             | Row Address Strobe             |

| CAS             | Column Address Strobe          |

| DT/OE           | Data Transfer/Output<br>Enable |

| WB/WE           | Write Per Bit/Write<br>Enable  |

| W1/IO1 ~ W4/IO4 | Write Mask/Data IN,<br>OUT     |

| SC              | Serial Clock                   |

| SE              | Serial Enable                  |

| SI01 ∿ SI04     | Serial Input Output            |

| V <sub>CC</sub> | Power (+5V)                    |

| V <sub>SS</sub> | Ground                         |

| N.C.            | No Connection                  |

#### PIN CONNECTION (TOP VIEW)

| , 1 00.             |                    | (                 |                             |                             |

|---------------------|--------------------|-------------------|-----------------------------|-----------------------------|

| Plast:              | ic DIP             | Plastic ZIP       | Plasti                      | c SOJ                       |

| scol                | 28 V <sub>SS</sub> | N.C. 1   W3/103   | N.C. 1                      | 32 <b>)</b> V <sub>SS</sub> |

| SI01 <b>d</b> 2     | 27 <b>1</b> SI04   | W4/I043 -4 SE     | ន <b>េ[</b> ឧ               | 31 <b>5</b> VSS             |

| SI02 <b>1</b> 3     | <b>26</b> SI 03    | SI03 5 6 SI04     | 8101 <b>[</b> 3             | 30 <b>)</b> SI04            |

| DT/OEC4             | 25 SE              | Vss 7 8 sc        | SI02 <b>[4</b>              | 29 <b>1</b> S103            |

| W1/101 <b>0</b> 5   | 24 W4/I04          | S101 9 10 S102    | DT∕OE <b>d</b> 5            | 28 <b>)</b> SE              |

|                     | 23 W3./103         | DT/OE H 12 W1/101 | W1/101 <b>0</b> 6           | 27 W4/104                   |

| WB/WED7             | 22 N.C.            | W2/IO2 F TA WB/WE | w2∕102 <b>0</b> 7           | 26 W3/103                   |

| N.C. 68             | 21) CAS            | N.C. 15 16 RAS    | WB∕WEX 8                    | 250 N.C.                    |

| RAS 09              | <b>201</b> и.с.    | A8 17 18 A5       | и.с. <b>ц</b> 9             | 24 CAS                      |

| A8 <b>0</b> 10      | 19 <b>1</b> AO     | A5 19 50          | PAS <b>[</b> 10             | 23 <b>)</b> N.C.            |

| A6 <b>0</b> 11      | 18 <b>3</b> A1     | Voc 21 22 A7      | 48 <b>d</b> 11              | 22 <b>1</b> A0              |

| A5 12               | 17 <b>1</b> A2     | A3 23 724 A2      | A6 <b>[</b> 12              | 21 <b>5</b> Al              |

| A4 1 13             | 16 <b>1</b> A3     | A1 25 26 A0       | A5 <b>[</b> 13              | 20 1 A2                     |

| V <sub>CC</sub> (14 | 15 <b>1</b> A7     | N.C. 27 28 CAS    | A4 <b>0</b> 14              | 19 <b>1</b> A3              |

| · 1                 |                    | LZA SAG           | V <sub>CC</sub> <b>1</b> 15 | 18 <b>1</b> A7              |

|                     |                    |                   | VCC <b>I</b> 16             | 17 <b>1</b> N.C.            |

|                     |                    |                   |                             |                             |

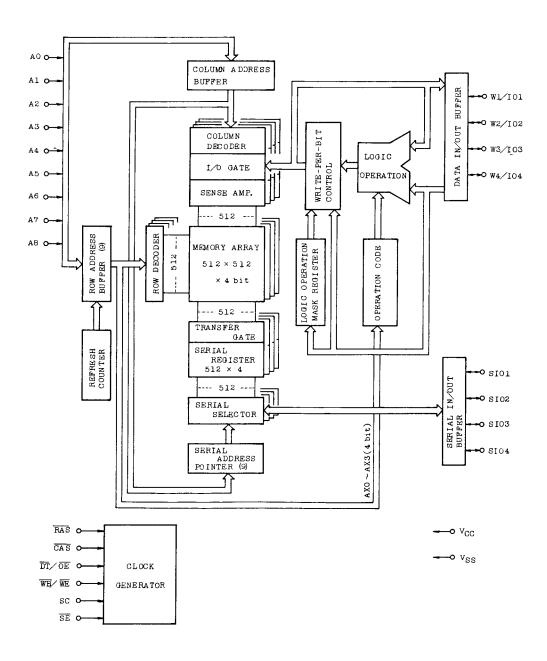

#### **BLOCK DIAGRAM**

## ABSOLUTE MAXIMUM RATINGS

| SYMBOL                           | ITEM                         | RATING     | UNITS  | NOTES |

|----------------------------------|------------------------------|------------|--------|-------|

| V <sub>IN</sub> V <sub>OUT</sub> | Input Output Voltage         | -1.0 ~ 7.0 | v      | 1     |

| V <sub>CC</sub>                  | Power Supply Voltage         | -1.0 ~ 7.0 | v      | 1     |

| Topr                             | Operating Temperature        | 0 ∿ 70     | °C     | 1     |

| T <sub>stg</sub>                 | Storage Temperature          | -55 ∿ 150  | °C     | 1     |

| TSOLDER                          | Soldering Temperature • Time | 260 • 10   | °C•sec | 1     |

| PD                               | Power Dissipation            | 1          | W      | 1     |

| IOUT                             | Short Circuit Output Current | 50         | mA     | 1     |

#### RECOMMENDED DC OPERATING CONDITION (Ta=0 ~ 70°C)

| RECOMMENT       | JED DC OF ERRYTHA CONDITION | 1 1/277 | TYP. | MAX. | UNIT | NOTES |

|-----------------|-----------------------------|---------|------|------|------|-------|

| SYMBOL          | PARAMETER                   | MIN.    | lir. | MAA. | UNII | HOTEL |

| V <sub>CC</sub> | Power Supply Voltage        | 4.5     | 5.0  | 5.5  | V    | 2     |

| VIH             | Input High Voltage          | 2.4     | -    | 6.5  | V    | 2     |

| VIL             | Input Low Voltage           | -1.0    | -    | 0.8  | V    | 2     |

# DC ELECTRICAL CHARACTERISTICS (V<sub>CC</sub>=5V $\pm$ 10%, Ta=0 $\sim$ 70°C)

| DO ELLO           | TRICAL CHARACTERISTICS ( CC )                                              | <del></del> | TC524 | 257P/ | TC5242 | 257P/ |       |       |

|-------------------|----------------------------------------------------------------------------|-------------|-------|-------|--------|-------|-------|-------|

| SYMBOL            | ITEM (RAM Port)                                                            | SAM         |       | -10   | Z/J-   |       | UNITS | NOTES |

| STABOL            | 111111 (111111 )                                                           | Port        | MIN.  | MAX.  | MIN.   | MAX.  |       |       |

| I <sub>CC1</sub>  | OPERATING CURRENT                                                          | Standby     | -     | 70    | -      | 60    | m.A.  | 3,4   |

| I <sub>CC1A</sub> | (RAS, CAS Cycling: tRC=tRC MIN.)                                           | Active      |       | 110   | -      | 100   | 11121 | 3,4   |

| I <sub>CC2</sub>  | STANDBY CURRENT                                                            | Standby     |       | 10    |        | 10    | mA.   |       |

| I <sub>CC2A</sub> | (RAS, CAS=V <sub>IH</sub> )                                                | Active      | -     | 50    | _      | 45    |       | 3,4   |

| I <sub>CC3</sub>  | RAS ONLY REFRESH CURRENT                                                   | Standby     |       | 70    |        | 60    | m.A   | 3     |

| I <sub>CC3A</sub> | (RAS Cycling, CAS=VIH: tRC=tRC MIN.)                                       | Active      | -     | 110   |        | 100   |       | 3,4   |

| I <sub>CC4</sub>  | PAGE MODE CURRENT                                                          | Standby     | -     | 60    |        | 50    | m.A   | 3,4   |

| ICC4A             | (RAS=V <sub>IL</sub> , CAS Cycling: t <sub>PC</sub> =t <sub>PC</sub> MIN.) | Active      | -     | 100   |        | 90    |       | 3,4   |

| I <sub>CC5</sub>  | CAS BEFORE RAS REFRESH CURRENT                                             | Stadnby     | -     | 70    |        | 60    | mA.   | 3     |

| I <sub>CC5A</sub> | (CAS Before RAS Cycling:tRC=tRC MIN.)                                      | Active      | -     | 110   |        | 100   |       | 3,4_  |

|                   | DATA TRANSFER CURRENT                                                      | Standby     | -     | 80    |        | 75    | mA    | 3     |

| I <sub>CC6A</sub> | (RAS, CAS Cycling: tRC=tRC MIN.)                                           | Active      | -     | 130   |        | 120   |       | 3,4   |

| SYMBOL            | ITEM                                                                      | MIN. | TYP. | MAX. | UNITS | NOTES |

|-------------------|---------------------------------------------------------------------------|------|------|------|-------|-------|

| I <sub>I(L)</sub> | INPUT LEAKAGE CURRENT (OV = VIN = 6.5V, All Other Pins Not Under Test=OV) | -10  | 0    | 10   | μА    |       |

|                   | OUTPUT LEAKAGE CURRENT (Output is disabled, OV \(^{V}\)OUT \(^{5.5V}\)    | -10  | 0    | 10   | μA    |       |

|                   | OUTPUT HIGH LEVEL VOLTAGE (Wi/IOi, SlOi IOUT=-2mA)                        | 2.4  | _    |      | V     |       |

| v <sub>OL</sub>   | OUTPUT LOW LEVEL VOLTAGE (Wi/IOi IOUT=+4.2mA, SIOi IOUT=+2mA)             |      | _    | 0.4  | V     |       |

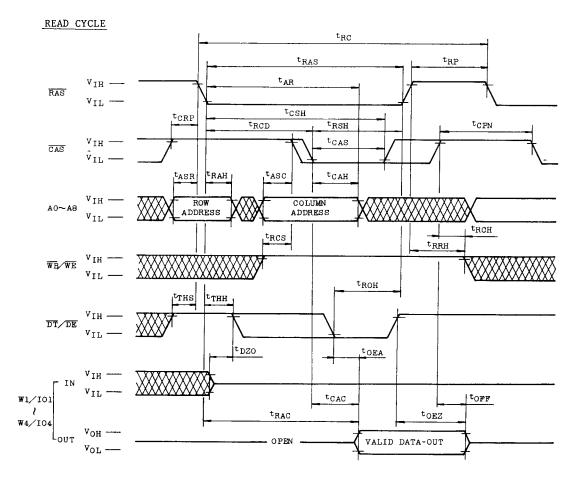

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS  $\ensuremath{\mathsf{C}}$

$(V_{CC}=5V\pm10\%, Ta=0 \sim 70^{\circ}C)$  (NOTES 5, 6, 7)

| SYMBOL           | PARAMETER                                                     |      | 24257P/<br>J-10 |      | 24257P/<br>/J-12 | IINITT | NOTES |

|------------------|---------------------------------------------------------------|------|-----------------|------|------------------|--------|-------|

| 0111202          | IMMILIER                                                      | MIN. | т               | MIN. | T                | UNII   | NOTE. |

| t <sub>RC</sub>  | Random Read or Write Cycle Time                               | 190  |                 | 220  |                  |        |       |

| tRWC             | Read-Write Cycle Time                                         | 250  | 1               | 290  |                  | 1      |       |

| tPC              | Page Mode Cycle Time                                          | 90   |                 | 105  | ļ                | 1      |       |

| tPRWC            | Page Mode Read-Write Cycle Time                               | 150  |                 | 175  |                  | 1      |       |

| t <sub>RAC</sub> | Access Time from RAS                                          | 1    | 100             |      | 120              | 1      | 8,14  |

| tCAC             | Access Time from CAS                                          |      | 50              |      | 60               | [      | 8,14  |

| tOFF             | Output Buffer Turn-Off Delay                                  | 0    | 30              | 0    | 35               |        | 10    |

| t <sub>T</sub>   | Transition Time (Rise and Fall)                               | 3    | 35              | 3    | 35               |        | 7     |

| t <sub>RP</sub>  | RAS Precharge Time                                            | 80   |                 | 90   | T                |        |       |

| t <sub>RAS</sub> | RAS Pulse Width                                               | 100  | 10,000          | 120  | 10,000           |        |       |

| t <sub>RSH</sub> | RAS Hold Time                                                 | 50   |                 | 60   |                  |        |       |

| t <sub>CSH</sub> | CAS Hold Time                                                 | 100  |                 | 120  |                  |        |       |

| tCAS             | CAS Pulse Width                                               | 50   |                 | 60   |                  |        |       |

| tRCD             | RAS to CAS Delay Time                                         | 20   | 50              | 25   | 60               |        |       |

| tCRP             | CAS to RAS Precharge Time                                     | 10   |                 | 10   |                  |        |       |

| t <sub>CPN</sub> | CAS Precharge Time                                            | 15   |                 | 20   |                  | ns     |       |

| t <sub>CP</sub>  | CAS Precharge Time (Page Mode)                                | 30   |                 | 35   |                  |        |       |

| tASR             | Row Address Set-Up Time                                       | 0    |                 | 0    |                  |        |       |

| t <sub>RAH</sub> | Row Address Hold Time                                         | 10   |                 | 15   |                  |        |       |

| t <sub>ASC</sub> | Column Address Set-Up Time                                    | 0    |                 | 0    |                  | Ì      |       |

| t <sub>CAH</sub> | Column Address Hold Time                                      | 20   |                 | 25   |                  |        |       |

| t <sub>AR</sub>  | Column Address Hold Time referenced to $\overline{RAS}$       | 70   |                 | 85   |                  |        |       |

| tRCS             | Read Command Set-Up Time                                      | 0    |                 | 0    |                  | ľ      |       |

| t <sub>RCH</sub> | Read Command Hold Time                                        | 0    |                 | 0    |                  | ļ      | 11    |

| t <sub>RRH</sub> | Read Command Hold Time referenced to $\overline{RAS}$         | 10   |                 | 10   |                  |        | 11    |

| t <sub>WCH</sub> | Write Command Hold Time                                       | 20   |                 | 25   |                  | Ī      |       |

| t <sub>WCR</sub> | Write Command Hold Time referenced to $\overline{\text{RAS}}$ | 70   |                 | 85   |                  | Ì      |       |

| twp              | Write Command Pulse Width                                     | 20   |                 | 25   |                  | ľ      |       |

| t <sub>RWL</sub> | Write Command to $\overline{RAS}$ Lead Time                   | 30   |                 | 35   |                  | ļ      |       |

| t <sub>CWL</sub> | Write Command to CAS Lead Time                                | 30   |                 | 35   |                  | F      |       |

| t <sub>DS</sub>  | Data Set-Up Time                                              | 0    |                 | 0    |                  |        | 12    |

| t <sub>DH</sub>  | Data Hold Time                                                | 20   |                 | 25   |                  |        | 12    |

| ERASP            | RAS Pulse Width (Page Mode)                                   | 190  | 100,000         | 225  | 100,000          | ļ      |       |

ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITION (Continued)

| SYMBOL           | PARAMETER                                                    |      | 257F/<br>-10 | TC524<br>Z/J- |      | UNITS | NOTES |

|------------------|--------------------------------------------------------------|------|--------------|---------------|------|-------|-------|

|                  |                                                              | MIN. | MAX.         | MIN.          | MAX. |       |       |

| t <sub>DHR</sub> | Data Hold Time referenced to RAS                             | 70   |              | 85            |      |       |       |

| twcs             | Write Command Set-Up Time                                    | 0    |              | 0             |      |       | 13    |

| tRWD             | RAS to WE Delay Time                                         | 125  |              | 150           |      |       | 13    |

| tCWD             | CAS to WE Delay Time                                         | 75   |              | 90            |      |       | 13    |

| tDZC             | Data to CAS Delay Time                                       | 0    |              | 0             |      |       |       |

| t <sub>DZO</sub> | Data to $\overline{\text{OE}}$ Delay Time                    | 0    |              | 0             |      |       |       |

| t <sub>OEA</sub> | Access Time from OE                                          |      | 25           |               | 30   |       |       |

| t <sub>OEZ</sub> | Output Buffer Turn-Off Delay from $\overline{\text{OE}}$     | 0    | 20           | 0             | 25   | ns    | 10    |

| t <sub>OED</sub> | OE to Data Input Delay Time                                  | 20   |              | 25            |      |       |       |

| tOEH             | OE Command Hold Time                                         | 20   |              | 20            |      |       |       |

| t <sub>ROH</sub> | RAS Hold Time referenced to $\overline{\text{OE}}$           | 20   |              | 20            |      |       |       |

| tCSR             | CAS Set-Up Time for CAS Before RAS Cycle                     | 10   |              | 10            |      |       |       |

| t <sub>CHR</sub> | CAS Hold Time for CAS Before RAS Cycle                       | 20   |              | 20            |      |       |       |

| tRPC             | RAS Precharge to CAS Active Time                             | 0    |              | 0             |      | 1     |       |

| t <sub>CPT</sub> | CAS Precharge Time for CAS Before RAS Counter<br>Test        | 40   |              | 50            |      |       |       |

| tREF             | Refresh Period                                               |      | 8            |               | 8    | ms    | L     |

| twsR             | WB Set-Up Time                                               | 0    |              | 0             |      |       |       |

| tRWH             | WB Hold Time                                                 | 10   |              | 15            |      |       |       |

| t <sub>MS</sub>  | Write-Per-Bit Mask Data Set-Up Time                          | 0    |              | 0             |      |       |       |

| tмн              | Write-Per-Bit Mask Data Hold Time                            | 10   |              | 15            |      |       |       |

| t <sub>THS</sub> | DT High Set-Up Time                                          | 0    |              | 0             |      |       |       |

| tTHH             | DT High Hold Time                                            | 10   |              | 15            |      |       |       |

| tTLS             | DT Low Set-Up Time                                           | 0    | 1            | 0             |      |       |       |

| tTLH             | DT Low Hold Time                                             | 10   |              | 15            |      | ns    |       |

| t <sub>RTH</sub> | DT Low Hold Time referenced to RAS (Real Time Read Transfer) | 80   |              | 95            |      |       |       |

| tCTH             | DT Low Hold Time referenced to CAS (Real Time Read Transfer) | 30   |              | 35            |      |       |       |

| t <sub>ESR</sub> | SE Set-Up Time referenced to RAS                             | 0    |              | 0             | ļ    |       |       |

| t <sub>REH</sub> | SE Hold Time referenced to RAS                               | 10   | 1            | 15            |      | _     |       |

| tTRD             | DT to RAS Delay Time (Read Transfer)                         | 0    |              | 0             |      |       |       |

| t <sub>RP</sub>  | DT Prechaege Time                                            | 30   |              | 35            |      |       | L     |

| tRSD             | RAS to First SC Delay Time (Read Transfer)                   | 100  |              | 120           |      | 1     |       |

# ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITION (Continued)

|                  |                                                                      |      | 257P/<br>J-10 |             | 257P/ | VINT III | мотра                                            |

|------------------|----------------------------------------------------------------------|------|---------------|-------------|-------|----------|--------------------------------------------------|

| SYMBOL           | PARAMETER                                                            | MIN. | MAX.          | Z/J<br>MIN. | MAX.  | UNIT     | NOTES                                            |

| t <sub>CSD</sub> | CAS to First SC Dealy Time (Read Transfer)                           | 50   |               | 60          |       | -        | <del>                                     </del> |

| t <sub>TSL</sub> | Last SC to DT Lead Time<br>(Real Time Read Transfer)                 | 5    |               | 10          |       |          |                                                  |

| tTSD             | DT to First SC Delay Time (Read Transfer)                            | 15   |               | 20          | ļ —   |          |                                                  |

| t <sub>SRS</sub> | Last SC to RAS Set-Up Time (Serial Input)                            | 30   |               | 40          |       |          |                                                  |

| t <sub>SRD</sub> | RAS to First SC Delay Time (Serial Input)                            | 25   |               | 30          |       |          |                                                  |

| tSDD             | RAS to Serial Input Delay Time                                       | 50   |               | 60          |       |          |                                                  |

| t <sub>SDZ</sub> | Serial Output Buffer Turn-Off Delay from RAS (Pseudo Write Transfer) | 10   | 50            | 10          | 60    |          | 10                                               |

| t <sub>SZS</sub> | Serial Input to First SC Delay Time                                  | 0    |               | 0           |       |          |                                                  |

| tscc             | SC Cycle Time                                                        | 30   |               | 40          |       |          |                                                  |

| t <sub>SC</sub>  | SC Pulse Width (SC High Time)                                        | 10   |               | 15          |       |          |                                                  |

| t <sub>SCP</sub> | SC Precharge Time (SC Low Time)                                      | 10   |               | 15          |       | ns       |                                                  |

| tSCA             | Access Time from SC                                                  |      | 25            |             | 35    |          | 9                                                |

| <sup>t</sup> son | Serial Output Hold Time from SC                                      | 5    |               | 5           |       |          |                                                  |

| t <sub>SDS</sub> | Serial Input Set-Up Time                                             | 0    |               | 0           |       |          |                                                  |

| t <sub>SDH</sub> | Serial Input Hold Time                                               | 20   |               | 30          |       |          |                                                  |

| t <sub>SEA</sub> | Access Time from SE                                                  |      | 25            |             | 35    |          | 9                                                |

| tSE              | SE Pulse Width                                                       | 25   |               | 35          |       |          |                                                  |

| t <sub>SEP</sub> | SE Precharge Time                                                    | 25   |               | 35          |       |          |                                                  |

| t <sub>SEZ</sub> | Serial Output Buffer Turn-Off Delay from $\overline{\text{SE}}$      | 0    | 20            | 0           | 30    |          | 10                                               |

| t <sub>SZE</sub> | Serial Input to $\overline{	ext{SE}}$ Delay Time                     | 0    |               | 0           |       | Ì        |                                                  |

| tsws             | Serial Write Enable Set-Up Time                                      | 5    |               | 10          |       | ľ        |                                                  |

| t <sub>SEH</sub> | Serial Write Enable Hold Time                                        | 15   |               | 20          |       | Ţ        |                                                  |

| tswis            | Serial Write Disable Set-Up Time                                     | 5    |               | 10          |       |          |                                                  |

| tSWIH            | Serial Write Disable Hold Time                                       | 15   |               | 20          |       | Ī        |                                                  |

|                  |                                                                      |      |               |             |       |          |                                                  |

# RASTER OPERATION WRITE CYCLE ELECTRICAL CHARACTERISTICS AND RECOMMENDED AC OPERATING CONDITIONS

$(V_{CC}=5V\pm10\%, Ta=0 \sim 70$ °C) (NOTES 5, 6, 7)

| SYMBOL            | PARAMETER                       |      | TC524257P/<br>Z/J-10 |      | TC524257P/<br>Z/J-12 |    | NOTES |

|-------------------|---------------------------------|------|----------------------|------|----------------------|----|-------|

| JIIDOL            | ******                          | MIN. | MAX.                 | MIN. | MAX.                 |    |       |

| tFRC              | Write Cycle Time                | 220  |                      | 260  |                      |    | 15    |

| tFRWC             | Read-Write Cycle Time           | 280  |                      | 330  |                      |    | 15    |

| t <sub>FPC</sub>  | Page Mode Write Cycle Time      | 120  |                      | 145  |                      |    | 15    |

| tFPRWC            | Page Mode Read-Write Cycle Time | 180  |                      | 215  |                      |    | 15    |

| tFRAS             | -RAS Pulse Width                | 130  |                      | 160  |                      | ns | 15    |

| t <sub>FRSH</sub> | RAS Hold Time                   | 80   |                      | 100  |                      |    | 15    |

| t <sub>FCSH</sub> | CAS Hold Time                   | 130  |                      | 160  |                      |    | 15    |

| t <sub>FCAS</sub> | CAS Pulse Width                 | 80   |                      | 100  |                      |    | 15    |

| tFRWL             | Write Command to RAS Lead Time  | 60   |                      | 75   |                      |    | 15    |

| tFCWL             | Write Command to CAS Lead Time  | 60   |                      | 75   |                      |    | 15    |

## CAPACITANCE ( $V_{CC}=5V\pm10\%$ , f=1MHz, Ta=0 $\sim70^{\circ}$ C)

| SYMBOL           | PARAMETER                                          | MIN. | MAX. | UNIT    |

|------------------|----------------------------------------------------|------|------|---------|

| c <sub>I1</sub>  | Input Capacitance (A0 ∿ A8)                        | _    | 8    |         |

| c <sub>12</sub>  | Input Capacitance (RAS, CAS, DT/OE, WB/WE, SC, SE) | -    | 8    | pF      |

| c <sub>101</sub> | Input/Output Capacitance (W1/IO1 ~ W4/IO4)         | -    | 10   | ] Pr    |

| C <sub>102</sub> | Input/Output Capacitance (SIO1 ~ SIO4)             |      | 10   | <u></u> |

#### NOTES:

- Stresses greater than those listed under "Absolute Maximum Ratings" may cause permanent damage to the device.

- All voltages are referenced to V<sub>SS</sub>.

- 3. These parameters depend on cycle rate.

- These parameters depend on output loading. Specified values are obtained with the output open.

- 5. Power must be applied to the RAS and DT/OE input signals to pull them "high" before or at the same time as the VCC supply is turned on. After power-up, a pause of 200 μseconds minimum is required with RAS and DT/OE held "high." After the pause, a minimum of eight (8) RAS and (8) SC dummy cycles must be performed to stabilize the internal circuitry, before valid read, write or transfer operations can begin. During the initialization period, the DT/OE signal must be held "high." If the internal refresh counter is used, a minimum (8) CAS-before-RAS initialization cycles are required instead of (8) RAS cycles.

- AC measurements assume t<sub>T</sub>=5ns.

- V<sub>IH</sub> (min.) and V<sub>IL</sub> (max.) are reference levels for measuring timing of input signals. Also, transition times are measured between V<sub>IH</sub> and V<sub>IL</sub>.

- 8. RAM port outputs are measured with a load equivalent to 2 TTL loads and 100pF.

- SAM port outputs are measured with a load equivalent to 2 TTL loads and 30pF. D<sub>OUT</sub> comparator level: V<sub>OH</sub>/V<sub>OL</sub>=2.0V/0.8V.

- t<sub>OFF</sub> (max.), t<sub>OEZ</sub> (max.), t<sub>SDZ</sub> (max.) and t<sub>SEZ</sub> (max.) define the time at which the outputs achieve the open circuit condition and are not referenced to output voltage levels.

- 11. Either t<sub>RCH</sub> or t<sub>RRH</sub> must be satisfied for a read cycle.

- These parameters are referenced to CAS leading edge of early write cycles and to WB/WE leading edge in read-write cycles.

- 13. t<sub>WCS</sub>, t<sub>RWD</sub> and t<sub>CWD</sub> are not restrictive operating parameters. They are included in the data sheet as electrical characteristics only. If t<sub>WCS</sub> ≥ t<sub>WCS</sub> (min.), the cycle is an early write cycle and the data out pin will remain open circuit (high impedance) throughout the entire cycle; if t<sub>RWD</sub>≥t<sub>RWD</sub> (min.) and t<sub>CWD</sub>≥ t<sub>CWD</sub> (min.), the cycle is a read-write cycle and the data out will contain data read from the selected cell: If neither of the above sets of conditions is satisfied, the condition of the data out (at access time) is indeterminate.

- 14. Operation within the  $t_{RCD}$  (max.) limit insures that  $t_{RAC}$  (max.) can be met.  $t_{RCD}$  (max.) is specified as a reference point only: If  $t_{RCD}$  is greater than the specified  $t_{RCD}$  (max.) limit, then access time is controlled by  $t_{CAC}$ .

DEVICE INFORMATION

RAM PORT OPERATION

#### Operation Truth Table

All operation modes of TC524257P/Z/J are determined by  $\overline{CAS}$ ,  $\overline{DT}/\overline{OE}$ ,  $\overline{WB}/\overline{WE}$ , and  $\overline{SE}$  at the falling edge of  $\overline{RAS}$ . They are shown in the following tabel 1.

| RAS | CAS | ADDRESS         | DT/OE | WB/WE | SĒ | FUNCTION                |  |  |

|-----|-----|-----------------|-------|-------|----|-------------------------|--|--|

| Н   | Н   | *               | *     | *     | *  | Standby                 |  |  |

|     | Н   | Valid           | H → L | Н     | *  | Read                    |  |  |

|     | Н   | Valid           | Н     | H → L | *  | Write                   |  |  |

|     | Н   | Valid(Row add.) | Н     | *     | *  | RAS only refresh        |  |  |

|     | L   | *               | H(1)  | Н     | *  | CAS-before-RAS Refresh  |  |  |

|     | Н   | Valid           | Н     | L     | *  | Write-per-Bit           |  |  |

|     | L   | Valid(A0 ~ A3)  | H(1)  | L     | *  | Raster Operation Set-up |  |  |

|     | Н   | Valid           | L     | Н     | *  | Read Transfer           |  |  |

|     | Н   | Valid           | L     | L     | L  | Write Transfer          |  |  |

|     | Н   | Valid           | L     | L     | Н  | Pseudo-Write Transfer   |  |  |

Table 1: Functional Truth Table

Note; H: VIH, L: VIL, \*: VIH or VIL

(1) The input level of  $\overline{DT}/\overline{OE}$  in the  $\overline{CAS}$  before  $\overline{RAS}$  timing is not ristricted. However it is recommended that  $\overline{DT}/\overline{OE}$  be held 'High' because this input will be used for future expansion of the operation mode.

#### ADDRESSING

The 18 address bits required to decode 4-bits of the 1,048,576 cell locations within the Dynamic RAM memory array of the TC524257P/Z/J, are multiplexed onto 9 address input pins (A0  $\sim$  A8). Nine row-address bits are latched on the falling edge of the row address strobe ( $\overline{RAS}$ ) and the following nine column address bits are latched on the falling edge of the column address strobe ( $\overline{CAS}$ ).

#### DATA TRANSFER/OUTPUT ENABLE (DT/OE)

The  $\overline{DT}/\overline{OE}$  input is a multifucntion pin. When  $\overline{DT}/\overline{OE}$  is 'High' at the falling edge of  $\overline{RAS}$ , a normal DRAM cycle is performed and this input is used as an output enable. When  $\overline{DT}/\overline{OE}$  is 'Low' at the falling edge of  $\overline{RAS}$ , a data transfer operation is started between the RAM port and the SAM port.

#### WRITE-PER-BIT/WRITE-ENABLE (WB/WE)

The  $\overline{\text{WB}}/\overline{\text{WE}}$  input is also a multifunction pin. For conventional DRAM cycle, the  $\overline{\text{WB}}/\overline{\text{WE}}$  input is used in the same manner as standard DRAMs except when the write-per-bit function or the raster operation are used. When  $\overline{\text{WB}}/\overline{\text{WE}}$  is 'low' at the falling edge of  $\overline{\text{RAS}}$ , the bit write-mask is enabled. When  $\overline{\text{WB}}/\overline{\text{WE}}$  and  $\overline{\text{CAS}}$  are 'low' at the falling edge of  $\overline{\text{RAS}}$ , the raster operation set-up cycle is executed.

The  $\overline{\text{WB}}/\overline{\text{WE}}$  input also determines the direction of data transfer between the DRAM memory array and the serial register. When  $\overline{\text{WB}}/\overline{\text{WE}}$  is 'high' at the falling edge of  $\overline{\text{RAS}}$ , the data is transferred from RAM to SAM (read-transfer cycle). When  $\overline{\text{WB}}/\overline{\text{WE}}$  is 'low' at the falling edge of  $\overline{\text{RAS}}$ , the data is transferred from SAM to RAM (write-transfer cycle).

#### WRITE-MASK DATA/DATA INPUT/OUTPUT (W1/101 to W4/104)

When the write-per-bit function is enabled, the mask data on the W1/I01 pins is latched into the write-mask register WM1 at the falling edge of  $\overline{\text{RAS}}$ . Data is written into the DRAM on data lines where the write-mask data is a logic '1'. Writing is inhibited on data lines where the write-mask data is a logic '0'. The write-mask data is valid for only one cycle except for during raster operation. In the raster operation set-up cycle, the mask data is latched into the write-mask register WM2 at the falling edge of  $\overline{\text{RAS}}$ . The write-mask selected during the raster operation set-up cycle remains valid for all subsequent raster operation write, read-modify-write or page-mode write cycles.

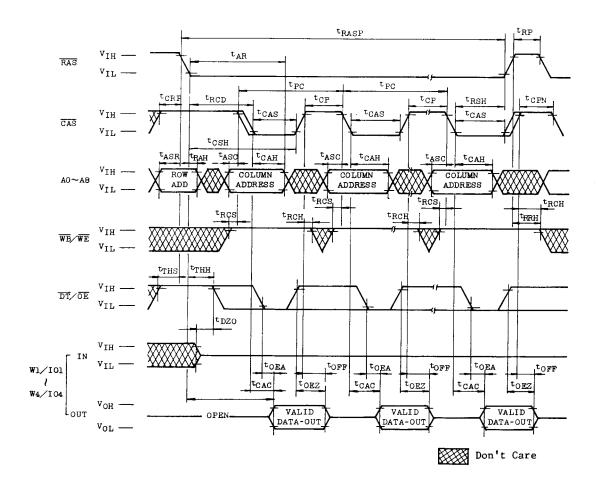

#### PAGE MODE

The page mode feature of the TC524257P/Z/J allows data to be transferred into or multiple column locations of the same row by having multiple column cycles during a single active  $\overline{\text{RAS}}$  cycle.

For the initial page mode access, the output data is valid after the specified access time from  $\overline{\text{RAS}}$ . For all subsequent page mode read operations, the output data is valid after the specified access time from  $\overline{\text{CAS}}$ . As a result, page mode operation reduces power dissipation and improves data access time.

When the write-per-bit function is enabled, the mask data specified in the first write operation, at the falling edge of  $\overline{RAS}$ , is maintained throughout the page mode write cycle.

#### RAS-ONLY REFRESH

The data in the DRAM cycle requires periodic refreshing to prevent data loss. Refreshing is accomplished by performing a memory cycle at each of the 512 rows in the DRAM array within the specified 8ms refresh period. Although any normal memory cycle will perform the refresh operation, this function is most easily accomplished with 'RAS-ONLY' cycles.

#### CAS-BEFORE-RAS REFRESH

The TC524257P/Z/J also offers an internal refresh function. When  $\overline{\text{CAS}}$  is held 'low' for a specified period (tcsr) before  $\overline{\text{RAS}}$  goes low, an internal refresh address counter and on-chip refresh control clock generators are enabled and an internal refresh operation takes place. When the refresh operation is completed, the internal refresh address counter is automatically incremented in preparation for the next  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  cycle. For successive  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh cycles,  $\overline{\text{CAS}}$  can remain low while cycling  $\overline{\text{RAS}}$ .

During a  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh cycle,  $\overline{\text{WB}}/\overline{\text{WE}}$  must be 'high' at the falling edge of  $\overline{\text{RAS}}$  to prevent a false raster operation set-up cycle from occurring.

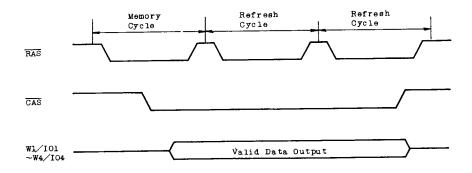

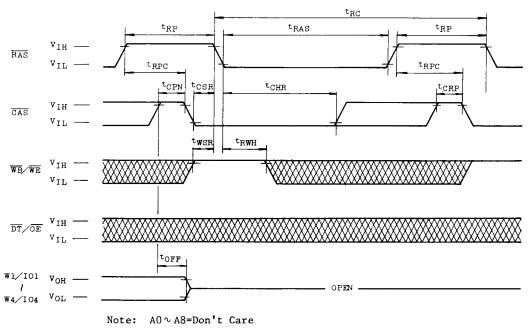

#### HIDDEN REFRESH

A hidden refresh is a  $\overline{\text{CAS}}$ -before- $\overline{\text{RAS}}$  refresh performed by holding  $\overline{\text{CAS}}$  'low' from a previous read cycle. This allows for the output data from the previous memory cycle to remain valid while performing a refresh. The internal refresh address counter provides the address and the refresh is accomplished by cycling  $\overline{\text{RAS}}$  after the specified  $\overline{\text{RAS}}$ -precharge period (refer to figure 1).

Figure 1: hidden refresh cycle

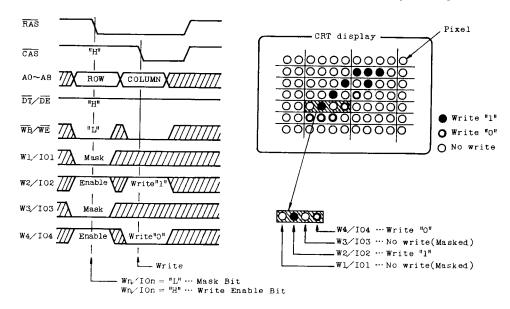

#### WRITE-PER-BIT FUNCTION

The write-per-bit function selectively controls the internal write-enable circuits of the RAM port. When  $\overline{\text{WB}}/\overline{\text{WE}}$  is held 'low' at the falling edge of  $\overline{\text{RAS}}$ , during a random access operation, the write-mask is enabled. At the same time, the mask data on the Wi/IOi pins is latched onto the write-mask register (WM1). When a '0' is sensed on any of the Wi/IOi pins, their corresponding write circuits are disabled and new data will not be wirtten.

When a '1' is sensed on any of the Wi/IOi pins, their corresponding write circuits will remain enabled so that new data is written. The truth table of the write-per-bit function is shown in table 2.

Table 2: Truth table for write-per-bit function

|     | At the | Function |                  |              |  |

|-----|--------|----------|------------------|--------------|--|

| CAS | DT/OE  | WB/WE    | Wi/IOi (i=1 ~ 4) | runction     |  |

| Н   | Н      | Н        | *                | Write Enable |  |

| Н   | н н г  |          | 1                | Write Enable |  |

|     |        |          | 0                | Write Mask   |  |

An example of the write-per-bit function illustrating its application to displays is shown in figures 2 and 3.

Figure 2: write-per-bit timing cycle

Figure 3: corresponding bit-map

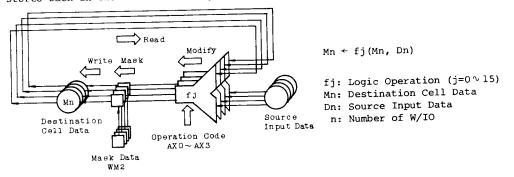

#### RASTER OPERATION

The TC524257P/Z/J features a logic function which provides 16 modes of raster operation. The desired logic function mode is selected during the raster operation set-up cycle and remains in effect until another selection is made. During raster operation, the TC524257P/Z/J performs internal logic operations when data is written through the RAM port. As shown in figure 4, the result (fj) of the logic operation, between the input data and the data residing in the accessed memory location is stored back in the accessed memory location.

Figure 4: block diagram of raster operation

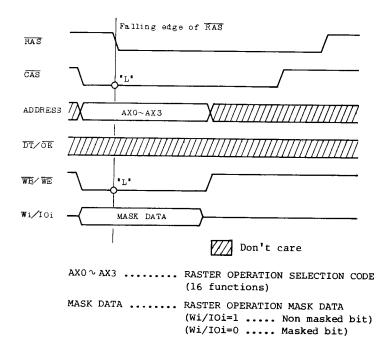

The row address inputs AXO thru AX3 are used as operation code input signals in the raster operation set-up cycle.

Table 3 lists the operation assigned to the sixteen logic function modes.

| Table 3: Truth table of raste | r operation |

|-------------------------------|-------------|

|-------------------------------|-------------|

| Operation Code |     |          | Code |               | Otion     | Note        | Operation Code |          |     |          | Symbol | Operation | Note |

|----------------|-----|----------|------|---------------|-----------|-------------|----------------|----------|-----|----------|--------|-----------|------|

| <u> </u>       | AX2 |          | AX0  | Symbol Symbol | Operation | Note        | AX3            | AX2      | AX1 | AX0      |        |           |      |

| 0              | 0   | 0        | 0    | ZERO          | 0         | *1          | 1              | 0        | 0   | 0        | NOR    | Dn + Mn   | *2   |

| 0              | 0   | 0        | 1    | AND1          | Dn • Mn   | *2          | 1              | 0        | 0   | 1        | ENOR   | Dn⊕Mn     | *2   |

| 0              | 0   | 1        | 0    | AND2          | Dn • Mn   | *2          | 1              | 0        | 1   | 0        | INV1   | Dn        | *1   |

| 0              | 0   | 1        | 1    | INHIBIT       | Mn        | *2          | 1              | 0        | 1   | 1        | OR2    | Dn + Mn   | *2   |

|                | 1   | 0        | 0    | AND3          | Dn • Mn   | *2          | 1              | 1        | 0   | 0        | INV2   | Mn        | *2   |

| 0              | 1-  | <u> </u> | 1-   | *3THROUGH     | Dn        | *1          | 1              | 1        | 0   | 1        | OR3    | Dn + Mn   | *2   |

| 0              | 1   | 0_       | 1    |               | Dn⊕Mn     | *2          | 1              | 1        | 1   | 0        | NAND   | Dn • Mn   | *2   |

| 0              | 1   | 1        | 0    | EOR           |           | ļ- <u>-</u> | 1              | 1        | 1   | 1        | ONE    | 1         | *1   |

| 0              | 1   | 1        | 1    | OR1           | Dn + Mn   | *2          | <u> </u>       | <u> </u> | 1   | <u> </u> | ONE    |           | L    |

Note: \*1 Normal write cycle timing is applied.

\*2 Raster operation write cycle timing must be applied.

\*3 The 'THROUGH' operation mode allows input data to be written directly into the selected memory location without raster operation. Therefore, 'THROUGH' is used to reset the raster operation.

Figure 5: Raster operation set-up cycle

Figure 5 shows the timing diagram for the raster operation set-up cycle. Both  $\overline{\text{CAS}}$  and  $\overline{\text{WB}}/\overline{\text{WE}}$  must be low at the falling edge of  $\overline{\text{RAS}}$ . At this point, the operation code specified by row addresses AXO thru AX3 determines the logic function to be performed and the mask data is latched into the write-mask register WM2. The logic function and mask data specified during the raster operation set-up cycle will remain in effect during all subsequent raster operation cycles, till another raster operation set-up cycle is executed to change the logic operation mode and mask data.

When the 'THROUGH' operation mode is selected, a logic operation is not performed but the mask data specified during the raster operation set-up cycle remains in effect during all subsequent raster operation cycles (persistent write per bit function).

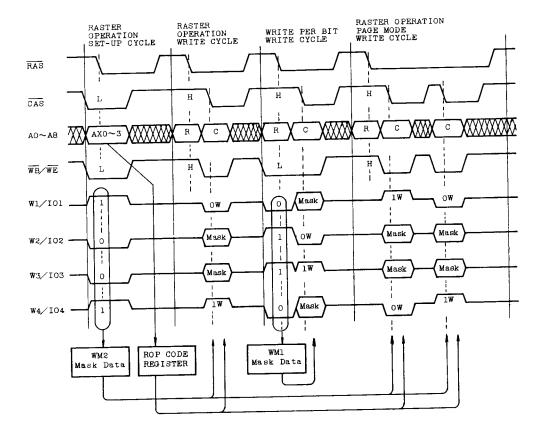

Figure 6 shows an example of raster operation cycles with a write-per-bit cycle mixed in the sequence. During the write-per-bit cycle, the raster operation is inhibited and the mask data in register WM1 is used while the mask data in register WM2 is ignored. In the subsequent raster operation page mode cycle, the raster operation is reactivated and the mask data in register WM2 is used again.

Figure 6: Example of raster operation

#### TRANSFER OPERATION

The TC524257P/Z/J features bi-directional transfer capability from RAM to SAM and from SAM to RAM. A transfer consists of loading 512 words by 4-bits of data from one port into the other. During a transfer cycle, RAM port and SAM port operations are restricted.

There are three types of transfer operations: read transfer, write transfer and pseudo-write transfer. As shown in table 4, the type of transfer operation is determined by  $\overline{\text{CAS}}$ ,  $\overline{\text{DT}}/\overline{\text{OE}}$ ,  $\overline{\text{WB}}/\overline{\text{WE}}$  and  $\overline{\text{SE}}$  at the falling edge of  $\overline{\text{RAS}}$ .

Table 4: Truth table of transfer operation

| At th | ne fallin | ng edge | of RAS |                                    | Transfer  |

|-------|-----------|---------|--------|------------------------------------|-----------|

| CAS   | DT/OE     | WB/WE   | SE     |                                    | direction |

| Н     | L         | Н       | *      | Read/real-time read transfer cycle | RAM → SAM |

| Н     | L         | L       | L      | Write-transfer cycle               | SAM → RAM |

| Н     | L         | L       | Н      | Pseudo-write transfer cycle        | _         |

\*: high or low

#### READ-TRANSFER CYCLE

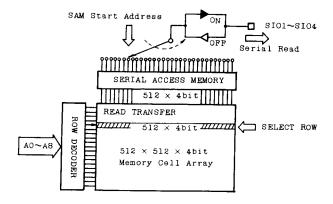

A read-transfer consists of loading a selected row of data from the RAM array into the SAM register. A read-transfer is accomplished by holding  $\overline{\text{CAS}}$  high,  $\overline{\text{DT}}/\overline{\text{OE}}$  low and  $\overline{\text{WB}}/\overline{\text{WE}}$  high at the falling edge of  $\overline{\text{RAS}}$ . The row address selected at the falling edge of  $\overline{\text{RAS}}$  determines the RAM row to be transferred into the SAM.

The actual data transfer completed at the rising edge of  $\overline{\text{DT}}/\overline{\text{DE}}$ . When the transfer is completed, the SIO lines are set into the output mode.

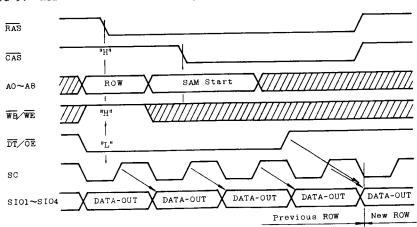

In a read/real-time read-transfer cycle, the transfer of a new row of data is completed at the rising edge of  $\overline{DT/OE}$  and becomes valid on the SIO lines after the specified access time t<sub>SCA</sub> from the rising edge of the subsequent serial clock(SC) cycle.

The start address of the serial pointer of the SAM is determined by the column address selected at the falling edge of  $\overline{\text{CAS}}$ . (refer to figure 7).

Figure 7: block diagram of RAM port and SAM port during read transfer

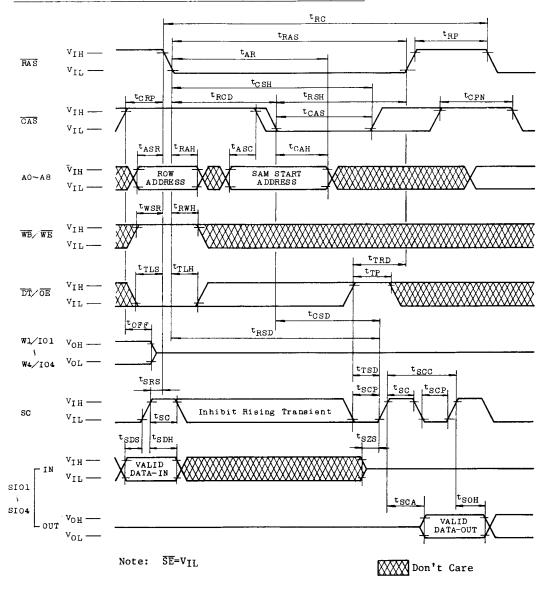

In a read-transfer cycle (which is preceded by a write-transfer cycle), the SC clock must be held at a constant V<sub>IL</sub> or V<sub>IH</sub>, after the SC precharge time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay t<sub>TSD</sub> from the rising edge of  $\overline{\text{DT}}/\overline{\text{OE}}$  (refer to Figure 8).

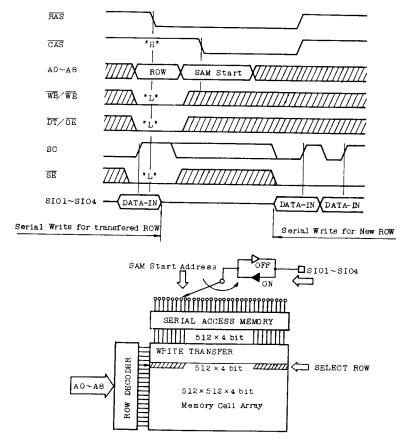

RAS "H" CAS SAM Start ROW A0~A8 WB/WE "H" DT/OE tTSD Inhibit rising transition SC <sup>t</sup>SCA DATA-OUT DATA-IN SI01~SI04

Figure 8: Read-transfer cycle (preceded by a write-transfer cycle)

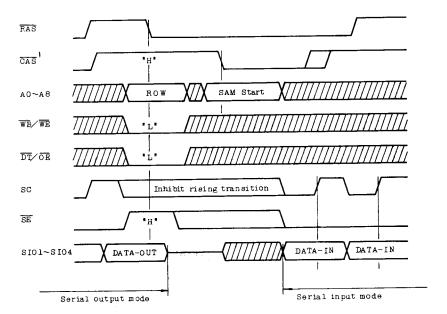

In a real-time read-transfer cycle (which is preceded by another read-transfer cycle), the previous row data appears on the SIO lines until the specified  $t_{SCA}$  access time from the same rising edge of SC.

This feature allows for the first bit of the new row of data to appear on the serial output as soon as the last bit of the previous row has been strobed, without any timing loss. To make this continuous data flow possible: the rising edge of  $\overline{DT}/\overline{OE}$  must be synchronized with  $\overline{RAS}$ ,  $\overline{CAS}$  and the subsequent rising edge of SC (refer to Figure 9).

Figure 9: Real-time read transfer cycle

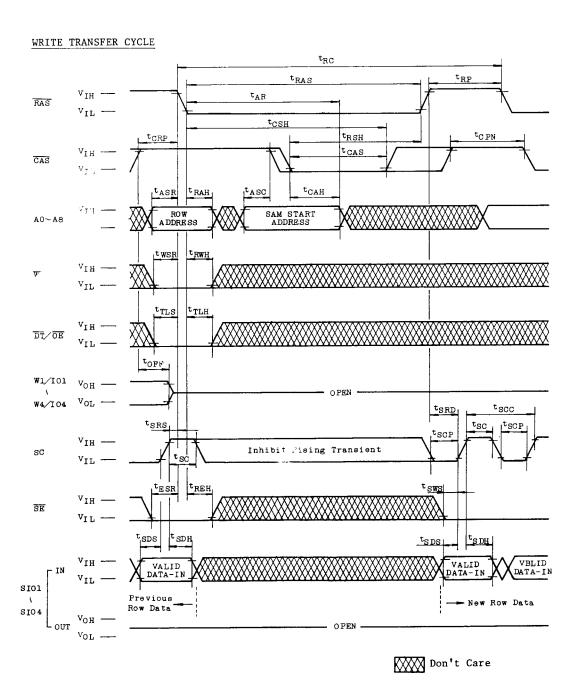

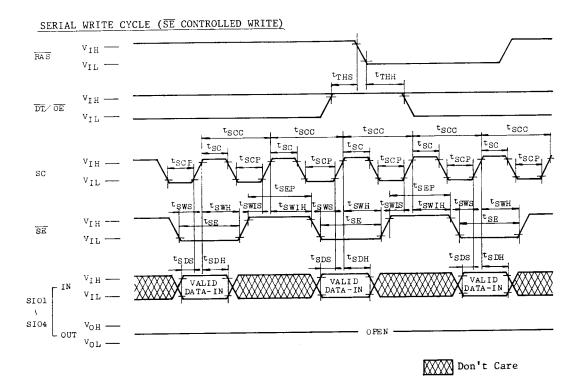

#### WRITE-TRANSFER CYCLE

A write-transfer cycle consists of loading the content of the SAM data register into a selected row of the RAM array. A write-transfer is accomplished by  $\overline{\text{CAS}}$  high,  $\overline{\text{DT}/\text{OE}}$  low,  $\overline{\text{WB}/\text{WE}}$  low and  $\overline{\text{SE}}$  low at the falling edge of  $\overline{\text{RAS}}$ . The row address selected at the falling edge of  $\overline{\text{RAS}}$  determines the RAM row address into which the data will be transferred. The column address selected at the falling edge of  $\overline{\text{CAS}}$  determines the start address of the serial pointer of the SAM. After the write-transfer is completed, the SIO lines are in the input mode so that serial data synchronized with SC can be loaded.

When two consecutive write-transfer operations are performed, there is a delay in availability between the last bit of the previous row and the first bit of the new row. Consequently the SC clock must be held at a constant  $v_{\rm IL}$  or  $v_{\rm IH}$  after the SC precharge time tsc-has seen satisfied, a rising edge of the SC clock until after a specified delay tsr from the rising edge of  $\overline{\rm RAS}$  (refer to figure 10).

Figure 10: Write-transfer cycle

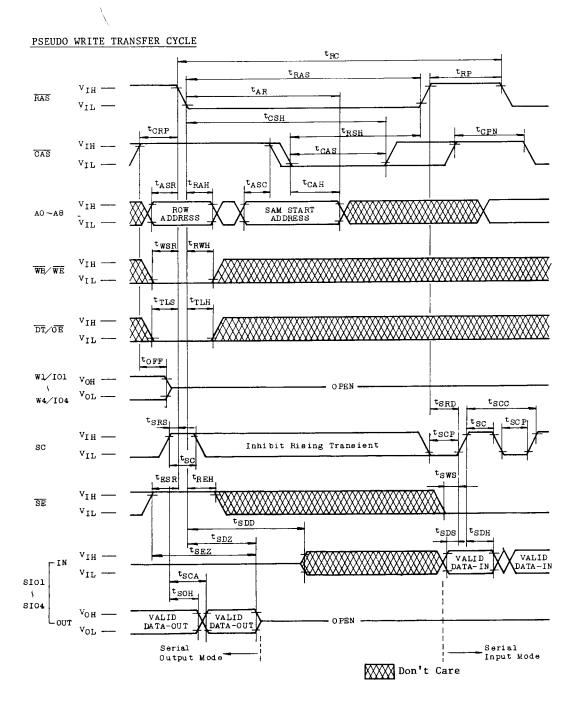

#### PSEUDO-WRITE-TRANSFER CYCLE

The pseudo-write-transfer cycle switches SIO lines from serial output mode to serial input mode. A pseudo-write-transfer is accomplished by holding  $\overline{\text{CAS}}$  high,  $\overline{\text{DT}}/\overline{\text{OE}}$  low,  $\overline{\text{WB}}/\overline{\text{WE}}$  low and  $\overline{\text{SE}}$  high at the falling edge of  $\overline{\text{RAS}}$ . The pseudo-write-transfer cycle must be performed after a read-transfer cycle if the subsequent operation is a write-transfer cycle.

There is a timing delay associated with the switching of the SIO lines from serial output mode to serial input mode. During this period, the SC clock must be held at a constant  $V_{\rm IL}$  or  $V_{\rm IH}$  after the tsc precharge time has been satisfied. A rising edge of the SC clock must not occur until after the specified delay tsrD from the rising edge of  $\overline{\rm RAS}$  (refer to Figure 11).

Figure 11: Pseudo-write-transfer cycle

#### SAM PORT OPERATION

The TC524257P/Z/J is provided with a 512-word by 4-bit serial access memory(SAM). High-speed read and write operation may be performed through the SAM port independent of the RAM port operations, except during transfer operations. The preceding transfer operation determines the direction of data flow through the SAM registers.

Data may be read out of the SAM port after a read-transfer cycle (RAM  $\rightarrow$  SAM) has been performed. Data can be shifted out of the SAM port starting at any of the 512-bit locations. This tap location corresponds to the column address selected a the falling edge of  $\overline{\text{CAS}}$  during the read-transfer cycle. The SAM registers are configured as circular data registers. The data is shifted out sequentially starting from the selected tap location to the most significant bit and then wraps around to the least significant bit.

Tap location determined by column address of read-transfer cycle.

Subsequent real-time-read-transfer may be performed on-the-fly as many times as desired within the refresh constrainst of the DRAM memory array.

A pseudo-write-transfer cycle must be performed in order to write data into the SAM port. This cycle switches the SAM port operation from output mode to input mode. Data is not transferred during a pseudo-write-transfer cycle. A write-transfer cycle (SAM  $\rightarrow$  RAM) may then be performed. The data in the SAM registers is loaded into the RAM row selected by the row address at the falling edge of  $\overline{\text{RAS}}$ . The start address of SAM registers is determined by the column address selected at the falling edge of  $\overline{\text{CAS}}$ .

| Table | 5:         | Truth  | table | for | SAM  | operation |

|-------|------------|--------|-------|-----|------|-----------|

| Table | <i>J</i> • | 114411 | Laure | 101 | OALL | ODELALION |

| Preceding<br>Transfer<br>Cycle | SAM port<br>operation | $\overline{\rm DT}/\overline{\rm OE}$ (at the falling edge of $\overline{\rm RAS}$ ) | SC | SĒ | Function             |

|--------------------------------|-----------------------|--------------------------------------------------------------------------------------|----|----|----------------------|

| read-<br>transfer              | serial<br>output      | -                                                                                    | Л  | Ł  | enable serial read   |

|                                | mode                  | н*                                                                                   |    | H  | disable serial read  |

| write-<br>transfer             | serial<br>input       | n                                                                                    | Л  | L  | enable serial write  |

| cranorer                       | mode                  |                                                                                      |    | Н  | disable serial write |

<sup>\*</sup> When simultaneous operation are being performed on the RAM port and the SAM port,  $\overline{DT}/\overline{DE}$  must be held high at the falling edge of  $\overline{RAS}$  so as not to perform a false transfer cycle.

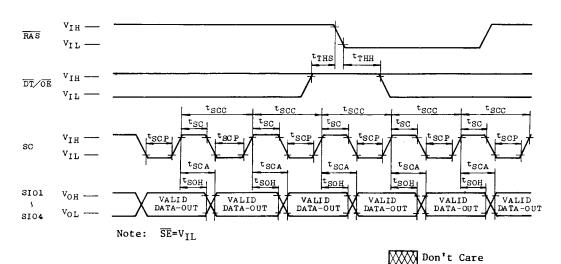

#### SERIAL CLOCK (SC)

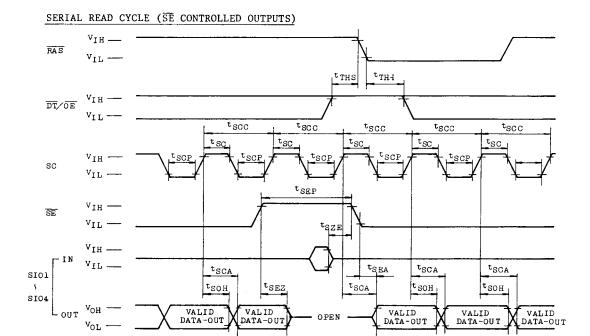

All operations of the SAM port are synchronized with the serial clock SC. Data is shifted in or out of the SAM registers at the rising edge of SC. In a serial-read, the output data becomes valid on the SIO pins after the maximum specified serial access time  $t_{\rm SCA}$  from the rising edge of SC.

The serial clock SC also increments the 9-bit serial pointer which is used to select the SAM address. The pointer address is incremented in a wrap-around mode to select sequential locations after the starting location which is determined by the column address in the read-transfer cycle. When the pointer reaches the most significant address location (decimal 511), the next SC clock will place it at the least significant address location (decimal 0).

#### SERIAL ENABLE (SE)

The  $\overline{\text{SE}}$  input is used to enable serial access operation. In a serial-read cycle,  $\overline{\text{SE}}$  is used as an output control. In a serial-write cycle,  $\overline{\text{SE}}$  is used as a write enable control. When  $\overline{\text{SE}}$  is high, serial access is disabled, however, the serial address pointer location is still incremented when SC is clocked even when  $\overline{\text{SE}}$  is high.

#### SERIAL INPUT/OUTPUT (SIO1 ~ SIO4)

Serial input and serial output share common I/O pins. Serial input or output mode is determined by the most recent transfer cycle. When a read-transfer cycle is performed, the SAM port is in the output mode. When a pseudo-write cycle is performed, the SAM port operation is switched from output mode to input mode.

During subsequent write-transfer cycle, the SAM port remains in the input mode.

#### REFRESH

The SAM data registers are static flip-flops therefore a refresh is not required.

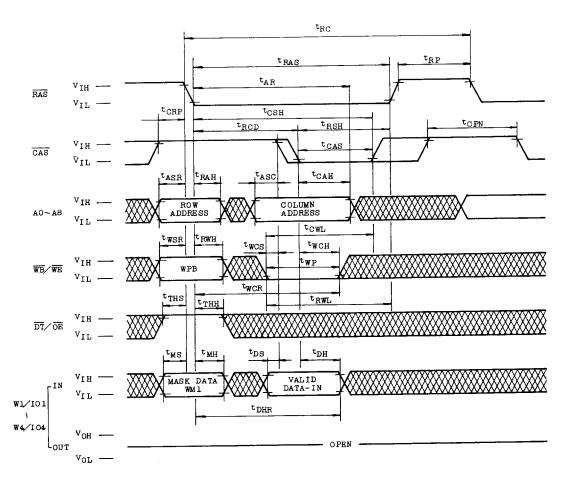

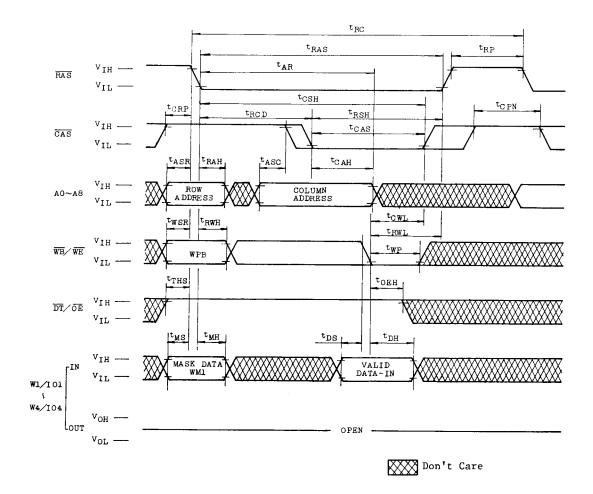

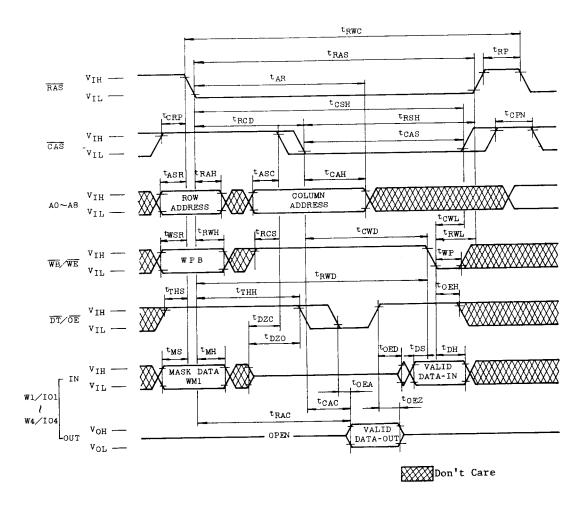

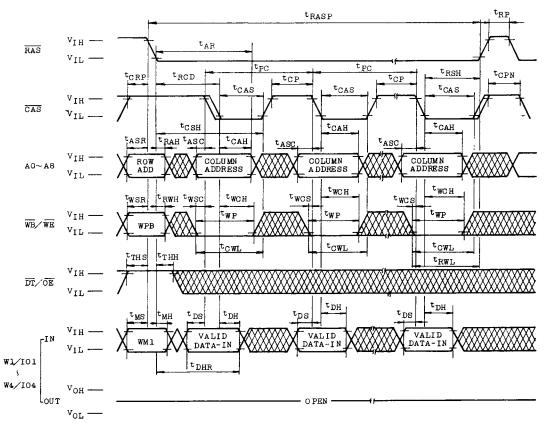

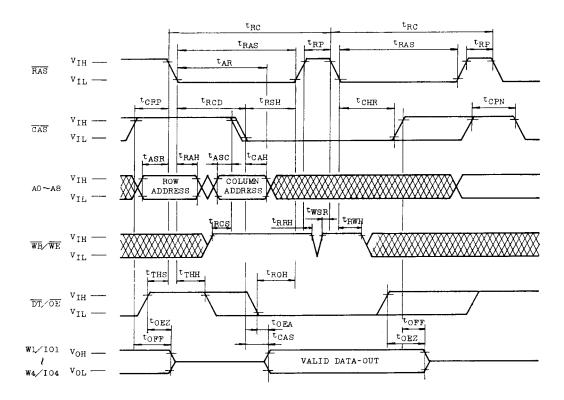

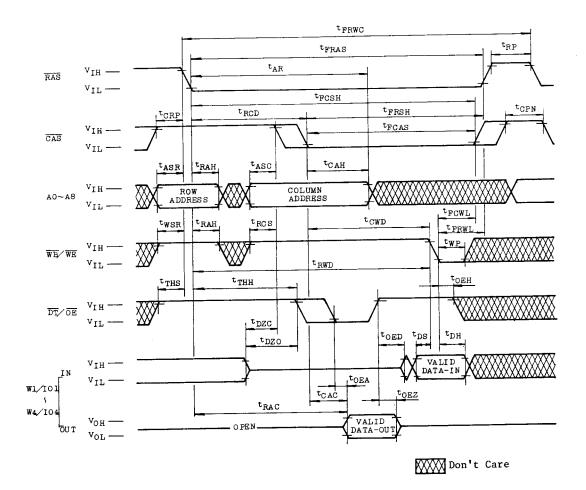

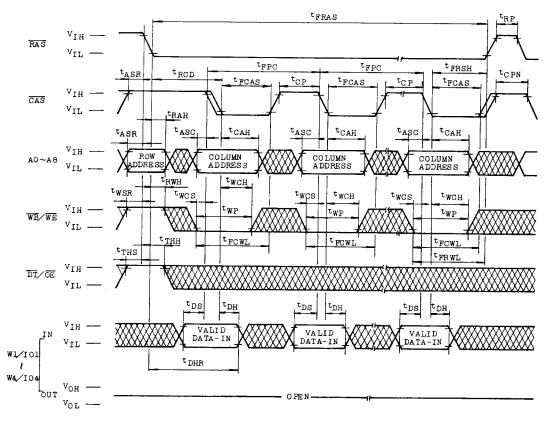

#### TIMING WAVEFORMS

Don't Care

#### WRITE CYCLE (EARLY WRITE)

#### WRITE CYCLE (OE CONTROLLED WRITE)

## READ-WTITE/READ-MODIFY-WRITE CYCLE

#### PAGE MODE READ CYCLE

#### PAGE MODE WRITE CYCLE (EARLY WRITE)

Don't Care

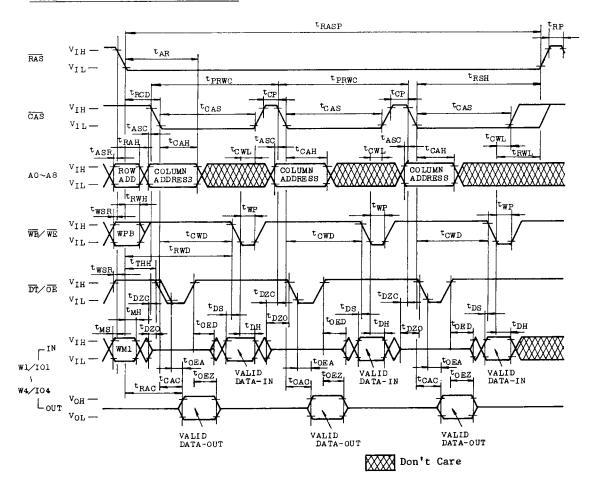

#### PAGE MODE READ-MODIFY-WRITE CYCLE

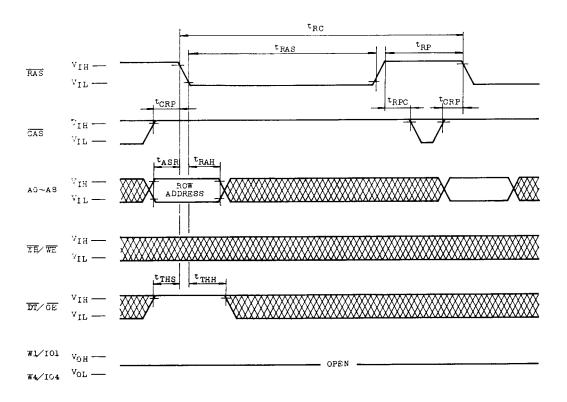

#### RAS ONLY REFRESH CYCLE

Don't Care

#### CAS BEFORE RAS REFRESH CYCLE

Don't Care

#### HIDDEN REFRESH CYCLE

Don't Care

#### REAL TIME READ TRANSFER CYCLE

#### READ TRANSFER CYCLE (Previous transfer is write transfer)

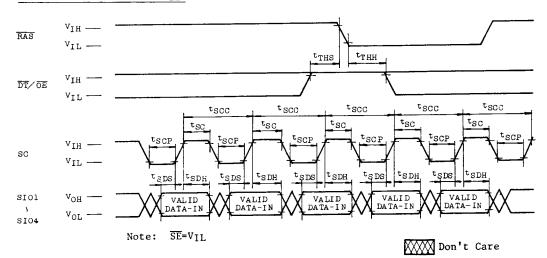

## SERIAL READ CYCLE (SE=VIL)

Don't Care

#### SERIAL WRITE CYCLE (SE=VIL)

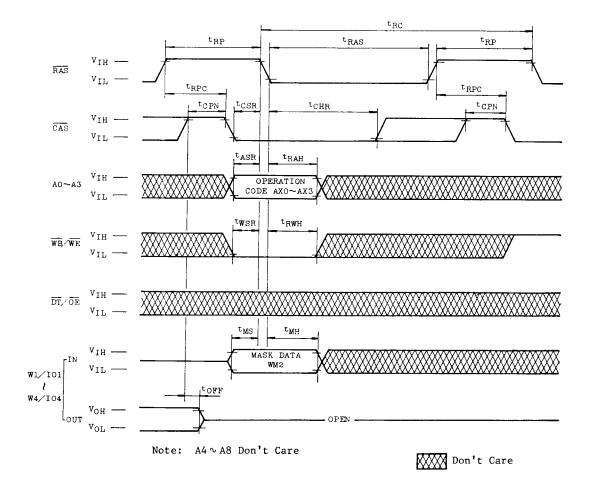

#### RASTER OPERATION SET-UP CYCLE

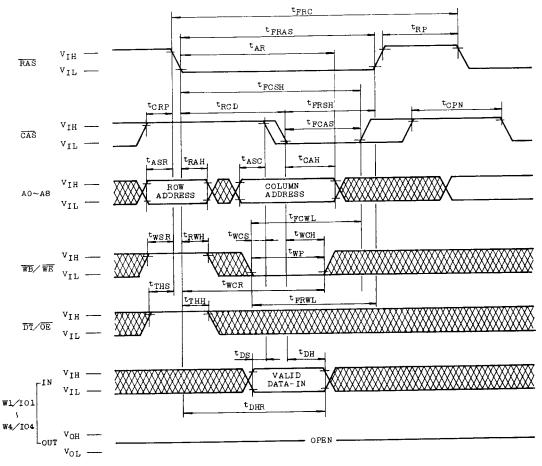

## RASTER OPERATION WRITE CYCLE (EARLY WRITE)

Don't Care

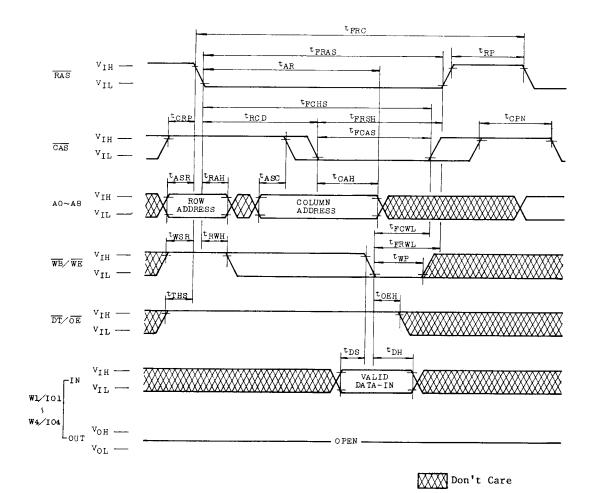

#### RASTER OPERATION WRITE CYCLE (OE CONTROLLED WRITE)

## RASTER OPERATION READ-WRITE/READ-MODIFY-WRITE CYCLE

#### RASTER OPERATION PAGE MODE WRITE CYCLE

Don't Care

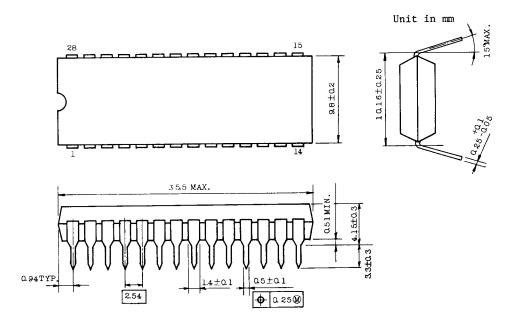

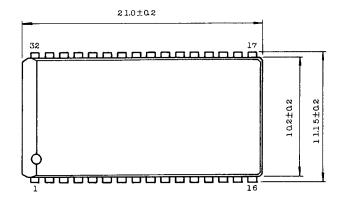

**OUTLINE DRAWINGS**

Plastic DIP

Note: Each lead pitch is 2.54mm.

All leads are located within  $0.25 \,\mathrm{mm}$  of their true longitudinal position with respect to No.1 and No.28 leads.

All dimensions are in millimeters.

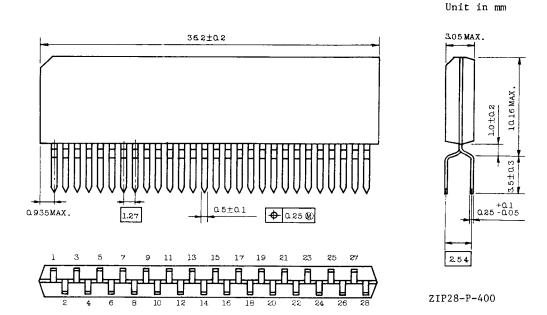

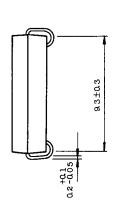

Plastic ZIP

Note: Each lead pitch is 1.27mm.

All dimensions are in millimeters.

Toshiba does not assume any responsibility for use of any circuitry described; no circuit patent licenses are implied, and Toshiba reserves the right, at any time without notice, to change said circuitry.

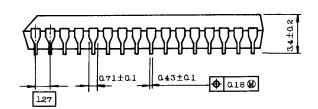

• Plastic SOJ

Unit in mm

SOJ32-P-400

Note: Each lead pitch is  $1.27 \mathrm{mm}$

All dimensions are in millimeters.