# TENTATIVE TOSHIBA MOS DIGITAL INTEGRATED CIRCUIT SILICON GATE CMOS

# 32 GBIT (4G $\times$ 8 BIT) CMOS NAND E<sup>2</sup>PROM (Triple-Level-Cell)

# **DESCRIPTION**

The TC58NVG5T2HTA00 is a single 3.3 V 32 Gbit (40,478,441,472 bits) NAND Electrically Erasable and Programmable Read-Only Memory (NAND E<sup>2</sup>PROM) organized as (8192 + 1024) bytes  $\times$  516 pages  $\times$  1064 blocks. The device has one 9216-byte static registers which allow program and read data to be transferred between the register and the memory cell array in 9216-byte increments. The Erase operation is implemented in a single block unit (4128 Kbytes + 516 Kbytes:9216 bytes  $\times$  516 pages).

The TC58NVG5T2HTA00 is a serial-type memory device which utilizes the I/O pins for both address and data input/output as well as for command inputs. The Erase and Program operations are automatically executed making the device most suitable for applications such as solid-state file storage, voice recording, image file memory for still cameras and other systems which require high-density non-volatile memory data storage.

# **FEATURES**

• Organization

|                 | TC58NVG5T2HTA00                                     |

|-----------------|-----------------------------------------------------|

| Device capacity | $9216 \times 516 \times 1064 \times 8 \text{ bits}$ |

| Register        | $9216 \times 8$                                     |

| Page size       | 9216 bytes                                          |

| Block size      | (4128K + 516K) bytes                                |

• Modes

Read, Reset, Auto Page Program, Auto Block Erase, Status Read, Multi Page Program, Multi Page Read

- Mode control Serial input/output Command control

- Number of valid blocks Min 1028 blocks Max 1064 blocks

- Power supply  $V_{CC} = 2.7 V$  to 3.6 V

- Access time Cell array to register 150 µs max (TBD) Serial Read Cycle 25 ns min

- Program/Erase time Auto Page Program Auto Block Erase

TBD μs/page typ. 3 ms/block typ.

- Operating current Read (25 ns cycle) 50 mA max. Program (avg.) 50 mA max. Erase (avg.) 50 mA max. Standby 100 µA max.(TBD)

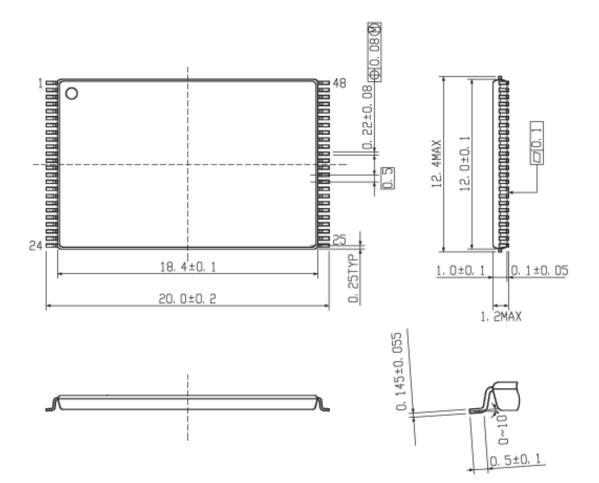

- Package TSOP I 48-P-1220-0.50C (Weight: 0.53 g typ.)

- FOR RELIABILITY GUIDANCE, PLEASE REFER TO THE APPLICATION NOTES AND COMMENTS (14). 60 bit ECC each 1K bytes required.

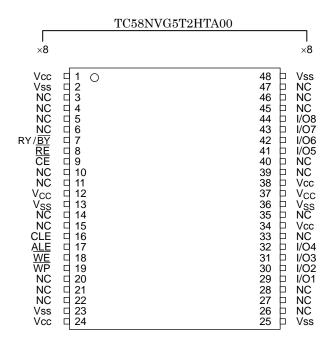

# **PIN ASSIGNMENT (TOP VIEW)**

# PIN NAMES

| I/O1 ~ I/O8     | I/O port             |

|-----------------|----------------------|

| CE              | Chip enable          |

| WE              | Write enable         |

| RE              | Read enable          |

| CLE             | Command latch enable |

| ALE             | Address latch enable |

| WP              | Write protect        |

| RY/BY           | Ready/Busy           |

| V <sub>CC</sub> | Power supply         |

| V <sub>SS</sub> | Ground               |

| N.C             | No connection        |

eet http://www.datasheet4u

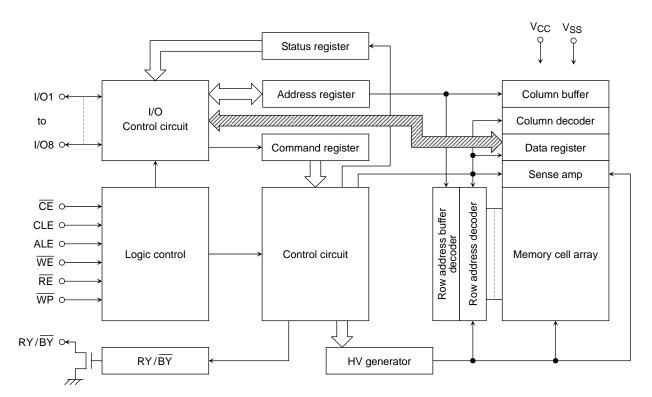

## **BLOCK DIAGRAM**

# **ABSOLUTE MAXIMUM RATINGS**

| SYMBOL              | RATING                       | VALUE                                             | UNIT |

|---------------------|------------------------------|---------------------------------------------------|------|

| V <sub>CC</sub>     | Power Supply Voltage         | -0.6 to 4.6                                       | V    |

| V <sub>IN</sub>     | Input Voltage                | –0.6 to 4.6                                       | V    |

| V <sub>I/O</sub>    | Input /Output Voltage        | –0.6 V to V <sub>CC</sub> + 0.3 V ( $\leq$ 4.6 V) | V    |

| PD                  | Power Dissipation            | 0.3                                               | W    |

| T <sub>SOLDER</sub> | Soldering Temperature (10 s) | 260                                               | °C   |

| T <sub>STG</sub>    | Storage Temperature          | -55 to 150                                        | °C   |

| T <sub>OPR</sub>    | Operating Temperature        | 0 to 70                                           | °C   |

# **CAPACITANCE** \*(Ta = 25°C, f = 1 MHz)

| SYMBOL           | PARAMETER | CONDITION       | MIN | MAX | UNIT |

|------------------|-----------|-----------------|-----|-----|------|

| C <sub>IN</sub>  | Input     | $V_{IN} = 0 V$  | _   | 10  | pF   |

| C <sub>OUT</sub> | Output    | $V_{OUT} = 0 V$ | _   | 10  | pF   |

\* This parameter is periodically sampled and is not tested for every device.

# TOSHIBA

# VALID BLOCKS\*

| SYMBOL          | PARAMETER              | MIN  | TYP. | MAX  | UNIT   |

|-----------------|------------------------|------|------|------|--------|

| N <sub>VB</sub> | Number of Valid Blocks | 1028 | —    | 1064 | Blocks |

NOTE: The device occasionally contains unusable blocks. Refer to Application Note (10) toward the end of this document. The first block (Block 0) is guaranteed to be a valid block at the time of shipment.

The specification for the minimum number of valid blocks is applicable over the device lifetime.

# **RECOMMENDED DC OPERATING CONDITIONS**

| SYMBOL          | PAR                      | AMETER                                              | MIN       | TYP. | MAX                   | UNIT |

|-----------------|--------------------------|-----------------------------------------------------|-----------|------|-----------------------|------|

| V <sub>CC</sub> | Power Supply Voltage     |                                                     | 2.7 V     |      | 3.6 V                 | V    |

| VIH             | High Level input Voltage | $2.7~\text{V} \leq \text{V}_{CC} \leq 3.6~\text{V}$ | 0.8 x Vcc | _    | V <sub>CC</sub> + 0.3 | V    |

| V <sub>IL</sub> | Low Level Input Voltage  | $2.7~V \leq V_{CC} \leq 3.6~V$                      | -0.3*     |      | 0.2 x Vcc             | V    |

\* -2 V (pulse width lower than 20 ns)

# DC CHARACTERISTICS (Ta = 0 to 70°C, V<sub>CC</sub> = 2.7 V to 3.6 V)

| SYMBOL                     | PARAMETER                   | CONDITION                                                                        | MIN | TYP. | MAX | UNIT |

|----------------------------|-----------------------------|----------------------------------------------------------------------------------|-----|------|-----|------|

| IIL                        | Input Leakage Current       | $V_{IN} = 0 V$ to $V_{CC}$                                                       | _   | _    | ±10 | μΑ   |

| I <sub>LO</sub>            | Output Leakage Current      | $V_{OUT} = 0 V \text{ to } V_{CC}$                                               |     | —    | ±10 | μA   |

| I <sub>CCO0</sub>          | Power On Reset Current      | —                                                                                | _   | _    | 30  | mA   |

| I <sub>CCO1</sub>          | Serial Read Current         | $\overline{CE} = V_{IL}, I_{OUT} = 0 \text{ mA}, \text{ tcycle} = 50 \text{ ns}$ | _   | —    | 50  | mA   |

| I <sub>CCO2</sub>          | Programming Current         | —                                                                                | _   | —    | 50  | mA   |

| I <sub>CCO3</sub>          | Erasing Current             | —                                                                                | _   | —    | 50  | mA   |

| I <sub>CCS</sub>           | Standby Current             | $\overline{CE} = V_{CC} - 0.2 \text{ V},  \overline{WP} = 0 \text{ V/V}_{CC}$    |     | —    | 100 | μA   |

| V <sub>OH</sub>            | High Level Output Voltage   | $I_{OH}$ = -0.4 mA (2.7 V $\leq$ V_{CC} $\leq$ 3.6 V)                            | 2.4 |      | _   | V    |

| V <sub>OL</sub>            | Low Level Output Voltage    | $I_{OL} = 2.1 \text{ mA} (2.7 \text{ V} \le \text{V}_{CC} \le 3.6 \text{ V})$    | _   | _    | 0.4 | V    |

| I <sub>OL</sub><br>(RY/BY) | Output current of RY/BY pin | $V_{OL} = 0.4 V (2.7 V \le V_{CC} \le 3.6 V)$                                    | _   | 8    | _   | mA   |

# <u>AC CHARACTERISTICS AND RECOMMENDED OPERATING CONDITIONS</u> (Ta = 0 to 70°C, $V_{CC}$ = 2.7 V to 3.6 V)

| SYMBOL             | PARAMETER                                                              | MIN | MAX          | UNIT |  |

|--------------------|------------------------------------------------------------------------|-----|--------------|------|--|

| t <sub>CLS</sub>   | CLE Setup Time                                                         | 12  |              | ns   |  |

| t <sub>CLS2</sub>  | CLE Setup Time                                                         | 42  |              | ns   |  |

| t <sub>CLH</sub>   | CLE Hold Time                                                          | 10  |              | ns   |  |

| t <sub>CS</sub>    | CE Setup Time                                                          | 20  |              | ns   |  |

| t <sub>CS2</sub>   | CE Setup Time                                                          | 32  |              | ns   |  |

| t <sub>CH</sub>    | CE Hold Time                                                           | 10  |              | ns   |  |

| t <sub>WP</sub>    | Write Pulse Width                                                      | 12  |              | ns   |  |

| t <sub>ALS</sub>   | ALE Setup Time                                                         | 12  | —            | ns   |  |

| t <sub>ALH</sub>   | ALE Hold Time                                                          | 10  | —            | ns   |  |

| t <sub>DS</sub>    | Data Setup Time                                                        | 10  | —            | ns   |  |

| t <sub>DH</sub>    | Data Hold Time                                                         | 5   | —            | ns   |  |

| t <sub>WC</sub>    | Write Cycle Time                                                       | 25  | —            | ns   |  |

| t <sub>WH</sub>    | WE High Hold Time                                                      | 10  | —            | ns   |  |

| t <sub>ADL</sub> * | $\overline{\text{WE}}$ High Hold Time from final address to first data | 300 | —            | ns   |  |

| t <sub>WW</sub>    | $\overline{WP}$ High to $\overline{WE}$ Low                            | 100 | 100 —        |      |  |

| t <sub>RW</sub>    | Ready to WE Falling Edge                                               | 20  | —            | ns   |  |

| t <sub>RP</sub>    | Read Pulse Width                                                       | 12  | —            | ns   |  |

| t <sub>RC</sub>    | Read Cycle Time                                                        | 25  | —            | ns   |  |

| t <sub>REA</sub>   | RE Access Time                                                         | —   | 20           | ns   |  |

| t <sub>CR</sub>    | CE Low to RE Low                                                       | 10  | —            | ns   |  |

| t <sub>CLR</sub>   | CLE Low to RE Low                                                      | 10  | —            | ns   |  |

| t <sub>AR</sub>    | ALE Low to RE Low                                                      | 10  | —            | ns   |  |

| t <sub>RHOH</sub>  | Data Output Hold Time from RE High                                     | 25  | —            | ns   |  |

| t <sub>RLOH</sub>  | Data Output Hold Time from RE Low                                      | 5   | —            | ns   |  |

| t <sub>RHZ</sub>   | RE High to Output High Impedance                                       | —   | 60           | ns   |  |

| t <sub>CHZ</sub>   | CE High to Output High Impedance                                       | —   | 30           | ns   |  |

| t <sub>CLHZ</sub>  | CLE High to Output High Impedance                                      | —   | 30           | ns   |  |

| t <sub>REH</sub>   | RE High Hold Time                                                      | 10  | —            | ns   |  |

| t <sub>IR</sub>    | Output-High-impedance-to- RE Falling Edge                              | 0   | —            | ns   |  |

| t <sub>RHW</sub>   | RE High to WE Low                                                      | 30  | —            | ns   |  |

| tWHC               | WE High to CE Low                                                      | 30  |              | ns   |  |

| twhr               | WE High to RE Low for data output                                      | 300 |              | ns   |  |

| tWHRS              | WE High to RE Low for Status & ID Read                                 | 180 | —            | ns   |  |

| t <sub>R</sub>     | Memory Cell Array to Starting Address                                  | —   | 150(TBD)     | μS   |  |

| t <sub>WB</sub>    | WE High to Busy                                                        | —   | 100          | ns   |  |

| t <sub>RST</sub>   | Device Reset Time (Ready/Read/Program/Erase)                           | —   | 10/20/30/200 | μS   |  |

\* tADL is the time from the  $\overline{WE}$  rising edge of final address cycle to the  $\overline{WE}$  rising edge of first data cycle.

# AC TEST CONDITIONS

| PARAMETER                      | CONDITION                      |  |  |  |  |  |

|--------------------------------|--------------------------------|--|--|--|--|--|

|                                | $2.7~V \leq V_{CC} \leq 3.6~V$ |  |  |  |  |  |

| Input level                    | 0 V to Vcc                     |  |  |  |  |  |

| Input pulse rise and fall time | 3ns                            |  |  |  |  |  |

| Input comparison level         | Vcc/2                          |  |  |  |  |  |

| Output data comparison level   | Vcc/2                          |  |  |  |  |  |

| Output load                    | C <sub>L</sub> (50 pF) + 1 TTL |  |  |  |  |  |

Note: Busy to ready time depends on the pull-up resistor tied to the  $RY/\overline{BY}$  pin. (Refer to Application Note (6) toward the end of this document.)

#### **PROGRAMMING AND ERASING CHARACTERISTICS** (Ta = 0 to 70°C, $V_{CC} = 2.7 V$ to 3.6 V)

| SYMBOL               | PARAMETER                                           | MIN | TYP. | MAX | UNIT | NOTES |

|----------------------|-----------------------------------------------------|-----|------|-----|------|-------|

| t <sub>PROG</sub>    | Average Programming Time                            | _   | TBD  | TBD | μS   |       |

| tDCBSYW1             | Data Cache Busy Time in Write Cache (following 11h) |     |      | 10  | μS   |       |

| tDCBSYW2             | Data Cache Busy Time in Write Cache (following 15h) | _   | TBD  | TBD | μS   | (2)   |

| t <sub>DCBSYW3</sub> | Data Cache Busy Time in Write Cache (following 1Ah) | _   | 10   | TBD | μs   | (3)   |

| Ν                    | Number of Partial Program Cycles in the Same Page   |     |      |     |      | (1)   |

| t <sub>BERASE</sub>  | Block Erasing Time                                  |     | 3    | 10  | ms   |       |

(1) Refer to Application Note (9) toward the end of this document.

(2) t<sub>DCBSYW2</sub> depends on the timing between internal programming time and data in time.

(3) In case of Program Operation with Data Cache, t<sub>DCBSYW3</sub> depends on the timing between internal programming time and data in time.

# Data Output

When tREH is long, output buffers are disabled by /RE=High, and the hold time of data output depend on tRHOH (25 ns MIN). On this condition, waveforms look like normal serial read mode.

When tREH is short, output buffers are not disabled by /RE=High, and the hold time of data output depend on tRLOH (5ns MIN). On this condition, output buffers are disabled by the rising edge of CLE, ALE, /CE or falling edge of /WE, and waveforms look like Extended Data Output Mode.

Data Output can be output synchronously with the clock after 05h+Address\*5cycle+E0h sequence.

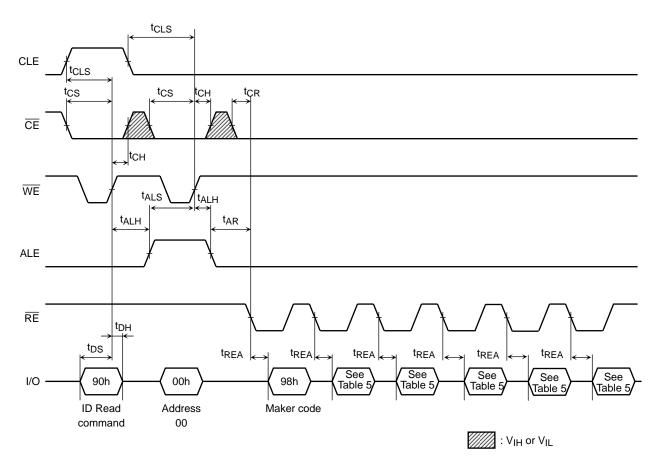

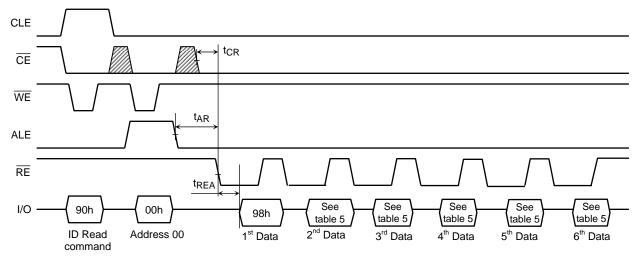

# ID Read Operation Timing Diagram

#### PIN FUNCTIONS

The device is a serial access memory which utilizes time-sharing input of address information.

#### Command Latch Enable: CLE

The CLE input signal is used to control loading of the operation mode command into the internal command register. The command is latched into the command register from the I/O port on the rising edge of the  $\overline{WE}$  signal while CLE is High.

#### Address Latch Enable: ALE

The ALE signal is used to control loading address information into the internal address register. Address information is latched into the address register from the I/O port on the rising edge of  $\overline{WE}$  while ALE is High.

### Chip Enable: CE

The device goes into a low-power Standby mode when  $\overline{CE}$  goes High during the device is in Ready state. The  $\overline{CE}$  signal is ignored when device is in Busy state (RY /  $\overline{BY}$  = L), such as during a Program or Erase or Read operation, and will not enter Standby mode even if the  $\overline{CE}$  input goes High.

### Write Enable: WE

The  $\overline{WE}$  signal is used to control the acquisition of data from the I/O port.

#### Read Enable: RE

The  $\overline{RE}$  signal controls serial data output. Data is available t<sub>REA</sub> after the falling edge of  $\overline{RE}$ . The internal column address counter is also incremented (Address = Address + 1) on this falling edge.

#### I/O Port: I/O1 to 8

The I/O1 to 8 pins are used as a port for transferring address, command and input/output data to and from the device.

#### Write Protect: WP

The  $\overline{WP}$  signal is used to protect the device from accidental programming or erasing. The internal voltage regulator is reset when  $\overline{WP}$  is Low. This signal is usually used for protecting the data during the power-on/off sequence when input signals are invalid.

#### Ready/Busy: RY/BY

The RY/ $\overline{BY}$  output signal is used to indicate the operating condition of the device. The RY/ $\overline{BY}$  signal is in Busy state (RY/ $\overline{BY}$  = L) during the Program, Erase and Read operations and will return to Ready state (RY/ $\overline{BY}$  = H) after completion of the operation. The output buffer for this signal is an open drain and has to be pulled-up to Vcc with an appropriate resister.

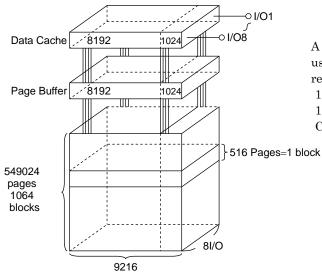

# Schematic Cell Layout and Address Assignment

The Program operation works on page units while the Erase operation works on block units.

A page consists of 9216 bytes in which 8192 bytes are used for main memory storage and 1024 bytes are for redundancy or for other uses.

1 page = 9216 bytes

1 block = 9216 bytes  $\times$  516 pages = (4128K + 516K)bytes Capacity = 9216 bytes  $\times$  516 pages  $\times$  1064 blocks

An address is read in via the I/O port over five consecutive clock cycles, as shown in Table 1.

|              | I/O8 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 |

|--------------|------|------|------|------|------|------|------|------|

| First cycle  | CA7  | CA6  | CA5  | CA4  | CA3  | CA2  | CA1  | CA0  |

| Second cycle | L    | L    | CA13 | CA12 | CA11 | CA10 | CA9  | CA8  |

| Third cycle  | L    | PA6  | PA5  | PA4  | PA3  | PA2  | PA1  | PA0  |

| Fourth cycle | PA14 | PA13 | PA12 | PA11 | PA10 | PA9  | PA8  | PA7  |

| Fifth cycle  | L    | L    | L    | L    | PA18 | PA17 | PA16 | PA15 |

CA0 to CA13: Column address PA0 to PA18: Page address

PA0 to PA6: WL address in a block

PA7: Left / Right plane address

(Left Plane=0 / Right Plane=1)

PA8 to PA18: Block address

Note)

Table 1. Addressing

(a) Block address (PA8 to PA18) can only be selected between Block 0 and Block 1063.

(b) WL address in a block (PA0 to PA6) can only be selected between WL 0 and WL 85.

(c) There are Lower/Middle/Upper address in a WL, which is selected 01/02/03h command.

Input of the address other than specified above is invalid.

If those unspecified addresses are inputted in program or erase operation, the device will output a fail status to respond to status read command.

In case of read operation, some invalid data will be outputted by the device.

Please refer to Application Note (11) toward the end of this document for block management.

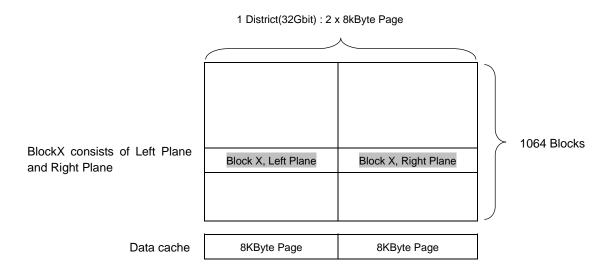

# Left / Right Plane Scheme of NAND

1 District of this NAND consists of Left / Right plane  $\times$  8kByte Page. Left / Right Plane Scheme is as follows.

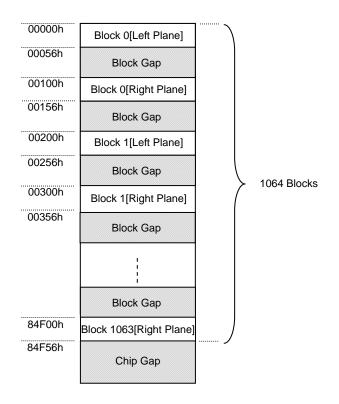

#### **Block Arrangement**

The device has block gaps and chip gap(s). Block arrangement is as follows.

Page Address (Hexadecimal)

#### ID Read

The device contains ID codes which can be used to identify the device type, the manufacturer, and features of the device. The ID codes can be read out under the following timing conditions:

#### Table 5. Code table

|          | Description                                            | I/O8 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | Hex Data  |

|----------|--------------------------------------------------------|------|------|------|------|------|------|------|------|-----------|

| 1st Data | Maker Code                                             | 1    | 0    | 0    | 1    | 1    | 0    | 0    | 0    | 98h       |

| 2nd Data | Device Code                                            | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | D7h       |

| 3rd Data | Chip Number, Cell Type                                 | _    | _    |      | _    | _    | _    | _    |      | See table |

| 4th Data | Page Size, Block Size,<br>Redundant Size, Organization |      | _    | _    |      | _    |      |      |      | See table |

| 5th Data | Extended Block                                         | _    |      |      | _    |      |      | _    |      | See table |

| 6th Data | Technology Code                                        | _    | _    | —    | _    | _    | —    | _    |      | See table |

#### 2nd Data

| Description    |           | I/O8 | I/07 | I/O6 | I/O5 | I/O4 | I/O3 | I/O2 | I/O1 | Hex Data |

|----------------|-----------|------|------|------|------|------|------|------|------|----------|

|                | 8 Gbits   | 1    | 1    | 0    | 1    | 0    | 0    | 1    | 1    | D3h      |

|                | 16 Gbits  | 1    | 1    | 0    | 1    | 0    | 1    | 0    | 1    | D5h      |

| Memory Density | 32 Gbits  | 1    | 1    | 0    | 1    | 0    | 1    | 1    | 1    | D7h      |

| per each /CE   | 64 Gbits  | 1    | 1    | 0    | 1    | 1    | 1    | 1    | 0    | DEh      |

|                | 128 Gbits | 0    | 0    | 1    | 1    | 1    | 0    | 1    | 0    | 3Ah      |

|                | 256 Gbits | 0    | 0    | 1    | 1    | 1    | 1    | 0    | 0    | 3Ch      |

3rd Data

|                                      | Description                                                   | I/O8   | I/07 | I/O6   | I/O5   | I/O4             | I/O3             | I/O2             | I/O1             |

|--------------------------------------|---------------------------------------------------------------|--------|------|--------|--------|------------------|------------------|------------------|------------------|

| Internal Chip Number<br>per each CE/ | 1<br>2<br>4<br>8                                              |        |      |        |        |                  |                  | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| Cell Type                            | 2 level cell<br>4 level cell<br>8 level cell<br>16 level cell |        |      |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |                  |                  |

| Reserved                             |                                                               | 0 or 1 | 0    | 0 or 1 | 0 or 1 |                  |                  |                  |                  |

# TOSHIBA CONFIDENTIAL

4th Data

|                                       | Description                      | I/O8 | I/07 | I/O6   | I/O5   | I/O4   | I/O3   | I/O2             | I/O1             |

|---------------------------------------|----------------------------------|------|------|--------|--------|--------|--------|------------------|------------------|

| Page Size<br>(without redundant area) | 2 KB<br>4 KB<br>8 KB<br>Reserved |      |      |        |        |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |

| Block Size                            | Default Value                    | 1    |      | 0      | 0      |        |        |                  |                  |

| (without redundant area)              | Reserved                         |      |      | 0 or 1 | 0 or 1 |        |        |                  |                  |

| Redundant area size                   | Default Value                    |      | 0    |        |        | 0      | 0      |                  |                  |

|                                       | Reserved                         |      |      |        |        | 0 or 1 | 0 or 1 |                  |                  |

5th Data

|                              | Description      | I/O8   | I/07   | I/O6   | I/O5   | I/O4             | I/O3             | I/O2   | I/O1   |

|------------------------------|------------------|--------|--------|--------|--------|------------------|------------------|--------|--------|

| District Number per each /CE | 1<br>2<br>4<br>8 |        |        |        |        | 0<br>0<br>1<br>1 | 0<br>1<br>0<br>1 |        |        |

| Reserved                     |                  | 0 or 1 | 0 or 1 | 0 or 1 | 0 or 1 |                  |                  | 0 or 1 | 0 or 1 |

6th Data

| Description             |                | I/O8   | I/07   | I/O6   | I/O5   | I/O4   | I/O3 | I/O2 | I/O1 |

|-------------------------|----------------|--------|--------|--------|--------|--------|------|------|------|

|                         | 130 nm process |        |        |        |        |        | 0    | 0    | 0    |

|                         | 90 nm process  |        |        |        |        |        | 0    | 0    | 1    |

|                         | 70 nm process  |        |        |        |        |        | 0    | 1    | 0    |

| To the state of a state | 56 nm process  |        |        |        |        |        | 0    | 1    | 1    |

| Technology code         | 43 nm process  |        |        |        |        |        | 1    | 0    | 0    |

|                         | 32 nm process  |        |        |        |        |        | 1    | 0    | 1    |

|                         | 24 nm process  |        |        |        |        |        | 1    | 1    | 0    |

|                         | Reserved       |        |        |        |        | 0 or 1 | 1    | 1    | 1    |

| Reserved                |                | 0 or 1 | 0 or 1 | 0 or 1 | 0 or 1 |        |      |      |      |

Free Datasheet http://www.datasheet4u.com/

#### APPLICATION NOTES AND COMMENTS

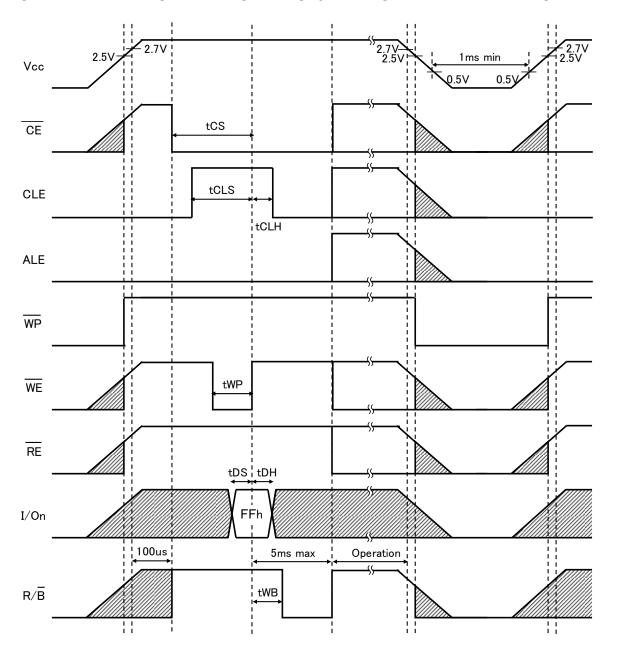

(1) Power-on/off sequence:

The device is designed to offer protection from any involuntary program/erase during power-transitions. An internal voltage detector disables all functions whenever  $V_{CC}$  is below about 2V. The Reset command(FFh) must be issued to all  $\overrightarrow{CEs}$  as the first command after the NAND Flash device is powered on. Each  $\overrightarrow{CE}$  will be busy for a maximum of 5ms after a RESET command is issued. In this time period, the acceptable command is 70h/71h/F1h.

Each NAND die will draw no more than 1st prior to execution of the first Reset command(FFh) after the device is powered on.

$\overline{WP}$  pin provices hardware protection and is recommended to be kept at V<sub>IL</sub> during power-up and power-down. The two step command sequence for program/erase provides additional software protection.

#### (2) Prohibition of unspecified commands

The operation commands are listed in Table 3. Input of a command other than those specified in Table 3 is prohibited. Stored data may be corrupted if an unknown command is entered during the command cycle.

(3) Restriction of commands while in the Busy state

During the Busy state, do not input any command except 70h(71h) and FFh.

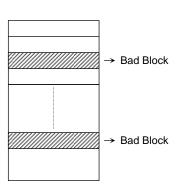

#### (10) Invalid blocks (bad blocks)

The device occasionally contains unusable blocks. Therefore, the following issues must be recognized:

At the time of shipment, the bad block information is marked on each bad block. Please do not perform an erase operation to bad blocks. It may be impossible to recover the bad block information, if the information is erased.

Check if the device has any bad blocks after installation into the system. Refer to the test flow for bad block detection. Bad blocks which are detected by the test flow must be managed as unusable blocks by the system.

A bad block does not affect the performance of good blocks because it is isolated from the bit lines by select gates.

|                           | MIN  | TYP. | MAX  | UNIT  |

|---------------------------|------|------|------|-------|

| Valid (Good) Block Number | 1028 |      | 1064 | Block |

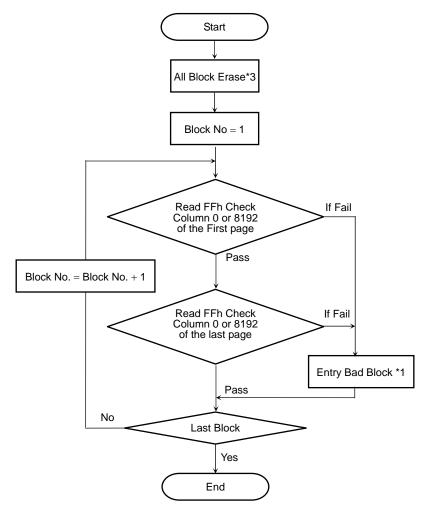

# **Bad Block Test Flow**

Regarding invalid blocks, bad block mark is in both the 1st and the last page.

\*1:No erase operation is allowed to detected bad blocks

\*2:Bad column detection should be operated before detecting bad block information and Bad Columns should be skipped when bad block information is read.

(for example) In case of Column 0 or 8192 is Bad Column, Column  $2(4,6,8,10,\cdots)$  or  $8194(8196,8198,8200,8202,\cdots)$  should be checked after Column 0 or 8192.

\*3: At first, all blocks should be erased.

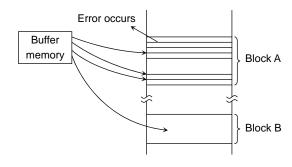

#### (11) Failure phenomena for Program and Erase operations

The device may fail during a Program or Erase operation.

The following possible failure modes should be considered when implementing a highly reliable system.

|            | FAILURE MODE                    | DETECTION AND COUNTERMEASURE SEQUENCE                     |

|------------|---------------------------------|-----------------------------------------------------------|

| Block      | Erase Failure                   | Status Read after Erase $\rightarrow$ Block Replacement   |

| Page       | Programming Failure             | Status Read after Program $\rightarrow$ Block Replacement |

| Single Bit | Programming Failure<br>"1 to 0" | ECC                                                       |

- ECC: Error Correction Code. 60 bit correction per 1KBytes is necessary.

- Block Replacement

#### Program.

When an error happens in Block A, try to reprogram the data into another Block (Block B) by loading from an external buffer. Then, prevent further system accesses to Block A ( by creating a bad block table or by using another appropriate scheme).

#### Erase

When an error occurs during an Erase operation, prevent future accesses to this bad block (again by creating a table within the system or by using another appropriate scheme).

#### Note)

(a) Block address (PA8 to PA18) can only be selected between Block 0 and Block 2083.

(b) WL address in block (PA0 to PA6) can only be selected between WL 0 and WL 85.

Input of a address other than specified above is invalid.

If those unspecified addresses are inputted in program or erase operation, the device will output a fail status to respond to status read command. However, it is not permitted to count such a fail status as a bad block information when those unspecified addresses are input.

(12) Do not turn off the power before write/erase operation is complete. Avoid using the device when the battery is low. Power shortage and/or power failure before write/erase operation is complete will cause loss of data and/or damage to data.

(13) The all data which are Lower/Middle/Upper data of the WL can be read out only if 3<sup>rd</sup> program is completed

# Package Dimensions

Weight: 0.53 g (typ.)

# **RESTRICTIONS ON PRODUCT USE**

- Toshiba Corporation, and its subsidiaries and affiliates (collectively "TOSHIBA"), reserve the right to make changes to the information in this document, and related hardware, software and systems (collectively "Product") without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- Product is intended for use in general electronics applications (e.g., computers, personal equipment, office equipment, measuring equipment, industrial robots and home electronics appliances) or for specific applications as expressly stated in this document.

Product is neither intended nor warranted for use in equipment or systems that require extraordinarily high levels of quality and/or reliability and/or a malfunction or failure of which may cause loss of human life, bodily injury, serious property damage or serious public impact ("Unintended Use"). Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. Do not use Product for Unintended Use unless specifically permitted in this document.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Product is subject to foreign exchange and foreign trade control laws.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA assumes no liability for damages or losses occurring as a result of noncompliance with applicable laws and regulations.