**Toshiba CDMOS Integrated Circuit Silicon Monolithic**

# T C 7 7 1 6 F T G

#### Residential and Commercial Renewable Energy System (up to 1000 V AC or 1500 V DC) Voltage Booster Controller

#### Outline

TC7716FTG is a DC booster control IC for solar cell power conditioners. The solar panel voltage input pin, 12-bit AD converter, detection circuits, 3 I/O pins for booster and full-bridge control, and UART I/F are built in the IC.

#### Features

- Process: CD-0.13

- Power supply voltage (VDD): 7.2 V to 14.0 V

- Startup voltage: 7.0 V

- Built in 12bit AD converter (ADC)

- UART I/F

- H-SW soft start

- Voltage booster converter + H-SW controller or full-bridge LLC controller

- Output pulse Duty

For voltage booster controller: External input

For H-SW controller: 50%

For full bridge LLC controller: External input

- Switching Pulse of voltage booster converter: External input

- Switching frequency of H-SW (4-values changeable)

#### Weight: 70 mg (typ.)

- :50.000 kHz :59.524 kHz :69.444 kHz :80.645 kHz

- Built in protection functions

Over current protection (OCP)

Output over voltage protection (OVP, timer latch type)

Under voltage lock out (UVLO)

Thermal shutdown (TSD)

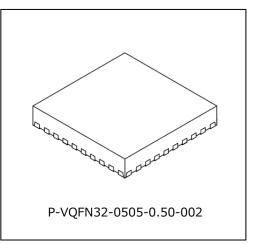

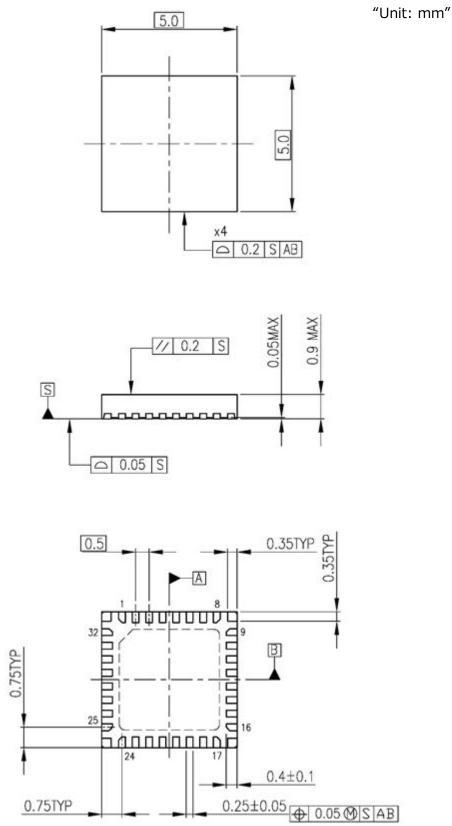

- Package QFN 32 (5.0 mm × 5.0 mm, 0.5 mm Pitch)

This product has a MOS structure and is sensitive to electrostatic discharge. When handling this product, ensure that the environment is protected against electrostatic discharge by using an earth strap, a conductive mat and an ionizer. Ensure also that the ambient temperature and relative humidity are maintained at reasonable levels.

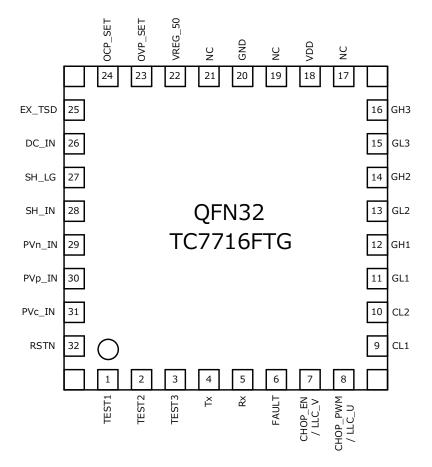

#### Pin assignment (Top View)

Figure-1

## Pin function (1)

Table-1(1)

| Pin    | Pin name            | Descriptions                                                                                                                                                                                                                                                                                                                                 |

|--------|---------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| No.    | TECT1               |                                                                                                                                                                                                                                                                                                                                              |

| 1<br>2 | TEST1<br>TEST2      | Test pin for IC shipment.                                                                                                                                                                                                                                                                                                                    |

| 3      | TEST3               | Connect to GND pin (20pin) in normal operation.                                                                                                                                                                                                                                                                                              |

| 5      | 16313               | It transmits serial data from UART (Note 1) module in the IC.                                                                                                                                                                                                                                                                                |

| 4      | Tx                  | (Refer to "UART transmitting protocol" in details.)                                                                                                                                                                                                                                                                                          |

| 5      | Rx                  | It receives serial data to UART (Note 1) module in the IC.<br>(Refer to "UART receiving protocol" in details.)                                                                                                                                                                                                                               |

| 6      | FAULT               | Monitor pin of protection circuits detection<br>In normal operation, this pin outputs "H" (= $5.0 \text{ V}$ ). And it outputs "L" (= $0 \text{ V}$ ) when any<br>circuit of OVP, OCP, or TSD operates.                                                                                                                                      |

| 7      | CHOP_EN<br>/ LLC_V  | It inputs an operation start signal of a half bridge for voltage boosting.<br>It also inputs PFM signal when H-SW operates as a full-bridge LLC converter.                                                                                                                                                                                   |

| 8      | CHOP_PWM<br>/ LLC_U | It inputs a synchronous rectification PWM signal of a half-bridge for voltage boosting. It also inputs PFM signal when H-SW operates as a full-bridge LLC converter.                                                                                                                                                                         |

| 9      | CL1                 | It connects to crystal oscillator which generates necessary clocks in the IC.<br>Oscillator of 10 MHz is constructed by connecting the crystal oscillator between CL1 pin<br>and CL2 pin. Oscillator of 10 MHz is used as the sampling clocks of 12-bit ADC. And it is                                                                       |

| 10     | CL2                 | also used as a switching signal generator for PWM controller of H-SW.                                                                                                                                                                                                                                                                        |

| 11     | GL1 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the right Low side of H-SW.                                                                                                                                                                                                                                                     |

| 12     | GH1 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the right High side of H-SW.                                                                                                                                                                                                                                                    |

| 13     | GL2 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the left Low side of H-SW.                                                                                                                                                                                                                                                      |

| 14     | GH2 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the left High side of H-SW.                                                                                                                                                                                                                                                     |

| 15     | GL3 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the Low side of the half bridge for voltage boosting.                                                                                                                                                                                                                           |

| 16     | GH3 (Note 2)        | It outputs PWM signal to FET gate driver IC which configures the High side of the half bridge for voltage boosting.                                                                                                                                                                                                                          |

| 17     | NC                  | Non connection pin. It connects to GND in normal use.                                                                                                                                                                                                                                                                                        |

| 18     | VDD                 | Power supply pin for IC.<br>Operating voltage range is 7.2 V (min) to 14.0 V (max). The IC starts at 6.5 V (typ.) and<br>stops operation at 6.0 V (typ.) or less with the UVLO function.<br>VDD voltage (0 V to 8.0 V) should be raised at 200µs or more.                                                                                    |

| 19     | NC                  | Non connection pin. It connects to GND in normal use.                                                                                                                                                                                                                                                                                        |

| 20     | GND                 | Ground (GND) pin for IC.                                                                                                                                                                                                                                                                                                                     |

| 21     | NC                  | Non connection pin. It connects to GND in normal use.                                                                                                                                                                                                                                                                                        |

| 22     | VREG_50             | 5 V regulator output pin. The 3.0 mA current can be drawn from this pin, with 5.0 V output. The 2.2 $\mu$ F capacitor is connected between this pin and GND pin (20pin) to stabilize the output voltage.<br>This pin supplies the voltage to OVP_SET pin (23pin), OCP_SET pin (24pin), and the thermistor element for temperature detection. |

| 23     | OVP_SET             | It configures the threshold value of the OVP (over voltage protection circuit).<br>It is set by dividing the voltage of VREG_50 pin (22pin) (5.0V) with the resistance.                                                                                                                                                                      |

| 24     | OCP_SET             | It configures the threshold value of the OCP (over current protection circuit).<br>It is set by dividing the voltage of VREG_50 pin (22pin) (5.0V) with the resistance.                                                                                                                                                                      |

### Pin function (2)

Table-1(2)

| Pin<br>No. | Pin name | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|------------|----------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 25         | EX_TSD   | It connects a thermistor element which monitors temperature around H-SW.<br>The thermistor element is connected between VREG_50 pin (22pin) and this pin.<br>The threshold voltage corresponding to TSD operating temperature is configured by<br>connecting the resistance between this pin and GND pin (20pin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |

| 26         | DC_IN    | This pin inputs the voltage which is boosted in the half bridge for a booster and is divided with the resistor.<br>When 2.0 $\mu$ s (typ.) has passed after the voltage of this pin exceeds the threshold value set by OVP_SET pin (23pin), OVP circuit drives and configures the voltage of GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V), and stops switching (Latch). In this time, FAULT pin (6pin) changes outputting "H" to "L" (= 0 V). To release the latch operation, re-starts the IC operation by setting VDD pin (18pin) 5.5 V or less or by setting RSTN pin (32pin) "L" ( $\leq$ 1.0 V).<br>After restarting, output of FAULT pin (6pin) returns "L" to "H".<br>(Refer to "Constant number for the threshold setting circuit of over voltage detection and voltage booster input circuit, and conversion equation to ADC input voltage" in details.) |

| 27         | SH_LG    | It is a reference pin for SH_IN pin (28pin) which detects the current flowing in the voltage booster circuit. This pin should be set the same potential as GND pin (20pin).                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 28         | SH_IN    | It detects the current flowing in the voltage booster circuit.<br>This current flowing is input by converting with the resistance.<br>When the voltage between this pin and SH_LG pin (27pin) exceeds the threshold value<br>set by OCP_SET pin (24pin), OCP circuit drives and configures the voltage of GL1 pin<br>(11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3<br>pin (16pin) "L" (= 0 V), and stops switching.<br>In this time, FAULT pin (6pin) changes outputting "H" (= 5.0 V) to "L".<br>When the current of the voltage booster circuit decreases to the current, which<br>corresponds to the threshold voltage, OCP is released and the IC operation restarts 1.0<br>ms (typ.) after release.<br>After restarting, FAULT pin (6pin) returns outputting "L" to "H."                                                                                                                      |

| 29         | PVn_IN   | These pins detect respectively a short-circuiting to the power supply and GND of the minus and the plus side, from the voltage of the minus side, the plus side, and the middle point of the solar panel.<br>PVn_IN pin inputs the voltage by dividing the voltage between the minus side of the solar panel                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |

| 30         | PVp_IN   | and GND, with a resistor.<br>PVp_IN pin inputs the voltage by dividing the voltage between the plus side of the solar panel<br>and GND, with a resistor.<br>PVc_IN pin inputs the voltage by dividing the voltage between the middle point of the solar                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 31         | PVc_IN   | panel and GND, with a resistor.<br>(Refer to 'Constant number for detecting voltage input circuit of PV voltage, PV current, and PV<br>short to the power supply or GND, and conversion equation to ADC input voltage' in details.)                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       |

| 32         | RSTN     | It forcedly resets the internal register externally.<br>When the voltage of this pin is configured 1.0 V or less, the register in the IC is reset<br>forcedly. Then, the reset is released when this pin is configured more than 4.0 V.<br>Do not apply this pin voltage of VREG_50 (5.0 V (typ.)) or more.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

Note 1: UART: Universal Asynchronous Receiver Transmitter

Note 2: Pull-down resistance in the IC is not connected to GL1 (11pin), GH1 (12pin), GL2 (13pin), GH2 (14pin), GL3 (15pin), and GH3 (16pin).

TC7716FTG

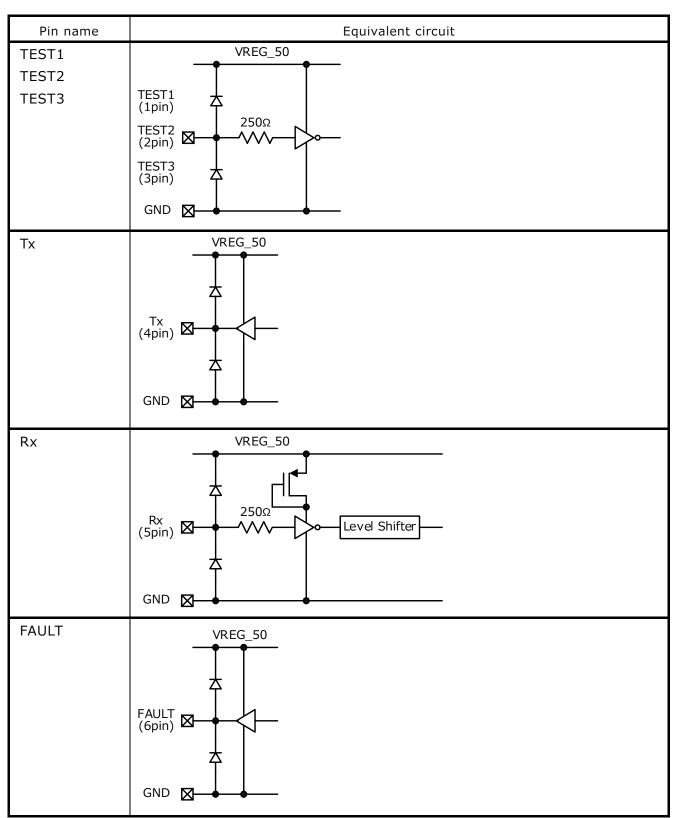

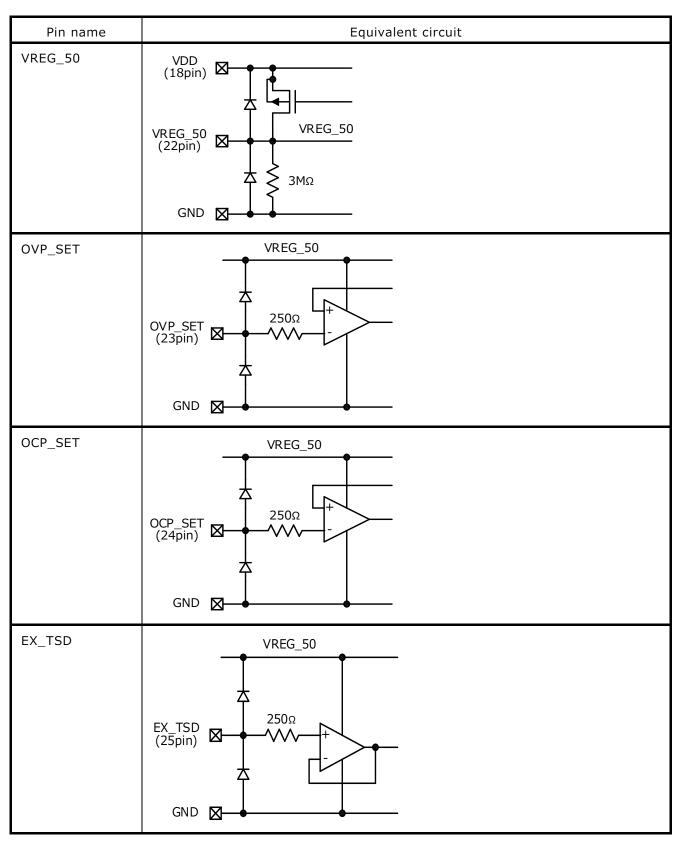

## I/O equivalent circuit (1)

Table-2(1)

TC7716FTG

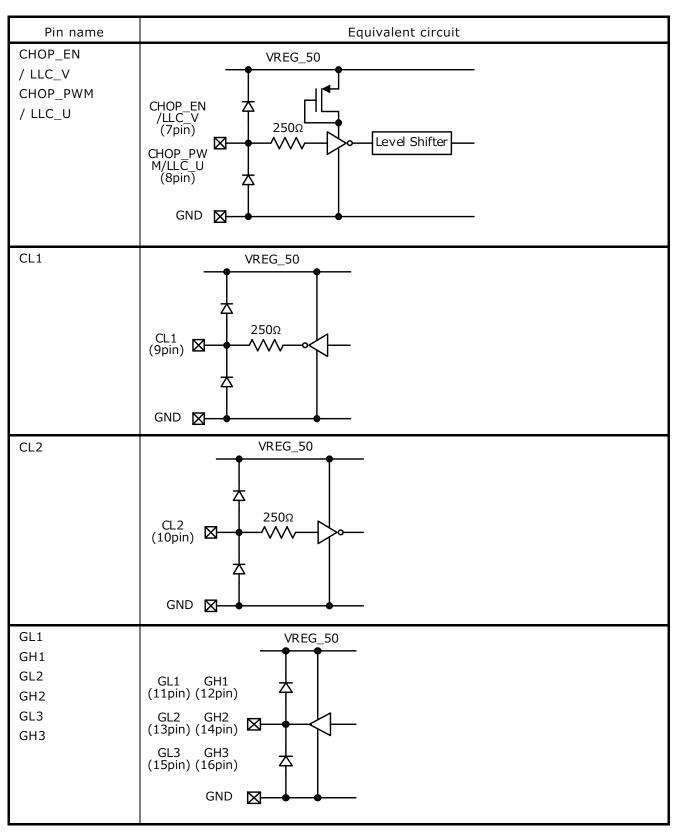

## I/O equivalent circuit (2)

Table-2(2)

TC7716FTG

### I/O equivalent circuit (3)

Table-2(3)

TC7716FTG

## I/O equivalent circuit (4)

Table-2(4)

## I/O equivalent circuit (5)

Table-2(5)

| Pin name | Equivalent circuit                |

|----------|-----------------------------------|

| RSTN     | VREG_50<br>KSTN<br>(32pin)<br>GND |

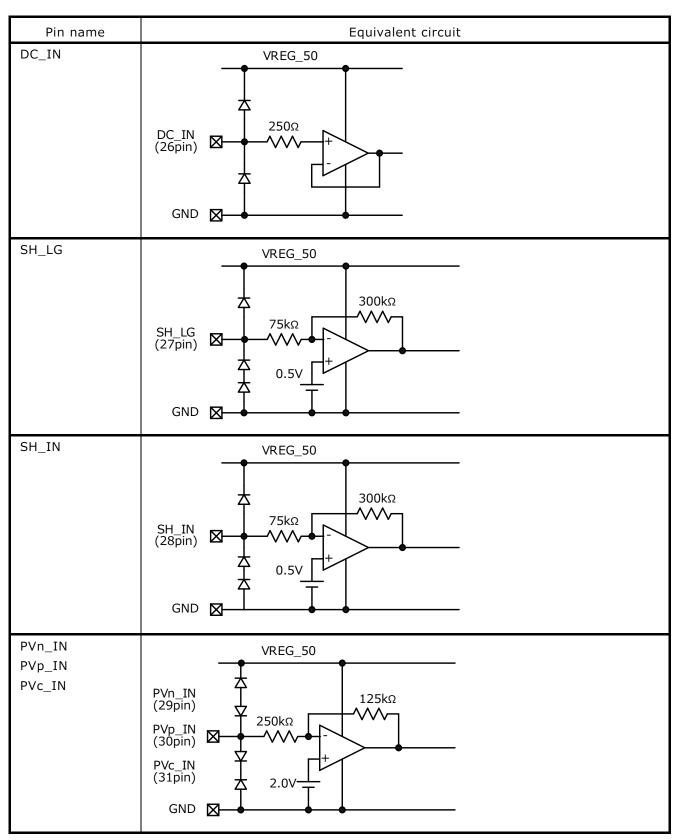

- Figure-2

- (\*) Some of the functional blocks, circuits, or constants in the block diagram may be omitted or simplified for explanatory purposes.

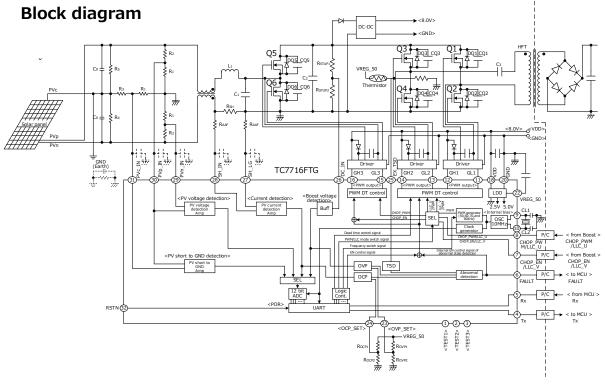

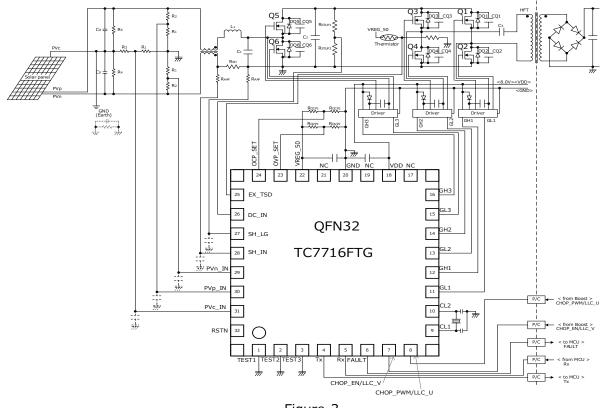

#### Example of application circuit

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage. Providing these application circuit examples does not grant a license for industrial property rights.

Figure-3

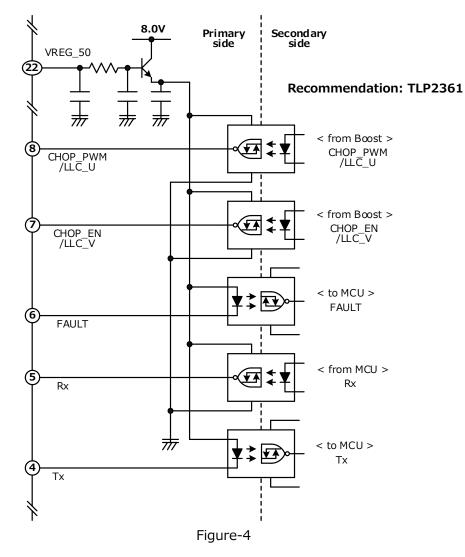

## Example of application circuit (Peripheral circuit of photo-coupler)

The application circuits shown in this document are provided for reference purposes only. Thorough evaluation is required, especially at the mass production design stage. Providing these application circuit examples does not grant a license for industrial property rights.

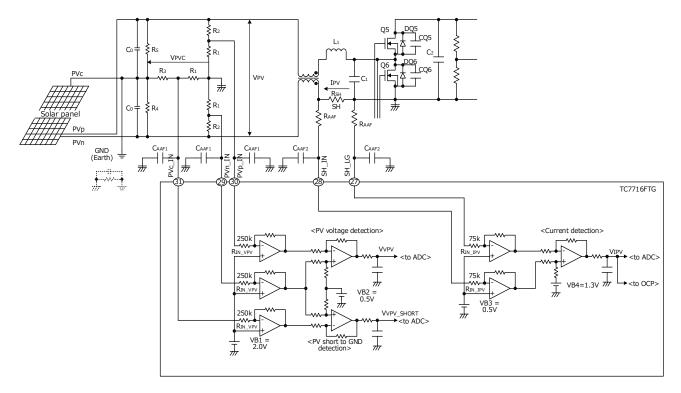

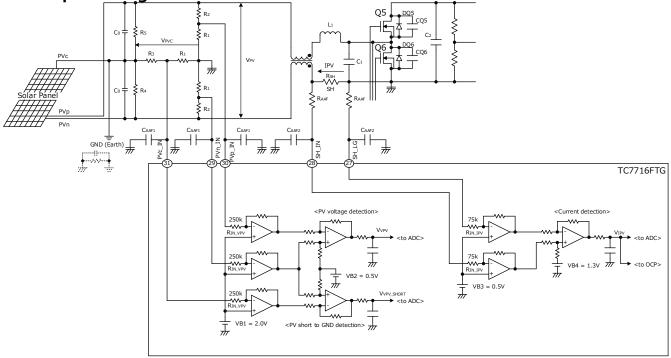

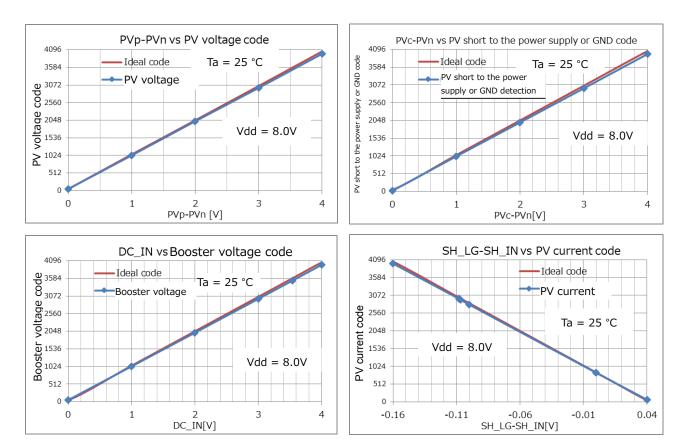

(1) Constant number for detecting voltage input circuit of PV voltage, PV current, and PV short to the power supply or GND, and conversion equation to ADC input voltage

Figure-5

The constant number for detecting voltage input circuit of PV voltage, PV current, and PV short to the power supply or GND, and the equivalent circuit of the ADC input in the IC are shown in the figure 5.

Input voltage for each pin is voltage-converted by the following equation, and is input to the ADC built in the IC.

When R1 to R5 (k $\Omega$ ), RSH (m $\Omega$ ), RAAF (k $\Omega$ ), VPV (V), IPV (A), and VPVC (V) are defined, the calculation is performed by the following equations.

1) Detecting voltage of PV voltage: VVPV (V)

$$V_{VPV} = V_{PV} \times \frac{R_1}{R_1 + R_2 + 4 R_1 \times R_2 \times 10^{-3}} + 0.5$$

The resistance is set to configure VVPV (V) as follows; 0.452 V  $\leq$  VVPV  $\leq$  4.548 V (for VPV (V))

2) Detecting voltage of PV current: VIPV (V)

$$V_{IPV} = 1.5 \times R_{SH} \times I_{PV} \times \frac{1}{75 + R_{AAF}} + 1.3$$

The resistance is set to configure VIPV (V) as follows; 0.452 V  $\leq$  VIPV  $\leq$  4.548 V (for IPV (A))

3) Detecting voltage of PV short to the power supply or GND: VVPV\_SHORT (V)

$$V_{VPV\_SHORT} = V_{PVC} \times \frac{R_1}{R_1 + R_2 + 4 R_1 \times R_2 \times 10^{-3}} + 0.5$$

© 2017

The resistance is set to configure VVPV\_SHORT (V) as follows;  $0.452 V \le VVPV_SHORT \le 4.548 V$  (for VPVC (V))

Then, the middle point voltage of PV (VPvc),  $K_1$  and  $K_2$  are obtained by the following equation.

$V_{PVC} = V_{PV} \times K_{1} \times \frac{R_{1} + R_{3} + 5 R_{1} \times R_{3} \times 10^{-3}}{R_{1} + R_{3} + 5 \times [R_{1} \times R_{3} + K_{2} \times (R_{1} + 200)] \times 10^{-3}}$  $K_{1} = \frac{R_{4}}{R_{4} + R_{5}} \qquad K_{2} = \frac{R_{4} \times R_{5}}{R_{4} + R_{5}}$

In the case of  $R_4 = R_5$ ,  $K_1 = 0.5$  and  $K_2 = 0.5^*R_4$ . Therefore the middle point voltage of PV (VPVC (V)) is obtained by the following equation.

$$V_{PVC} = V_{PV} \times 0.5 \times \frac{R_1 + R_3 + 5 R_1 \times R_3 \times 10^{-3}}{R_1 + R_3 + 5 \times [R_1 \times R_3 + 0.5 R_4 \times (R_1 + 200)] \times 10^{-3}}$$

Each value of obtained ADC input voltage (VVPV (V), VIPV (V), and VVPV\_SHORT (V)) minus 0.452V is converted to 12-bit binary code. And it is transmitted as ADC output from UART Tx pin (4pin).

<Detecting voltage of PV voltage is coded> (Vvpv-0.452) -> Converting to 12-bit binary code

<Detecting voltage of PV voltage is coded> (VIPV-0.452) -> Converting to 12-bit binary code

<Detecting voltage of PV short to the power supply or GND is coded > (Vvpv\_short-0.452) -> Converting to 12-bit binary code (2) Constant number for the threshold setting circuit of over voltage detection and voltage booster input circuit, and conversion equation to ADC input

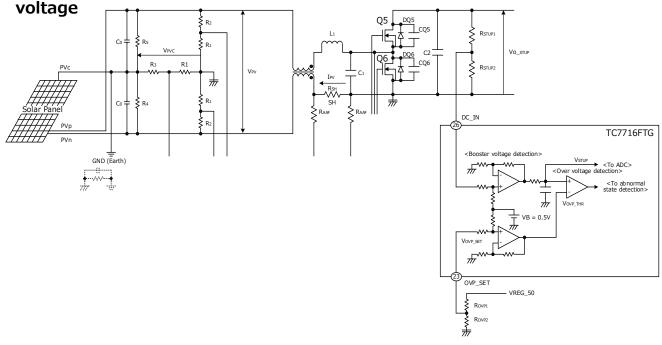

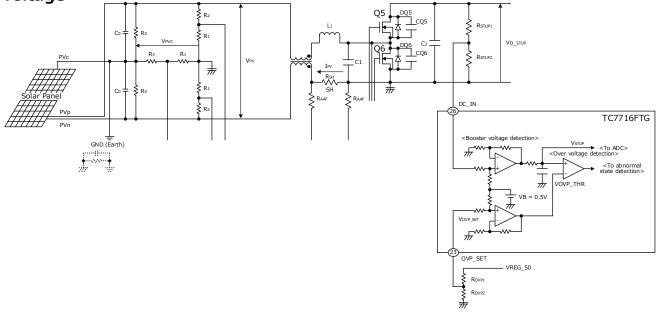

#### Figure-6

Constant numbers of the threshold setting circuit of over voltage detection and voltage booster input circuit, and the equation circuit to ADC input are shown in the figure 6.

Boosted voltage (Vo\_STUP (V)) is divided by the dividing resistance ([RSTUP1 ( $k\Omega$ )] and [RSTUP2 ( $k\Omega$ )]) and is input to DC\_IN pin (26pin). The voltage of VDC\_IN (V) input by DC\_IN pin is voltage-converted to VSTUP (V) by the following equation and is supplied to ADC in the IC and OVP detection comparator in each.

$V_{STUP} = V_{DC_{IN}} + 0.5$

The voltage of VDC\_IN (V) is obtained from the following equation.

$V_{DC_{IN}} = V_{o_{STUP}} \times \frac{R_{STUP2}}{R_{STUP1} + R_{STUP2}}$

The resistance is set to configure VDC\_IN (V) as follows;  $0V \le VDC_IN \le 4.048 V$

The value of voltage-converted VSTUP (V) minus 0.452 V is converted to 12-bit binary code. And it is transmitted as ADC output from UART Tx pin (4pin).

<Boosting voltage is coded> (VSTUP - 0.452) -> Converting 12-bit binary code

On the other hand, VSTUP (V), which is input to OVP detecting comparator, is compared to the threshold value (VOVP\_THR (V)) set by OVP\_SET pin (23pin). And when the following equation is obtained, the over voltage detecting circuit operates to configure GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V) and stops switching (Latch).

#### VSTUP $\geq$ VOVP\_THR

The threshold value of VOVP\_THR is

$$VOVP_THR = VOVP_SET + 0.5$$

Then,

$VDC_{IN} \ge VOVP_{SET}$

OVP threshold setting voltage (VovP\_SET (V)) is obtained by following equation when dividing resistance connected to OVP\_SET pin (23pin) is described [RovP1 ( $k\Omega$ )] and [RovP2 ( $k\Omega$ )], and the voltage of VREG\_50 pin (22pin) is described VvREG\_50 (= 5.0 V).

$Vovp\_set = Vvreg\_50 \times \frac{Rovp_2}{Rovp_1 + Rovp_2} = 5.0 \times \frac{Rovp_2}{Rovp_1 + Rovp_2}$

Therefore, the threshold value of over voltage detection is configured under the condition that satisfies the following equation.

$V_{DC_IN} \ge V_{OVP_SET} = 5.0 \times \frac{R_{OVP2}}{R_{OVP1} + R_{OVP2}}$

So, the relation of ROVP1 and ROVP2 is as follows;

$Rovp_1 \ge (\frac{5.0}{V_{DC_IN}} - 1) \times Rovp_2$

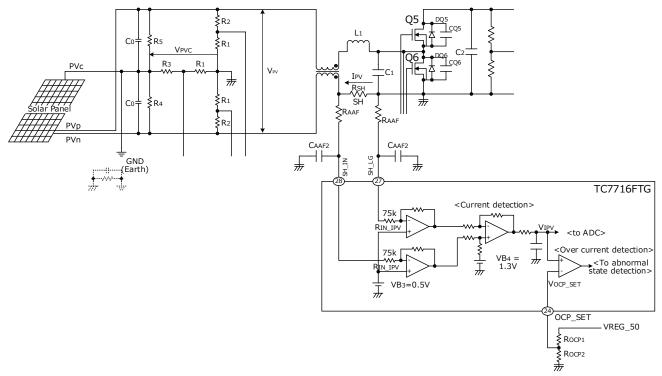

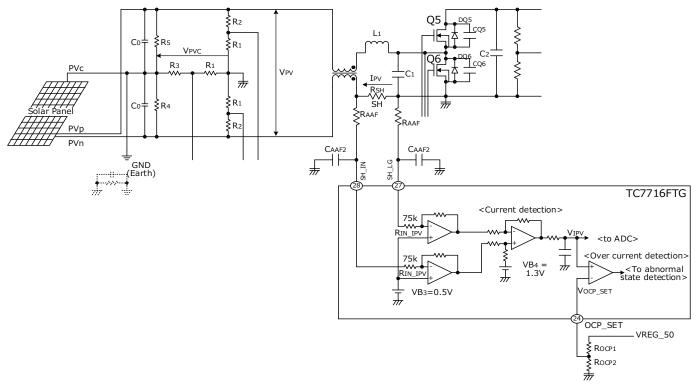

# (3) Constant number setting for threshold setting circuit of over current detection

#### Figure-7

The equivalent circuit for threshold setting circuit of over current detection is shown in Figure-7.

VIPV (V), which is inputted to OCP detecting comparator, is compared to the threshold value (VOCP\_SET (V)) set by OCP\_SET pin (24pin). And when the following formula is obtained, the over current detection circuit operates to configure GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V) and stops switching.

#### $V \mathsf{IPV} \geq V \mathsf{OCP}_\mathsf{SET}$

When RSH (m $\Omega$ ), IPV (A), and RAAF (k $\Omega$ ) are defined, VIPV is obtained by the following equation.

$$V_{IPV} = 1.5 \times R_{SH} \times I_{PV} \times \frac{1}{75 + R_{AAF}} + 1.3$$

When the voltage between SH\_IN pin (28pin) and SH\_LG pin (27pin) is defined VOCP\_IN (V) (When the current of IPV flows in the direction of the arrow in Figure-7, it is defined VOCP\_IN >0). VOCP\_IN is obtained by the following equation.

$$V_{OCP_IN} = \frac{3}{40} \times R_{SH} \times I_{PV} \times \frac{1}{75 + R_{AAF}}$$

$$V_{IPV} = 20 \times V_{OCP_IN} + 1.3$$

OCP threshold setting voltage (VocP\_SET(V)) is obtained by following equation when dividing resistance connected to OCP\_SET pin (24pin) is described [RocP1 ( $k\Omega$ )] and [RocP2 ( $k\Omega$ )], and the voltage of VREG\_50 pin (22pin) is described VVREG\_50 (= 5.0 V).

$VOCP\_SET = VVREG\_50 \times \frac{ROCP2}{ROCP1 + ROCP2} = 5.0 \times \frac{ROCP2}{ROCP1 + ROCP2}$

Therefore, the threshold value of over current detection is configured under the condition that satisfies the following equation.

(1) In case of focusing on the voltage (VocP\_IN (V)) between SH\_IN pin (28pin) and SH\_LG pin (27pin),

$$V_{OCP_IN} \ge \frac{1}{20} \times (V_{OCP_SET} - 1.3)$$

$$= \frac{1}{20} \times \frac{3.7 \times R_{OCP2} - 1.3 \times R_{OCP1}}{R_{OCP1} + R_{OCP2}}$$

(2) In case of focusing on PV current (IPV(A)),

$$I_{PV} \ge \frac{2}{3} \times \frac{75 + R_{AAF}}{R_{SH}} \times (V_{OCP\_SET} - 1.3)$$

$$= \frac{2}{3} \times \frac{75 + R_{AAF}}{R_{SH}} \times \frac{3.7 \times R_{OCP2} - 1.3 \times R_{OCP1}}{R_{OCP1} + R_{OCP2}}$$

The relation between ROCP1 and ROCP2 is as follows;

(1) In case of focusing on the voltage (VocP\_IN (V)) between SH\_IN pin (28pin) and SH\_LG pin (27pin)

$$ROCP1 \geq \frac{0.185 - VOCP_{IN}}{0.065 + VOCP_{IN}} \times ROCP2$$

(2) In case of focusing on PV current (IPV(A)),

$$ROCP1 \ge \frac{3.7 \times K - IPV}{1.3 \times K + IPV} \times ROCP2$$

$$*K = \frac{2}{3} \times \frac{75 + RAAF}{RSH}$$

## Appendix

Example of calculation

(1) Constant number for detecting voltage input circuit of PV voltage, PV current, and PV short to the power supply or GND, and conversion equation to ADC input voltage

Figure-5 (Re-posting)

When R1=27 k $\Omega$ , R2=540 k $\Omega$ , R3=540 k $\Omega$ , R4=200 k $\Omega$ , R5=200 k $\Omega$ , RSH=12 m $\Omega$ , and RAAF=1 k $\Omega$  are defined,

1) Detecting voltage of PV voltage: ADC input voltage  $V_{VPV}$  (V) is obtained by the following equation.

$$V_{VPV} = V_{PV} \times \frac{R_1}{R_1 + R_2 + 4 R_1 \times R_2 \times 10^{-3}} + 0.5$$

$$= \frac{25}{579} \times V_{PV} + 0.5$$

<Detecting voltage of PV voltage is coded>

$$V_{VPV} - 0.452 = \left(\frac{25}{579} \times V_{PV} + 0.5\right) - 0.452$$

$$= \frac{25}{579} \times V_{PV} + 0.048$$

This value is converted to 12-bit binary code. (Refer to Table-3.)

code

E5B

FC6

| ADC input voltage (V) | ADC output                                 |

|-----------------------|--------------------------------------------|

| (VVPV)                | (Hex)                                      |

| 0.500                 | 030                                        |

| 1.450                 | 3E6                                        |

| 1.687                 | 4D3                                        |

| 2.767                 | 90B                                        |

| 3.522                 | BFE                                        |

|                       | (VVPV)<br>0.500<br>1.450<br>1.687<br>2.767 |

4.127

4.490

| Tab | e-3 |

|-----|-----|

| iub |     |

2) Detecting voltage of PV current: ADC input voltage VIPV (V) is obtained by the following equation.

$$V_{IPV} = 1.5 \times R_{SH} \times I_{PV} \times \frac{1}{75 + R_{AAF}} + 1.3$$

$$= \frac{9}{38} \times I_{PV} + 1.3$$

<Detecting voltage of PV current is coded>

84.0

92.4

$$V_{IPV} - 0.452 = \left(\frac{9}{38} \times I_{PV} + 1.3\right) - 0.452$$

$$= \frac{9}{38} \times I_{PV} + 0.848$$

This value is converted to 12-bit binary code. (Refer to Table-4.)

| PV current (A)<br>(IPV) | ADC input voltage (V)<br>(VIPV) | ADC output code<br>(Hex) |

|-------------------------|---------------------------------|--------------------------|

| 0.00                    | 1.300                           | 350                      |

| 7.50                    | 3.076                           | A40                      |

| 8.25                    | 3.254                           | AF2                      |

| 11.25                   | 3.964                           | DB8                      |

| 13.12                   | 4.407                           | F73                      |

Table-4

3) Detecting voltage of PV short to the power supply or GND: ADC input voltage VVPV\_SHORT(V) is obtained by the following equation.

$$V_{VPV\_SHORT} = V_{PVC} \times \frac{R_1}{R_1 + R_2 + 4 R_1 \times R_2 \times 10^{-3}} + 0.5$$

$$= \frac{25}{579} \times V_{PVC} + 0.5$$

Although the middle point voltage of PV (VPvc) is obtained by the following equation: R4=R5=200 kΩ

$$V_{PVC} = V_{PV} \times 0.5 \times \frac{R_1 + R_3 + 5 R_1 \times R_3 \times 10^{-3}}{R_1 + R_3 + 5 \times [R_1 \times R_3 + 0.5 R_4 \times (R_1 + 200)] \times 10^{-3}}$$

$$= \frac{6399}{15068} \times V_{PV}$$

ADC input voltage is obtained by the following equation.

$V_{VPV_short} = \frac{25}{579} \times (\frac{6399}{15068} \times V_{PV}) + 0.5$

<Detecting voltage of PV short to the power supply and GND is coded>

$VVPV\_SHORT - 0.452 = (\frac{25}{579} \times (\frac{6399}{15068} \times VPV) + 0.5) - 0.452$  $=\frac{25}{579}$  × ( $\frac{6399}{15068}$  × VPV ) + 0.048

This value is converted to 12-bit binary code. (Refer to Table-5.)

Table-5

| PV voltage (V)<br>(VPV) | ADC input voltage (V)<br>(VVPV_SHORT) | ADC output code<br>(Hex) |

|-------------------------|---------------------------------------|--------------------------|

| 0.00                    | 0.500                                 | 030                      |

| 22.0                    | 0.903                                 | 1C3                      |

| 27.5                    | 1.004                                 | 228                      |

| 52.5                    | 1.463                                 | 3F3                      |

| 70.0                    | 1.784                                 | 534                      |

| 84.0                    | 2.040                                 | 634                      |

| 92.4                    | 2.194                                 | 6CE                      |

(2) Constant number for the threshold setting circuit of over voltage detection and voltage booster input circuit, and conversion equation to ADC input voltage

Figure-6 (Re-posting)

1) Detecting voltage of boosting voltage: ADC input voltage VSTUP (V) is obtained by

$V_{STUP} = V_{DC_{IN}} + 0.5$

When RSTUP1 = 470 k $\Omega$ , and RSTUP2 = 27 k $\Omega$  are defined,

$V_{DC_{IN}} = V_{o_{stup}} \times \frac{R_{stup2}}{R_{stup1} + R_{stup2}} = \frac{27}{497} \times V_{o_{stup}}$

Therefore, ADC input voltage VSTUP (V) is obtained by the following equation.

$$V_{\text{STUP}} = \left( \frac{27}{497} \times V_{\text{o}} \text{STUP} \right) + 0.5$$

<Voltage boosting is coded>

$$V_{\text{STUP}} - 0.452 = \left(\frac{27}{497} \times V_{\text{o}\_\text{STUP}} + 0.5\right) - 0.452$$

$$= \frac{27}{497} \times V_{\text{o}\_\text{STUP}} + 0.048$$

This value is converted to 12-bit binary code. (Refer to Table-6.)

| Table-0 | Table-6 |  |

|---------|---------|--|

|---------|---------|--|

| Boosting voltage (V)<br>(Vo_STUP) | ADC input voltage (V)<br>(VSTUP) | ADC output code<br>(Hex) |

|-----------------------------------|----------------------------------|--------------------------|

| 0.00                              | 0.500                            | 030                      |

| 22.0                              | 1.695                            | 4DB                      |

| 27.5                              | 1.994                            | 606                      |

| 53.0                              | 3.379                            | B6F                      |

| 60.0                              | 3.760                            | CEC                      |

| 67.0                              | 4.140                            | F68                      |

| 72.0                              | 4.411                            | F77                      |

2) Threshold voltage setting of over voltage detection

When 120% (= 72 V) of boosting voltage (Vo\_STUP (V) = 60 V) is regarded the over voltage, the voltage of DC\_IN pin (26pin) (VDC\_IN (V)) is obtained by the following equation.

$$V_{DC_{IN}} = V_{0}_{STUP} \times \frac{R_{STUP2}}{R_{STUP1} + R_{STUP2}} = 72 \times \frac{27}{497} \approx 3.911$$

\*Rstup1 = 470 kΩ, Rstup2 = 27 kΩ

When RovP2=47 k $\Omega$  is defined, the equation is as follows;

$$\mathsf{R}_{\mathsf{OVP1}} \geq (\frac{5.0}{\mathsf{V}_{\mathsf{DC}_{\mathsf{IN}}}} - 1) \times \mathsf{R}_{\mathsf{OVP2}} \doteq 0.2783 \times \mathsf{R}_{\mathsf{OVP2}}$$

The threshold value can be configured by considering ROVP1  $\approx$  13 k $\Omega$  from above equation.

(3) Constant number setting for threshold setting circuit of over current detection

Figure-7 (Re-posting)

When 150% (= 11.25 A) or more of PV current (IPv (A)) 7.5 A is regarded the over current, the voltage (VocP\_IN (V)) between SH\_IN pin (28pin) and SH\_LG pin (27pin) is obtained by the following equation.

$V_{OCP_IN} = \frac{3}{40} \times R_{SH} \times I_{PV} \times \frac{1}{75 + R_{AAF}}$  $= \frac{9}{760} \times 11.25$  $*R_{SH}=12 \text{ m}\Omega, R_{AAF}=1 \text{ k}\Omega$

When ROCP2=68 k $\Omega$  is defined,

$\mathsf{Rocp1} \geq \frac{0.185 - \mathsf{Vocp_{IN}}}{0.065 + \mathsf{Vocp_{IN}}} \times \mathsf{Rocp2} \doteq 0.2612 \times \mathsf{Rocp2}$

The threshold value can be configured as  $ROCP1 \approx 18 \text{ k}\Omega$  from above equation.

#### **Function description**

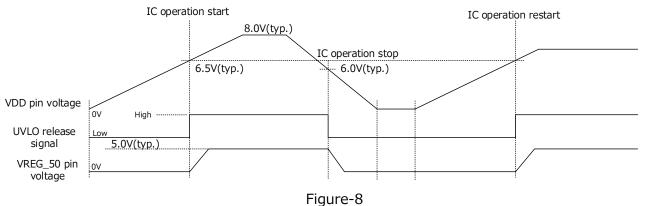

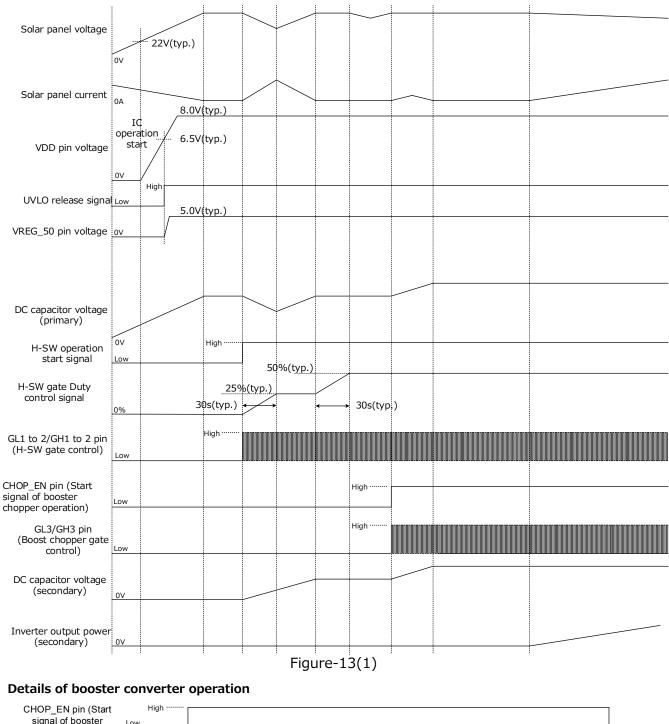

#### (1) UVLO (under voltage lockout) function

When the voltage of VDD pin (18pin) becomes 6.5 V (typ.) or more, UVLO is released and the IC operation starts. When the voltage of VDD falls 6.0 V (typ.) or less in the normal operation, UVLO operates and the IC operation stops. However, when it returns to 6.5 V (typ.) or more, the IC operation starts again.

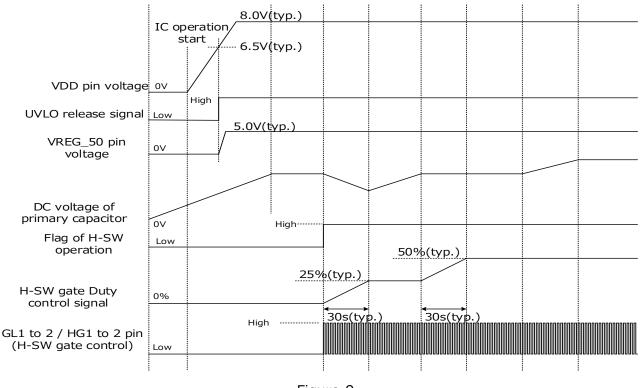

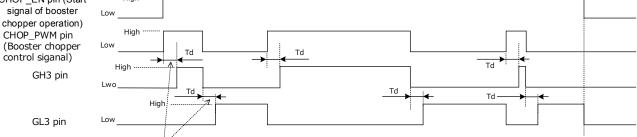

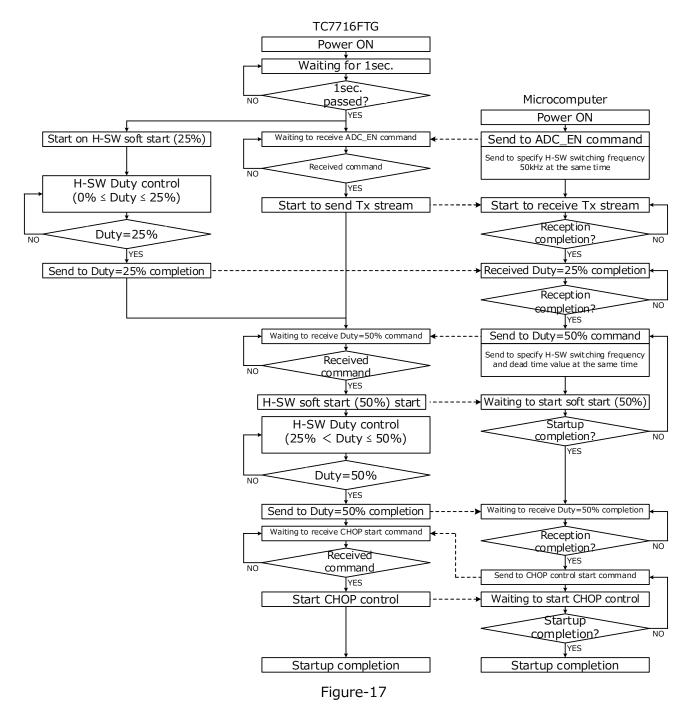

#### (2) Soft start function

Switching pulse of H-SW starts when Duty is 0%. After 30 s passes, the duty becomes 25% by the soft start function. After the information that the duty becomes 25% is sent to microcomputer through UART, the control microcomputer transmits the command (D2 = [1] in the receiving protocol Byte\_1) that the duty should be extended to 50% through UART. Then, the duty increases from 25% to 50% 30 s after the command is received by the soft start function. (As for detailed communication flow with the control microcomputer, refer to Figure-17.)

#### Figure-10

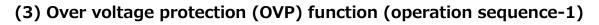

OVP operates under the condition that the boosting voltage exceeds the over voltage detection threshold for 2  $\mu$ s or more because the temporary blackout or open state are generated at the system connection side (secondary side) in the normal operation after completing IC power on. GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) are configured "L" (= 0V) and switching operation is stopped (Latch).

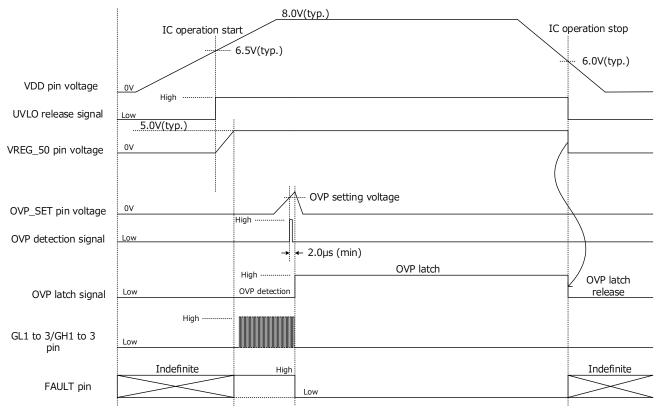

#### (4) Over voltage protection (OVP) function (operation sequence-2)

When OVP operates to configure GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V) and stops switching (latch), latch is released and the operation starts again by configuring RSTN pin (32pin) "L" ( $\leq$  1.0 V). After the IC operation starts again, FAULT pin (6pin) outputs "L" to "H" again.

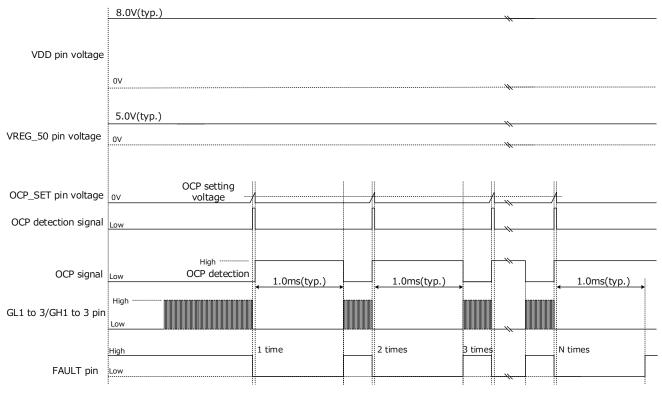

#### (5) Over current protection (OCP) function

It limits the current flowing in the voltage booster circuit.

When the voltage between SH\_IN pin (28pin) and SH\_LG pin (27pin) exceeds the threshold value set by OCP\_SET pin (24pin), OCP circuit operates to configure GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V) and stops switching.

In this time, the voltage of FAULT pin (6pin) becomes "H" (= 5.0 V pull-up) to "L" and it informs the microcomputer for system control that the OCP operates.

1.0 ms (typ.) passes after the over current state is released, OCP is released and the IC re-starts operation without soft start. When it re-starts, FAULT pin (6pin) outputs "L" to "H".

When system failure is not cleared and "stop" and "re-start" repeat N times, the microcomputer for system control judges that this state is system malfunction. Then it transmits stop command through UART and stops IC operation (latch).

## (6) Thermal shutdown (TSD) function

When ambient temperature rises, the resistance of the thermistor decreases and the pin voltage rises. The pin voltage rises to the threshold value which corresponds to TSD operation temperature or more, TSD circuit operates and configures GL1 pin (11pin), GH1 pin (12pin), GL2 pin (13pin), GH2 pin (14pin), GL3 pin (15pin), and GH3 pin (16pin) "L" (= 0 V) and stops switching.

In this time, FAULT pin (6pin) outputs "H" (= 5.0 V pull up) to "L" and it informs the microcomputer for system control that TSD operates.

When the ambient temperature falls to the threshold value which corresponds to TSD release temperature or less, TSD is released and the IC re-starts operation by soft start.

When the IC re-starts operation, FAULT pin (6pin) outputs "L" to "H".

When system failure is not cleared and "stop" and "re-start" repeat N times, the microcomputer for system control judges that this state is system malfunction. Then it transmits stop command through UART and stops IC operation (latch).

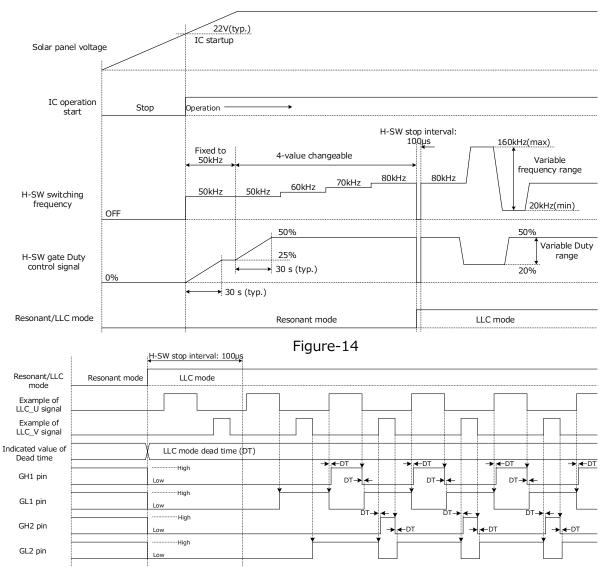

When the GH3 and GL3 pins output H level by the booster chopper control signal, the dead time, Td is output as the head period. When the pulse width of the booster chopper control signal is shorter than Td, the booster chopper signal inputs enough longer time width than Td because the GH3 and GL3 pins do not output H level.

Figure-13(2)

# Resonance control mode -> Shift sequence of LLC control mode (Example of control by external input signal)

Figure-15

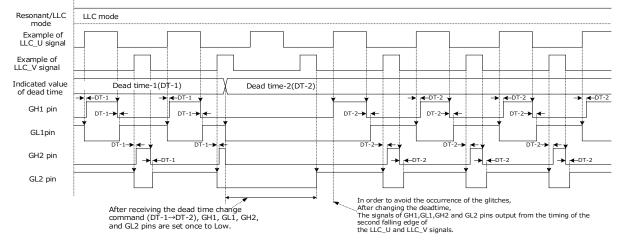

#### Changing sequence of dead time during operation in LLC control mode

#### Communication flow between TC7716FTG and Control MCU in startup

(\*) During soft start (Duty change), do not change switching frequency of H-SW and designated value of dead time.

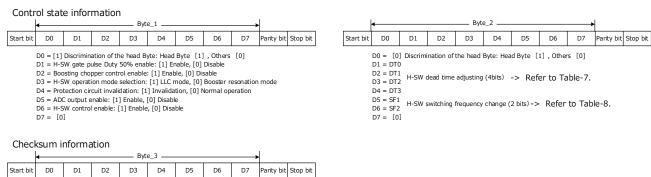

#### **UART transmitting protocol**

#### **UART** receiving protocol

| D0 = [0] | Discrimina | ition of th | e head By | te: Head I | Byte [1] | , Others | [0] |  |

|----------|------------|-------------|-----------|------------|----------|----------|-----|--|

D0 = [0]D1 = CS0D1 = CS1D3 = CS2D4 = CS3D5 = CS4D6 = CS5D7 = CS6D7 = CS6D5 = CS7D5 = CS7D7 = C

Checksum (7 bits) Checksum: MOD ( - ( Byte\_1 + Byte\_2 ) , 128 )

Transmission speed: 500 kbps (2µs / bit) Parity: Even

[1]

[1]

#### Figure-19

#### Table-7

| H-SW dead time adjusting (4 bits) |     |     |     |                     |  |

|-----------------------------------|-----|-----|-----|---------------------|--|

| D4                                | D3  | D2  | D1  | H-SW dead time [µs] |  |

| [0]                               | [0] | [0] | [0] | 0.9                 |  |

| [0]                               | [0] | [0] | [1] | 1.0                 |  |

| [0]                               | [0] | [1] | [0] | 1.1                 |  |

| [0]                               | [0] | [1] | [1] | 1.2                 |  |

| [0]                               | [1] | [0] | [0] | 1.3                 |  |

| [0]                               | [1] | [0] | [1] | 1.4                 |  |

| [0]                               | [1] | [1] | [0] | 1.5                 |  |

| [0]                               | [1] | [1] | [1] | 1.6                 |  |

| [1]                               | [0] | [0] | [0] | 1.7                 |  |

| [1]                               | [0] | [0] | [1] | 1.8                 |  |

| [1]                               | [0] | [1] | [0] | 1.9                 |  |

| [1]                               | [0] | [1] | [1] | 2.0                 |  |

| [1]                               | [1] | [0] | [0] | 2.1                 |  |

| [1]                               | [1] | [0] | [1] | 2.2                 |  |

| [1]                               | [1] | [1] | [0] | 2.3                 |  |

| [1]                               | [1] | [1] | [1] | 2.4                 |  |

#### Table-8

| H-SW switching frequency change (2 bits) |     |                               |  |  |  |

|------------------------------------------|-----|-------------------------------|--|--|--|

| D6                                       | D5  | H-SW switching frequency[kHz] |  |  |  |

| [0]                                      | [0] | 50.000                        |  |  |  |

| [0]                                      | [1] | 59.524                        |  |  |  |

| [1]                                      | [0] | 69 444                        |  |  |  |

80.645

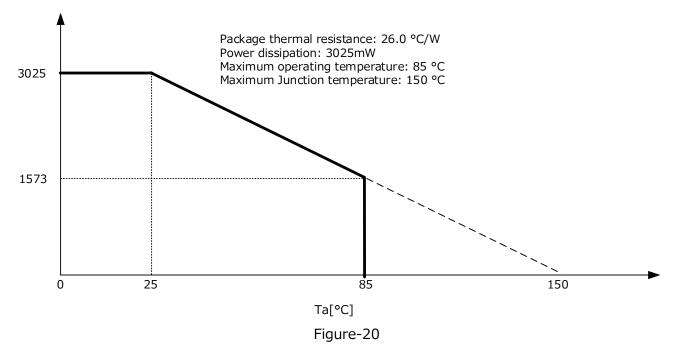

### Absolute maximum ratings (Unless otherwise specified, Ta=25°C)

| Table-9                                 |                  |             |      |  |  |  |  |

|-----------------------------------------|------------------|-------------|------|--|--|--|--|

| Characteristics                         | Symbol           | Rating      | Unit |  |  |  |  |

| Power supply voltage                    | Vdd              | 15.0        | V    |  |  |  |  |

| Maximum applied voltage<br>for each pin | VIMAX            | (*1)        | V    |  |  |  |  |

| Minimum applied voltage<br>for each pin | ViMIN            | GND-0.3(*2) | V    |  |  |  |  |

| Power dissipation (*3)                  | P <sub>D</sub>   | 3025        | mW   |  |  |  |  |

| Operating temperature                   | T <sub>opr</sub> | - 40 to 85  | °C   |  |  |  |  |

| Storage temperature                     | T <sub>stg</sub> | - 55 to 150 | °C   |  |  |  |  |

| Junction temperature                    | Tj               | 150         | °C   |  |  |  |  |

\*1:

#### Table-10(Maximum applied voltage for each pin)

| Pin No. | Symbol              | Rating         | Unit |  |

|---------|---------------------|----------------|------|--|

| 1       | TEST1               | Vvreg_50 + 0.5 |      |  |

| 2       | TEST2               | Vvreg_50 + 0.5 |      |  |

| 3       | TEST3               | Vvreg_50 + 0.5 |      |  |

| 4       | Тх                  | Vvreg_50 + 0.5 |      |  |

| 5       | Rx                  | Vvreg_50 + 0.5 |      |  |

| 6       | FAULT               | Vvreg_50 + 0.5 |      |  |

| 7       | CHOP_EN<br>/ LLC_V  | Vvreg_50 + 0.5 |      |  |

| 8       | CHOP_PWM<br>/ LLC_U | Vvreg_50 + 0.5 | V    |  |

| 9       | CL1                 | Vvreg_50 + 0.5 |      |  |

| 10      | CL2                 | Vvreg_50 + 0.5 |      |  |

| 11      | GL1                 | Vvreg_50 + 0.5 |      |  |

| 12      | GH1                 | Vvreg_50 + 0.5 |      |  |

| 13      | GL2                 | Vvreg_50 + 0.5 |      |  |

| 14      | GH2                 | Vvreg_50 + 0.5 |      |  |

| 15      | GL3                 | Vvreg_50 + 0.5 |      |  |

| 16      | GH3                 | Vvreg_50 + 0.5 |      |  |

| Pin No. | Symbol  | Rating         | Unit |

|---------|---------|----------------|------|

| 17      | NC      | -              |      |

| 18      | VDD     | 15.0           |      |

| 19      | NC      | -              |      |

| 20      | GND     | -              |      |

| 21      | NC      | -              |      |

| 22      | VREG_50 | (*4)           |      |

| 23      | OVP_SET | Vvreg_50 + 0.5 |      |

| 24      | OCP_SET | Vvreg_50 + 0.5 | V    |

| 25      | EX_TSD  | Vvreg_50 + 0.5 | v    |

| 26      | DC_IN   | Vvreg_50 + 0.5 |      |

| 27      | SH_LG   | VVREG_50 + 0.5 |      |

| 28      | SH_IN   | Vvreg_50 + 0.5 |      |

| 29      | PVn_IN  | Vvreg_50 + 1.0 |      |

| 30      | PVp_IN  | Vvreg_50 + 1.0 |      |

| 31      | PVc_IN  | Vvreg_50 + 1.0 |      |

| 32      | RSTN    | Vvreg_50 + 0.5 |      |

|         |         |                |      |

\*2: 29pin (PVn\_IN), 30pin (PVp\_IN), and Pin 31pin (PVc\_IN): GND - 2.0 V

layer 3.5% (only pin assignment) In case of Ta = 25 °C or more, the

power dissipation of 24.2 mW is decreased per 1 °C rising.

\*4: Do not apply voltage from outside of the IC.

The absolute maximum ratings of a semiconductor device are a set of ratings that must not be exceeded, even for a moment. Do not exceed any of these ratings. Exceeding the rating (s) may cause the device breakdown, damage or deterioration, and may result injury by explosion or combustion. Please use the IC within the specified operating ranges.

#### Package power dissipation (PD-Ta)

Power dissipation (PD) [mW]

## Operating condition (Ta = 25 °C)

#### Table-11

| Characteristics             | Sym<br>bol | Remarks | Min | Тур. | Max  | Unit |

|-----------------------------|------------|---------|-----|------|------|------|

| Power supply voltage (Note) | Vdd        | VDD pin | 7.2 | -    | 14.0 | V    |

Note: Though it is a necessary power supply voltage range to operate the IC in stable, the IC starts operation at Startup voltage (Vstr).

# Electrical characteristics (1) (Unless otherwise specified, Ta = 25 °C, Vdd = 8.0 V)

| Characteristics                           | Symbol       | Remarks                                                                                     | Min        | Тур.       | Max         | Unit |

|-------------------------------------------|--------------|---------------------------------------------------------------------------------------------|------------|------------|-------------|------|

| Startup voltage<br>(UVLO release voltage) | Vstr         |                                                                                             | 6.0        | 6.5        | 7.0         | V    |

| UVLO operation voltage                    | Vuvlo        |                                                                                             | 5.5        | 6.0        | 6.5         | V    |

| Consumption current                       | Idd          | Pulse output pin: Open<br>Switching frequency:50 kHz                                        | -          | -          | 30          | mA   |

| Reset voltage                             | Vrston       |                                                                                             | 1.0        | -          | -           | V    |

| Reset release voltage                     | Vrstoff      | RSTN pin voltage                                                                            | -          | -          | 4.0         |      |

| VREG_50 output voltage                    | VREG_50      |                                                                                             | 4.75       | 5.00       | 5.25        | V    |

| VREG_50 output current                    | Ireg50       |                                                                                             | -          | -          | 3.0         | mA   |

| I/O characteristics of digit              | al interface | block (Tx, Rx, FAULT, CHOP_EN/                                                              | LLC_V, CHO | P_PWM/LLC_ | J each pin) |      |

| High level input voltage                  | VIH_PC       |                                                                                             | 3.15       | -          | -           | V    |

| Low level input voltage                   | VIL_PC       |                                                                                             | -          | -          | 0.90        | V    |

| High level input current                  | IIH_PC       | Pin voltage: 5.0 V                                                                          | -1.0       | -          | -           | μA   |

| Low level input current                   | IIL_PC       | Pin voltage: GND                                                                            | -          | -          | 1.0         | μA   |

| High level output voltage                 | VOH_PC       | Isource = 10 mA                                                                             | 4.50       | -          | -           | V    |

| Low level output voltage                  | VOL_PC       | Isink = 10 mA                                                                               | -          | -          | 0.25        | V    |

| Booster DC-DC block                       |              |                                                                                             |            |            |             |      |

| Maximum voltage of output pulse           | VOH_GHL3     | GH3, GL3 pin: Isource = 5.0mA                                                               | 4.5        | -          | -           | v    |

| Minimum voltage of output pulse           | VOL_GHL3     | GH3, GL3 pin: Isink = 5.0mA                                                                 | -          | -          | 0.5         | V    |

| Dead time                                 | Td           | Crystal oscillator (10 MHz)                                                                 | 180        | 200        | 220         | ns   |

| Pin input current                         | IDC_IN       | DC_IN pin voltage: 5.0 V                                                                    | - 1.0      | -          | 1.0         | μA   |

| OVP operation voltage                     | VOVP-on      | DC_IN pin voltage when OVP_SET pin voltage is 3.5 V.                                        | 3.15       | 3.50       | 3.85        | V    |

| Starting time of<br>OVP operation         | TOVP-on      | DC_IN pin voltage rises from 3.0 V<br>to 4.0 V (Step) when OVP_SET pin<br>voltage is 3.5 V. | 2.8        | 4.3        | 5.8         | μS   |

| OCP operation voltage                     | VOCP-on      | Voltage (VocP_IN) between SH_IN<br>and SH_LG when OCP_SET pin<br>voltage is 3.5 V.          | 99         | 110        | 121         | mV   |

| OCP release time                          | TOCP-off     |                                                                                             | -          | 1.0        | -           | ms   |

| Thermal shutdown block                    |              |                                                                                             |            |            |             |      |

| Thermal shutdown voltage                  | VTTSD-on     |                                                                                             | -          | -          | 4.4         |      |

| Thermal shutdown release voltage          | VTTSD-off    | EXT_TSD pin voltage                                                                         | 3.8        | -          | -           | V    |

| Flowing current of input pin              | ITSD_IN      | Applied voltage of EXT_TSD pin:<br>4.5 V                                                    | - 1.0      | -          | 1.0         | μA   |

Table-12

# Electrical characteristics (2) (Unless otherwise specified, Ta = 25 °C, Vdd = 8.0 V)

Table-13

| Characteristics                     | Symbol         | Remarks                                                               | Min    | Тур.   | Мах  | Unit |

|-------------------------------------|----------------|-----------------------------------------------------------------------|--------|--------|------|------|

| H-SW block                          |                |                                                                       |        |        |      |      |

|                                     | Fhsw_50        | Crystal oscillator (10 MHz)<br>UART receiving Byte_2 : D6 = 0, D5 = 0 | -      | 50.000 | -    |      |

| Switching frequency                 | Fhsw_60        | UART receiving Byte $_2$ : D6 = 0, D 5=1                              | -      | 59.524 | -    | kHz  |

|                                     | Fhsw_70        | UART receiving Byte _2 : D6 = 1, D 5=0                                | -      | 69.444 | -    | ]    |

|                                     | Fhsw_80        | UART receiving Byte $_2$ : D6 = 1, D5 = 1                             | -      | 80.645 | -    |      |

| Soft start time                     | Tss            | 1st and 2nd each soft start time                                      | -      | 30     | -    | S    |

| Maximum voltage of output pulse     | VOH_ GHL12     | GH1, 2, and GL1, 2 pin: Isource=5.0 mA                                | 4.5    | -      | -    | v    |

| Minimum voltage of output pulse     | VOL_ GHL12     | GH1, 2, and GL1, 2 pin: Isink=5.0 mA                                  | -      | -      | 0.5  | v    |

| PWM pulse duty                      | DGHL12         | Fixed value                                                           | -      | 50     | -    | %    |

| Dead time adjusting range           | Tdmin          | UART receiving Byte $_2$<br>D4 = 0, D3 = 0, D2 = 0, D1 = 0            | 0.85   | 0.90   | 0.95 | μS   |

|                                     | Tdmax          | D4 = 1, D3 = 1, D2 = 1, D1 = 1                                        | 2.28   | 2.40   | 2.52 |      |

| Dead time adjusting step            | Tdsetp         | Adjusting step per 1 bit (4 bits)                                     | -      | 100    | -    | ns   |

| PV voltage detection block          |                |                                                                       |        |        |      |      |

| Maximum voltage of difference input | ∆Vdif_PVp      | Between PVp_IN and PVn_IN                                             | 0      | -      | 4.0  | V    |

| Offset voltage of difference input  | ΔVPVp          | AD output conversion in short between<br>PVp_IN and PVn_IN            | - 100  | 0      | 100  | mV   |

|                                     | IPVp_IN        | Applied voltage of PVp_IN pin: - 1.0 V                                | 9      | 12     | 15   |      |

|                                     |                | Applied voltage of PVp_IN pin: VvREG_50 + 1.0V                        | - 20   | - 16   | - 12 | - μΑ |

| Pin input current                   | IPVn_IN        | Applied voltage of PVn_IN pin: - 1.0 V                                | 9      | 12     | 15   |      |

|                                     |                | Applied voltage of PVn_IN pin:<br>VvREG_50+1.0V                       | - 20   | - 16   | - 12 |      |

| PV short to GND detection block     |                |                                                                       |        |        |      |      |

| Maximum voltage of difference input | ∆Vdif_PVc      | Between PVc_IN and PVn_IN                                             | 0      | -      | 4.0  | V    |

| Offset voltage of difference input  | ΔVPVc          | AD output conversion in short<br>between PVc_IN and PVn_IN            | - 100  | 0      | 100  | mV   |

|                                     |                | Applied voltage of PVc_IN pin: - 1.0 V                                | 9      | 12     | 15   |      |

| Pin input current                   | IPVc_IN        | Applied voltage of PVc_IN pin: VvREG_50 + 1.0V                        | - 20   | - 16   | - 12 | μA   |

| PV current detection block          |                |                                                                       |        |        |      |      |

| Maximum voltage of difference input | Vdif_SH        | Between GNDs                                                          | - 0.36 | -      | 0.24 | v    |

| Maximum voltage of unreferice input | ∆Vdif_SH       | Between SH_IN and SH_LG                                               | - 0.16 | -      | 0.04 | V    |

| Offset voltage of difference input  | ΔVSH           | AD output conversion in short between<br>SH_IN and SH_LG              | - 5.0  | 0      | 5.0  | m٧   |

| Pin input current                   | ISH_IN         | Applied voltage of SH_IN: - 0.36 V                                    | 9.2    | 11.5   | 14.9 |      |

|                                     |                | Applied voltage of SH_IN: 0.24 V                                      | 2.8    | 3.5    | 4.5  | μA   |

|                                     |                | Applied voltage of SH_LG: - 0.36 V                                    | 9.2    | 11.5   | 14.9 | μΑ   |

|                                     | 1311_LG        | Applied voltage of SH_LG: 0.24 V                                      | 2.8    | 3.5    | 4.5  |      |

| ADC block (Reference data: characte | eristics of AD | PC only)                                                              |        |        |      |      |

| Integration non-liner error         | INL            | VREG_50 = 5.0 V                                                       | - 5    | -      | 5    | LS   |

| Differensiation non-liner error     | DNL            | VREG_50 = 5.0 V                                                       | - 4    | -      | 4    | LSE  |

Toshiba Electronic Devices & Storage Corporation

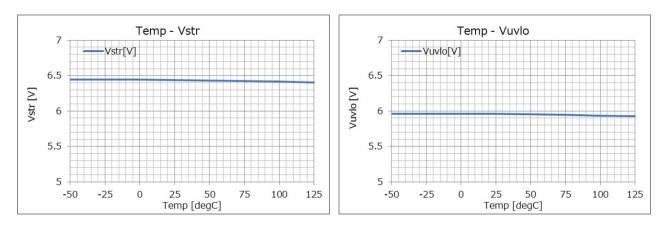

#### Temperature characteristics of startup and stop voltage

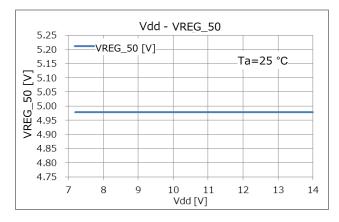

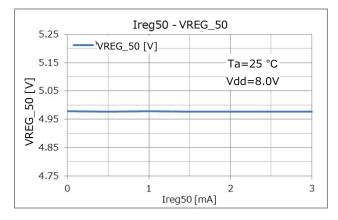

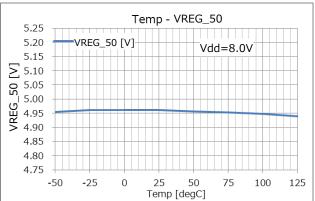

### Output voltage characteristics of VREG\_50 pin

## **ADC characteristics**

## Package dimensions

P-VQFN32-0505-0.50-002

#### **RESTRICTIONS ON PRODUCT USE**

Toshiba Corporation and its subsidiaries and affiliates are collectively referred to as "TOSHIBA". Hardware, software and systems described in this document are collectively referred to as "Product".

- TOSHIBA reserves the right to make changes to the information in this document and related Product without notice.

- This document and any information herein may not be reproduced without prior written permission from TOSHIBA. Even with TOSHIBA's written permission, reproduction is permissible only if reproduction is without alteration/omission.

- Though TOSHIBA works continually to improve Product's quality and reliability, Product can malfunction or fail. Customers are responsible for complying with safety standards and for providing adequate designs and safeguards for their hardware, software and systems which minimize risk and avoid situations in which a malfunction or failure of Product could cause loss of human life, bodily injury or damage to property, including data loss or corruption. Before customers use the Product, create designs including the Product, or incorporate the Product into their own applications, customers must also refer to and comply with (a) the latest versions of all relevant TOSHIBA information, including without limitation, this document, the specifications, the data sheets and application notes for Product and the precautions and conditions set forth in the "TOSHIBA Semiconductor Reliability Handbook" and (b) the instructions for the application with which the Product will be used with or for. Customers are solely responsible for all aspects of their own product design or applications, including but not limited to (a) determining the appropriateness of the use of this Product in such design or applications; (b) evaluating and determining the applicability of any information contained in this document, or in charts, diagrams, programs, algorithms, sample application circuits, or any other referenced documents; and (c) validating all operating parameters for such designs and applications. TOSHIBA ASSUMES NO LIABILITY FOR CUSTOMERS' PRODUCT DESIGN OR APPLICATIONS.

- PRODUCT IS NEITHER INTENDED NOR WARRANTED FOR USE IN EQUIPMENTS OR SYSTEMS THAT REQUIRE EXTRAORDINARILY HIGH LEVELS OF QUALITY AND/OR RELIABILITY, AND/OR A MALFUNCTION OR FAILURE OF WHICH MAY CAUSE LOSS OF HUMAN LIFE, BODILY INJURY, SERIOUS PROPERTY DAMAGE AND/OR SERIOUS PUBLIC IMPACT ("UNINTENDED USE"). Except for specific applications as expressly stated in this document, Unintended Use includes, without limitation, equipment used in nuclear facilities, equipment used in the aerospace industry, medical equipment, equipment used for automobiles, trains, ships and other transportation, traffic signaling equipment, equipment used to control combustions or explosions, safety devices, elevators and escalators, devices related to electric power, and equipment used in finance-related fields. IF YOU USE PRODUCT FOR UNINTENDED USE, TOSHIBA ASSUMES NO LIABILITY FOR PRODUCT. For details, please contact your TOSHIBA sales representative.

- Do not disassemble, analyze, reverse-engineer, alter, modify, translate or copy Product, whether in whole or in part.

- Product shall not be used for or incorporated into any products or systems whose manufacture, use, or sale is prohibited under any applicable laws or regulations.

- The information contained herein is presented only as guidance for Product use. No responsibility is assumed by TOSHIBA for any infringement of patents or any other intellectual property rights of third parties that may result from the use of Product. No license to any intellectual property right is granted by this document, whether express or implied, by estoppel or otherwise.

- ABSENT A WRITTEN SIGNED AGREEMENT, EXCEPT AS PROVIDED IN THE RELEVANT TERMS AND CONDITIONS OF SALE FOR PRODUCT, AND TO THE MAXIMUM EXTENT ALLOWABLE BY LAW, TOSHIBA (1) ASSUMES NO LIABILITY WHATSOEVER, INCLUDING WITHOUT LIMITATION, INDIRECT, CONSEQUENTIAL, SPECIAL, OR INCIDENTAL DAMAGES OR LOSS, INCLUDING WITHOUT LIMITATION, LOSS OF PROFITS, LOSS OF OPPORTUNITIES, BUSINESS INTERRUPTION AND LOSS OF DATA, AND (2) DISCLAIMS ANY AND ALL EXPRESS OR IMPLIED WARRANTIES AND CONDITIONS RELATED TO SALE, USE OF PRODUCT, OR INFORMATION, INCLUDING WARRANTIES OR CONDITIONS OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, ACCURACY OF INFORMATION, OR NONINFRINGEMENT.

- Do not use or otherwise make available Product or related software or technology for any military purposes, including without limitation, for the design, development, use, stockpiling or manufacturing of nuclear, chemical, or biological weapons or missile technology products (mass destruction weapons). Product and related software and technology may be controlled under the applicable export laws and regulations including, without limitation, the Japanese Foreign Exchange and Foreign Trade Law and the U.S. Export Administration Regulations. Export and re-export of Product or related software or technology are strictly prohibited except in compliance with all applicable export laws and regulations.

- Please contact your TOSHIBA sales representative for details as to environmental matters such as the RoHS compatibility of Product. Please use Product in compliance with all applicable laws and regulations that regulate the inclusion or use of controlled substances, including without limitation, the EU RoHS Directive. TOSHIBA ASSUMES NO LIABILITY FOR DAMAGES OR LOSSES OCCURRING AS A RESULT OF NONCOMPLIANCE WITH APPLICABLE LAWS AND REGULATIONS.

## **TOSHIBA ELECTRONIC DEVICES & STORAGE CORPORATION**