E201 P04 4745500 P457P0P

TOSHIBA (UC/UP)

64E D

#### 1. GENERAL

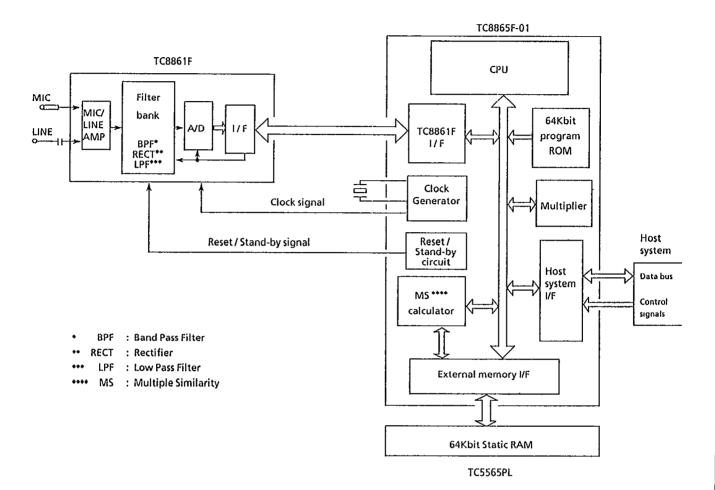

The speaker dependent isolated word recognition device set consists of TC8861F, TC8865F-01 and 64kbit static RAM. The device set contains the whole circuits and functions necessary to recognize voices, and is applied to mobile instruments easily. The device set operates with commands given by a host computer.

#### 2. FEATURES

|  | Reference pattern generation* with Differential Filter Method**. Three utterances per word required.                                                                                                 |

|--|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|  | Pattern matching with Multiple Similarity Method***.                                                                                                                                                 |

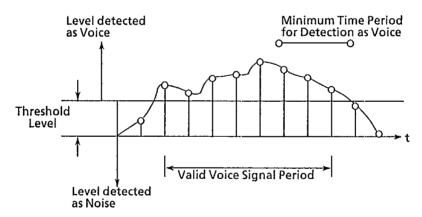

|  | Multiple word boundary candidates are detected, and the device set uses these candidates to avoid miss detection.                                                                                    |

|  | The recognition device set makes two reference patterns for each word. One is for lower noise environment and the other is for higher noise environment.                                             |

|  | Configuration: TC8861F, TC8865F-01 and 64kbit static RAM.                                                                                                                                            |

|  | Recognition rate: 93%  ( 20 place names, 5 males and 1 female voice, environmental noise level: 45dBA in registration mode, 70dBA in test mode.                                                      |

|  | Vocabulary numbers: Maximum 20.                                                                                                                                                                      |

|  | Response time: 0.3~1 seconds.  (Defined as the time length from the utterance end point to the time point of result return to the host computer.                                                     |

|  | Input voice time length allowed: 0.12~1.6 seconds.                                                                                                                                                   |

|  | Recommended distance between microphone and mouth is 5 through 15 centimeters and the distance more than 15 centimeters reduces system performance.                                                  |

|  | Signal to Noise ratio (S/N) at the microphone location needs over 15dB.                                                                                                                              |

|  | Reference pattern bank setting: Every reference pattern can be, if necessary, allocated to one of 8 banks so that the device set executes pattern matching with vocabularies in the designated bank. |

TOSHIBA (UC/UP)

64E D

| LJ | Rejection:       |                                                                                                                                                                                    |

|----|------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|    | On registration: | If three utterances for a word shows characteristic differences among them, the device set rejects these three utterances and then requires another three for the same word again. |

|    | On recognition:  | If a voice to be recognized presents low similarity to all the vocabularies registered, the device set rejects input voice and requests another input voice.                       |

|    | Directly connect | able to a voice input microphone.                                                                                                                                                  |

|    | Power saving mo  | ode available.                                                                                                                                                                     |

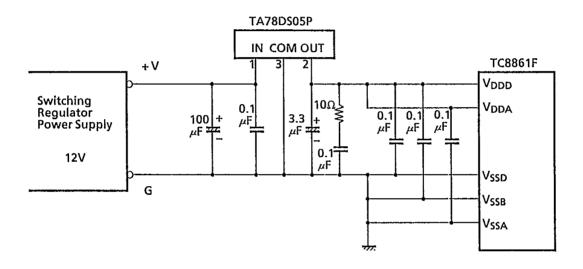

|    |                  | r supply (Caution: The separate second power supply is recommended to be $861\mathrm{F}\mathrm{in}$ order to improve the recognition rate.)                                        |

- \* Reference patterns must be readily generated on 64kbit static RAM through registration process requiring users to store vocabularies by their own voices. These patterns are examined to choose the most possible vocabulary candidate when voice to be recognized enters the device set.

- \*\* The method uniquely developed by Toshiba.

- \*\*\* The method jointly developed by the Agency of Industrial Science & Technology of MITI in Japanese Government, and Toshiba. The device set adopts the Patent "Multiple Similarity Method" (Japanese Patent No.739890) under license of the Japanese Industrial Technology Association. Details are to be referred to references (1), (2).

#### References

- (1) Y.Takebayashi, et al., "Telephone Speech Recognition Using a Hybrid Method", IEEE 7th International Conference on Pattern Recognition Proc., pp.1232-1235, 1984.

- (2) H.Sekiguchi, et al., "A Three-Chip LSI System for Speaker Independent Isolated Word Recognition by Multiple Similarity Method", IEEE ICCE Dig. of Tech. Papers pp.240-241, 1987.

64E D

- **BLOCK DIAGRAM AND SYSTEM CONFIGURATION** 3.

- 3.1 TC8861F/TC8865F-01 Block Diagram

### TOSHIBA (UC/UP)

64E D

#### 3.2 Description of Block Diagram

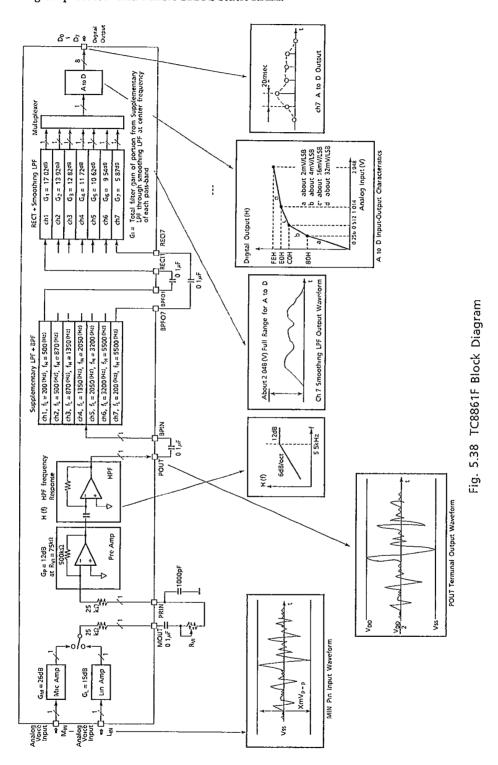

#### 3.2.1 TC8861F (Analog Processor)

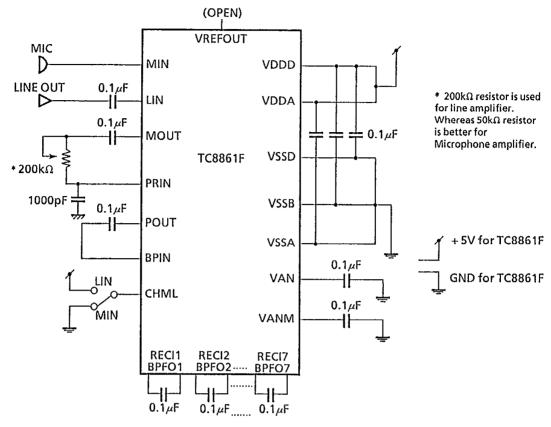

#### (1) MIC/LINE AMP

Two types of amplifiers respectively for a microphone input or for an audio line input. A microphone can connect with MIC AMP directly.

#### (2) Filter bank

Built-in 7 channel band-pass filters.

#### (3) A/D

Built-in analog-to-digital convertor

#### (4) I/F

Interface with TC8865F-01.

#### 3.2.2 TC8865F-01 (Digital Processor)

#### (1) CPU

Built-in central processing unit with system architecture compatible with TMPZ84C00A

#### (2) TC8861F I/F

Interface with TC8861F.

#### (3) 64kbit program ROM

This ROM contains the speaker dependent word recognition program codes.

#### (4) Multiplier

Multiplier speeds up registration process, used by CPU.

#### (5) MS calculator

This block calculates the similarity between the input voice data and reference patterns for each words.

#### (6) External memory I/F

Interface for a external RAM.

#### (7) Host system I/F

Interface for a host system.

#### (8) Reset/Stand-by circuit

This block makes system reset and stand-by signal.

#### (9) Clock Generator

Built-in oscillation circuit for ceramic resonator. This block makes 8MHz system clock.

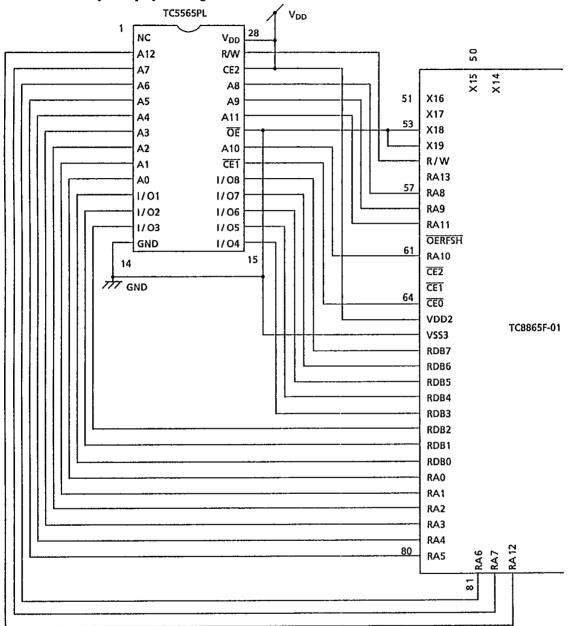

#### 3.2.3 64Kbit Static RAM

This memory stores scratchpad data and reference patterns.

3

64E D

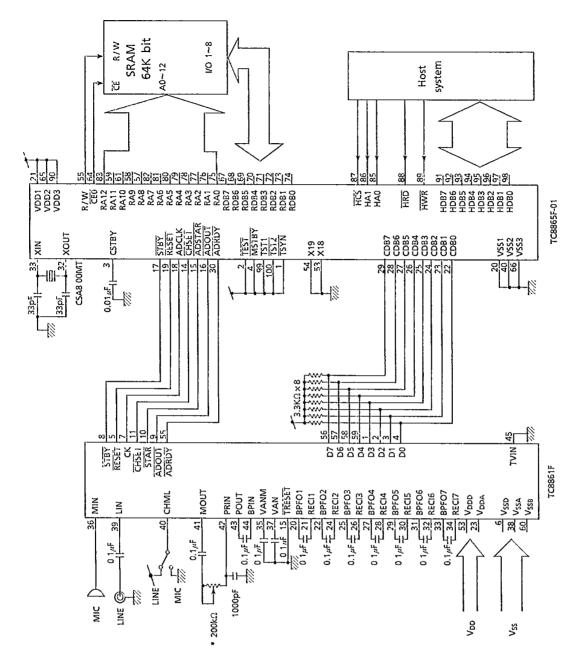

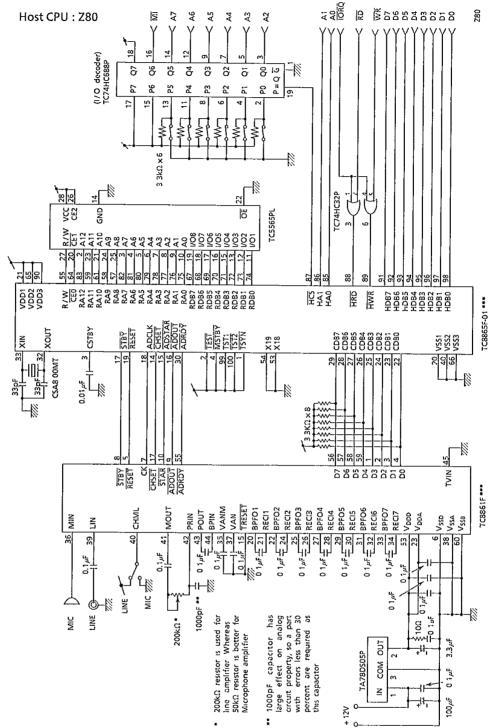

#### 3.3 System Configuration

The recognition device set is comprised of 3 chips. They are TC8861F analog processor, TC8865F-01 digital processor and 64kbit CMOS static RAM.

796

64E D

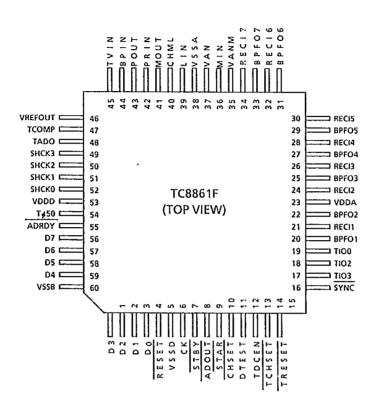

- 4. PIN ASSIGNMENTS

- 4.1 Pin Assignments

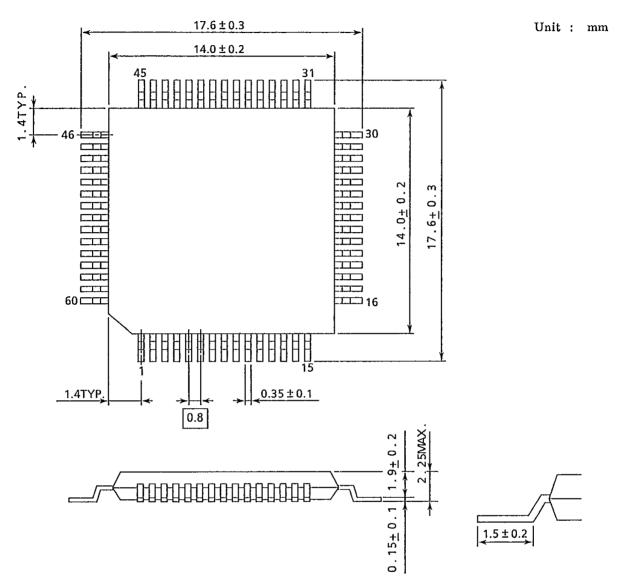

- 4.1.1 TC8861F

64E D

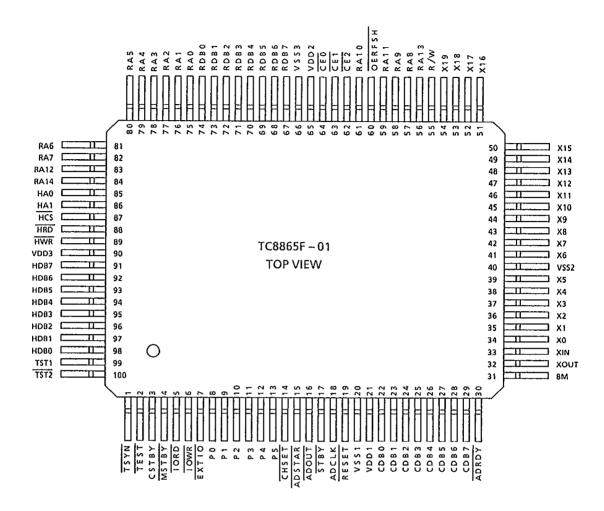

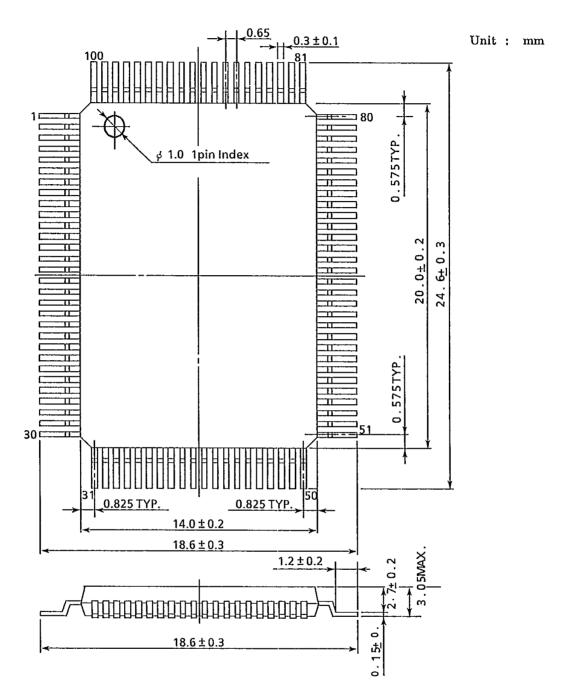

4.1.2 TC8865F-01

64E D

4.2 Pin Descriptions

4.2.1 TC8861F

| Pin Name | Pin No. | Input/Output | Function                                               | Status at stand-by |

|----------|---------|--------------|--------------------------------------------------------|--------------------|

| D0       | 4       | I/O, 3-State | System controller data bus                             | *H <sub>Z</sub>    |

| D1       | 3       | I/O, 3-State | System controller data bus                             | *H <sub>Z</sub>    |

| D2       | 2       | 1/O, 3-State | System controller data bus                             | *H <sub>Z</sub>    |

| D3       | 1       | I/O, 3-State | System controller data bus                             | *H <sub>Z</sub>    |

| D4       | 59      | I/O, 3-State | System controller data bus                             | *Hz                |

| D5       | 58      | I/O, 3-State | System controller data bus                             | *H <sub>Z</sub>    |

| D6       | 57      | I/O, 3-State | System controller data bus                             | *Hz                |

| D7       | 56      | I/O, 3-State | System controller data bus                             | *Hz                |

| CHSET    | 11      | Input        | Control signal from TC8865F-01                         | -                  |

| ADOUT    | 9       | Input        | Control signal from TC8865F-01                         | -                  |

| STAR     | 10      | Input        | Control signal from TC8865F-01                         | -                  |

| CK       | 7       | Input        | Clock input                                            | -                  |

| RESET    | 5       | Input        | Reset input                                            | -                  |

| STBY     | 8       | Input        | Stand-by input                                         | -                  |

| ADRDY    | 55      | Output       | TC8861F A/D operational status                         | Н                  |

| MIN      | 36      | Input        | Microphone input                                       | -                  |

| LIN      | 39      | Input        | Line input                                             | -                  |

| CHML     | 40      | Input        | Analog input change-over signal                        | -                  |

| MOUT     | 41      | Output       | Output of MIC Amplifier or LIN Amplifier               | *HZ                |

| PRIN     | 42      | Input        | Preamplifier input                                     | -                  |

| POUT     | 43      | Output       | Preamplifier output                                    | *H <sub>Z</sub>    |

| BPIN     | 44      | Input        | Band-pass filter input                                 | -                  |

| VAN      | 37      | Output       | Ground level of analog signal on analog circuit        | L                  |

|          |         |              | (except MIN amplifier, LIN amplifier and preamplifier) |                    |

|          |         |              | Ground level of analog signal on MIN amplifier, LIN    |                    |

| VANM     | 35      | Output       | amplifier and preamplifier                             | L                  |

|          |         |              | Reference voltage for A/D circuit                      |                    |

| VREFOUT  | 46      | Output       | Band-pass filter 1 output                              | L                  |

| BPF01    | 20      | Output       | Rectifier 1 input                                      | *HZ                |

| RECI1    | 21      | Input        | Band-pass filter 2 output                              | -                  |

| BPF02    | 22      | Output       | Rectifier 2 input                                      | *HZ                |

| REC12    | 24      | Input        | Band-pass filter 3 output                              | -                  |

| BPF03    | 25      | Output       | Rectifier 3 input                                      | *HZ                |

| REC13    | 26      | Input        | Band-pass filter 4 output                              | -                  |

| BPF04    | 27      | Output       | Rectifier 4 input                                      | *Hz                |

| RECI4    | 28      | Input        | Band-pass filter 5 output                              | -                  |

| BPF05    | 29      | Output       | Rectifier 5 input                                      | *Hz                |

| RECI5    | 30      | Input        | Band-pass filter 6 output                              | -                  |

| BPF06    | 31      | Output       | Rectifier 6 input                                      | *HZ                |

| RECI6    | 32      | Input        | Band-pass filter 7 input                               | -                  |

| BPF07    | 33      | Output       |                                                        | *H <sub>Z</sub>    |

<sup>\*</sup> HZ = High impedance

■ 9097249 0025482 585 ■ TOS3

TOSHIBA (UC/UP)

64E D

| Pin Name | Pin No. | Input/Output   | Function                                     | Status at stand-by |

|----------|---------|----------------|----------------------------------------------|--------------------|

| RECI7    | 34      | Input .        | Rectifier 7 input                            | -                  |

| TIO0     | 19      | Input/Output   | Test Pin                                     | *H <sub>Z</sub>    |

| TIO2     | 18      | Input/Output   | Test Pin                                     | *Hz                |

| TIO3     | 17      | Input/Output   | Test Pin                                     | *H <sub>Z</sub>    |

| TVIN     | 45      | Input          | Test Pin                                     | -                  |

| SYNC     | 16      | Input          | Test pin: with a built-in pull-up resistor   | ~                  |

| TRESET   | 15      | Input          | Test pin: with a built-in pull-down resistor | -                  |

| TCHSET   | 14      | Input          | Test pin: with a built-in pull-up resistor   | -                  |

| TDCEN    | 13      | Input          | Test pin: with a built-in pull-down resistor | -                  |

| DTEST/   | 12      | Input          | Test pin: with a built-in pull-down resistor | -                  |

| TDCSET   |         |                |                                              |                    |

| TADO     | 48      | Input          | Test pin: with a built-in pull-down resistor | -                  |

| ТФ50     | 54      | Output         | Test pin                                     | L                  |

| TCOMP    | 47      | Output         | Test pin                                     | L                  |

| SHCK0    | 52      | Output         | Test pin                                     | L.                 |

| SHCK1    | 51      | Output         | Test pin                                     | L                  |

| SHCK2    | 50      | Output         | Test pin                                     | L                  |

| SHCK3    | 49      | Output         | Test pin                                     | L                  |

| VDDD     | 53      | _              | Digital circuit power supply pin             | -                  |

| VDDA     | 23      | <del>-</del>   | Analog circuit power supply pin              | -                  |

| VSSD     | 6       |                | Digital circuit ground pin                   | -                  |

| VSSB     | 60      | <del>-</del> , | Data bus buffer ground pin                   | -                  |

| VSSA     | 38      | _              | Analog circuit ground pin                    | -                  |

<sup>\*</sup>HZ = High impedance

#### TOSHIBA (UC/UP)

### 64E D

#### (1) D0 ~ D7 (Data bus) [Input/Output]

8-bit bidirectional data bus. To be connected to the inner bus of the recognition system. These pins are used by TC8865F-01 to write data into TC8861F and read data from TC8861F.

#### (2) CHSET (CHannel SET strobe) [Input]

When L to H rising signal is input to this pin, D0-D7 data (To select multiplexer input filter channel) is written in the internal register of TC8861F. This pin is connected to the CIISET pin of TC8865F-01.

#### (3) ADOUT (A/D read OUT strobe) [Input]

When L level signal is input to this pin, D0-D7 become the output mode and data (<u>A/D</u> output data) of the output register on TC8861F is output on D0-D7. This pin is to be connected to the <del>ADOUT</del> pin of TC8865F-01.

#### (4) STAR (a to d STAR t signal) [Input]

A/D conversion start signal for A/D converter to be connected to the ADSTAR pin of TC8865F-01.

#### (5) CK (ClocK) [Input]

Clock input pin. By being connected to the ADCLK pin of TC8865F-01, system clock (Typ. 2MHz) is supplied from TC8865F-01.

#### (6) RESET (system RESET) [Input]

Reset input pin. To be connected to the  $\overline{RESET}$  pin of TC8865F 01. When L level signal is input to this pin, TC8861F is reset.

#### (7) STBY (STand-BY) [Input]

Stand-by input pin. To be connected to the  $\overline{STBY}$  pin of TC8865F-01. When L level signal is input to this pin, TC8861F is put in the stand-by state. At this time, however, the  $\overline{RESET}$  pin must have been set at L level in advance.

#### (8) ADRDY (A/D ReaDY) [Output]

This pin is H level when the A/D converter is in the conversion operation and is L level after end of the conversion. This pin is to be connected to the ADRDY pin of TC8865F-01.

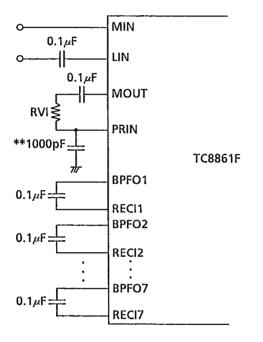

#### (9) MIN (Microphone INput) [Input]

Microphone signal input pin. A microphone can be directly connected. When the CHML pin is at L level, this pin is valid. The microphone signal ground level must be equal to Vss (ground) level of the LSI.

#### (10) LIN (Line INput) [Input]

Line input pin. Voice signal is input to this pin through the coupling capacitor. When the CHML pin is at H level, this pin is valid.

(11) CHML (CHange input pin between Min and Lin) [Input]

Control signal to select whether a signal to be processed by TC8861F is input signal from the MIN pin or that from the LIN pin.

(12) MOUT (Min/lin amplifier OUTput) [Output]

Output pin of the MIN or LIN input amplifier selected by the CHML pin. To be connected to the PRIN pin through a capacitor and a variable resistor.

(13) PRIN (PReamplifier INput) [Input]

Preamplifier input pin. Output signal from the MOUT pin is input to this pin. A capacitor 1000pF (deviation within ±30%) is to be placed between this pin and Vss (ground) level in order to stabilize analog characteristics. Without the capacitor, TC8861F does not operate properly.

(14) POUT (Preamplifier OUTput) [Output]

Preamplifier output pin. To be connected to the BPIN pin through a capacitor.

(15) BPIN (Band-Pass-filter INput) [Input]

Band-pass filter input pin. Output signal from the POUT pin is input to this pin.

(16) VAN (Voltage level of ANalog ground) [Output]

Ground level of analog signal on analog circuit except the MIN amplifier. To be connected to the system ground (Vss) through a capacitor.

(17) VANM (Voltage level of ANalog ground for Mic amplifier) [Output]

Ground level of analog signal on the MIN amplifier. To be connected to the system ground (Vss) through a capacitor.

(18) VREFOUT (Voltage level of REFerence OUTput for A/D) [Output]

Reference voltage monitor pin for A/D converter.

(19) BPF01~BPF07 (Band-Pass-Filter Output) [Output]

Output pins for 7 band-pass filters. These pins are respectively to be connected to the rectifier input pins (RECI1-7) correspondent to each channel.

(20) RECI1~RECI7 (RECtifier Input) [Input]

Input pins of 7 rectifiers.

(21) TIO0, TIO2, TIO3 (Test Input/Output) [Input/Output]

Test input/output pins. Nothing should be connected to these pins.

(22) TVIN, TRESET [Input]

Test input pins. TRESET pin contains pull down resistor.

Set them at L level. (Connect to the system ground Vss.)

#### TOSHIBA (UC/UP)

#### 64E D

(23) SYNC, TCHSET, TDCEN, DTEST/TDCSET, TAD0 [Input]

Test input pin with pull-up or pull-down resistor. Nothing should be connected to these pins.

(24) T $\Phi$ 50, TCOMP [Output]

Test output pin. Nothing should be connected.

(25) SHCK0~SHCK3 (Sample & Hold Clock) [Output]

Test output pin. Nothing should be connected.

(26) VDDD, VDDA

VDDD is the TC8861F digital circuit power supply pin. VDDA is the TC8861F analog circuit power supply pin. Both should be connected to the plus side of the power supply.

(27) VSSD, VSSB, VSSA

Ground pins. VSSD is the ground for TC8861F digital circuit, VSSB is the ground for TC8861F data bus buffer and VSSA is the ground for TC8861F analog circuit.

64E D

4.2.2 TC8865F01

| Pin Name   | Pin No. | Input/Output | Function                              | Status at stand-by |

|------------|---------|--------------|---------------------------------------|--------------------|

| CDB0       | 22      | I/O, 3-State | Internal data bus                     | *Hz                |

| 1          | 23      | I/O, 3-State | Internal data bus                     | *Hz                |

| 2          | 24      | I/O, 3-State | Internal data bus                     | *Hz                |

| 3          | 25      | I/O, 3-State | Internal data bus                     | *Hz                |

| 4          | 26      | I/O, 3-State | Internal data bus                     | *Hz                |

| 5          | 27      | I/O, 3-State | Internal data bus                     | *Hz                |

| 6          | 28      | I/O, 3-State | Internal data bus                     | *Hz                |

| 7          | 29      | I/O, 3-State | Internal data bus                     | *Hz                |

| ADCLK      | 18      | Output       | Clock output for TC8861F              | Н                  |

| CHSET      | 14      | Output       | TC8861F control signal                | Н                  |

| ADSTAR     | 15      | Output       | TC8861F control signal                | Н                  |

| ADOUT      | 16      | Output       | TC8861F control signal                | H                  |

| ADRDY      | 30      | Input        | TC8861F status signal                 | -                  |

| RESET      | 19      | Output       | System reset output                   | L                  |

| STBY       | 17      | Output       | System stand-by output                | L                  |

| HDB0       | 98      | I/O, 3-State | Host system data bus                  | *Hz                |

| 1          | 97      | I/O, 3-State | Host system data bus                  | *Hz                |

| 2          | 96      | I/O, 3-State | Host system data bus                  | *Hz                |

| 3          | 95      | I/O, 3-State | Host system data bus                  | *Hz                |

| 4          | 94      | I/O, 3-State | Host system data bus                  | *Hz                |

| 5          | 93      | I/O, 3-State | Host system data bus                  | *Hz                |

| 6          | 92      | I/O, 3-State | Host system data bus                  | *Hz                |

| 7          | 91      | I/O, 3-State | Host system data bus                  | *Hz                |

| HA0        | 85      | Input        | Address signal input from Host system | _                  |

| 1          | 86      | Input        | Address signal input from Host system | -                  |

| HCS        | 87      | Input        | Control signal input from Host system | -                  |

| HRD        | 88      | Input        | Control signal input from Host system | -                  |

| HWR        | 89      | Input        | Control signal input from Host system | _                  |

| RDB0       | 74      | I/O, 3-State | External memory data bus              | HorL               |

| 1          | 73      | I/O, 3-State | External memory data bus              | H or L             |

| 2          | 72      | I/O, 3-State | External memory data bus              | HorL               |

| 3          | 71      | I/O, 3-State | External memory data bus              | HorL               |

| 4          | 70      | I/O, 3-State | External memory data bus              | HorL               |

| 5          | 69      | I/O, 3-State | External memory data bus              | H or L             |

| 6          | 68      | I/O, 3-State | External memory data bus              | H or L             |

| 7          | 67      | I/O, 3-State | External memory data bus              | HorL               |

| <u>ČEO</u> | 64      | Output       | External memory chip selection signal | Н                  |

| CE1        | 63      | Output       | External memory chip selection signal | н                  |

| CE2        | 62      | Output       | External memory chip selection signal | Н                  |

| OERFSH     | 60      | Output       | Control signal for external memory    | L                  |

| R/W        | 55      | Output       | Control signal for external memory    | Н                  |

<sup>\*</sup> Hz = High Impedance

ьче Д

| Pin Name    | Pin No. | Input/Output | Function                            | Status st stand-by |

|-------------|---------|--------------|-------------------------------------|--------------------|

| RA0         | 75      | Output       | External memory address bus         | Н                  |

| 1           | 76      | Output       | External memory address bus         | Н                  |

| 2           | 77      | Output       | External memory address bus         | Н                  |

| 3           | 78      | Output       | External memory address bus         | Н                  |

| 4           | 79      | Output       | External memory address bus         | Н                  |

| 5           | 80      | Output       | External memory address bus         | н                  |

| 6           | 81      | Output       | External memory address bus         | Н                  |

| 7           | 82      | Output       | External memory address bus         | Н                  |

| 8           | 57      | Output       | External memory address bus         | Н                  |

| 9           | 58      | Output       | External memory address bus         | Н                  |

| 10          | 61      | Output       | External memory address bus         | Н                  |

| 11          | 59      | Output       | External memory address bus         | Н                  |

| 12          | 83      | Output       | External memory address bus         | Н                  |

| 13          | 56      | Output       | External memory address bus         | н                  |

| 14          | 84      | Output       | External memory address bus         | Н                  |

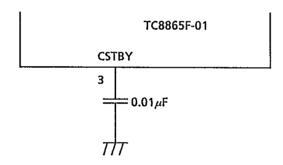

| CSTBY       | 3       | Input        | For producing rising startup timing | _                  |

| MSTBY       | 4       | Input        | Manual stand-by input               | _                  |

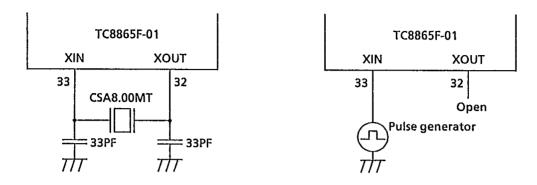

| XIN         | 33      | Input        | Ceramic resonator connecting pin    | _                  |

| XOUT        | 32      | Input        | Ceramic resonator connecting pin    | _                  |

| IORD        | 5       | Output       | External I/O control signal         | Н                  |

| <b>IOWR</b> | 6       | Output       | External I/O control signal         | H                  |

| EXTIO       | 7       | Output       | External I/O control signal         | Н                  |

| P0          | 8       | I/O, 3-State | External I/O port                   | *Hz                |

| P1          | 9       | I/O, 3-State | External I/O port                   | *Hz                |

| P2          | 10      | I/O, 3-State | External I/O port                   | *Hz                |

| Р3          | 11      | I/O, 3-State | External I/O port                   | *Hz                |

| P4          | 12      | I/O, 3-State | External I/O port                   | *Hz                |

| P5          | 13      | I/O, 3-State | External I/O port                   | *Hz                |

| 8M          | 31      | Output       | Clock output                        | Н                  |

| X0          | 34      | Output       | Test pin                            | Н                  |

| 1           | 35      | Output       | Test pin                            | Н                  |

| 2           | 36      | Output       | Test pin                            | Н                  |

| 3           | 37      | Output       | Test pin                            | H                  |

| 4           | 38      | Output       | Test pin                            | Н                  |

| 5           | 39      | Output       | Test pin                            | Н                  |

| 6           | 41      | Output       | Test pin                            | н                  |

| 7           | 42      | Output       | Test pin                            | Н н                |

| 8           | 43      | Output       | Test pin                            | н                  |

| 9           | 44      | Output       | Test pin                            | H                  |

| 10          | 45      | Output       | Test pin                            | Н Н                |

<sup>\*</sup> Hz = High Impedance

# TC8861F/65F-01-15 TOSHTBA (UC/UD)

(QU\)U) ABIHZOT

64E D

| Pin Name | Pin No. | Input/Output | Function         | Status at stand-by |

|----------|---------|--------------|------------------|--------------------|

| X11      | 46      | Output       | Test pin         | Н                  |

| X12      | 47      | Output       | Test pin         | Н                  |

| X13      | 48      | Output       | Test pin         | н                  |

| X14      | 49      | Output       | Test pin         | н                  |

| X15      | 50      | Output       | Test pin         | Н                  |

| X16      | 51      | Output       | Test pin         | н                  |

| X17      | 52      | Output       | Test pin         | Н                  |

| X18      | 53      | Input        | Test pin         | -                  |

| X19      | 54      | Input        | Test pin         | -                  |

| TEST     | 2       | Input        | Test pin         | -                  |

| TST1     | 99      | Input        | Test pin         | _                  |

| TST2     | 100     | Input        | Test pin         | -                  |

| TSYN     | 1       | Input        | Test pin         | -                  |

| VDD1     | 21      | 1            | Power supply pin | _                  |

| VDD2     | 65      | -            | Power supply pin | -                  |

| VDD3     | 90      | _            | Power supply pin | _                  |

| VSS1     | 20      | _            | Ground pin       | _                  |

| VSS2     | 40      |              | Ground pin       | _                  |

| VSS3     | 66      | -            | Ground pin       |                    |

64E D

#### TC8861F I/F Signals

- (1) CDB0~CDB7 (Cpu Data Bus) [Input/Output]

8bit bidirectional data bus connected to the internal bus in the recognition system for address and data input/output. These pins are to be connected to DB0~7 of TC8861F.

- (2) ADCLK (A DCLocK) [Output]

TC8861F clock output pin. 2MHz, duty 50% signal is output. This pin is to be connected to the CK pin of TC8861F.

- (3) CHSET(CHannel SET strobe) [Output]

TC8861F channel set signal output pin. This pin is to be connected to the CHSET pin of TC8861F.

- (4) ADOUT(A D read OUT strobe) [Output]

TC8861F A/D output data read out signal outputpin. This pin is to be connected to the ADOUT pin of TC8861F.

- (5) ADSTAR(A D STARt signal) [Output]

TC8861F A/D conversion start signal output pin. To be connected to the STAR pin of TC8861F.

- (6) ADRDY(A D ReaDY) [Input]

TC8861F A/D conversion end signal input pin. To be connected to the ADRDY pin of TC8861F.

#### Host System I/F Signals

- (7) HDB0~HDB7 (<u>H</u>ost <u>D</u>ata <u>B</u>us) [Input/Output]

8bit bidirectional data bus. These pins are to be connected to the data bus of a host system and used for transferring all kinds of data such as commands, status and recognition result.

- (8) HA0, HA1 (Host Port Address 0, 1) [Input]

These pins are to be connected to the address output of a host system and used to specify the kind of data transferred through HDB0~7.

- (9) HCS (Host Chip Select) [Input]

A low on this pin enables the TC8865F-01 host system I/F to be active and the HRD and HWR pins described below become valid.

- (10) HRD (Host ReaD strobe) [Input]

When L level signal is input to this pin at HCS=L, the HDB0~7 pins are set to the output mode, and recognition result, status, etc. are output according to the signals of the HA0 and HA1 pins. The HRD and HWR pins must not be put at L level at the same time.

64E D

#### (11) HWR (Host WRite strobe) [Input]

At the rising edge of this pin at  $\overline{HCS} = L$  as described above, HDB0~7 data are latched in TC8865F-01. The  $\overline{HRD}$  and  $\overline{HWR}$  pins should not be put at L level simultaneously.

#### Signals to Reset & Standby Circuits, Clock Oscillator, Test Circuits

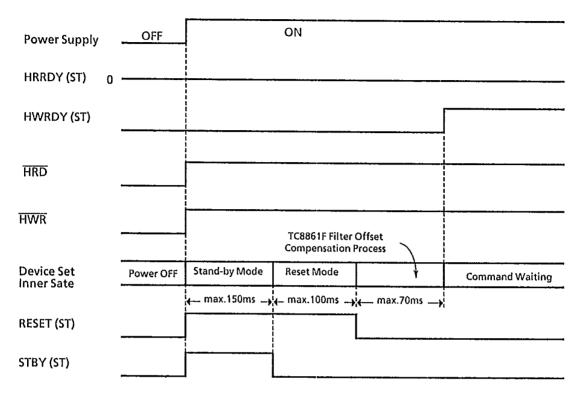

#### (12) CSTBY (Capacitor for STand-BY) [Input]

This pin is connected with a capacitor to the ground to produce the system start sequence control timing when the power supply becomes ON.

### (13) MSTBY (Manual STand - BY) [Input]

Manual standby pin. This pin should be set at High level in normal operation.

#### (14) RESET [Output]

System reset signal output pin. This pin is to be connected to RESET pin of TC8861F.

#### (15) STBY (STand-BY) [Output]

System standby signal output pin. To be connected to STBY pin of TC8861F.

#### (16) XIN, XOUT (Xtal-IN, OUT) [Input]

Ceramic resonator connecting pins. An 8MIIz ceramic resonator and capacitor are connected.

#### (17) TEST, TST1, TST2 [Input]

Test input pin. These pins should be set at High level in normal operation.

#### (18) TSYN [Input]

Test input pin. This pin should be set at High level in normal operation.

#### External memory I/F Signals

#### (19) RDB0~RDB7(Reference memory Data Bus) [Input/Output]

8bit bidirectional external memory data bus. These pins are to be connected to the external memory data bus.

#### (20) RA0~RA14 (Reference memory Address) [Output]

The 15bit external pattern memory address bus. These pins are to be connected to the external memory address bus.

#### (21) CEO (Chip Enable 0) [Output]

This pin is a chip select output available for CPU to accesses memory data addressed 4000H through 5FFFH. This pin should be connected to a chip select pin of 64K static RAM because program codes in TC8865F-01 are located within this address space.

#### (22) CEI (Chip Enable 1) [Output]

This pin is a chip select output available for CPU to access memory data addressed 6000H through 7FFFH. CE1 should not be connected to any signals.

#### TOSHIBA (UC/UP)

#### 64E D

- (23) CE2 (Chip Enable 2) [Output]

This pin is a chip select output available for CPU to access memory data addressed 8000II through FFFFH. CE2 should not be connected to any signals.

- (24) R/W (Read/Write) [Output]

This pin is to be connected to R/W pin of 64kbit static RAM.

- (25) OERFSH (Output Enable /ReFreSH enable) [Output]

OERFSH should not be connected to any signals.

#### Internal general purpose interface signals

Following pins are not supported by TC8865F-01 system.

- (26) IOWR (I/O WRite strobe) [Output]

This pin is enabled when CPU writes to a specified I/O port.

- (27)  $\overline{\text{IORD}}$  (I/O ReaD strobe) [Output]

This pin is enabled when CPU reads from a specified I/O port.

- (28) EXTIO (EXTernal I/O select) [Output]

This pin is a chip select output using with IOWR, IORD pins.

- (29) P0~5 (Port 0~5) [Input/Output]

P0 through P5 pins are 6bit general purpose I/O ports, but not available in TC8865F-01 system. These pins should not be connected any signals.

- (30) 8M (8MHz clock output) [Output] This pin outputs 8MHz clock.

- (31) X0~X17 [Output]

These pins are test output pins, and should not be connected any signals.

- (32) X18,X19 [Input]

These pins are test input pins and should be connected to VSS pin.

#### Power Supply Signals

- (33) VDD1, VDD2, VDD3

The power supply pins. All pins are to be connected to the plus side of the power supply.

- (34) VSS1, VSS2, VSS3

The ground pins. All pins are to be connected to the ground side of the power supply.

3

64E D

#### **OPERATION AND FUNCTION** 5.

#### 5.1 **Device Set Functional Organization**

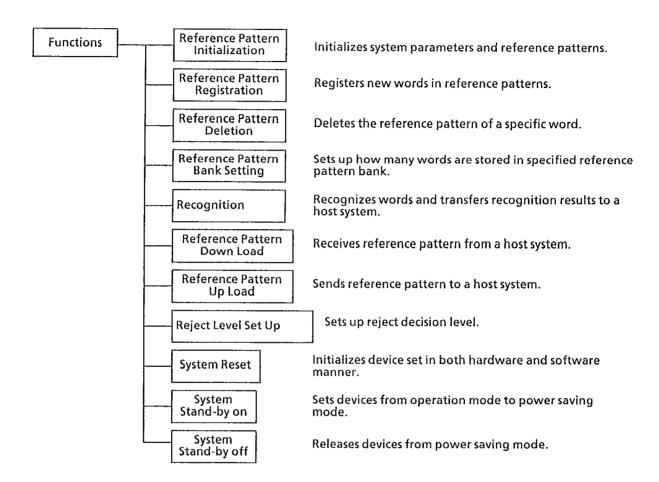

The device set provides 11 functions as described in Fig. 5.1. These functions are embedded in 3 LSI hardware and software program on the TC8865F-01 on-chip Mask ROM \*.

\* Toshiba holds the copyright for the programs embedded in the Mask ROM.

Fig. 5.1 Functional organization of device set

64E D

#### 5.1.1 Reference Pattern Registration

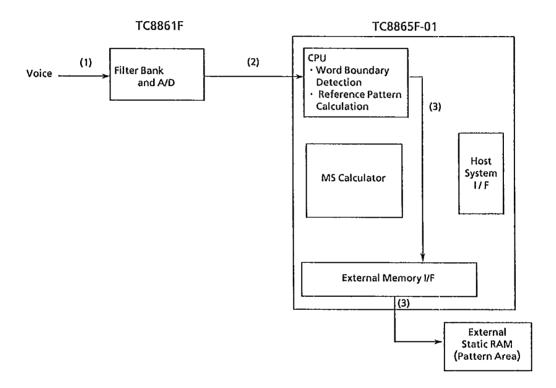

Reference patterns for vocabularies to be recognized must be stored in external static RAM before recognition. To store reference patterns is called registration. A reference pattern for a word is made by analyzing three utterances. The sequence of reference pattern production is itemized below and is illustrated in Fig. 5.2.

- (1) TC8861F receives three utterances per word to analyze them and to digitize the analyzed analog signals with A/D.

- (2) CPU detects word boundaries with A/D output signals. Then it prepares a reference pattern.

- (3) The prepared reference pattern is, through external memory I/F, transferred to and is stored in external static RAM.

Fig. 5.2 Data flow in reference pattern registration

64E D

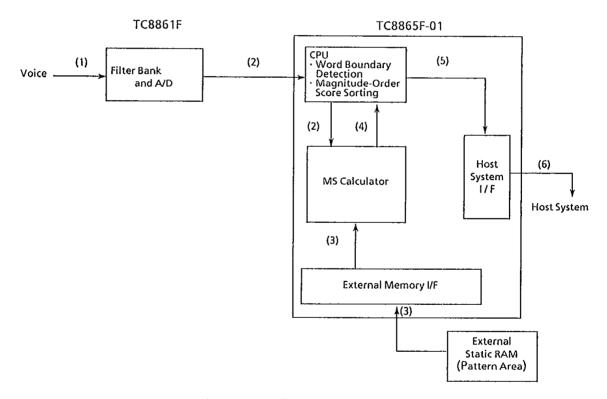

#### 5.1.2 Recognition

The device set recognizes voices in a way that it compares input voice features with vocabulary reference patterns beforehand stored in an external static RAM. The recognition results indicating most possible word candidates for input words are transferred to a host computer. The functional process is itemized below and is charted in Fig. 5.3.

- (1) TC8861F receives a voice to be recognized, analyzes acoustically, and digitizes the analyzed analog signals with A to D.

- (2) CPU detects word boundary of A/D output signals. Then the detected signals are transmitted to a data RAM in the MS calculator.

- (3) The similarity of the detected signals to all reference patterns stored in external static RAM is examined.

- (4) All similarity scores with the whole vocabularies are transferred to CPU.

- (5) CPU arranges the scores in reverse-numerical order. And the top three scores and their word numbers are sent to the host system I/F on TC8865F-01.

- (6) The top three scores and their word numbers are transferred to a host system.

Fig. 5.3 Data flow in recognition

64E D

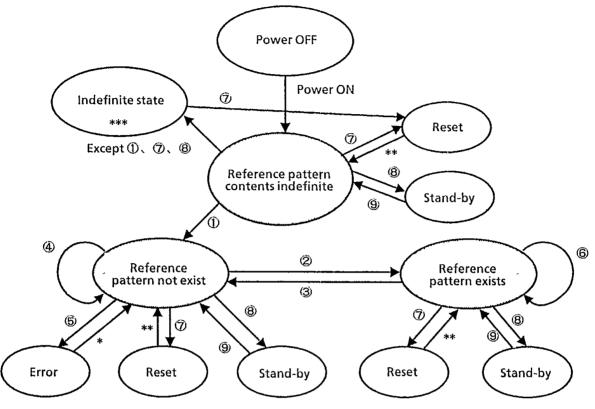

#### 5.1.3 System Inner State Transfer Chart

The device set state transfer chart is described below. This chart is drawed on the view of reference pattern exists or not.

Fig. 5.4 System inner state transfer chart

- ① Reference Pattern Initialization

- ② Reference Pattern Registration, Reference Pattern Down Load

- ③ Reference Pattern Initialization, Reference Pattern Deletion (All word)

- ④ Reference Pattern Initialization, Reference Pattern Bank Setting, Reject Level Set Up

- (5) Recognition, Reference Pattern Up Load

- Reference Pattern Registration, Reference Pattern Deletion(A part), Reference Pattern Bank Setting, Recognition, Reference Pattern Down Load, Reference Pattern Up Load, Reject Level Set Up

- System Reset

- System Stand-by on

- System Stand-by off

- \* Host system can know that the recognition device set is in error state from reading the return code. After reading return code, the device set status returns command waiting mode.

- \*\* Reset state is released automatically.

- \*\*\*The recognition device set status is indefinite because the system work area contents are not defined.

#### TOSHIBA (UC/UP)

64E D

#### 5.1.4 Definition of Recognition Rate

Recognition rate varies with a vocabulary, a voice quality and a recognition rate calculation method. Though many calculation method for unbiased recognition rate have been proposed, there is no standard formula for recognition rate. In this manual, recognition rate is calculated by following definition.

#### Expression:

Recognition rate

$$=\frac{N-E-R}{N}$$

Where: N means all test voice count. N = 2 (times per words)  $\times$  m (words).

E means incorrect result count.

R means reject count.

#### Evaluation method:

- (1) The voice is recorded to an audio tape 5 times for each word.

- (2) The tape is played back, and 3 utterances of each word are sent to the device set and are analyzed for the reference pattern. Here the audio signal line is fed into LIN pin of TC8861F.

- (3) Remaining 2 utterances per word in the audio tape are used for the test data to calculate recognition rate.

#### Condition:

Reject flag, Too Long flag, Too Low flag and Too High flag are all available and they are counted as R in the above expression. Too Long flag, Too Low flag and Too High flag are mentioned at 5.3.4 (2).

#### 5.1.5 Reject

In the recognition command, the device set calculates the similarity between the input voice and the word in the reference pattern memory. If the device set outputs the most similar word as recognition result unconditionally, there are some problems when the user speaks unregistered word. Therefore, when similarity is lower than the decided level, the device set returns reject status to show that the similarity between input voice and whole reference patterns are low. The device set can not decide from comparison of the similarity and a constant value because the similarity varies with not only input voice but also reference pattern contents. So the device set decides reject state from comparison the value, multiplied calculated value from input voice by the constant value, and the similarity of each word. Host system can change this constant value by using reject level set up command. Reject level set up command is described in 5.3.3 (8).

64E D

#### 5.1.6 To Get Optimal Performance

To achieve optimal performance of the device set, it is recommended to follow several notes and advise mentioned below.

#### Notes about a vocabulary:

- (1) This system can deal with an isolated word recognition, but it can hardly recognize connected words and sentences which are spoken continuously.

- (2) A vocabulary must be made of 2 through 5 syllables words. A word with one syllable or over six syllables decreases system performance. Especially the alphabet is similar to each other, leading to low performance.

#### Notes about an utterance:

- (1) On registration, at least three utterances are needed and each utterance must be same as much as possible. Different utterances will be rejected.

- (2) On recognition, an utterance should be same as registered voice as possible.

- (3) The dynamic range of input voice signal is 10 through 15 dB for maintaining high performance.

- (4) Two factors to decide the level of input voice signal exist, one is the speaker's voice volume and the other is the distance from the speaker's mouth to a microphone. The recommended distance between the mouth and the microphone is roughly 5 through 15 centimeters according to voice level.

- (5) A microphone must observe following conditions:

Frequency characteristics: Flat gain from 200Hz to 7KHz.

Gain deviation is within ±2.5dB.

Directivity: Single directional.

#### Limitations about an environment noise:

The recognition device set made on the assumption that it is used in a mobile. But the device set may not recognize in all mobile condition because noise level in a mobile varies drastically. The device set is made on the assumption that it is used in regular about 70dBA noise condition. We decide a this 70dBA noise level from environment noise in the mobile which runs with close window and with 100km/h speed on the free way. Usually user registers the reference pattern when the mobile stops and the engine is in idling state. At this time we assume that noise level is about 50dBA. Then the device set is used by executing recognition command even when the mobile runs. At this time we assume that stereo doesn't operate so louder, people except user doesn't speak so louder and the mobile windows are closed in order to shut out external noise. The performance of the device set will decrease under the condition that many pop noise comes from load joint.

64E D

#### Limitation of candidates:

In the case that only a part of the words in reference patterns are previously known as targets, reference pattern bank setting command and specified-bank recognition command are recommended. The unnecessary words for recognition are removed and better performance is achieved.

#### 5.1.7 Improvements on TC8861F/TC8864F-00

Followings are TC8861F/TC8865F-01 improvements on TC8861F/TC8864F-00.

- 1. TC8861F/TC8865F-01 detects multiple candidates for word duration and uses most possible candidate to register and recognize. This algorithm leads fewer errors in word boundary detection.

- 2. When the device set is used in a mobile. There are many cases that recognition is executed when the mobile stops and recognition is executed when the mobile runs. Therefore the device set makes two different reference patterns for each word. One is for fewer noise environment and the other is for larger noise environment.

- 3. At registration and recognition, the environment noise measured at word boundary detection is subtracted from input voice to reduce effects of environment noise.

- 4. The host system can register all word to each bank. Therefore the word can register to plural banks. For example when bank 0 contains word 1 though word 5, bank 1 can contain word 1 and word 10 TC8861F/TC8864F-00 can not register a word to plural banks.

By above measures the performance of TC8861F/TC8865F-01 increases in regular noise condition. But the device set uses TC8861F and is applied more complicated algorithm, following restrictions still exist.

- 1. The device set uses two conventional word area for one reference pattern, so maximum recognizable word becomes 20.

- 2. The device set contains TC8861F for feature extraction, the distance between a microphone and user's mouth needs within 5 though 15 centimeters. If the distance becomes over 15 centimeters, the recognition performance will decrease.

- 3. The recognition performance will also decrease on the noisy condition such as existing other human's voices or audio sounds. Signal to Noise ratio (S/N) needs about 15dB or larger.

64E D

#### 5.2 Host System Interface

#### 5.2.1 Introduction to Interface Hardware

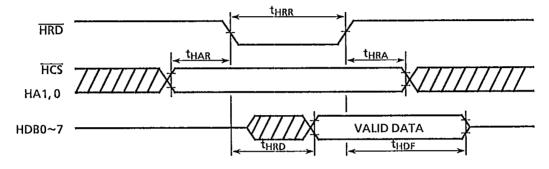

A host system operates the recognition device set with both commands and data transferred through the host system interface circuit on TC8865F-01. The circuit reads or writes 8bit parallel data bus like a general purpose 8bit parallel interface TMP82C55AP-5. TC8865F-01 pins for the operations are HDB0 $\sim$ 7,  $\overline{\text{HCS}}$ ,  $\overline{\text{HRD}}$ ,  $\overline{\text{HWR}}$ , HA0 $\sim$ 1. Functional description for the pins are given in Table 5.1.

Table 5.1 Host interface pins and their functions

| Pin Names | Number of<br>Pins | Input/<br>Output            | Description                                                                                                                                                      |

|-----------|-------------------|-----------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| HDB0∼7    | 8                 | 3 state<br>Input/<br>Output | 8 bit 3-state bidirectional data bus. Used for transferring commands, data and status between host system and device set. HDB7 = MSB *, HDB0 = LSB **            |

| HCS       | 1                 | Input                       | Chip select input. At "L" level, data transfer with host system is enabled. At "H" level, all signals given by host system are ignored.                          |

| HRD       | 1                 | Input                       | Read strobe signal.  At "L" level, HDB0 $\sim$ 7 is put in the output mode so that host system may read data on HDB0 $\sim$ 7. (at $\overline{HCS}$ = HA1 = "L") |

| HWR       | 1                 | Input                       | Write strobe signal. At rising edge, command or data are written from HDB0~7 into a specific register. (at HCS = HA0 = "L")                                      |

| HA1, HA0  | 2                 | Input                       | Addresses selecting command/data register, status register or reset/stand-by register. Generally connect to lower 2bits of address bus of host system.           |

\* MSB: Most Significant Bit

\*\* LSB: Least Significant Bit

64E D

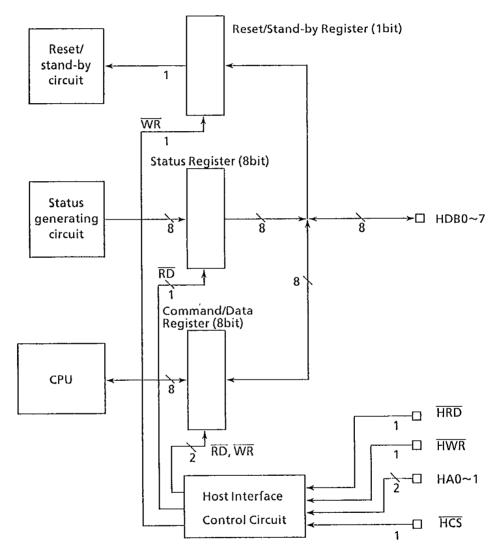

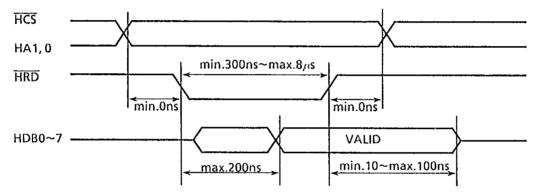

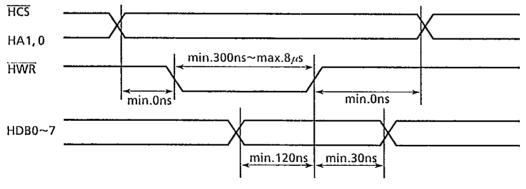

#### 5.2.2 Interface Hardware Configuration and Its Timing

TC8865F-01 host interface circuit hardware block diagram is illustrated in Fig.5.5. The circuit contains three registers, command/data register (8bit), status register (8bit) and reset/stand-by register (1bit). Host systems reading/writing operations with these registers run the device set. The registers are distinguished among themselves by two address pins (HAO, HA1). The command/data register can be read/written and the status register is dedicated to reading only. The reset/stand-by register is dedicated to writing only.

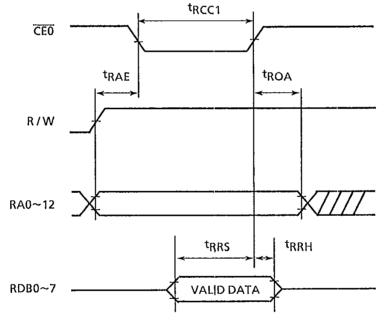

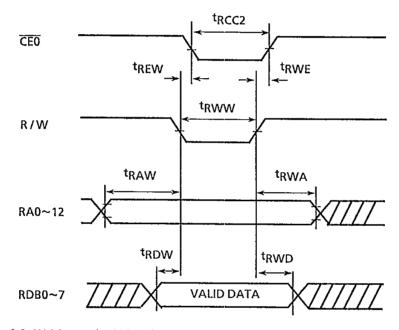

Table 5.2 shows the pin setting to realize the above mentioned functions. Switching timings in reading or writing operations are illustrated in Fig.5.6 and Fig.5.7.

Fig. 5.5 Host interface circuit block diagram

64E D

Table 5.2 Pin setting for functions

| HA1 | HA0 | HCS | HRD | HWR | Functions                       |  |  |  |

|-----|-----|-----|-----|-----|---------------------------------|--|--|--|

| 0   | 0   | 0   | 0   | 1   | Data Reading.                   |  |  |  |

| 0   | 0   | 0   | 1   | 0   | Command/Data Writing.           |  |  |  |

| 0   | 1   | 0   | 0   | 1   | Status Reading.                 |  |  |  |

| 1   | 0   | 0   | 1   | 0   | Reset/Stand-by Command Writing. |  |  |  |

| ×   | ×   | 0   | 1   | 1   | Device Set remains unchanged.   |  |  |  |

| ×   | ×   | 1   | ×   | ×   | Device Set remains unchanged.   |  |  |  |

| 0   | 1   | 0   | 1   | 0   | Device Set remains unchanged.   |  |  |  |

| 1   | 0   | 0   | 0   | 1   | Device Set remains unchanged.   |  |  |  |

| 1   | 1   | 0   | 0   | 1   | Device Set remains unchanged.   |  |  |  |

| 1   | 1   | 0   | 1   | 0   | Device Set remains unchanged.   |  |  |  |

| ×   | ×   | 0   | 0   | 0   | Not Allowed.                    |  |  |  |

0 = L level, 1 = H level, x = Don't care

Fig.5.6 Host interface reading cycle timing

Fig.5.7 Host interface writing cycle timing

64E D

#### 5.2.3 How to Use Command/Data Register

Command/data register with 8bit data is used for "command"/"data" writing operation and data reading operation. Here "command code" is defined as 8bit code given into this register by a host computer on waiting state for the next command. On the other hand, "data" are defined as 8bit data transferred through the register while the device set is executing commands. Examples of "data" are "word number" given by a host system and "control code" output to a host system in registration command execution.

Table 5.3 shows a command list to with the command/data register.

Table 5.3 Commands with command/data register

| Command                          | HDB0~7               | HA1 | НА0 | HCS  | HRD | HWR |

|----------------------------------|----------------------|-----|-----|------|-----|-----|

| Reference Pattern Initialization | 28H                  |     |     |      |     |     |

| Reference Pattern Registration   | 29H                  |     |     | <br> |     |     |

| Reference Pattern Deletion       | 2AH                  |     |     |      |     |     |

| Reference Pattern Bank Setting   | 2CH                  | 0   | 0   | 0    | 1   | 0   |

| Recognition 1,2 *                | 08H~0FH、<br>18H~1FH* |     |     |      |     |     |

| Reference Pattern Down Load      | 22H                  |     |     |      |     |     |

| Reference Pattern Up Load        | 23H                  |     |     |      |     |     |

| Reject Level Set Up              | зсн                  |     |     |      |     |     |

<sup>1 =</sup> H Level, 0 = L Level

\* Recognition command consists of Recognition 1 command and Recognition 2 command. In Recognition 1 command the device set uses average noise data that is measured before recognition command is entered as decision data for detecting word boundary. In Recognition 2 command the device set uses noise data that is measured just after recognition command is entered. Recognition 1 command code number is from 08H to 0FH and Recognition 2 command code number is from 18H to 1FH. If the host system has not executed bank setting command, command code 08H though 0FH has same effects as Recognition 1 command and command code 18H though 1FH has same effects as Recognition 2 command. On the other hand, if the host system has executed bank setting command, command code 08H and 18H only effects bank 0 and 19H effects bank 1 and 0AH and 1AH effects bank 2 and so on.

64E D

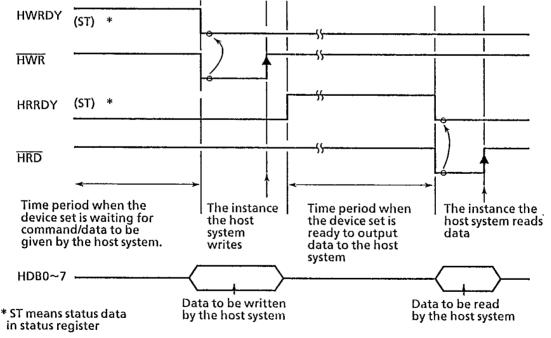

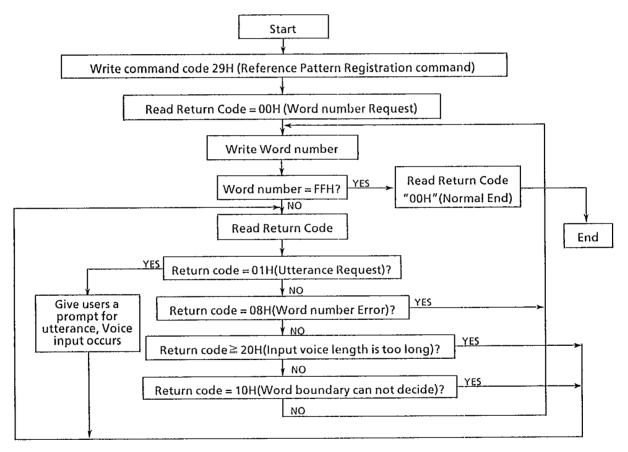

#### 5.2.4 Hand Shake with Command/Data Register

Communication between the host system and the device set with the command/data register employs "hand shake" protocol. This protocol uses two status signals HRRDY ( $\underline{\underline{H}}$ ost  $\underline{\underline{R}}$ ead  $\underline{\underline{R}}$ ead  $\underline{\underline{N}}$ Ead  $\underline{\underline{N}}$ ) and HWRDY ( $\underline{\underline{H}}$ ost  $\underline{\underline{W}}$ rite  $\underline{\underline{R}}$ ead  $\underline{\underline{N}}$ Ead bits on the status register.

HRRDY = 1 indicates that the device set is ready to send some data to the host system. HWRDY = 1 means that the device set is waiting for command code and data to come from the host system. Note that the two status signals will not be 1 simultaneously.

Host system operational sequence is as follows:

- (1) When commands/data are written into the device set,

- ① Check whether HWRDY 1.

- ② Go to ① when HWRDY is 0 (when the device set is not ready to receive command / data from the host system).

- Write command code or data into the device set when HWRDY is 1 (when the device set is waiting for command code or data). The finish of writing operation automatically leads to HWRDY = 0. (The device set is released from the command / data waiting state.) Exit.

- (2) When data are read out from the device set

- ① Check whether HRRDY = 1.

- ② Return to ① when HRRDY is 0.

- ③ Read data from the device set when HRRDY is 1 (when the device set is ready to output date to the host system). Reading operation automatically leads to HRRDY = 0. (The device set is released from the sending-data ready state.) Exit.

Fig. 5.8 illustrates the "hand shake" protocol timing chart.

Fig.5.8 "Hand shake" timing chart

64E D

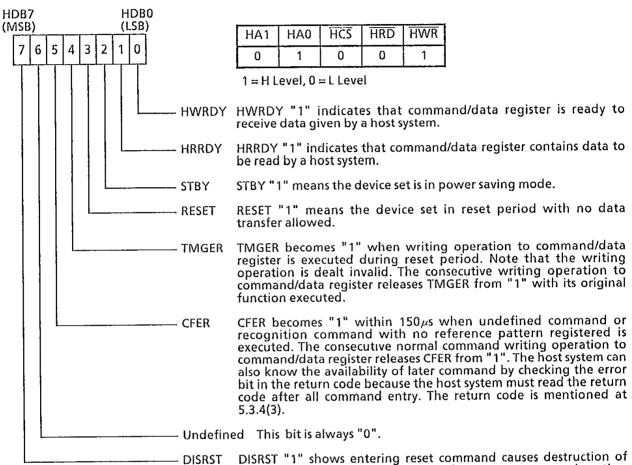

#### 5.2.5 How to Use Status Register

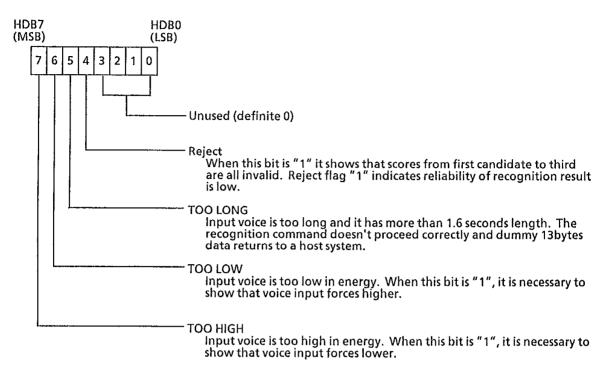

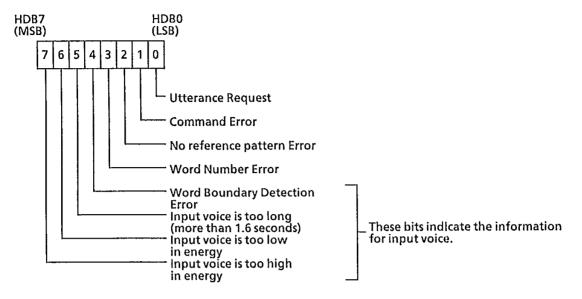

Status register with 8bit flags indicating the device set state is allowed only to be read. Reading operation doesn't require the "hand shake" protocol described in 5.2.4. Instead reading is permitted in any instance. Each bit flag meaning is explained in the following figure.

DISRST "1" shows entering reset command causes destruction of reference pattern in executing reference pattern registration command. So when DISRST is "0" or the command without reference pattern registration command is in executing, the host system can initialize the device set with no attention by using reset command. But in this case the host system must enter the reset command within 20ms after checking the DISRST status.

Fig.5.9 Flag meanings of status register

64E D

#### 5.2.6 How to Use Reset/Stand-by Register

Reset/stand-by register with a 1bit writing only flipflop offers three kinds of functions determined by combination of the current device set state (power saving mode or operating mode) and 1bit datum, 0 or 1, to be written.

Writing with the least significant bit (LSB) of 0 (ex. 00H) to the reset/stand-by register in the operating mode results in reset command execution, which initializes the device set in hardware way and then returns it back to a waiting state for host system commands. Also writing with LSB of 1 (ex. 01H, FFH) in the operating mode leads to the power saving mode in the device set; which ceases all operations. Writing with LSB of 0 in the power saving mode releases the device set from the power saving mode to the operating mode.

Table 5.4 describes pin settings and functions. Note that writing to the reset/stand-by register do not require the "hand shake" protocol described in 5.2.4, and is allowed to be executed any time.

Table 5.4 Reset/stand-by register function

| HA1 | НА0 | HCS | HRD | HWR | HDB0<br>(LSB) | Description                                   | The Device Set State on Writing |

|-----|-----|-----|-----|-----|---------------|-----------------------------------------------|---------------------------------|

| 1   | 0   | 0   | 1   | 0   | 0             | Reset the device set                          | Operating Mode                  |

| 1   | 0   | 0   | 1   | 0   | 1             | Place the device set in power saving mode     | Operating Mode                  |

| 1   | 0   | 0   | 1   | 0   | 0             | Release the device set from power saving mode | Power Saving Mode               |

1 = H level, 0 = L level

TOSHIBA (UC/UP)

64E D

#### 5.3 Host System Command

#### 5.3.1 Command List

All commands available are listed in Table 5.5. These commands are 8bit data written into the device set by a host system. The commands are divided into two categories, one employing command/data register and the other using reset/stand-by register.

Table 5.5 Command list (1 = H level, 0 = L level)

| Command Name                     | Command Code          | HA1 | НА0 | HCS | HRD | HWR | Notes          |

|----------------------------------|-----------------------|-----|-----|-----|-----|-----|----------------|

| Reference Pattern Initialization | 28H                   | 0   | 0   | 0   | 1   | 0   |                |

| Reference Pattern Registration   | 29H                   | 0   | 0   | 0   | 1   | 0   |                |

| Reference Pattern Deletion       | 2AH                   | 0   | 0   | 0   | 1   | 0   |                |

| Reference Pattern Bank Setting   | 2CH                   | 0   | 0   | 0   | 1   | 0   | Command/data   |

| Recognition 1,2 *                | 08H~0FH,<br>18H~1FH * | 0   | 0   | 0   | 1   | 0   | Register used  |

| Reference Pattern Down load      | 22H                   | 0   | 0   | 0   | 1   | 0   |                |

| Reference Pattern Up load        | 23H                   | 0   | 0   | 0   | 1   | 0   |                |

| Reject Level Set Up              | 3CH                   | 0   | 0   | 0   | 1   | 0   |                |

| Reset                            | HDB0 = 0              | 1   | 0   | 0   | 1   | 0   | Reset/stand-by |

| Stand-by On                      | HDB0 = 1              | 1   | 0   | 0   | 1   | 0   | Register used  |

| Stand-by Off                     | HDB0 = 0              | 1   | 0   | 0   | 1   | 0   | negister daed  |

\* Recognition command consists of Recognition 1 command and Recognition 2 command. In Recognition 1 command the device set uses average noise data that is measured before recognition command is entered as decision data for detecting word boundary. In Recognition 2 command the device set uses noise data that is measured just after recognition command is entered. Recognition 1 command code number is from 08H to 0FH and Recognition command 2 code number is from 18H to 1FH. If the host system has not executed bank setting command, command code 08H though 0FH has same effects as Recognition 1 command and command code 18H though 1FH has same effects as Recognition 2 command. On the other hand, if the host system executed bank setting command, command code 08H and 18H effects only bank 0 and 09H and 19H effects bank 1 and 0AH and 1AH effects bank 2 and so on.

64E D

Table 5.6 Recognition 1, 2 command list (1 = H level, 0 = L level)

| Command Name       | Command Code | Test Condition                                    |

|--------------------|--------------|---------------------------------------------------|

| Bank 0 Recognition | 08H、18H      | $HA1 = HA0 = \overline{HCS} = \overline{HWR} = 0$ |

| Bank 1 Recognition | 09H、19H      |                                                   |

| Bank 2 Recognition | OAH, 1AH     |                                                   |

| Bank 3 Recognition | 0BH, 1BH     |                                                   |

| Bank 4 Recognition | OCH, 1CH     | $\overline{HRD} = 1$                              |

| Bank 5 Recognition | 0DH、1DH      |                                                   |

| Bank 6 Recognition | OEH, 1EH     |                                                   |

| Bank 7 Recognition | OFH, 1FH     |                                                   |

#### 5.3.1 (1) Reference Pattern Initialization Command (28H)

Reference pattern initialization command initializes reference patterns and CPU scratchpad memory so that it may enable the device set to be ready for initial registration. The reference pattern memory is cleared to zero. This command should be executed at least once after power supply to the device set is turned on.

Process in the device set:

Start.

CPU scratchpad area in the external static RAM is initialized.

Reference pattern area is cleared to zero.

command waiting.

64E D

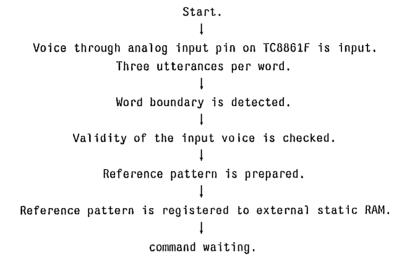

#### 5.3.1 (2) Reference Pattern Registration Command (29H)

This command registers voice features on reference pattern RAM segments designated by word numbers. Usually three utterances per word are required to be input through analog input pin on TC8861F. Reference pattern is generated by calculating these three utterances. If the similarity among the spoken three is low, another three utterances for the word are required.

Process in the device set:

#### 5.3.1 (3) Reference Pattern Deletion Command (2AH)

Reference pattern deletion command clears into zero reference pattern data of a specified word.

Process in the device set:

Start.  $\downarrow$  Reference pattern data for the designated word is cleared to zero.  $\downarrow$  command waiting.

64E D

#### 5.3.1 (4) Reference Pattern Bank Setting Command (2CH)

This command specifies connection with bank number and word number in each bank. After execution of reference pattern initialization command, whole words in the reference pattern connects with whole bank. After execution of reference pattern bank setting command, at the recognition command, only the registered words in the specified bank become recognition object.

Process in the device set:

Start.

Validity of written bank setting parameters for each bank is examined.

Bank setting parameters are registered to the specified area in scratchpad area.

command waiting.

#### Recognition Command 1,2 (08H~0FH, 18H~1FH) 5.3.1 (5)

These commands perform recognition of input voice with the reference pattern which is registered in reference pattern registration command. If the reference pattern doesn't exist (the case happens if any registration has not been executed after reference pattern initialization), the recognition command does not proceed any longer and returns command error code 02H and leads to command waiting state.

Process in the device set:

Start. Į

Voice through analog input pin on TC8861F is input.

Word boundary is detected.

Similarity scores between input voice and reference patterns are calculated.

Similarity scores are arranged in reverse numerical order.

Final recognition result is decided according to above similarity score order.

Recognition result is transferred to host system.

command waiting.

# TC8861F/65F-01-37

EZOT TSS OLESSON EMESTEDP

TOSHIBA (UC/UP)

64E D

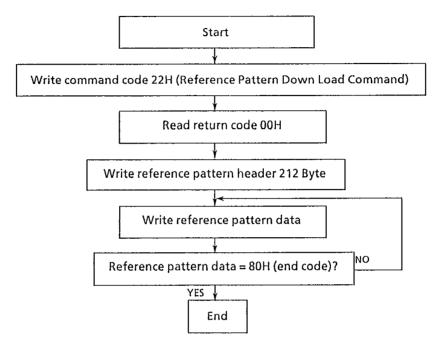

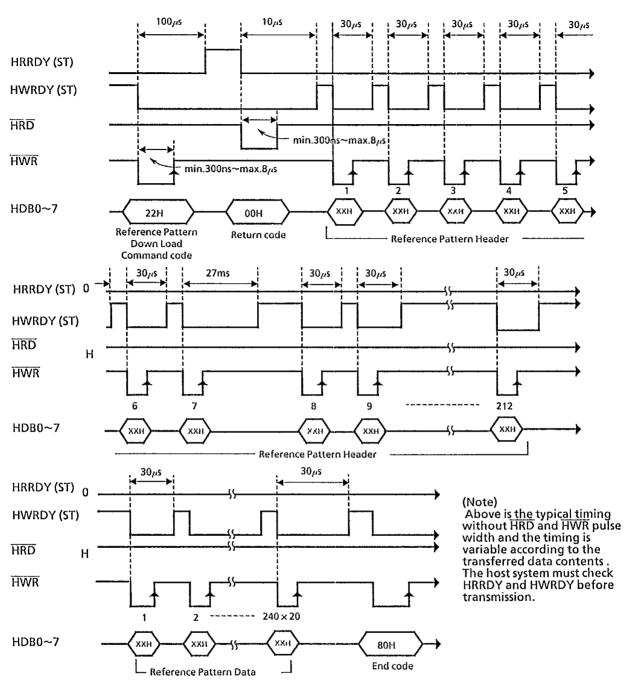

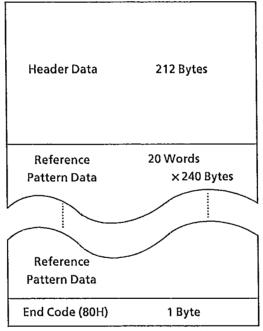

5.3.1 (6) Reference Pattern Down Load Command (22H)

Reference pattern down load command receives the reference patterns from a host system and then stores them to the external static RAM. When reference patterns already exist in the external static RAM, contents of reference pattern are replaced with the new data from the host system.

Process in the device set:

Start.

Header data (212 bytes) are received and stored to the scratchpad area.

Reference pattern data are transferred to device set until end of data code (80H) is met. They are all stored to the reference pattern area.

command waiting.

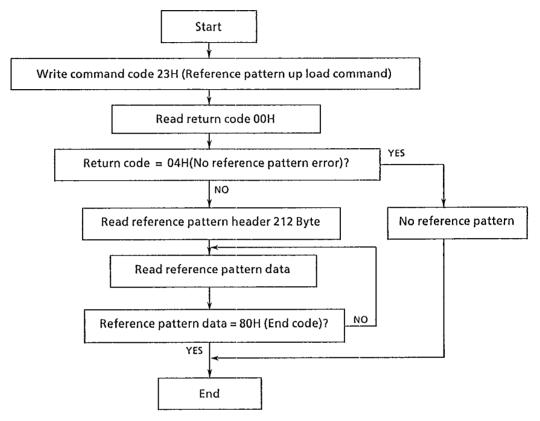

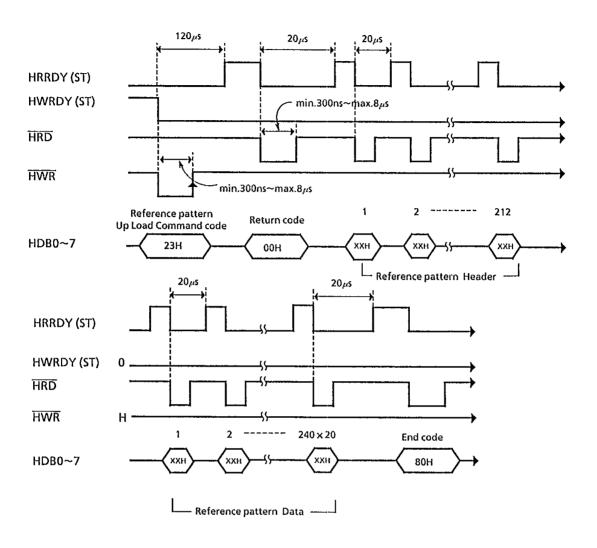

5.3.1 (7) Reference Pattern up Load Command (23H)

Reference pattern up load command sends the reference patterns to a host system. Reference patterns are transferred with the format explained in 5.3.4(4). When there is no reference patterns, if the host system sends this command, the device set returns the error code 04H and becomes command waiting mode.

Process in the device set:

Start.

Number of words (212 byte) is sent to host system.

Reference pattern data and end of data code (80H) are sent.

command waiting.

(qu/ou) ABIHZOT

64E D

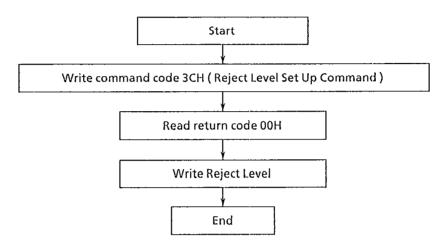

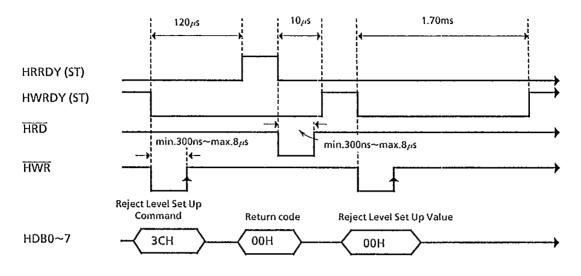

# 5.3.1 (8) Reject Level set up Command (3CH)

The device set tells information about that recognition result has low reliability by setting reject bit in recognition header. The decision whether reject or not is made by comparison similarity and criterion. This criterion is set up by reject level set up command. The initial reject level is set up as 01H by Reference pattern initialization command.

Process in the device set:

Start.

Reject level set up value is received.

Data validity is checked.

The data is stored to the work area.

command waiting.

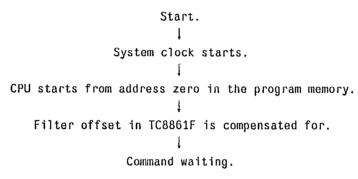

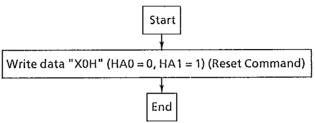

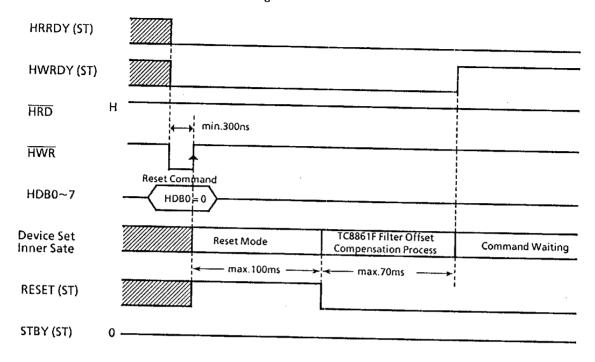

# 5.3.1 (9) System Reset Command (Reset / Stand-by Register)

This command initializes the device set in hardware manner. The data in the external static RAM keeps its contents after this command. But in some cases, the device can't keep the contents of the external static RAM. Refer to 5.3.3(14) Notes on system Reset Command Usage for more details.

Process in the device set:

Start.

CPU starts from address zero in the program memory.

Filter offset in TC8861F is compensated.

command waiting.

64E D

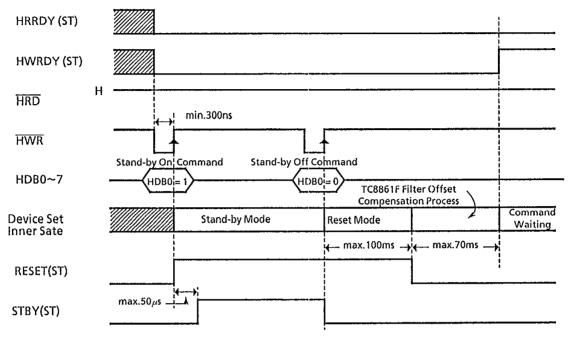

# 5.3.1 (10) System Stand-by on Command (Reset / Stand-by Register)

The device set has the power saving function. In the power saving mode, internal system clock is stopped and system power consumption becomes less than  $10\mu$ A. This state is called stand-by mode. The data in the scratchpad area and reference patterns keep their contents even in the stand-by mode. To release from stand-by mode, system stand-by off command should be executed.

Process in the device set:

$\label{eq:total_stand} \mbox{$\downarrow$}$  To stand-by mode (system clock is stopped).

# 5.3.1 (11) System Stand-by off Command (Reset / Stand-by Register)

This command releases the device set from stand-by mode to normal mode. In normal mode internal system clock operates normally.

Process in the device set:

(Note): Offset values vary by individual TC8861F or its assembly condition. Offset degrades frequency analysis accuracy of TC8861F and then reduces recognition performance. To eliminate this harmful influence, TC8861F is equipped with offset compensation function.

64E D

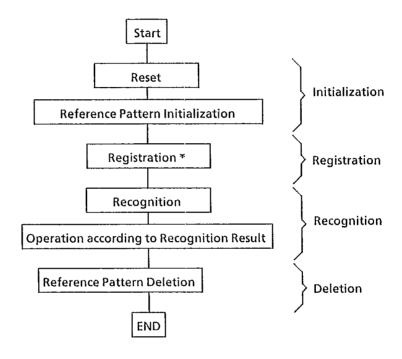

# 5.3.2 Host System Operation Flow Chart Example

Here described is a flow chart example to operate the device set in the following sequence:

- (1) Reference pattern initial registration.

- (2) Reference pattern registration.

- (3) Recognition.

- (4) Reference pattern deletion.

These three activities are essential to any recognition device. Fig.5.10 illustrates the flow chart. More details in each operation in Fig.5.10 are referred to 5.3.3.

Fig.5.10 Host system operation flow chart example

\* More than 3 utterances per word may be required in some cases.

See details in 5.3.3 (2) Reference Pattern Registration Command.

64E D

# 5.3.3 Command Description

This section describes a host system operational flow chart and a timing diagram for each command.

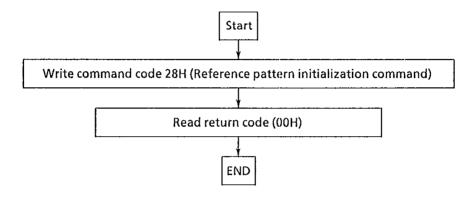

# 5.3.3 (1) Reference Pattern Initialization Command (28H)

Reference pattern initialization command initializes reference patterns and CPU scratch-pad memory so that it may enable the device set to be ready for initial registration. System parameters stored in the scratch-pad RAM are initialized. Reference patterns on external RAM are initialized to zero from word number 1 to the word number 20. This command should be executed at least once after power supply to the device set is turned on.

# (1) Flow chart

Fig.5.11 Reference pattern initialization command flow chart

64E D

(2) Timing chartand HWRDY before transmission.

\* ST means status in status resister. Status logic on the timing chart is shown by "0" or "1", and the device pin signal is shown by "L" or "H".

Fig.5.12 Reference pattern initialization command timing chart

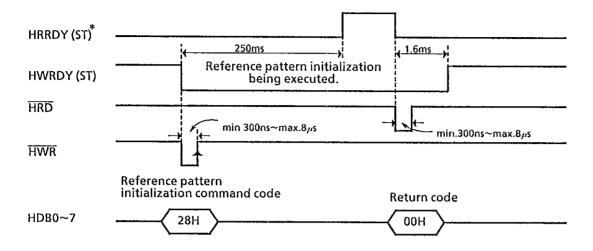

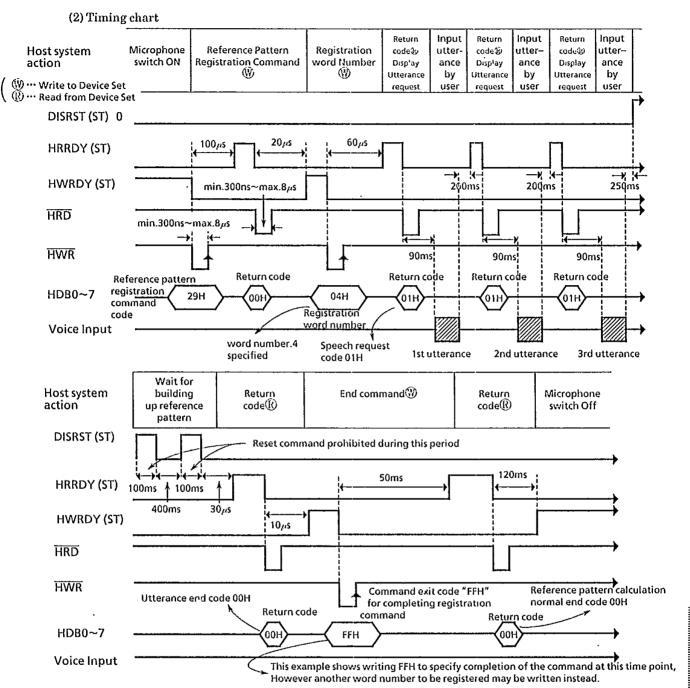

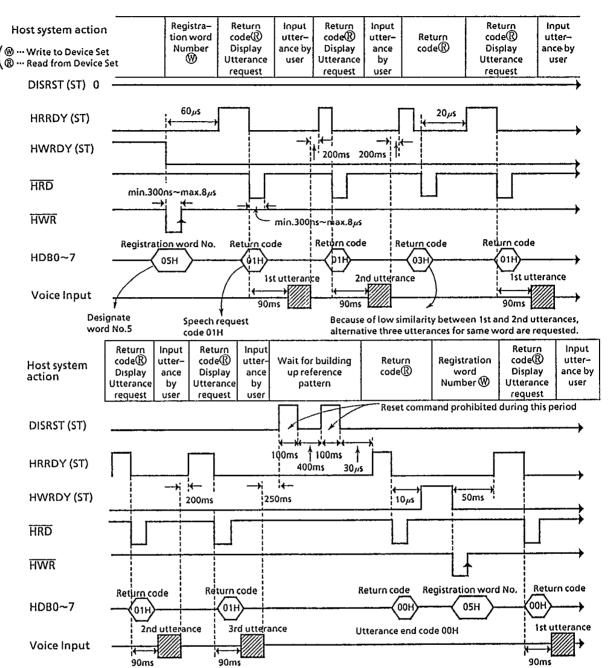

#### Reference Pattern Registration Command (29H) 5.3.3 (2)

This command registers voice features on reference pattern RAM segments designated by word number, It allows multiple words to be registration in single execution, When reference pattern already exists in designated word area, contents of reference pattern are replaced with new data, Fig. 5.13 shows the flow chart for a host system, After registration command (29H) is written to command/data register, the device set returns return code (00H) and asks for a word number to be registered, When the word number is written, usually three utterances per word are required to be input through analog input pin on TC8861F, In some cases where similarity among the spoken three is low, another three utterances for the word is required, The device set may request utterance up to 9 times per word, Writing "FFII" as a word number starts arithmetic operations to create reference patterns and then output return code which means normal end state, Reading this code leads the device set to the state waiting for another command, The arithmetic operations for more number of words stored require more processing time, Typical processing time is 10 seconds for 20 words.

#### (1) Flow chart

Fig. 5.13 Reference pattern registration command flow chart

64E D

Fig. 5.14 Reference pattern registration command timing chart (In the case of three times utterance for word)

(Note) Above is the typical timing without  $\overline{\text{HRD}}$  and  $\overline{\text{HWR}}$  pulse width and the timing is variable according to the transferred data contents, The host system must check HRRDY and HWRDY before transmission.

64E D

Fig. 5.15 Reference pattern registration command timing chart (The case of low similarity between 1st and 2nd utterance)

(Note) Above is the typical timing without HRD and HWR pulse width and the timing is variable according to the transferred data contents, The host system must check HRRDY and HWRDY before transmission.

64E D

(3) Cautions in Using Reference Pattern Registration.

A host system is required to observe cautions described below when it uses reference pattern registration command, Refer to Fig. 5.14 and Fig. 5.15 for thorough understanding.

- ① Microphone must be on and ready to transmit voice signal to TC8861F by the time the host system writes word number to be registered, When multiple of words are to be registered sequentially in a single registration command, the microphone may not be turned off word by word, Instead, it is allowed to be kept on all the time when reference pattern registration command is executing.

- ② After word number is written, the control code must be read out both to confirm the utterance request code 01H and to give users a prompt for utterance within 90ms from the time point when  $\overline{\text{HRD}}$  pin changes from H to L.

- ① However, a speaker is prohibited to give utterance in this 90ms time period, The reason is that the device set monitors environmental noise level to determine a threshold for discrimination of voice signal from background noise, This monitor is done immediately before the device set is ready to receive input voice signal, Thus the period is called environmental noise level monitoring period, So microphone must be on to receive background noise then, Also note that every utterance request is accompanied by the monitoring period.

- ① Nevertheless, a prompt to urge utterance can still be given to speakers within the period, It is because response time of human being is not less than 100ms, Therefore there is no risk that a speaker actually gives utterance in that period even if the speaker recognizes a prompt and utters immediately.

- ⑤ A prompt given far behind the period may cause the device set to mistake meaningless voice signal for targeted utterance, So a prompt is strongly recommended to be given within the period.

- ⑤ Once an utterance is given, the device set analyzes the utterance acoustic signal and sets HRRDY status flag to 1 at its completion, The control code is then read out to check whether the given utterance is normally accepted, The control codes 00H or 01H indicates normal completion of voice input activity but the others mean abnormal completion, 00H indicates that three utterances for a word have been successfully given, whereas 01H shows that more utterances for the word are to be given next, Other codes than 00H and 01H urge the host system to read out another control code successively, Then the device set retries a prompt again for the first utterance of the word.

(QU\)U) ABIHZOT

64E D

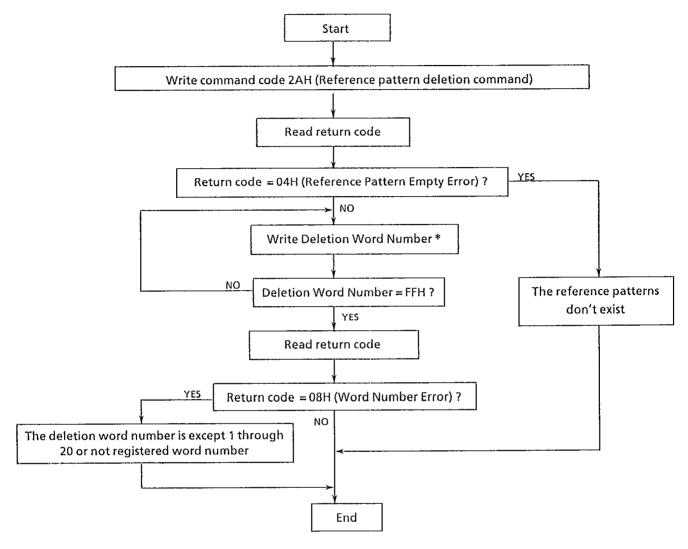

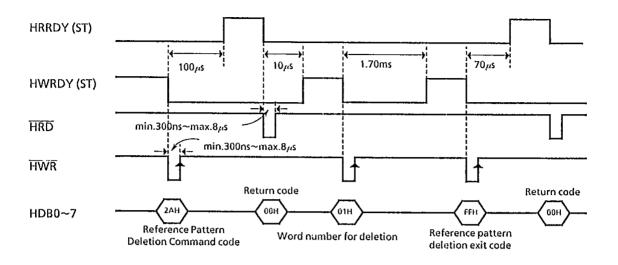

# 5.3.3 (3) Reference Pattern Deletion Command (2AH)

Reference Pattern Deletion command clears reference pattern data of a specified word into zero, Word numbers and their reference patterns of words other than the specified remains unchanged.

#### (1) Flow Chart

\* If the host system writes the word number which is not registered or not 1 through 20, the reference pattern or work area contents are not destroyed.

Fig.5.16 Reference pattern deletion command flow chart

64E D

(2) Timing Chart

Fig.5.17 Reference pattern deletion command timing chart

# (Note)

Above is the typical timing without  $\overline{\text{HRD}}$  and  $\overline{\text{HWR}}$  pulse width and the timing is variable according to the transferred data contents, The host system must check HRRDY and HWRDY before transmission.

64E D

# 5.3.3 (4) Reference Pattern Bank Setting Command (2CH)

This command specifies connection with bank number and word number in each bank, After execution of reference pattern initialization command, whole words in the reference pattern connects with whole bank, After execution of reference pattern bank setting command, at the recognition command, only the registered words in the specified bank become recognition object. Each word in the reference pattern can set multiple bank. For example, word number 2 can set into bank 0 and bank 3, If the host system write word number FFH right after writing bank number, the bank holds no word and if the host system select this bank at recognition command, error status will be returned

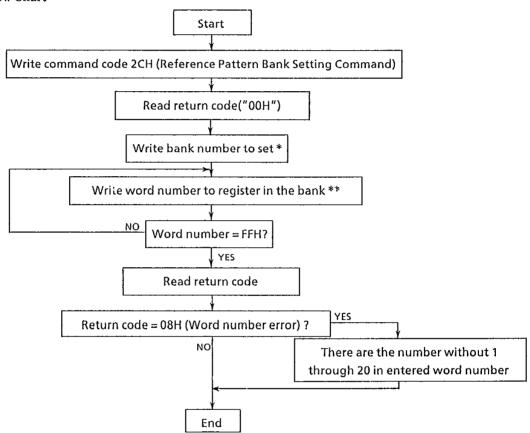

#### (1) Flow Chart

- \* The device set uses lower 3 bit and doesn't check the validity of input data.

- \*\* The word number 1 through 20 is available, If the host system enters the number without 1 through 20, the input data is ignored and the device set returns 08H as word number error.

Fig.5.18 Reference pattern bank setting command flow chart

(QU/JU) ABIHZOT

64E D

(2) Timing Chart

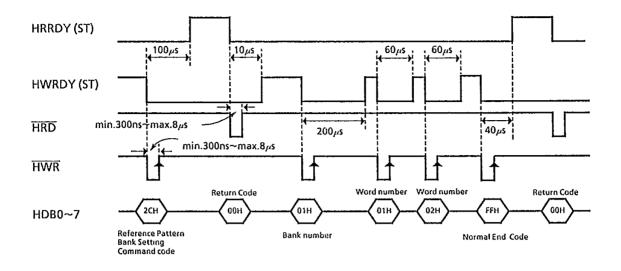

Fig.5.19 Reference pattern bank setting command timing chart

# (Note)

Above is the typical timing without HRD and HWR pulse width and the timing is variable according to the  $transferred\ at a\ contents\ , The\ host\ system\ must\ check\ HRRDY\ and\ HWRDY\ before\ transmission\ .$

TC8861F/65F-01-51 ■ 9097249 0025524 864 ■ T0S3

TOSHIBA (UC/UP)

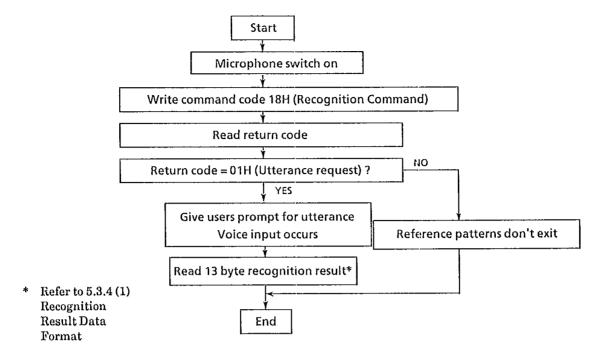

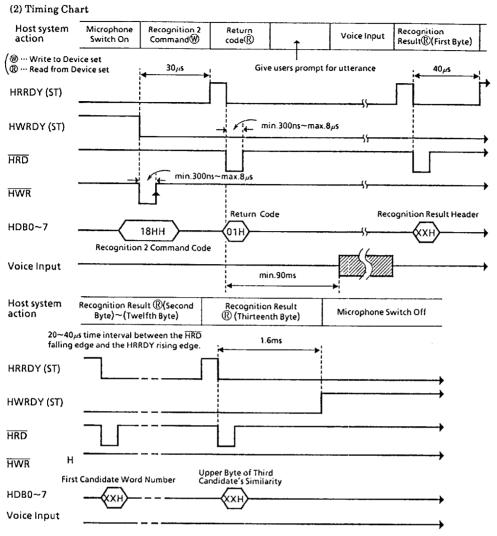

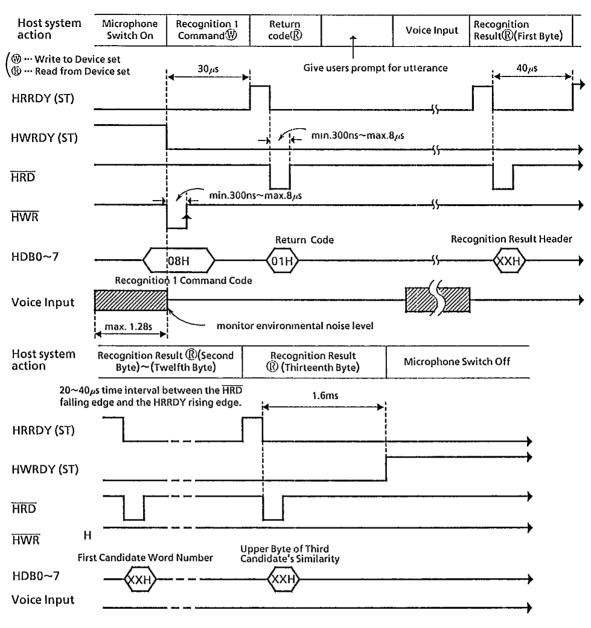

Recognition Command 1,2 (08H~0FH, 18H~1FH) 5.3.3 (5)

> The command performs recognition of input voice on vocabulary reference patterns registered by reference pattern registration command. As a result 13byte data returns back to a host system.

> If the reference patterns don't exist (the case happens if any registration has not been executed after reference pattern initialization), the recognition command does not proceed any longer and the device set returns command error code 02H to host system and becomes command waiting state.