TOSHIBA CMOS Digital Integrated Circuit Silicon Monolithic

# TC9028AP, TC9028AF

# Infrared Remote Control Transmitting CMOS LSI with Microcontrolling

TC9028AP, TC9028AF is CMOS LSI for Infrared Remote Control Transmitting suitable for Remote Controlling TV, VCR, Video Disk, CD-Player etc.

Using a 4 bit Microcontroller, various transmittings are structured by a programming.

#### **Features**

• Low voltage operation: 2.0~4.0 V

• Low power dissipation: ≤ 1 µA (at Hold Function)

• Program memory (ROM) capacity: 768 × 8 bit

• Data memory (RAM) capacity: 16 × 4 bit

• Instruction: 44 kinds

• Timer/Counter: 10~15 bit

• I/O port (15pins)

I/O : 2 ports 8 pins Input : 1 port 4 pins

Output: 1 port 3 pins (Including High Current Output)

• Subcarrier frequency: fosc/12, fosc/8

$f_{osc}/24$ ,  $f_{osc}/16$  (Option)

• Oscillating frequency: 400~800 kHz

Instruction execution time: 11 μs (at 455 kHz)

Package : DIP20 (TC9028AP) SOP20 (TC9028AF)

Note: This device is Vulnerable to surge voltages.

Take it into account when using this device in your system.

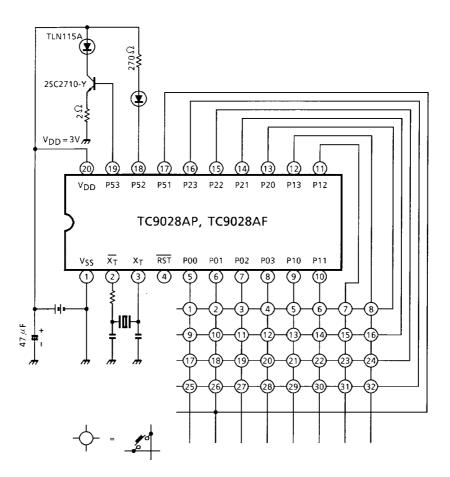

# Pin Connection (top view)

Weight

DIP20-P-300-2.54A: 1.4 g (typ.) SOP20-P-300-1.27: 0.48 g (typ.)

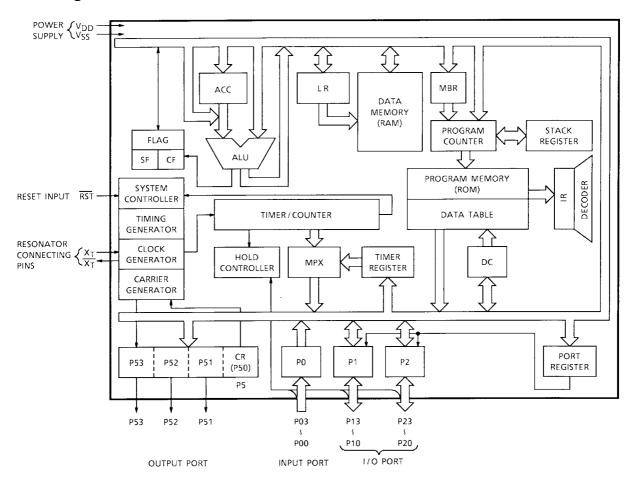

# **Block Diagram**

# **Pin Function**

| Pin No.  | Symbol          | Pin Name        | Function                                                                       |

|----------|-----------------|-----------------|--------------------------------------------------------------------------------|

| 1        | $V_{SS}$        | Power supply    | V <sub>DD</sub> = 2.0 V to 4.0 V, 3 V (typ.)                                   |

| 20       | $V_{DD}$        | Fower suppry    | V <sub>DD</sub> = 2.0 V to 4.0 V, 3 V (typ.)                                   |

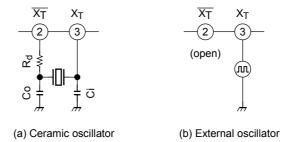

| 2        | $\overline{XT}$ | Output for osc. | Resonator connecting pins. Connects ceramic resonator with capacitor. Built-in |

| 3        | X <sub>T</sub>  | Input for osc.  | feedback resistance.                                                           |

| 4        | RST             | Reset input     | RST for going reset. Be held to "L". (≥ 3 instruction cycles)                  |

| 5 to 8   | P00 to 03       | Input port P0   | 4bit input port. Built-in pulldown resistance.                                 |

| 9 to 12  | P10 to 13       | I/O port P1     | 4bit I/O ports with latch. Input/output mode can be specified by [MOV A, P]    |

| 13 to 16 | P20 to 23       | I/O port P2     | instruction. Built-in pulldown resistance.                                     |

| 17       | P51             | Output port P51 | Pch open drain output port.                                                    |

| 18       | P52             | Output port P52 | High current output port. For driving indication LED.                          |

| 19       | P53             | Output port P53 | High current output port. For driving infrared LED.                            |

# Operation

## 1. Configuration

- (1) Program counter (PC)

- (2) Memory bank register (MBR)

- (3) Stack register (STACK)

- (4) Data counter (DC)

- (5) Program memory (ROM)

- (6) L register (LR)

- (7) Data memory (RAM)

- (8) Arithmetic and logic unit (ALU), accumulator

- (9) Flags

- (10) Clock generator, timing generator

- (11) I/O ports

- a. Port register (PR)

- b. Command register (CR)

- (12) Timer counter

- a. Timer register (TR)

- b. Timer counter output

- c. Watch dog timer output

- (13) Hold mode control circuit

- (14) Reset circuit

Following is a description of the hardware configuration and operation of the components listed above.

## 2. Internal CPU functions

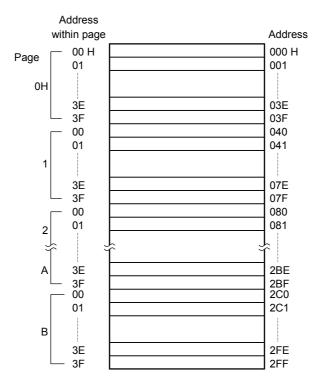

## 2.1 Program counter (PC)

The program counter is a 10bit binary counter which holds the program memory address of the next instruction to be executed.

The program counter is normally incremented for each instruction fetch.

When branch instructions and subroutine instructions are executed, the values specified in Table 2.1 are set. The program counter is initialized to 0 at reset.

Figure 2.1 Program memory configuration

3

Table 2.1 Program counter values depending on conditions

| Inetru                | ction or                 |                   |                                    |                           |     |                 | Prog                                        | gram Co                                   | ounter                                  | (PC)                              |     |     |       |  |  |

|-----------------------|--------------------------|-------------------|------------------------------------|---------------------------|-----|-----------------|---------------------------------------------|-------------------------------------------|-----------------------------------------|-----------------------------------|-----|-----|-------|--|--|

|                       | ration                   |                   | Condition                          |                           |     | Page Assignment |                                             |                                           |                                         | Address Specification within Page |     |     |       |  |  |

| 575                   | operation.               |                   |                                    | PC9                       | PC8 | PC7             | PC6                                         | PC5                                       | PC4                                     | PC3                               | PC2 | PC1 | PC0   |  |  |

|                       | LD MBR,<br>#k            | SF = 1<br>conditi | Memory bank register contents      |                           |     |                 | Value directly specified by BSS instruction |                                           |                                         |                                   |     | S   |       |  |  |

|                       | +<br>BSS a               | SF = 0<br>conditi | +2                                 |                           |     |                 |                                             |                                           |                                         |                                   |     |     |       |  |  |

|                       | BSS a                    | SF = 1            | Lower 6 bits of address<br>≠111111 | No change                 |     |                 |                                             | Value directly specified by instruction   |                                         |                                   |     |     | ction |  |  |

| Instruction execution |                          | 51 - 1            | Lower 6 bits of address = 1111111  |                           | +1  |                 |                                             |                                           | Value directly specified by instruction |                                   |     |     | ction |  |  |

|                       |                          | SF=0              |                                    |                           |     |                 |                                             | +                                         | 1                                       |                                   |     |     |       |  |  |

|                       | CALLS a                  |                   | 0                                  | 0                         | 0   | 0               | 0                                           | 0 Value directly specified by instruction |                                         |                                   | 0   |     |       |  |  |

|                       | RET                      |                   |                                    | Value restored from stack |     |                 |                                             |                                           |                                         |                                   |     |     |       |  |  |

|                       | Instructions other above | _                 |                                    | +1                        |     |                 |                                             |                                           |                                         |                                   |     |     |       |  |  |

| Reset                 |                          |                   | _                                  | 0                         | 0   | 0               | 0                                           | 0                                         | 0                                       | 0                                 | 0   | 0   | 0     |  |  |

#### 2.2 Memory bank register (MBR)

The memory bank register is a 4bit write-only register. It holds the page specification (upper 4 bits of the program counter) when a branch is made anywhere in program memory.

#### 2.3 Stack register (STACK)

The stack is a 10bit register. When the [CALLS a] instruction is executed, the stack register saves the contents of the program counter (return address) before the program jumps to the processing routine. Only one level of subroutines can be used. When there are two calls, the first return address is overwritten when the second return address is saved to the stack register.

When the program returns from the processing routine, execution of the [RET] instruction restores the contents of the stack register to the program counter.

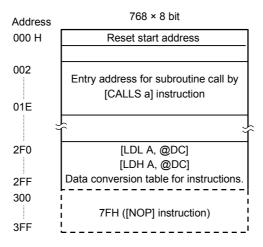

#### 2.4 Data counter (DC)

When fixed data stored in the data table in program memory (ROM) are read, the data counter (DC) are used to specify 4 bits of the address.

In addition to transferring data to the accumulator, the data counter is also equipped with increment and decrement functions and can therefore be used as a general-purpose register.

Fixed data stored in the data table can be read using the table look-up instruction.

4

When the table look-up instruction is executed, the upper 6 bits of the ROM address are "101111" and the lower 4 bits are the contents of the data counter (DC). These bits specify the last 16 bytes (addresses  $2F0\sim2FFH$ ) of program memory for fixed data.

# 2.5 Program memory (ROM)

Program memory stores program and fixed data. The next instruction to be executed is read from the address indicated by the program counter.

Physical program memory doesn't exist in addresses 300~3FFH.

When this area is read on the program, 7FH ([NOP] instruction) is read.

Figure 2.2 Program memory map

5

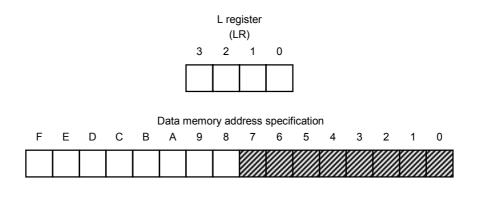

## 2.6 L register (LR)

The L register is a 4bit register. It is used as a data memory (RAM) address pointer. It can also be used as a general-purpose register.

#### 2.7 Data memory (RAM)

Data memory stores data to be processed by the user.

There are two data memory addressing modes. One is register indirect addressing mode, where the L register specifies an address. The other is direct addressing mode, where the lower 3 bits of the instruction field directly specify an address.

Figure 2.3 shows the L register and data memory configuration.

The data memory contents are undefined at reset. Make initial settings using the initialization routine.  $_{\circ}$

Note: Area directly addressable

Figure 2.3 L register and data memory configuration

6

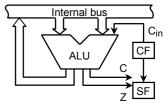

#### 2.8 ALU, Accumulator

#### 2.8.1 ALU

The ALU is a circuit which performs various operations on 4 bit binary data.

The ALU performs operations according to instructions and outputs results (4 bit), carry data (C) and zero detection data (Z).

Note: C<sub>in</sub> indicates carry input specified by instruction.

Figure 2.4 ALU and flags

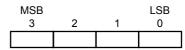

#### 2.8.2 Accumulator (Acc)

The accumulator is a 4bit register. It stores source data and results.

Figure 2.5 Accumulator

### 2.9 Flags (FLAG)

There are two types of flags: carry flag (CF) and status flag (SF).

These are set and cleared according to conditions specified by instructions.

The status flag is initialized to 1 at reset.

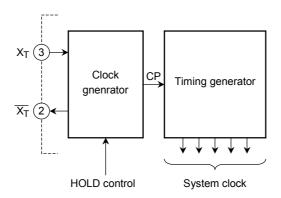

#### 2.10 Clock generator, Timing generator

Figure 2.6 shows the clock generator and timing generator configuration.

Figure 2.6 Clock generator and timing generator

#### 2.10.1 Clock generator

The clock generator is a circuit which generates the fundamental clock pulse (CP) as the basis for the system clock supplied to the CPU. The fundamental clock is easily established by connecting the oscillator to the  $\overline{X_T}$  and  $X_T$  pins. A clock can also be input from an external oscillator.

Clock input to the XT pin is used as the fundamental clock.

The clock generator stops oscillation during hold mode.

Figure 2.7 Typical oscillator connections

#### 2.10.2 Timing generator

The timing generator is a circuit which uses the fundamental clock to generate various system clocks for the CPU and peripheral hardware.

#### 2.10.3 Instruction cycle

Instructions and internal hardware operations are executed in sync with the fundamental clock. The minimum unit of instruction execution is called the instruction cycle. TC9028AP and TC9028AF has 1 and 2-cycle instructions. An instruction cycle consists of 5 states (S0-S4). Each state consists of 1 fundamental clock. Therefore, the instruction cycle time is  $5/f_c$  [s].

## 3. Peripheral hardware functions

#### 3.1 Ports

The following functions are executed using I/O instructions (4 types):

key scan, send signal output, send display output, internal circuit control.

This system features the 2 types of ports listed below. Addresses (00-05H) are allocated to these ports:

- (1) I/O ports: key scan, send signal output, send display output

- (2) Command register: internal circuit control

Ports are selected by specifying port addresses with I/O instructions. The port register controls input and output of programmable I/O ports.

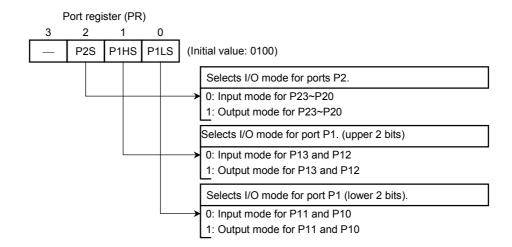

#### 3.1.1 Port register (PR)

The port register is a 4 bit write-only register. It is used for selecting input or output mode for programmable I/O ports. Since an option is used to select input or output mode during hold, the port register cannot select the mode.

Figure 3.1 Programmable I/O port control using port register

8

#### 3.1.2 I/O ports

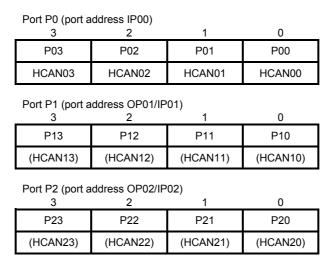

TC9028AP and TC9028AF has 4 I/O ports with 15 pins.

- 1. Port P0: 4 bit input

- 2. Ports P1, P2: 4bit programmable input/output

- 3. Port P5: 3 bit output (P52 and P53 are for large current output)

#### (1) Port P0 (P03 to P00)

Port P0 is a 4bit input port. All its pins are equipped with hold mode cancellation function.

#### (2) Ports P1 (P13 to P10), P2 (P23 to P20)

Ports P1, P2 are 4bit programmable I/O ports with latches.

Input or output can be selected by program. (8 types)

Latches are initialized to 1 at reset.

Pins which can be switched using an option to input mode during hold mode are equipped with hold mode cancellation functions.

Figure 3.2 Ports P0, P1 and P2

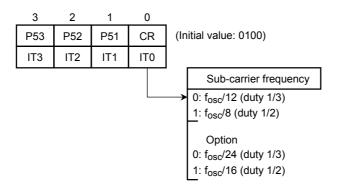

#### (3) P5 (P53 to P51) port

Port P5 is a 3bit output port with a latch.

P51 is for P-ch open-drain output. An option allows it to be used for push/pull output. The latch is initialized to 0 at reset.

P52 is for large current output for driving the send display LED.

The output latch is initialized to 1 at reset.

P53 is for large current output for driving the infrared LED. Resetting the output latch to 1 outputs  $f_{\rm 0sc}/12$  (duty 1/3) or  $f_{\rm 0sc}/8$  (duty 1/2) sub-carrier frequency for modulation. An option allows selection of  $f_{\rm 0sc}/24$  (duty 1/3) or  $f_{\rm 0sc}/16$  (duty 1/2) sub-carrier frequency. Sub-carrier frequency (duty) is selected by the command register. The latch is initialized to 0 at reset. The LSB (P50) of the port P5 is used for selecting the sub-carrier frequency (duty) output from P53 using the write-only command register.

The latch is initialized to 0 at reset.

Although port P5 is an output port, when an input instruction is executed, P5 can read timer/counter output (IT3 to IT0).

Port P5, Command Register (port address OP05) and,

Timer / Counter Output (port address IP05)

Figure 3.3 Port P5

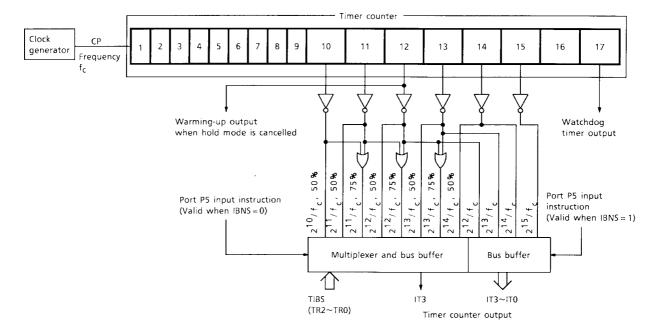

#### 3.2 Timer/counter

The timer/counter is a 17 step binary counter used to divide the fundamental clock. It outputs a pulse with a cycle selected from steps 10 through 15.

The timer/counter is a 17 step binary counter used to divide the fundamental clock. It outputs a pulse with a cycle selected from steps 10 through 15.

The uses of the timer/counter are listed below. The timer/counter is cleared to 0 at reset, when a timer reset instruction (TMRST) is executed, and when hold mode is cancelled.

- 1. Timer generating  $f_c/2^{10}$  to  $f_c/2^{15}$  [Hz] pulses

- 2. Watchdog timer

- 3. Warming-up timer when hold mode is cancelled

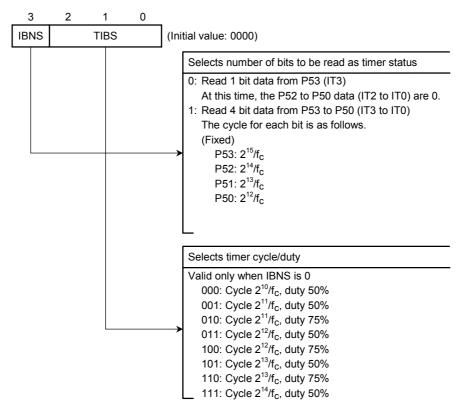

## 3.2.1 Timer register (TR)

The timer register is a 4bit write-only register.

It selects the mode when the timer status is read.

The timer register is initialized to 0 at reset.

Figure 3.4 Timer/counter output mode control using timer register

#### 3.2.2 Timer counter output (IT3 to IT0)

The timer counter is cleared to 0 at reset. It is incremented, from 0, each time the fundamental clock is input. The timer counter output transfers the inverted value of the timer counter to the accumulator or data memory using port P5 input instructions [IN %IP05, A] and [IN %IP05, @LR]. Thus, 1 is read at reset. (Decrement)

Figure 3.5 Timer counter configuration

### 3.2.3 Watchdog timer output

The watchdog timer output becomes active  $2^{16}/f_c$  (s) after the timer is reset. If the timer is not reset again before timer reset, TC9028AP and TC9028AF regards this as a CPU runaway and resets the CPU.

#### 4. Low power consumption operation

TC9028AP and TC9028AF features a hold mode for low power consumption operation.

#### 4.1 Hold mode

The hold function stops system operation and holds the internal states in effect immediately before stopping.

The hold function is controlled by the port hold mode cancellation function and by the hold instruction [HOLD]. The hold cancel function is valid with pins P00 to P03, and with pins P10 to P13, P20 to P23 (HCAN pins) which are switched using and option to input mode during hold mode.

#### 4.1.1 Hold mode

Hold mode is activated by executing the hold instruction [HOLD]. Hold mode continues as long as the HCAN pins are at low level.

The following states are held during hold mode.

- (1) Oscillation stops and all internal operations stop.

- (2) The timer counter is cleared to 0.

- (3) Data memory, registers, and port latches hold the states immediately before entering hold mode. (Note that the status flag is set to 1.)

- (4) The program counter holds the 2 addresses after the hold instruction.

(After hold mode is cancelled, execution resumes with the instruction following the hold instruction.)

#### 4.1.2 Hold mode cancellation

Hold mode is cancelled and normal operation resumes when high level is input to the HCAN pins during hold mode.

Hold mode is cancelled in the following sequence.

- (1) Oscillation begins.

- (2) Warming-up for the time required to stabilize oscillation. Internal operation remains stopped during warming-up. The warming-up time is 2<sup>11</sup>/fc (s).

- (3) After the warming-up time has elapsed, normal operation resumes from the instruction following the hold instruction.

Note: The fundamental clock is divided by the interval timer. If the oscillation frequency fluctuates after hold mode is cancelled, the warming-up time is not exactly the same as the value given above. Thus, the warming-up time has allowance.

Hold mode is also cancelled by setting the  $\overline{RST}$  pin to low level. In this case, the reset operation is performed immediately. Since normal operation begins at the same time the reset operation is cancelled, the RST pin must be kept at the low level for the warming-up time until oscillation becomes stable.

If input to the HCAN pin is at high level, executing the hold instruction does not enter hold mode but instead moves immediately to the cancellation sequence (warming-up). The warming-up time in this case is an undefined value between 0 to  $2^{11}$ /fc (s). Therefore, when the hold instruction is executed, input to the HCAN pin must be set to low level.

## 5. Reset

If the  $\overline{\text{RST}}$  pin remains at low level for more than a minimum of 3 instruction cycles (15 fundamental clocks) when the power supply voltage is within the operating voltage range and oscillation is stable, the system is reset and the internal states are initialized.

When the  $\overline{RST}$  pin is set to high level, the reset operation is cancelled and execution of the program at address 000H begins.

Table 5.1 Initialization of internal states by reset

| Internal Hardware    | Initial Value | Internal Hardware          | Initial Value                    |  |  |

|----------------------|---------------|----------------------------|----------------------------------|--|--|

| Program counter (PC) | 000H          |                            |                                  |  |  |

| Status flag (SF)     | 1             | Output latches (I/O ports) | See description of I/O circuits. |  |  |

| Port register (PR)   | 000B          |                            |                                  |  |  |

# **Instruction list**

| F ati a      | D.4  |         |      | Obje | ct Code     | Organstian                                     | F  | ag | Cyalaa |

|--------------|------|---------|------|------|-------------|------------------------------------------------|----|----|--------|

| Function     | IVIN | emonic  | Bin  | ary  | Hexadecimal | Operation                                      | CF | SF | Cycles |

|              | LD   | A, @LR  | 0000 | 0110 | 06          | Acc ← RAM (LR)                                 | _  | 1  | 1      |

|              | LD   | A, x    | 1001 | 0xxx | 90 + x      | $Acc \leftarrow RAM [x]$                       | _  | 1  | 2      |

|              | LDL  | A, @DC  | 0110 | 0111 | 67          | $Acc \leftarrow ROM \; \left( DC \right) \; L$ | _  | 1  | 2      |

|              | LDH  | A, @DC  | 0110 | 0110 | 66          | $Acc \leftarrow ROM \; \left( DC \right) \; H$ | _  | 1  | 2      |

|              | ST   | A, @LR  | 0111 | 0110 | 76          | RAM (LR) ← Acc                                 | _  | 1  | 1      |

|              | ST   | #k, @LR | 0011 | kkkk | 3k          | RAM (LR) ← k                                   | _  | 1  | 1      |

|              | ST   | A, x    | 1001 | 1xxx | 98 + x      | RAM [x] ← Acc                                  | _  | 1  | 2      |

| Transfer     | LD   | A, #k   | 0001 | kkkk | 1k          | $Acc \leftarrow k$                             | _  | 1  | 1      |

|              | LD   | L, #k   | 0010 | kkkk | 2k          | $LR \leftarrow k$                              | _  | 1  | 1      |

|              | MOV  | L, A    | 0000 | 1111 | 0F          | $Acc \leftarrow LR$                            | _  | 1  | 1      |

|              | MOV  | A, L    | 0000 | 1100 | 0C          | LR ← Acc                                       | _  | 1  | 1      |

|              | MOV  | D, A    | 0000 | 1110 | 0E          | Acc ← DC                                       | _  | 1  | 1      |

|              | MOV  | A, D    | 0000 | 1101 | 0D          | DC ← Acc                                       | _  | 1  | 1      |

|              | MOV  | A, P    | 0111 | 1110 | 7E          | PR ← Acc                                       | _  | 1  | 1      |

|              | MOV  | A, T    | 1000 | 1010 | 8A          | TR ← Acc                                       | _  | 1  | 1      |

|              | IN   | %p, A   | 0110 | 0ррр | 60 + p      | Acc ← PORT (p)                                 | _  | Z  | 2      |

| Input/output | IN   | %p, @LR | 0110 | 1ppp | 68 + p      | $RAM\ (LR)\ \leftarrow PORT\ (p)$              | _  | Z  | 2      |

| πραι/σαιραι  | OUT  | A, %p   | 0111 | 0ррр | 70 + p      | PORT (p) ← Acc                                 | _  | 1  | 2      |

|              | OUT  | @LR, %p | 0111 | 1ррр | 78 + p      | PORT (p) ← RAM (LR)                            | _  | 1  | 2      |

| C                                           | Maa   |         |      | Obje | ct Code     | Operation                                     | F  | ag | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 1 |

|---------------------------------------------|-------|---------|------|------|-------------|-----------------------------------------------|----|----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---|

| Function                                    | ivine | emonic  | Bin  | ary  | Hexadecimal | Operation                                     | CF | SF | Cycles                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |   |

|                                             | ADD   | A, @LR  | 0000 | 0011 | 03          | Acc ← Acc + RAM (LR)                          | _  | C  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | ADDC  | A, @LR  | 0000 | 0100 | 04          | Acc ← Acc + RAM (LR) + CF                     | С  | C  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | ADD   | A, #k   | 0100 | kkkk | 4k          | Acc ← Acc + k                                 | _  | C  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | ADD   | L, #k   | 0101 | kkkk | 5k          | LR ← LR + k                                   | _  | C  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | SUBRC | @LR     | 0000 | 0101 | 05          | Acc ← RAM (LR) - Acc - CF                     | С  | С  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Operation<br>(Arithmetic                    | INC   | @LR     | 0000 | 1001 | 09          | RAM (LR) ←RAM (LR) +1                         | _  | C  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| and logical)                                | DEC   | A, @LR  | 0000 | 1000 | 08          | RAM (LR) ←RAM (LR) -1                         | _  | С  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | INC   | D       | 0000 | 1011 | 0B          | DC←DC + 1                                     | _  | C  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | DEC   | D       | 0000 | 1010 | 0A          | DC←DC - 1                                     | _  | С  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | AND   | A, @LR  | 0000 | 0000 | 00          | Acc ← Acc∧RAM (LR)                            | _  | Z  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | OR    | A, @LR  | 0000 | 0001 | 01          | Acc ← Acc V RAM (LR)                          | _  | Z  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | XOR   | A, @LR  | 0000 | 0010 | 02          | Acc ← Acc∀RAM (LR)                            | _  | Z  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Bit<br>manipulation                         | CLR   | @LR, b  | 1000 | 01bb | 84 + b      | RAM (LR) b ← 0                                | _  | 1  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

|                                             | SET   | @LR, b  | 1000 | 00bb | 80 + b      | RAM (LR) b ← 1                                | _  | 1  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | TEST  | @LR, b  | 1000 | 11bb | 8C + b      | SF ← RAM (LR) b                               | _  | *  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

|                                             | CLR   | CF      | 1000 | 1011 | 8B          | CF ← 0                                        | 0  | 1  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

| Bit<br>manipulation<br>Flag<br>manipulation | SET   | CF      | 1000 | 1001 | 89          | CF ← 1                                        | 1  | 1  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| ·                                           | TESTP | CF      | 0111 | 0111 | 77          | SF ← CF                                       | _  | *  | C       1         C       2         C       1         C       1         C       1         C       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z       1         Z |   |

| Branch                                      | BSS   | а       | 11dd | dddd | C0 + d      | if SF = 1 then PC←a else null,<br>a = PC9-6·d | _  | 1  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ٨ |

|                                             | LD    | MBR, #k | 1011 | kkkk | Bk          | MBR ← k                                       | _  | _  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Subroutine                                  | CALLS | а       | 1010 | nnnn | An          | STACK ← PC, PC ← a,<br>a = 2n (n = 1~15)      | _  | _  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | ٨ |

|                                             | RET   |         | 0110 | 1110 | 6E          | PC ← STACK                                    | _  | _  | 2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| CDI Locatas                                 | HOLD  |         | 0000 | 0111 | 07          | hold                                          | _  | 1  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 1 |

| CPU control                                 | NOP   |         | 0111 | 1111 | 7F          | no operation                                  |    | _  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

| Timer<br>counter<br>control                 | TMRST |         | 1000 | 1000 | 88          | reset timer counter                           | _  | _  | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |   |

Note 1: C : Carry from the highest digit for addition and non-borrow to the highest digit for subtraction.

$\, Z \,\,$  : Zero detection data are 1 when data transferred to the accumulator or RAM are  $0000_B.$

\* : Value specified by operation is set.

— : No flag change.

Note 2: The PC contains the address following the instruction being executed.

# Instruction code map

| Lower | 0                      | 1               | 2                | 3                | 4                 | 5                  | 6                    | 7         | 8          | 9          | Α           | В         | С           | D           | Е           | F           |

|-------|------------------------|-----------------|------------------|------------------|-------------------|--------------------|----------------------|-----------|------------|------------|-------------|-----------|-------------|-------------|-------------|-------------|

| Upper |                        |                 |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| 0     | AND<br>A,<br>@LR       | OR<br>A,<br>@LR | XOR<br>A,<br>@LR | ADD<br>A,<br>@LR | ADDC<br>A,<br>@LR | SUBRC<br>A,<br>@LR | LD<br>A,<br>@LR      | HOLD      | DEC<br>@LR | INC<br>@LR | DEC<br>D    | INC<br>D  | MOV<br>A, L | MOV<br>A, D | MOV<br>D, A | MOV<br>L, A |

| 1     |                        | LD A, #k        |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| 2     |                        | LD L, #k        |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| 3     |                        |                 |                  |                  |                   |                    |                      | ST #k, (  | @LR        |            |             |           |             |             |             |             |

| 4     |                        | ADD A, #k       |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| 5     |                        | ADD L, #k       |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| 6     | IN %p, A               |                 |                  |                  |                   | LDH<br>A<br>@DC    | LDL<br>A<br>@DC      | IN %p, LR |            |            |             |           |             |             |             |             |

| 7     | OUT A, %p ST A, @LR CF |                 |                  |                  |                   | TESTP<br>CF        | OUT @LR, %p MOV A, P |           |            |            |             | NOP       |             |             |             |             |

| 8     |                        | SET @           | DLR, b           |                  |                   | CLR @              | DHL, b               |           | TMRST      | SET<br>CF  | MOV<br>A, T | CLR<br>CF |             | TEST        | @LR, b      |             |

| 9     |                        |                 |                  | LC               | ) A, x            |                    |                      |           |            |            |             | ST        | A, x        |             |             |             |

| Α     |                        |                 |                  |                  |                   |                    |                      | CA        | ALLS a     |            |             |           |             |             |             |             |

| В     |                        |                 |                  |                  |                   |                    |                      | LD MBF    | R, #k      |            |             |           |             |             |             |             |

| С     |                        |                 |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| D     |                        |                 |                  |                  |                   |                    |                      | BSS       | а          |            |             |           |             |             |             |             |

| E     | DOO d                  |                 |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

| F     |                        |                 |                  |                  |                   |                    |                      |           |            |            |             |           |             |             |             |             |

Note 3: Blank code is undefined.

Note 4: 1-Cycle instruction 2-Cycle instruction

# **Maximum Ratings (Ta = 25°C)**

| Characteri            | stics    | Symbol           | Rating                                          | Unit  |

|-----------------------|----------|------------------|-------------------------------------------------|-------|

| Power supply voltage  |          | V <sub>CC</sub>  | -0.3~5.0                                        | V     |

| Input voltage         |          | V <sub>IN</sub>  | V <sub>SS</sub> - 0.3~<br>V <sub>DD</sub> + 0.3 | V     |

| Output current        |          | V <sub>OUT</sub> | V <sub>OUT</sub> –20                            |       |

| Power dissipation     | TC9028AP | PD               | 350                                             | mW    |

| Fower dissipation     | TC9028AF | FD               | 300                                             | IIIVV |

| Operation temperature | ;        | T <sub>opr</sub> | −20 to 75                                       | °C    |

| Storage temperature   |          | T <sub>stg</sub> | -40 to 125                                      | °C    |

# **Electrical Characteristics**

# Recommended Operating Conditions (In \*marked items, Ta = $-20\sim75^{\circ}$ C, unless otherwise specified, V<sub>DD</sub> = 3.0 V, Ta = 25°C)

| Characteristics         |           | Symbol           | Test<br>Circuit | Test Condition          | Min                      | Тур. | Max                      | Unit |  |

|-------------------------|-----------|------------------|-----------------|-------------------------|--------------------------|------|--------------------------|------|--|

| Operation power supp    | $V_{DD}$  | _                | _               | 2.0                     | _                        | 4.0  | V                        |      |  |

| Oscillation frequency * | ķ.        | f <sub>osc</sub> | _               |                         | 400                      | _    | 800                      | kHz  |  |

|                         | "H" level | V <sub>IH</sub>  | _               | Except hysteresis input | V <sub>DD</sub><br>× 0.7 | _    | V <sub>DD</sub>          | V    |  |

| Input voltago           |           |                  |                 | Hysteresis input (RST)  | V <sub>DD</sub><br>× 0.8 | _    | V <sub>DD</sub>          | v    |  |

| Input voltage           | "L" level | V <sub>IL</sub>  | _               | Except hysteresis input | 0                        | _    | V <sub>DD</sub><br>× 0.3 | V    |  |

|                         |           |                  |                 | Hysteresis input (RST)  | 0                        | _    | V <sub>DD</sub><br>× 0.2 |      |  |

# DC Characteristics (V<sub>DD</sub> = 3.0 V, Ta=25°C, unless otherwise specified)

| Charact                         | teristics         | Symbol          | Test<br>Circuit | Test Condition                                     | Min  | Тур. | Max | Unit |  |

|---------------------------------|-------------------|-----------------|-----------------|----------------------------------------------------|------|------|-----|------|--|

| Operation power supply currrent |                   | I <sub>DD</sub> | _               | f <sub>C</sub> = 455 kHz                           | _    | _    | 1.0 | mA   |  |

| Static dissipation current      |                   | I <sub>QD</sub> | _               | at hold function                                   | _    | _    | 10  | μΑ   |  |

| Pulldown resistance             |                   | R <sub>D</sub>  | _               | (P0, P1, P2)                                       | 100  | _    | 400 | kΩ   |  |

| Pullup resistance               | Pullup resistance |                 | _               | (RST)                                              | 25   | _    | 100 | kΩ   |  |

|                                 | "H" level         | la              | _               | V <sub>OH</sub> (P52) = 2. 6 V                     | -0.4 | -1.4 | _   |      |  |

| Output current                  | n level           | Іон             |                 | V <sub>OH</sub> (P53) = 1.5 V                      | -10  | _    | _   | mA   |  |

|                                 | "L" level         | I <sub>OL</sub> | _               | V <sub>OL</sub> (P52) = 1.5 V                      | 5    | _    | _   |      |  |

| Input leak current              |                   | ILI             | _               | V <sub>IN</sub> = V <sub>DD</sub> ·V <sub>SS</sub> | -1.0 | _    | 1.0 | μΑ   |  |

# **Application Circuit**

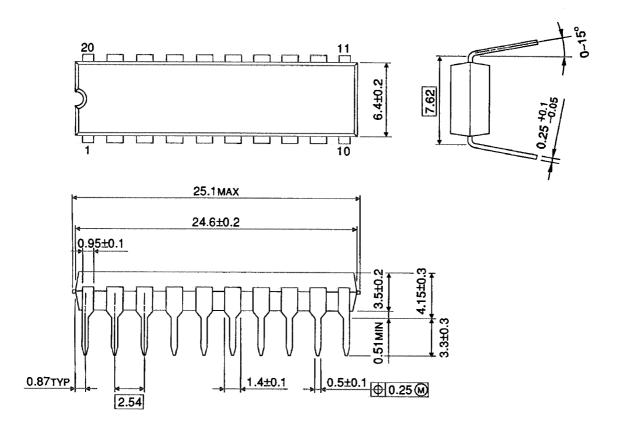

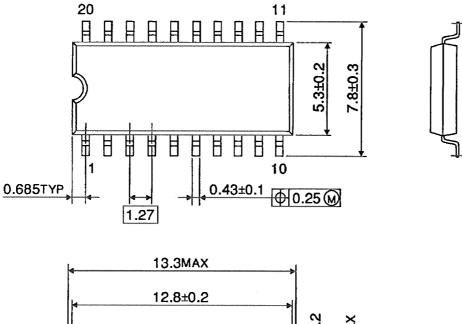

# **Package Dimensions**

DIP20-P-300-2.54A Unit: mm

Weight: 1.4 g (typ.)

# **Package Dimensions**

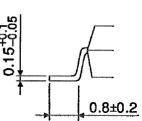

SOP20-P-300-1.27 Unit: mm

**Z** 0.1

7.62 (300mil)

Weight: 0.48 g (typ.)

# RESTRICTIONS ON PRODUCT USE

000707EBA

- TOSHIBA is continually working to improve the quality and reliability of its products. Nevertheless, semiconductor devices in general can malfunction or fail due to their inherent electrical sensitivity and vulnerability to physical stress. It is the responsibility of the buyer, when utilizing TOSHIBA products, to comply with the standards of safety in making a safe design for the entire system, and to avoid situations in which a malfunction or failure of such TOSHIBA products could cause loss of human life, bodily injury or damage to property. In developing your designs, please ensure that TOSHIBA products are used within specified operating ranges as set forth in the most recent TOSHIBA products specifications. Also, please keep in mind the precautions and conditions set forth in the "Handling Guide for Semiconductor Devices," or "TOSHIBA Semiconductor Reliability Handbook" etc..

- The TOSHIBA products listed in this document are intended for usage in general electronics applications (computer, personal equipment, office equipment, measuring equipment, industrial robotics, domestic appliances, etc.). These TOSHIBA products are neither intended nor warranted for usage in equipment that requires extraordinarily high quality and/or reliability or a malfunction or failure of which may cause loss of human life or bodily injury ("Unintended Usage"). Unintended Usage include atomic energy control instruments, airplane or spaceship instruments, transportation instruments, traffic signal instruments, combustion control instruments, medical instruments, all types of safety devices, etc.. Unintended Usage of TOSHIBA products listed in this document shall be made at the customer's own risk.

- The products described in this document are subject to the foreign exchange and foreign trade laws.

- The information contained herein is presented only as a guide for the applications of our products. No responsibility is assumed by TOSHIBA CORPORATION for any infringements of intellectual property or other rights of the third parties which may result from its use. No license is granted by implication or otherwise under any intellectual property or other rights of TOSHIBA CORPORATION or others.

- The information contained herein is subject to change without notice.