## TCP4620AP TCP4630AP SILICON MONOLITHIC

CMOS 4-BIT SINGLE CHIP MICROCOMPUTER GENERAL DESCRIPTION

TLCS-46A is a  $C^2 MOS$  high speed and low power 4-bit single chip micro-computer for consumer applications.

A single and integral microcomputer has been composed of a 4-bit parallel arithmetic and logical unit (ALU), accumulator (AC), program memory (ROM), data memory (RAM), input/output ports, clock generator, and divider incorporated.

TLCS-46A Family consists of two kinds of chips having different ROM/ RAM capacities for mass production and evaluator for system development.

## INTEGRATEDCIRCUIT

TECHNICAL DATA

## TCP4620AP TCP4630AP

#### FEATURES

- o TCP4620AP 2048 x 8 ROM 96 x 4 RAM 34 I/O Lines

- o TCP4630AP 3072 x 8 ROM 160 x 4 RAM 34 I/O Lines

- o TCP4600AP Evaluator Chip for TLCS-46A

- Low Power Dissipation by Employment of C<sup>2</sup>MOS Process

Typical Supply Current : 400µA (at 400 kHz Basic Clock)

- o Single 5V Supply

Wide Operating Range : 3V to 6V

o Wide Operating Temperature Range: -30°C to 85°C

- 52 Instructions

46 One Cycle Instructions

6 Two Cycle Instructions

- o Single Level Subroutine Nesting

- o Single Level External Interrupt

- o  $10\mu s$  Instruction Execution Time

- o PLA and Decode Matrix for Display Operation

- Many Kinds of Mask Options for Optimum

Application Systems

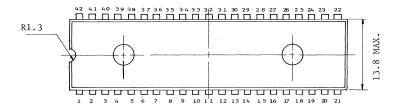

#### PIN CONNECTIONS (TOP VIEW)

|                  | <b></b>       | $\sim$      |          |

|------------------|---------------|-------------|----------|

| Роз              | <b>d</b> 1    | 42          | VDD      |

| P 02             | <b>C</b> 2    | 41 🛓        | P 23     |

| Poi              | <b>d</b> 3    | 40 þ        | P 22     |

| P oo             | <b>q</b> 4    | 39 🗖        | P 21     |

| P 13             | <b>C</b> 5    | 38 🗖        | P 20     |

| P 12             | <b>[</b> 6    | 37 🗖        | P43      |

| Pii              | <b>d</b> 7    | 36 🗖        | P 42     |

| P 10             | С 8           | 35 🗖        | P 41     |

| P0 67            | <b>d</b> 9    | 34 🗖        | P 40     |

| PO 66            | <b>C</b> 10   | 33 🗖        | ΡI 60    |

| P0 65            | <b>d</b> 11   | 32 🗖        | INT      |

| P <sub>064</sub> | <b>D</b> 12   | 31 🗖        | RESET    |

| РО <sub>63</sub> | <b>L</b> 13   | 30 🗗        | TEST     |

| P0 62            | <b>D</b> 14   | 29 <b>þ</b> | CK       |

| P0 61            | <b>d</b> 15   | 28 🗖        | XOUT     |

| P0 60            | <b>[</b> 16   | 27 Þ        | $X_{IN}$ |

| PO 54            | <b>L</b> 17   | 26 🗖        | PI 53    |

| P053             | <b>[</b> 18   | 25 🏼        | PI 52    |

| PO 5 2           | <b>d</b> 19   | 24 🏼        | ΡI 51    |

| PO 51            | <b>d</b> 20   | 23 🏼        | PI 50    |

| GND              | <b>D</b> 21 . | 22 <b>þ</b> | PO 50    |

|                  |               |             |          |

## PIN NAMES & PIN DESCRIPTION

| Pin Name                            | Input/Output    | Function                                                                                   |  |  |  |  |

|-------------------------------------|-----------------|--------------------------------------------------------------------------------------------|--|--|--|--|

| P . 3 - P                           | Input/Output    | 4-bit general purpose I/O port (I/O is designated by a program).                           |  |  |  |  |

| P <sub>13</sub> - P <sub>10</sub>   | Output          | 4-bit general purpose output port.                                                         |  |  |  |  |

| P <sub>23</sub> - P <sub>20</sub>   | Input or Output | 4-bit general purpose ] Input/Output is                                                    |  |  |  |  |

| P <sub>43</sub> - P <sub>40</sub>   | Input or Output | 4-bit general purpose designated by mask Input/Output port options.                        |  |  |  |  |

| PO <sub>54</sub> - PO <sub>50</sub> | Output          | 5-digit output port for display. (Can be<br>used as the general purpose 5-bit output port) |  |  |  |  |

INTEGRATEDCIRCUIT

TECHNICAL DATA

| Pin Name                           | Input/Output | Function                                                                                    |

|------------------------------------|--------------|---------------------------------------------------------------------------------------------|

| P0 <sub>67</sub> -P0 <sub>60</sub> | Output       | 8-segment output port for display (can be<br>used as the general purpose 8-bit output port) |

| PI53-PI50                          | Input        | 4-bit general purpose input port.                                                           |

| PI60                               | Input        | l-bit general purpose input port (with a internal Schmitt circuit).                         |

| RESET                              | Input        | Initialize signal input (with a internal Schmitt circuit).                                  |

| INT                                | Input        | Interrupt request signal input (with a inter-<br>internal Schmitt circuit).                 |

| XIN                                | Input        | Oscillator connecting terminal                                                              |

| X <sub>OUT</sub>                   | Output       | Oscillator connecting terminal                                                              |

| СК                                 | Output       | External timing output                                                                      |

| TEST                               | Input        | LSI test signal input, used by connecting to GND                                            |

| V <sub>DD</sub>                    |              | Power supply                                                                                |

| GND                                |              | GND                                                                                         |

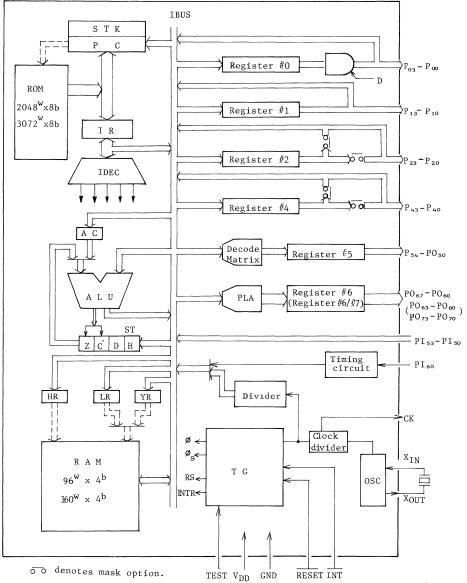

#### BLOCK DIAGRAM

#### FUNCTIONAL DESCRIPTION

#### [SYSTEM CONFIGURATION]

TLCS-46A consists of the following elements.

#### 1. BASIC ELEMENTS

- (1) Arithmetic and Logical Unit (ALU)

- (2) Accumulator (AC)

- (3) Status Register (ST)

- (4) H Register (HR), L Register (LR), Y Register (YR), Y Register Flag (EYR)

- (5) Port (P), Port Register (Register)

- (6) Internal Bus (IBUS)

- (7) Data Memory (RAM)

- (8) Program Memory (ROM)

- (9) Program Counter (PC)

- (10) Stack (STK), Stack Flag (FSTK)

- (11) Instruction Register (IR), Instruction Decoder (IDEC)

- (12) Clock Generator (OSC)

- (13) Divider

- (14) Timing Generator (TG)

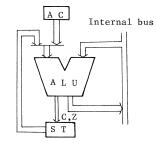

- (1) Arithmetic and Logical Unit (ALU)

ALU performs the principal function involved in the data processing of TLCS-46A, and consists of 4-bit binary parallel arithmetic circuit.

One of the inputs of the arithmetic and logical unit is the accumulator

or the status register, and another input is the internal bus, and the result of operation is output to the internal bus and at the same time, carry (barrow) and zero are detected.

(2) Accumulator (AC)

The accumulator is a 4-bit register that temporarily stores data for arithmetic process, arithmetic result and data from/to the input/output ports.

(3) Status Register (ST)

The status register is a 4-bit register having a meaning per bit, and is called H flag, D flag, C flag and Z flag in that order from LSB side.

| (MSB) |   |   | (LSB) |

|-------|---|---|-------|

| 3     | 2 | 1 | 0     |

| Z     | С | D | Н     |

(1) Zero Flag (Z)

The zero flag (Z) is set to "l", if the result generated by certain instructions is zero.

The zero flag is cleared, if the result is not zero.

Further, z flag is used not only for judgement of zero but also as a branch condition for program flow.

(2) C Flag

When an instruction indicating update is executed, C flag is set at "1" if carry is resulted at time of addition and increment, and at "0" if no carry is resulted.

Further C flag is also set at "0" when borrow is resulted at time of substruction and at "1" when no borrow is resulted. C flag is used for judging size of data and for multiple digit arithmatic operation.

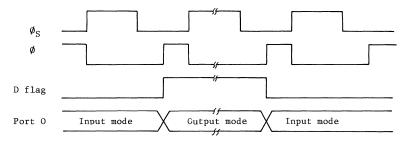

(3) D Flag

D flag is used by a program as an input/output designating signal of the input/output port (Po). When D flag is "0", the input/output port serves as the input port and when D flag is "1", it serves as the output port.

When the input/output port is used exclusively as the output port (specified by mask option), D flag becomes the general purpose flag bit that can be optionally used by user. D flag is reset at "0" by the initialize operation.

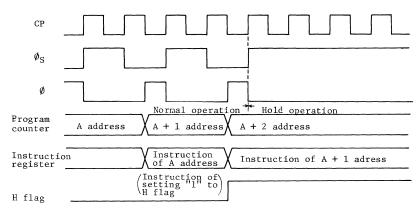

(4) H Flag

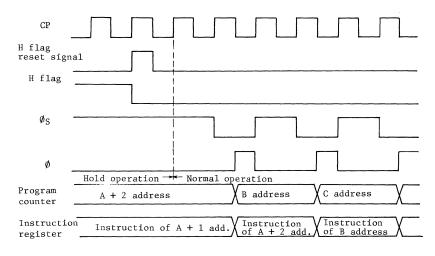

H flag is used as a control signal for hold operation. When "1" is set on H flag, the timing generator is placed in hold mode and the operation is held suspensed. The restart from the hold mode is accomplished by resetting H flag at "0" in the hardware processing, and after released from the hold mode, the process that was held suspended prior to the hold operation is resumed. However, interrupt request is not accepted under the hold operation.

When the hold operation is not used (specified by mask option), H flag becomes a general purpose flag bit that can be optionally used by user.

H flag is reset at "O" by the initialize operation.

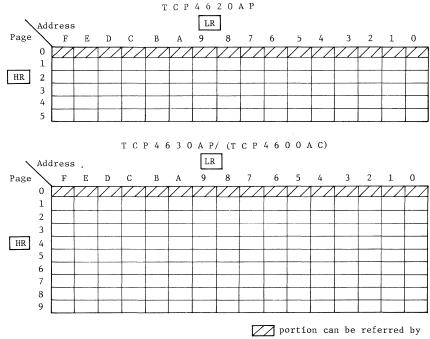

(4) H Register (HR), L Register (LR), Y Register (YR), Y Register Flag (EYR)

H register and L register are 4-bit registers and function as an address pointer of the data memory (RAM) or a general purpose register.

When H register and L register are used as an address pointer of the data memory, H register represents high order 4 bits of an address and L register represents low order 4 bits, and they designate an address space of total 8 bits (256 words). Therefore, when 16 words in the address space of the data memory are expressed as one page, H register designates a page address and L register designates an address in the page.

When an undefined region without data memory is read with H register and L register used as address pointers of the data memory, the data memory contents are regarded as being undefined. Further, data write into an undefined region should be avoided.

Y register is a 4-bit register and functions as an address pointer in page 0 of the data memory or a general purpose register.

Y register flag is an 1-bit flag that shows as to whether H register or L register is used as an address pointer of the data memory. When Y register flag is "1" (EYR=1), Y register is selected as an address pointer of the data memory, and when Y register flag is "0" (EYR=0), H register and L register are selected as address pointers.

Y register flag is set at "1" by the execution of Y register data setting instruction. And Y register flag is cleared at "0" by the execution of the instruction which does not set data to data memory. Further,while Y register flag is set at "1", it is kept in interrupt disabled (waiting) state.

Y register flag is reset at "0" by the initialize operation.

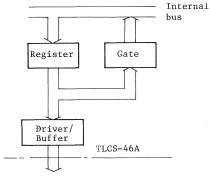

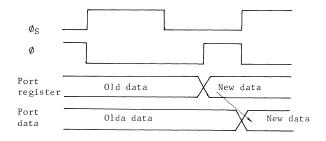

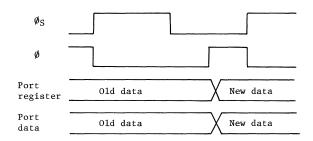

(5) Port (P), Port Register (Register)

TCP4620AP/TCP4630AP is provided with a total 34 ports; input port, output port, input output port, and input/output port.

ТСР4620АР тср4630АР

When a port is used as input, it is processed as non-latch input, and therefore, it is necessary to hold external input data till completion of read-in.

When a port is used as output, output data is set in the port register by an instruction and contents of this prot register are output. On some ports it is possible to read contents of the port registers by an instruction.

Further, the port register is reset at "0" by initialize operation. In addition, the input level is compatible with CMOS, and the output level is compatible with CMOS/TTL.

General purpose input port configuration

| Port | Configuration |

|------|---------------|

|------|---------------|

| Port Name                      | Symbol | Pin Name                          | Register<br>Number | Port<br>Function       | Remarks                                                                                                                  |

|--------------------------------|--------|-----------------------------------|--------------------|------------------------|--------------------------------------------------------------------------------------------------------------------------|

| Input Ou <b>t-</b><br>Put port | Po     | P <sub>03</sub> - P <sub>00</sub> | 0                  | Input out-<br>put port | Control designating of I/O by D flag.<br>This port can be specified as an ex-<br>clusive use output port by mask option. |

INTEGRATEDCIRCUIT

| Port Name                 | Symbol          | Pin Name                            | Register<br>Number | Port<br>Function | Remarks                                                                                                                |

|---------------------------|-----------------|-------------------------------------|--------------------|------------------|------------------------------------------------------------------------------------------------------------------------|

| Output<br>Port            | P <sub>1</sub>  | P <sub>13</sub> - P <sub>10</sub>   | 1                  | Output<br>port   | General purpose output port. Con-<br>tents of registers can be read by<br>an instruction.                              |

| I/O Port                  | P 2             | P <sub>23</sub> - P <sub>20</sub>   | 2                  | I/O port         | Input/output is specified by mask<br>option. Contents of registers can<br>be read by instruction at the output         |

| I/O Port                  | Ρ4              | P <sub>43</sub> - P <sub>40</sub>   | 4                  | I/O port         | mode.                                                                                                                  |

| Key Input<br>Port         | PI5             | PI <sub>53</sub> ¬PI <sub>50</sub>  | 5                  | Input<br>port    | General purpose input port with a 150KΩ(Typical) resistor. (Pull-<br>up/down can be specified by mask<br>options).     |

| Digit<br>Output<br>Port   | PO5             | PO54-PO50                           | 2                  | Output<br>port   | Digit output port for dynamic dis-<br>play. Can be specified as a gen-<br>eral purpose output port by mask<br>options. |

| Input Port                | PI <sub>6</sub> | PI <sub>60</sub>                    | 6                  | Input<br>port    | General purpose input port.                                                                                            |

| Segment<br>Output<br>Port | PO <sub>6</sub> | PO <sub>6 7</sub> PO <sub>6 0</sub> | U                  | Output<br>port   | 8-segment output port for dynamic<br>display. Can be specified as a<br>general purpose output port by<br>mask options. |

Generalization of Segment Output Port (Sepcified by Mask Options)

| Port Name      | Symbol          | Pin Name                            | Register<br>Number | Port<br>Function | Remarks                      |

|----------------|-----------------|-------------------------------------|--------------------|------------------|------------------------------|

| Output<br>Port | PO <sub>6</sub> | PO63 - PO60                         | 6                  | Output<br>port   | General purpose output port. |

| Output<br>Port | PO7             | P0 <sub>73</sub> - P0 <sub>70</sub> | 7                  | Output<br>port   | General purpose output port. |

Port 0 (Po)

Port 0 is a 4-bit general purpose input/output port. This port is selected when Register 0 is specified in an instruction.

Input/output designation is made by D flag of the status register. When D flag is "0", this port becomes the input and when D flag is "1", it becomes the output and output the content of Register 0. Port 0 can be used as an exclusive output port by mask options.

2 Port 1 (P1)

Port 1 is a 4-bit general purpose output port. This port is selected when Register 1 is specified in an instruction and the content of Register 1 is output.

Further, the content of Register 1 can be read by an instruction.

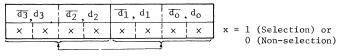

③ Port 2 (P2), Port 4 (P4)

Port 2 and Port 4 are 4-bit input/output ports that can be specified as either input or output by mask options. When Register 2 and Register 4 are specified in an instruction, Port 2 and Port 4 are selected, respectively.

In specifying input or output in a mask option, the following combination is possible.

(a) p2/F/, P4/F/-Port 2 and Port 4 as output.

(b) P2/F/, P4/3/-Port 2 as output. High order 2 bits (P43,P42) of Port 4 as input, low order 2 bits (P41, P40) as output.

(c) P2/0/, P4/F/-Port 2 as input. Port 4 as output.

(d) Specify  $P2/\theta/$ , P4/3/-Port 2 as input.

High order 2 bits (P43,P42) of Port 4 as input low order 2 bits (P41, P40) of Port 4 as output.

(e) Specify P2/0/, P4/0/-Port 2 and P4 as input.

Further, in case of input bits these ports operate as non-latch inputs, and in case of output bits they operate functionally same as in Port 1.

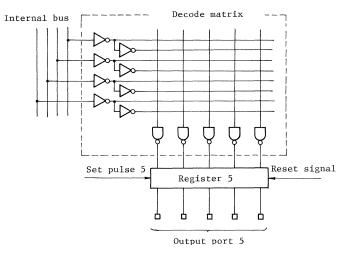

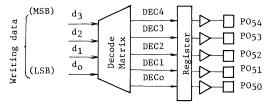

(4) Output Port 5 (PO5)

Output Port 5 is a 5-bit output port with the purpose of digit data output in dynamic display.

When an instruction for writing data in Register 5 is executed, 4-bit data on the internal bus is converted into 5-bit data by the decoder matrix, this data is written into the 5-bit Register 5 and further, output to Port 5.

User is able to specify the content of the decode matrix optionally by mask options.

Further, the content of Register 5 cannot be read by an instruction.

```

(5) Input Port 5 (PI5)

```

Input Port 5 is a 4-bit input port. This port is selected by a Read Register 5 instruction.

Input Port 5 is equipped with a  $150k\Omega($  Typ.) input resistor, and the pull-up/down is specified by mask options.

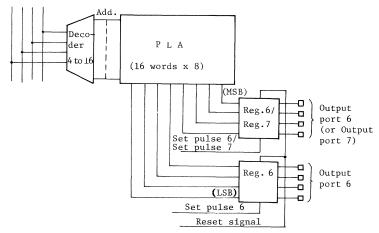

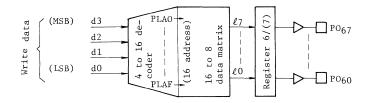

6 Output Port 6 (PO<sub>6</sub>), Output Port 7 (PO<sub>7</sub>)

Output Port 6 is a 8-bit output port for segment data output in dynamic display.

When an instruction for writing data in Register 6 is executed, a output data is read from 16 words x 8 bits PLA with a 4-bit data on the internal bus used as an address, this output data is written into the 8-bit Register 6, and output to Port 6.

#### TECHNICAL DATA

## TCP4620AP TCP4630AP

User is able to specify the content of PLA optionally by mask options.

Further, it is possible to specify and use output Port 6 as two 4-bit general purpose output ports by mask options. In this case, the 8-bit output port is split into high order 4 bits and low order 4 bits, and the high order 4 bits are assigned to output Port 7 (Register 7) and low order 4 bits to Output Port 6 (Register 6).

The contents of Register 6 (and Register 7) cannot be read by an instruction.

Internal bus

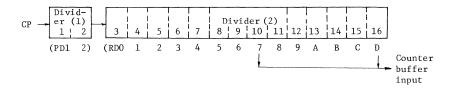

#### ⑦ Input Port 6 (PI6), Counter Buffer

Input Port 6 is the input port of 1 terminal ( $PI_{60}$ ), but internally it is treated as a 4-bit data in combination with 3-bit data that are output from the divider (refer to Item for Divider).

The read circuit which reads this 4-bit data is called Counter Buffer/Input Port 6 or Counter Buffer simply. This counter buffer is selected by a Read Register 6 instruction and processed as 4-bit parallel non-latch input as in other input ports.

The bit configuration of the counter buffer is such that external input from PI60 terminal is connected to LSB side 1 bit and output from the divider is connected to MSB side 3 bits.

Further, the output stage of the divider to be connected is specified by mask options, but is fixed by a combination of an oscillator to be used and internal basic frequency. (Refer to Item for Divider.)

A Schmitt circuit and a timing shaping shift register are connected to PI60 terminal, which therefore cannot be operated at frequency above the internal basic clock frequency. The internal signal from the input terminal is subject to a time delay of maximum.

$$\frac{3}{\text{Internal basic frequency x 2}}$$

(sec.)

(6) Internal Bus (IBUS)

The internal bus consists of 4 bits, connects various registers and blocks such as the accumulator, status register, data memory, H register, L register, Y register, port register, ALU, etc., and data to be processed and data of process result are transfered through the internal bus.

#### (7) Data Memory (RAM)

TLCS-46A Family has the following internal data memories in order to store user's process data.

| Туре       | Capacity            |  |  |  |  |

|------------|---------------------|--|--|--|--|

| TCP4620AP  | 96 words x 4 bits   |  |  |  |  |

| TCP4630AP  | 160 words x 4 bits  |  |  |  |  |

| (TCP4600AC | 160 words x 4 bits) |  |  |  |  |

The data memory consists of the static memory cells.

Addressing of the data memory is executed by contents of H register/L register or Y register.

Y register.

Addressing of Data Memory

# INTEGRATEDCIRCUIT

## TECHNICAL DATA

## TCP4620AP TCP4630AP

(8) Program Memory (ROM)

TLCS-46A Family has the following internal program memory in order to store user's process programs.

| Туре       | Capacity            |

|------------|---------------------|

| TCP4620AP  | 2048 words x 8 bits |

| TCP4630AP  | 3072 words x 8 bits |

| (TCP4600AC | No internal ROM)    |

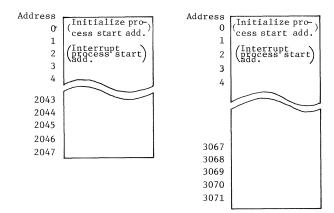

The program memory addressing is executed by the program counter (PC). Inherent meaning is given to Addresses 0 and 2 by the hardware, normal user process programs are place in Address 4 and subsequent addresses.

Further, the program counter consists of 12 bits and is capable of directly specifying addresses up to 4095, however, data in an undefined region having no program memory loaded becomes unstable.

ТСР4620АР

ТСР4630АР

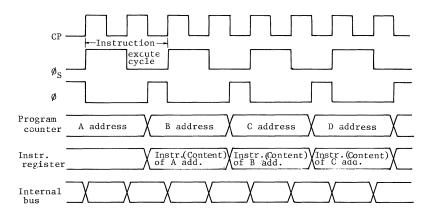

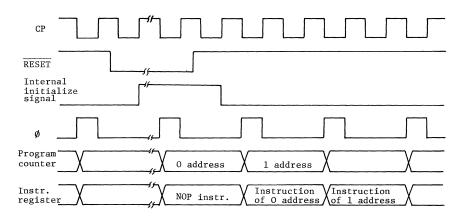

(9) Program Counter (PC)

The program counter consists of a 12-bit binary counter, adds count increment at every instruction fetch, and makes the addressing of a program memory in which an instruction to be executed.

When a branch instruction, an interrupt operation, or subroutine instruction is executed, the contents of the program counter are changed.

Addresses 0 and 2 are compulsorily set in the program counter by a initialize signal and an interrupt request signal, respectively.

(10) Stack (STK), Stack Flag (FSTK)

The stack is used for temporary evacuation of the contents of the program counter when an interrupt request is accepted or a subroutine is to be executed.

The stack flag is a flag indicating whether the contents of the program counter have been evacuated in the stack.

When the contents of the program counter are pushed down in the stack, the stack flag is set at "1" (FSTK=1). And when the contents of the stack are popped up by a RTN instruction and returned to the original program flow, the stack flag is set at "0" (FSTK=0). At time of FSTK=1, the interrupt request becomes the disable (waiting) state.

Further, the stack flag is set at FSTK=1 by the initialize operation.

#### (11) Instruction Register (IR), Instruction Decoder (IDEC)

The instruction register latches a 8-bit data from the program memory and outputs it to the instruction decoder. (Program memory data may be used for direct internal control.)

The instruction decoder receives data from the instruction register and outputs a control signal required for processing.

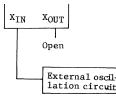

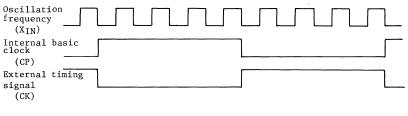

#### (12) Clock Generator (OSC)

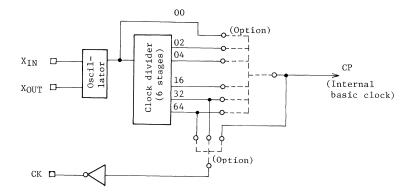

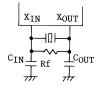

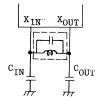

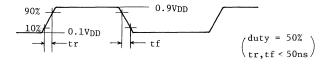

TCP4620AP/TCP4630AP has a internal clock generator. By externally installing a crystal oscillator/ceramic oscillator or a LC oscillator, required clock is easily obtained. Furhter, clock can be supplied externally, however, in this case, the clock is input through  $X_{\rm IN}$  terminal and  $X_{\rm OUT}$  terminal is kept open. While TCP4620AP/TCP4630AP starts by RESET, the clock should be always continuously supplied.

Oscillation frequency shall be selected from several frequencies ranging from 20KHz to 4.2MHz by mask options. The clock generator has a internal 6-stage clock divider and specifies the optimum divide ratio to obtain internal basic clock (CP) on the basis of oscillation frequency by mask options.

The clock generator is provided with the output terminal CK for external timing, and output frequency is specified by mask options.

Further, a divide ratio for obtaining internal basic clock and external timing output frequency specified by mask options (refer to Item for Divider) are determined by an oscillator (oscillation frequency) to be used and internal basic clock frequency.

Clock Generator Circuit Configuration

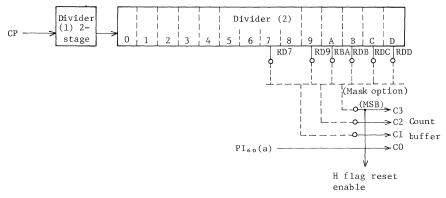

#### (13) Divider

The divider is a binary 16-stage divider provided for a clock counter, timer, etc., and makes the count of internal basic clock (CP).

Of output from the 16-stage divider, 3 bits are connected to the counter buffer by mask options and can be read by a program as the counter buffer contents.

The relation between output 3 bits that can be specified by mask options and the divider output stage is determined by an oscillator (oscillation frequency) to be used and internal basic frequency as shown below.

| Oscillator                 | 32.76K<br>X tal | 100K<br>X tal | 400 -<br>500K<br>Ceramic<br>/IFT | 400K<br>ce-<br>ramic<br>/IFT | 3 -<br>4.2M<br>X tal | 3 -<br>4.2M<br>X tal |  |

|----------------------------|-----------------|---------------|----------------------------------|------------------------------|----------------------|----------------------|--|

| Internal basic CP<br>clock | 00              | 00            | 04                               | 02                           | 64                   | 32                   |  |

| External timing CK         | 32              | 64            | СР                               | СР                           | CP                   | CP                   |  |

| C1                         | RD9             | RDB           | RDB                              | RD7                          | RDA                  | RD7                  |  |

| Counter C2<br>buffer       | RDA             | RDC           | RDC                              | RDA                          | RDB                  | RDA                  |  |

| C3                         | RD B            | RDD           | RDD                              | RDD                          | RDC                  | RDD                  |  |

Further, the most significant bit (C3) of the counter buffer is used as a hold release signal (H flag reset enable signal of the status register) when the hold operation is used.

In addition, only when a 100K Xtal is used as an oscillator, the divider (2) is reset when the count value of the divider (2) reaches "12500" and the count value is reset to zero and then the count is resumed.

#### (14) Timing Generator (TG)

The timing generator consists of the internal timing signal generation circuit, initialize control circuit and interrupt control circuit.

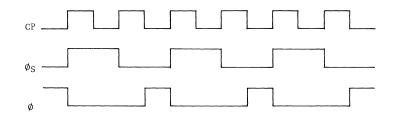

(1) Internal Timing Signal Generation Circuit

This circuit receives the internal basic clock (CP) from the clock generator and generates two internal basic timing signals  $\phi$  and  $\phi_{\rm S}$ .

#### (2) Initialize Control Circuit

This circuit shapes the timing of external RESET signal and generates an internal initialize signal. This initialize signal ia used for internal initialization. (For details of the initialize operation refer to "Operation Description".)

#### (3) Interrupt Control Circuit

This circuit shapes the timing of external interrupt request signal INT, store it in the internal interrupt latch, and makes a judgement as to if the internal state is interrupt enable. When it is in evable state, this circuit generates an interrupt request signal internally and starts an interrupt operation, but if it is in disable state, controls the interrupt request to wait till it becomes enables.

(For details of the interrupt operation refer to "Operation Description".)

## [MACHINE INSTRUCTION]

1. Symbol Meaning

The explanation of symbols used for the following description is collected in the following table.

| Symbol          | Meaning                                                           |

|-----------------|-------------------------------------------------------------------|

| PC              | Program counter                                                   |

| AC              | Accumulator                                                       |

| ST              | Status register                                                   |

| М               | Data memory                                                       |

| LR              | L register                                                        |

| HR              | H register                                                        |

| YR              | Y register                                                        |

| EYR             | Y register flag                                                   |

| С               | C flag of status register                                         |

| Z               | Z flag of status register                                         |

| R               | Port register, Field designating register under instruc-<br>tions |

| I               | Value of immediate data field                                     |

| G               | Field designating bit position under bit processing instructions  |

| AP              | Address branched by branch instructions                           |

| AP <sub>H</sub> | Field showing higher order 4 bits of AP                           |

| APM             | Field showing intermediate order 4 bits of AP                     |

| $AP_L$          | Field showing lower order 4 bits of AP                            |

| (A)             | Content of A                                                      |

| (Ā)             | Values that contents of A are inverted every bit                  |

| +               | Binary addition                                                   |

| -               | Binary subtraction                                                |

| ^               | Logical AND for every bit                                         |

| ~               | Logical OR for every bit                                          |

TECHNICAL DATA

INTEGRATEDCIRCU

## TCP4620AP TCP4630AP

| Symbol              | Meaning                                               |

|---------------------|-------------------------------------------------------|

| ¥                   | Exclusive OR for every bit                            |

| *                   | Value of left side is equalized to that of right side |

| A <a :="" b=""></a> | Content from b bitth to a bitth of A                  |

| 0                   | Value is made into one by connecting two fields       |

| *                   | Value is updated by operation result                  |

| -                   | Value is not changed by operation result              |

| Push PC             | Content of program counter is saved in stack          |

| Pop PC              | Content of stack is returned to program counter       |

| Nu11                | No operation                                          |

#### 2. Instruction Description

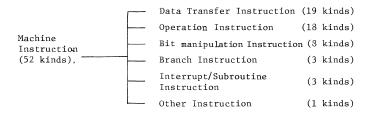

The machine instruction of TLCS-46A consists of 52 kinds of instruction, being divided roughly into 6 kinds as follows:

In this paragraph, the function of each instruction is described according to the following instruction description description format.

|                       | Instruction name      |                                              |                    |

|-----------------------|-----------------------|----------------------------------------------|--------------------|

| Assembler<br>mnemonic | Machine code          |                                              | Execution<br>cycle |

|                       | Function              | Z flag C fla<br>after<br>execu-<br>tion tion | after              |

|                       | Operation description |                                              |                    |

#### Instruction Description Format

#### (1) Data Transfer Instruction

The data transfer instruction mainly provides the data transfer among accumulator, status register, memory (RAM), and registers.

|       | Load Accumulator from Regsiter                                                        |   |

|-------|---------------------------------------------------------------------------------------|---|

|       | 70                                                                                    |   |

| LAR R | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                 | 1 |

|       | $(AC) \leftarrow (R)$                                                                 | 0 |

|       | The content of register or input port designated by R field is loaded in accumulator. | I |

INTEGRATEDCIRCUIT

TECHNICAL DATA

|       | Load Accumulator from Register and Test                                                          |   |   |    |

|-------|--------------------------------------------------------------------------------------------------|---|---|----|

| LTR R | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                           |   |   | 1  |

|       | $(AC) \leftarrow (R)$                                                                            | * | - | 0  |

|       | The content of resister or input port designate<br>loaded in accumulator. After execution Z flag | , |   | is |

|       | Load Accumulator from Memory                                                                     |   |   |    |

| LAM   | 7 0                                                                                              |   |   | 1  |

|       | $(AC) \leftarrow (M)$                                                                            | - | - | 0  |

|       | The content of memory is loaded in accumulator<br>Note 1                                         |   |   |    |

|       | Load Accumulator from Memory and Test                                                            |   |   |    |

| LTM   | 7 0<br>1 0 0 0 0 1 1 1                                                                           |   |   | 1  |

|       | (AC) ← (M)                                                                                       | * | - | 0  |

|       | The content of memory is loaded in accumulator.<br>After execution Z flag is updated.<br>Note 1  |   |   |    |

|       | Load Status-register from Memory                       |         |                    |   |

|-------|--------------------------------------------------------|---------|--------------------|---|

|       | 7 0                                                    |         |                    |   |

| LSM   | 0 0 0 0 1 0 1                                          |         |                    | 1 |

|       |                                                        | Note 3  | Noto 3             |   |

|       | $(ST) \leftarrow (M)$                                  | *       | *                  | 0 |

|       |                                                        |         |                    |   |

|       | The content of memory is loaded in status re<br>Note 1 | egister | •                  |   |

|       | Load Accumulator from L-register                       |         |                    |   |

|       |                                                        |         | Tanka - Vana - Tan |   |

| LAL   | 7 0 0 0 0 1 1 0                                        |         |                    | 1 |

|       |                                                        |         |                    |   |

|       | $(AC) \leftarrow (LR)$                                 | -       | -                  | 0 |

|       | The content of L register is loaded in accum           | ulator  |                    |   |

|       | The content of B register is found in accum            | aracor  | •                  |   |

|       | Load Accumulator from H-register                       |         |                    |   |

|       | 7 0                                                    |         |                    |   |

| LAH   |                                                        |         |                    | 1 |

|       | $(AC) \leftarrow (HR)$                                 | _       | _                  | 0 |

|       |                                                        |         |                    |   |

|       | The content of H register is loaded in accum           | ulator  | •                  |   |

|       |                                                        |         |                    |   |

|       | Load Accumulator Immediate                             |         |                    |   |

|       | 7 0                                                    |         |                    |   |

| LAI I | $0   1   0   0   I = 0 \le I \le 15$                   |         |                    | 1 |

|       |                                                        |         |                    |   |

|       | (AC) ← I                                               | -       | -                  | 0 |

|       | The value of I field is set to accumulator.            |         |                    |   |

|       |                                                        |         |                    |   |

| 1     |                                                        |         |                    |   |

|       | Load L-register Immediate                                                                 |        |    |   |

|-------|-------------------------------------------------------------------------------------------|--------|----|---|

| LLI I | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |        |    | 1 |

|       | (LR) ← I                                                                                  | -      | -  | 0 |

|       | The value of I field is set to L register.                                                |        |    |   |

|       | Load H-register Immediate                                                                 |        |    |   |

| LHI I | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |        |    | 1 |

|       | (HR) + I                                                                                  | -      | -  | 0 |

|       | The value of I field is set to H register.                                                |        |    |   |

|       | Load Y-register Immediate                                                                 |        |    |   |

| LYI I | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |        |    | 1 |

|       | (YR) + I                                                                                  | -      | -  | 1 |

|       | The value of I field is set to Y register. After execution, Y register flag is set to "1" | ".     |    |   |

|       | Store Accumulator to Register                                                             |        |    |   |

| SAR R | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                    |        |    | 1 |

|       | $(R) \leftarrow (AC)$                                                                     | -      | -  | 0 |

|       | The content of accumulator is stored in the designated by R field.                        | regist | er |   |

|       | Store Accumulator to Memory                 |         |   |   |

|-------|---------------------------------------------|---------|---|---|

| SAM   | 7 0 0 0 0 1 1 0 0                           |         |   | 1 |

|       | (M) ← (AC)                                  | -       | - | - |

|       | The content of accumulator is stored in mem | roy.    |   |   |

|       | Note 1, Note 2                              |         |   |   |

|       | Store Status-register to Memory             |         |   |   |

| SSM   |                                             |         |   | 1 |

|       | (M) ← (ST)                                  | -       | - | - |

|       | The content of status register is stored in | memory  | , |   |

|       | Note 1, Note 2                              | -       |   |   |

|       | Store Accumulator to L-register             |         |   |   |

| SAL   |                                             |         |   | 1 |

|       | $(LR) \leftarrow (AC)$                      | -       | - | 0 |

|       | The content of accumulator is stored in L r | egister |   |   |

|       | Store Accumulator to H-register             |         |   |   |

| S A H | 7 0 0 0 0 1 1 1 1 1                         |         |   | 1 |

|       | (HR) ← (AC)                                 | -       | - | 0 |

|       | The content of accumulator is stored in H r | egister |   |   |

|       | Store Accumulator to Y-register                                                                                                                                                            |    |  |

|-------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|--|

| SAY   | 7 0 0 0 0 1 0 0 0                                                                                                                                                                          |    |  |

|       | (YR) ← (AC) – –                                                                                                                                                                            | 1  |  |

|       | The content of accumulator is stored in Y register.<br>After execution, Y register flag is set to "1".                                                                                     |    |  |

|       | Store Y-register to Register                                                                                                                                                               |    |  |

| SYR R | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                      | 1  |  |

|       | (R) + (YR)                                                                                                                                                                                 | 0  |  |

|       | The content of Y register is stored in register designate<br>by R field.                                                                                                                   | ed |  |

|       | Clear Register                                                                                                                                                                             |    |  |

| CLR R | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                      | 1  |  |

|       | $(R) \leftarrow 0 \qquad (0 \leq R \leq 4) \qquad - \qquad -$                                                                                                                              | 0  |  |

|       | "0" is written in the register designated by R field ( $0 \le R \le 4$ )<br>For $5 \le R \le 7$ , decode matrix output or PLA output corresponding<br>data "0" is written in the register. |    |  |

#### (2) Operation Instruction

Operation instruction has 2 operand instruction and 1 operand instruction, and performs arithmetic operation and logical operation.

|       | Add Accumulator Immediate                                                                                                                         |        |         |      |

|-------|---------------------------------------------------------------------------------------------------------------------------------------------------|--------|---------|------|

| ADI I | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                            |        |         | 1    |

|       | (AC) ← (AC) + I                                                                                                                                   | *      | *       | 0    |

|       | The value of I field is added to the content of After execution of instruction, Z flag and C f                                                    |        |         |      |

|       | Add and Store to Accumulator                                                                                                                      |        |         |      |

| ADA   |                                                                                                                                                   |        |         | 1    |

|       | $(AC) \leftarrow (M) + (AC)$                                                                                                                      | *      | *       | 0    |

|       | The content of accumulator is added to the cor<br>and the result is loaded in accumulator. Afte<br>instruction, Z flag and C flag are updated.    |        |         |      |

|       | Add and Store to Memory                                                                                                                           |        |         |      |

| ADM   | 7 0 0 0 1 0 0 0                                                                                                                                   |        |         | 1    |

|       | $(M) \leftarrow (M) + (AC)$                                                                                                                       | *      | *       | -    |

|       | The content of accumulator is added to the cor<br>and the result is stored in memory. After exe<br>struction, Z flag and C flag are updated. Note | cution | of in-  | у,   |

|       | Add with Carry and Store to Accumulator                                                                                                           |        |         |      |

| АСА   | 7 0<br>1 0 0 0 0 0 1                                                                                                                              | 1      |         | 1    |

|       | $(AC) \leftarrow (M) + (AC) + (C)$                                                                                                                | *      | *       | 0    |

|       | The content of accumulator and the content of<br>the content of memory, and the result is loade<br>After execution of instruction,Z flag and C fl | d in a | ccumula | tor. |

INTEGRATEDCIRCUIT

TECHNICAL DATA

|                                        | Add with Carry and Store to Memory                                                                                                                |         |         |       |

|----------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|-------|

| АСМ                                    | 7 0                                                                                                                                               |         |         | 1     |

|                                        | $(M) \leftarrow (M) + (AC) + (C)$                                                                                                                 | *       | *       | -     |

|                                        | The content of accumulator and the content of<br>the content of memory, and the result is sotr<br>execution of instruction,Z flag and Cflag are u | ed in m | emory.  | After |

|                                        | Subtract and Store to Accumulator                                                                                                                 |         |         |       |

| SUA                                    |                                                                                                                                                   |         |         | 1     |

|                                        | $(AC) \leftarrow (M) - (AC)$                                                                                                                      | *       | *       | 0     |

|                                        | The content of accumulator is subtracted from memory, and the result is loaded in accumulat of instruction, Z flag and C flag are updated         | or. Af  | ter exe |       |

| ······································ | Subtract and Store to Memory                                                                                                                      |         |         |       |

| SUM                                    | 7 0<br>1 0 0 0 1 0 1 0 1                                                                                                                          |         |         | 1     |

|                                        | (M) - (M) - (AC)                                                                                                                                  | *       | *       | -     |

|                                        | The content of accumulator is subtracted from memory, and the result is stored in memory. instruction,Z flag and C flag are updated. N            | After e | xecutio |       |

|                                        | Or and Store to Accumulator                                                                                                                       |         |         |       |

| ORA                                    | 7 0                                                                                                                                               |         |         | 1     |

|                                        | $(AC) \leftarrow (M) \lor (AC)$                                                                                                                   | *       | -       | 0     |

|                                        | The logical sum of every bit of the content<br>content of accumulator is loaded in accumula<br>tion of instruction, Z flag is updated. Note       | tor. A  |         |       |

|     | Or and Store to Memory                                                                                                                       |         |                     |             |

|-----|----------------------------------------------------------------------------------------------------------------------------------------------|---------|---------------------|-------------|

| ORM | 7 0 0 0 0 1 1 0 0                                                                                                                            |         |                     | 1           |

|     | $(M) \leftarrow (M) \lor (AC)$                                                                                                               | *       | -                   | -           |

|     | The logical sum of every bit of the content o<br>content of accumulator is stored in memory.<br>of instruction, Z flag is updated. Note 1, N | After t | -                   |             |

|     | Exclusive-or and Store to Accumulator                                                                                                        |         |                     |             |

| ЕОА |                                                                                                                                              |         |                     | 1           |

|     | $(AC) \leftarrow (M) \nleftrightarrow (AC)$                                                                                                  | *       | -                   | 0           |

|     | The exclusive OR of every bit of the content<br>content of accumulator is loaded in accumulat<br>of instruction, Z flag is updated. Note 1   |         |                     |             |

|     | Exclusive-or and Store to Memory                                                                                                             |         |                     |             |

| ЕОМ | 7 0 0 0 0 1 1 0 1                                                                                                                            |         |                     | 1           |

|     | $(M) \leftarrow (M) \checkmark (AC)$                                                                                                         | *       | -                   | -           |

|     | The exclusive OR of every bit of the content<br>content of accumulator is stored in memory.<br>instruction, Z flag is updated. Note 1, Note  | After e | bry and<br>executio | the<br>n of |

|     | Complement Accumulator                                                                                                                       |         |                     |             |

| СМА | 7 0                                                                                                                                          |         |                     | 1           |

|     | $(AC) \leftarrow \overline{(AC)}$                                                                                                            | *       | _                   | 0           |

|     | The content of accumulator is inverted every<br>After exectuion of instruction, Z flag is upd                                                |         |                     |             |

INTEGRATEDCIRCUIT

TECHNICAL DATA

|     | Complement Accumulator and Store to Memory                                                                                    |         |                    |           |

|-----|-------------------------------------------------------------------------------------------------------------------------------|---------|--------------------|-----------|

| СММ |                                                                                                                               |         |                    | 1         |

|     | $(M) \leftarrow \overline{(AC)}$                                                                                              | *       | -                  | -         |

|     | The content of accumulator is inverted every h<br>is stored in memory. After execution of instr<br>updated. Note 1, Note 2    |         |                    |           |

|     | Load Accumulator and Increment                                                                                                |         |                    |           |

| ICA | 7 0<br>1 0 0 0 0 0 1 1 1                                                                                                      |         |                    | 1         |

|     | $(AC) \leftarrow (M) + 1$                                                                                                     | *       | *                  | 0         |

|     | "1" is added to the content of memory, and the<br>in accumulator. After execution of instruction<br>flag are updated. Note 1. | e resul | t is lo<br>lag and | aded<br>C |

|     | Increment Memory                                                                                                              |         |                    |           |

| ІСМ | 7 0 1 0 0 0 1 0 1 1                                                                                                           |         |                    | 1         |

|     | ,<br>(M) ← (M) + 1                                                                                                            | *       | *                  | -         |

|     | "1" is added to the content of memory. After<br>struction, Z flag and C flag are updated.<br>Note 1, Note 2 .                 | execut  | ion of i           | in-       |

|     | Increment L-register                                                                                                          |         |                    |           |

| ICL |                                                                                                                               |         |                    | 1         |

|     | $(LR) \leftarrow (LR) + 1$                                                                                                    | -       | -                  | 0         |

|     | "1" is added to the content of L register.                                                                                    |         |                    |           |

|     |                                                                                                                               |         |                    |           |

|     | Increment H-register                                            |      |   |   |  |

|-----|-----------------------------------------------------------------|------|---|---|--|

| ІСН | 7     0       0     0     0     0     1     1                   |      |   | 1 |  |

|     | (HR) ← (HR) + 1                                                 | -    | - | 0 |  |

|     | "1" is added to the content of H register.                      |      |   |   |  |

|     | Test Memory                                                     |      |   |   |  |

| тѕм | 7 0<br>1 0 0 0 1 1 1 1 1<br>1 0                                 |      |   |   |  |

|     | (M) ← (M)                                                       | *>   | _ | - |  |

|     | Z flag is set according to the content of mem<br>Note 1, Note 2 | ory. |   |   |  |

#### (3) Bit Manipulation Instruction

The bit manipulation instruction is performed to each bit of accmulator or status register.

|       | Test a bit for Accumulator                                            |       |        |   |  |

|-------|-----------------------------------------------------------------------|-------|--------|---|--|

|       | 7 0                                                                   |       |        |   |  |

| TBA G | $1 \   \ 0 \   \ 1 \   \ 0 \   \ 0 \   \ 0 \ G \qquad 0 \le G \le 3$  |       |        | 1 |  |

|       | Null $\leftarrow$ (AC) $\land 2^{G}$                                  | *     | -      | 0 |  |

|       | The Z flag is updated, according to the bit of designated by G field. | accum | ulator |   |  |

|       | Tast a bit for Status-register                                                      |      |

|-------|-------------------------------------------------------------------------------------|------|

| TBS G | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                              | 1    |

|       | Null $\leftarrow$ (ST) $\land 2^{G}$ * -                                            | 0    |

|       | The Z flag is updated, according to the bit of status regist designated by G field. | er   |

|       | Set a bit for Accumulator                                                           |      |

| SBA G | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                              | 1    |

|       | $(AC) \leftarrow (AC) \lor 2G$                                                      | 0    |

|       | The bit of accumulator designated by G field is set to "1".                         |      |

|       | Set a bit for Status-register                                                       |      |

| SBS G | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                               | 1    |

|       | $(ST) \leftarrow (ST) \lor 2^{G}$ Note 3 Note 3 * *                                 | 0    |

|       | The bit of status-register designated by G field is set to "                        | '1". |

|       | Clear a bit for Accumulator                                                         |      |

| CBA G | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                               | 1    |

|       | $(AC) \leftarrow (AC) \land \overline{2^G}$                                         | 0    |

|       | The bit of accumulator designated by G field is cleared to "                        | '0". |

|       | Clear a bit for Status register                                                                |    |

|-------|------------------------------------------------------------------------------------------------|----|

| CBS G | $\begin{bmatrix} 7 & & 0 \\ \hline 1 & 0 & 1 & 1 & 1 & 0 \\ \end{bmatrix}  G  0 \leq G \leq 3$ | 1  |

|       | $(ST) \leftarrow (ST) \land 2^{\overline{G}}$ Note 3 Note 3 *                                  | 0  |

|       | The bit of status register designated by G field is cleared "0".                               | to |

|       | Invert a bit for Accumulator                                                                   |    |

| IBA G | $ \begin{array}{cccccccccccccccccccccccccccccccccccc$                                          | 1  |

|       | $(AC) \leftarrow (AC) \neq 2^{G}$                                                              | 0  |

|       | The bit of accumulator designated by G field is inverted.                                      |    |

|       | Invert a bit for Status register                                                               |    |

| IBS G | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                         | 1  |

|       | $(ST) \leftarrow (ST) \neq 2G$<br>Note 3 Note 3 *                                              | 0  |

|       | The bit of status register designated by G field is inverted                                   | 1. |

### (4) Branch nstruction

|        | Jump                                                                                                                                                                                                                                                                                      |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|        | 7 015 8                                                                                                                                                                                                                                                                                   |

| JMP AP | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                                                                                    |

|        | 0 S Ar S 4095                                                                                                                                                                                                                                                                             |

|        | (PC) ← AP 0                                                                                                                                                                                                                                                                               |

|        | The value of AP field is set to program counter. After execution of instruction, therefore, program sequence changes to the AP address.                                                                                                                                                   |

|        | Branch on Condition Set                                                                                                                                                                                                                                                                   |

| BCS AP | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                     |

| 500 m  | $0 \le AP \le 4095$                                                                                                                                                                                                                                                                       |

|        | If Z = 1 then (PC) $\leftarrow$ AP, else Null 0                                                                                                                                                                                                                                           |

|        | The content of Z flag is "1", the value of AP field is set to pro-<br>gram counter. After execution of instruction, therefore, progra<br>sequence changes to the AP address.<br>If the content of Z flag is "0", the program sequence follows<br>the next address without any operation.  |

|        | Branch on Condition Clear                                                                                                                                                                                                                                                                 |

| BCC AP | $ \begin{array}{c ccccccccccccccccccccccccccccccccccc$                                                                                                                                                                                                                                    |

|        | If Z = 0 then (PC) $\leftarrow$ AP, else Null 0                                                                                                                                                                                                                                           |

|        | The content of Z flag is "0", the value of AP field is set to pro-<br>gram counter. After execution of instruction, therefore, program<br>sequence changes to the AP address.<br>If the content of Z flag is "1", the program sequence follows<br>the next address without any operation. |

The branch instruction performs unconditional or conditional branch.

#### (5) Interrupt/Subroutine Instruction

The interrupt/subroutine instruction is used for performing a call of subroutine and a return from interrupt routine or subroutine.

In addition NOP instruction is available as one other instruction.

|        | Call Subroutine                                                                                                                                                                                                             |         |         |                |

|--------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------|---------|----------------|

|        | 7 015                                                                                                                                                                                                                       |         | 8       |                |

| CAL AP | $\begin{array}{ c c c c c c c c c c c c c c c c c c c$                                                                                                                                                                      | М       |         | 2              |

|        | $0 \leq AP \leq 4095$                                                                                                                                                                                                       |         |         |                |

|        | push (PC), and (PC) $\leftarrow$ AP                                                                                                                                                                                         | -       | -       | 0              |

|        | The content (the next address) of program cour<br>the stack, and the value of AP field is set to<br>counter. The interrupt is placed in disable<br>during execution of subroutine.                                          | o the p | rogram  |                |

|        | Return                                                                                                                                                                                                                      |         |         |                |

| RTN    | 7 0                                                                                                                                                                                                                         |         |         | 2              |

|        | POP (PC)                                                                                                                                                                                                                    | -       | -       | 0              |

|        | The content of the stack is restored to progr<br>execution of instruction, the interrupt is pl                                                                                                                              |         |         | After<br>state |

|        | Jump by Accumulator                                                                                                                                                                                                         |         |         |                |

| JAC    | 7 0<br>0 0 0 0 0 1 0 0 1                                                                                                                                                                                                    |         |         | 2              |

|        | (PC)+(PC)+1, and (PC)+(PC)<11:4>∘(AC)                                                                                                                                                                                       | -       | -       | 0              |

|        | The content (address where JAC instruction is<br>the incremented program counter is taken as th<br>the content of AC is taken as the lower 4 bits<br>of 12 bits in total that these contents are co<br>the program counter. | ne high | er 8 bi | ts, and        |

|        | No Operation                                                                                                                                                                                                                |         |         |                |

| NOP    |                                                                                                                                                                                                                             |         |         | 1              |

|        | Null                                                                                                                                                                                                                        | -       | -       | 0              |

|        | This is an instruction by which nothing is exec<br>However, Y register flag is reset to "O".                                                                                                                                | cuted.  | L       |                |

Note 1: The address of data memory becomes as follows;

EYR = 0, (HR $\circ$ LR) EYR = 1, (O $\circ$ YR).

Note 2: Care should be taken to the fact that, even after this instruction is ececuted, Y register flag does not change.

Note 3: A flag may be updated as a result of processing.

TECHNICAL DATA

TCP4620AP TCP4630AP

# 3. LIST OF INSTRUCTIONS

|                           | Mne-<br>monic                                                                                                                     | Machin<br>Hexa-<br>decimal                                                                                                                                                                                        | e code<br>Binary                                                                            | Operation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | Update<br>of flag                                                                       | Remarks                  |

|---------------------------|-----------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------|--------------------------|

| Data Transfer Instruction | LAR<br>LTR<br>LAM<br>LAM<br>LAL<br>LAL<br>LAH<br>LAI<br>LLI<br>LHI<br>LYI<br>SAR<br>SAM<br>SAM<br>SAL<br>SAH<br>SAY<br>SYR<br>CLR | $ \begin{array}{c} 1\underline{i} \\ 1\underline{i} \\ 04 \\ 87 \\ 05 \\ 06 \\ 07 \\ 4i \\ 6i \\ 7i \\ 5i \\ 2\underline{i} \\ 0C \\ 0D \\ 0E \\ 0F \\ 08 \\ 3\underline{1} \\ 2\underline{i} \\ 01 \end{array} $ | 000101111<br>00001111<br>00000110<br>10000111<br>00000110<br>00000110<br>01001111<br>011011 | $(AC) \leftarrow (Register 1ii)$<br>$(AC) \leftarrow (Register 1ii)$<br>$(AC) \leftarrow (M)$<br>$(AC) \leftarrow (M)$<br>$(AC) \leftarrow (M)$<br>$(AC) \leftarrow (LR)$<br>$(AC) \leftarrow (LR)$<br>$(AC) \leftarrow (LR)$<br>$(AC) \leftarrow (III)$<br>$(AC) \leftarrow (III)$<br>$(AC) \leftarrow (III)$<br>$(AC) \leftarrow (III)$<br>$(AC) \leftarrow (III)$<br>$(AC) \leftarrow (III)$<br>$(Register 1ii) \leftarrow (AC)$<br>$(Register 1ii) \leftarrow (VR)$<br>$(Register 1ii) \leftarrow (0)$                                                                                                                                                                                                                                                    | Z<br>Z<br>ZC                                                                            | EYR is set<br>EYR is set |